Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Dataila                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Details                    |                                                                                |

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f256l-v-pf |

### TABLE 5: PIN NAMES FOR 100-PIN DEVICES

100-PIN TQFP (TOP VIEW)(1,2)

PIC32MX430F064L PIC32MX450F128L PIC32MX450F256L PIC32MX470F512L

100

1

| Pin# | Full Pin Name                         |

|------|---------------------------------------|

| 1    | RG15                                  |

| 2    | Vpp                                   |

|      | AN22/RPE5/PMD5/RE5                    |

| 3    |                                       |

| 4    | AN23/PMD6/RE6                         |

| 5    | AN27/PMD7/RE7                         |

| 6    | RPC1/RC1                              |

| 7    | RPC2/RC2                              |

| 8    | RPC3/RC3                              |

| 9    | RPC4/CTED7/RC4                        |

| 10   | AN16/C1IND/RPG6/SCK2/PMA5/RG6         |

| 11   | AN17/C1INC/RPG7/PMA4/RG7              |

| 12   | AN18/C2IND/RPG8/PMA3/RG8              |

| 13   | MCLR                                  |

| 14   | AN19/C2INC/RPG9/PMA2/RG9              |

| 15   | Vss                                   |

| 16   | VDD                                   |

| 17   | TMS/CTED1/RA0                         |

| 18   | RPE8/RE8                              |

| 19   | RPE9/RE9                              |

| 20   | AN5/C1INA/RPB5/VBuson/RB5             |

| 21   | AN4/C1INB/RB4                         |

| 22   | PGED3/AN3/C2INA/RPB3/RB3              |

| 23   | PGEC3/AN2/C2INB/RPB2/CTED13/RB2       |

| 24   | PGEC1/AN1/RPB1/CTED12/RB1             |

| 25   | PGED1/AN0/RPB0/RB0                    |

| 26   | PGEC2/AN6/RPB6/RB6                    |

| 27   | PGED2/AN7/RPB7/CTED3/RB7              |

| 28   | VREF-/CVREF-/PMA7/RA9                 |

| 29   | VREF+/CVREF+/PMA6/RA10                |

| 30   | AVDD                                  |

| 31   | AVss                                  |

| 32   | AN8/RPB8/CTED10/RB8                   |

| 33   | AN9/RPB9/CTED4/RB9                    |

| 34   | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 |

| 35   | AN11/PMA12/RB11                       |

| Pin # | Full Pin Name                   |

|-------|---------------------------------|

| 36    | Vss                             |

| 37    | VDD                             |

| 38    | TCK/CTED2/RA1                   |

| 39    | RPF13/RF13                      |

| 40    | RPF12/RF12                      |

| 41    | AN12/PMA11/RB12                 |

| 42    | AN13/PMA10/RB13                 |

| 43    | AN14/RPB14/CTED5/PMA1/RB14      |

| 44    | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 45    | Vss                             |

| 46    | VDD                             |

| 47    | RPD14/RD14                      |

| 48    | RPD15/RD15                      |

| 49    | RPF4/PMA9/RF4                   |

| 50    | RPF5/PMA8/RF5                   |

| 51    | USBID/RF3                       |

| 52    | RPF2/RF2                        |

| 53    | RPF8/RF8                        |

| 54    | VBUS                            |

| 55    | Vusb3v3                         |

| 56    | D-                              |

| 57    | D+                              |

| 58    | SCL2/RA2                        |

| 59    | SDA2/RA3                        |

| 60    | TDI/CTED9/RA4                   |

| 61    | TDO/RA5                         |

| 62    | VDD                             |

| 63    | OSC1/CLKI/RC12                  |

| 64    | OSC2/CLKO/RC15                  |

| 65    | Vss                             |

| 66    | SCL1/RPA14/RA14                 |

| 67    | SDA1/RPA15/RA15                 |

| 68    | RPD8/RTCC/RD8                   |

| 69    | RPD9/RD9                        |

| 70    | RPD10/SCK1/PMCS2/RD10           |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 12.0 "I/O Ports" for more information.

A68

## TABLE 6: PIN NAMES FOR 124-PIN DEVICES

124-PIN VTLA (BOTTOM VIEW)<sup>(1,2,3,4,5)</sup>

A17

B13

B29

Conductive

Thermal Pad

PIC32MX330F064L

PIC32MX350F128L

PIC32MX350F256L

PIC32MX370F512L

A51

A1

Polarity Indicator

| Package<br>Bump # | Full Pin Name                         |

|-------------------|---------------------------------------|

| A1                | No Connect                            |

| A2                | RG15                                  |

| A3                | Vss                                   |

| A4                | AN23/PMD6/RE6                         |

| A5                | RPC1/RC1                              |

| A6                | RPC3/RC3                              |

| A7                | AN16/C1IND/RPG6/SCK2/PMA5/RG6         |

| A8                | AN18/C2IND/RPG8/PMA3/RG8              |

| A9                | AN19/C2INC/RPG9/PMA2/RG9              |

| A10               | VDD                                   |

| A11               | RPE8/RE8                              |

| A12               | AN5/C1INA/RPB5/RB5                    |

| A13               | PGED3/AN3/C2INA/RPB3/RB3              |

| A14               | VDD                                   |

| A15               | PGEC1/AN1/RPB1/CTED12/RB1             |

| A16               | No Connect                            |

| A17               | No Connect                            |

| A18               | No Connect                            |

| A19               | No Connect                            |

| A20               | PGEC2/AN6/RPB6/RB6                    |

| A21               | VREF-/CVREF-/PMA7/RA9                 |

| A22               | AVDD                                  |

| A23               | AN8/RPB8/CTED10/RB8                   |

| A24               | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 |

| A25               | Vss                                   |

| A26               | TCK/CTED2/RA1                         |

| A27               | RPF12/RF12                            |

| A28               | AN13/PMA10/RB13                       |

| A29               | AN15/RPB15/OCFB/CTED6/PMA0/RB15       |

| A30               | VDD                                   |

| A31               | RPD15/RD15                            |

| A32               | RPF5/PMA8/RF5                         |

| A33               | No Connect                            |

| A34               | No Connect                            |

| A35               | RPF3/RF3                              |

| A36               | RPF2/RF2                              |

| A37               | RPF7/RF7                              |

| toi               |                                                                                |  |  |  |  |  |  |  |

|-------------------|--------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| Package<br>Bump # | Full Pin Name                                                                  |  |  |  |  |  |  |  |

| A38               | SDA1/RG3                                                                       |  |  |  |  |  |  |  |

| A39               | SCL2/RA2                                                                       |  |  |  |  |  |  |  |

| A40               | TDI/CTED9/RA4                                                                  |  |  |  |  |  |  |  |

| A41               | VDD                                                                            |  |  |  |  |  |  |  |

| A42               | OSC2/CLKO/RC15                                                                 |  |  |  |  |  |  |  |

| A43               | Vss                                                                            |  |  |  |  |  |  |  |

| A44               | RPA15/RA15                                                                     |  |  |  |  |  |  |  |

| A45               | RPD9/RD9                                                                       |  |  |  |  |  |  |  |

| A46               | RPD11/PMCS1/RD11                                                               |  |  |  |  |  |  |  |

| A47               | SOSCI/RPC13/RC13                                                               |  |  |  |  |  |  |  |

| A48               | VDD                                                                            |  |  |  |  |  |  |  |

| A49               | No Connect                                                                     |  |  |  |  |  |  |  |

| A50               | No Connect                                                                     |  |  |  |  |  |  |  |

| A51               | No Connect                                                                     |  |  |  |  |  |  |  |

| A52               | AN24/RPD1/RD1                                                                  |  |  |  |  |  |  |  |

| A53               | AN26/RPD3/RD3                                                                  |  |  |  |  |  |  |  |

| A54               | PMD13/RD13                                                                     |  |  |  |  |  |  |  |

| A55               | RPD5/PMRD/RD5                                                                  |  |  |  |  |  |  |  |

| A56               | PMD15/RD7                                                                      |  |  |  |  |  |  |  |

| A57               | No Connect                                                                     |  |  |  |  |  |  |  |

| A58               | No Connect                                                                     |  |  |  |  |  |  |  |

| A59               | VDD                                                                            |  |  |  |  |  |  |  |

| A60               | RPF1/PMD10/RF1                                                                 |  |  |  |  |  |  |  |

| A61               | RPG0/PMD8/RG0                                                                  |  |  |  |  |  |  |  |

| A62               | TRD3/CTED8/RA7                                                                 |  |  |  |  |  |  |  |

| A63               | Vss                                                                            |  |  |  |  |  |  |  |

| A64               | PMD1/RE1                                                                       |  |  |  |  |  |  |  |

| A65               | TRD1/RG12                                                                      |  |  |  |  |  |  |  |

| A66               | AN20/PMD2/RE2                                                                  |  |  |  |  |  |  |  |

| A67               | AN21/PMD4/RE4                                                                  |  |  |  |  |  |  |  |

| A68               | No Connect                                                                     |  |  |  |  |  |  |  |

| B1                | VDD                                                                            |  |  |  |  |  |  |  |

| B2                | AN22/RPE5/PMD5/RE5                                                             |  |  |  |  |  |  |  |

| B3                | AN27/PMD7/RE7                                                                  |  |  |  |  |  |  |  |

| B4                | RPC2/RC2                                                                       |  |  |  |  |  |  |  |

| B5                | RPC4/CTED7/RC4                                                                 |  |  |  |  |  |  |  |

| B6                | AN17/C1INC/RPG7/PMA4/RG7 vailable peripherals and Section 12.3 "Peripheral Pin |  |  |  |  |  |  |  |

- Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RAx-RGx), with the exception of RF6, can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

- 3: RPF6 (bump B30) and RPF7 (bump A37) are only remappable for input functions.

- 4: Shaded package bumps are 5V tolerant.

- 5: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

## **Table of Contents**

| 1.0  | Device Overview                                    | 17  |

|------|----------------------------------------------------|-----|

| 2.0  | Guidelines for Getting Started with 32-bit MCUs    |     |

| 3.0  | CPU.                                               |     |

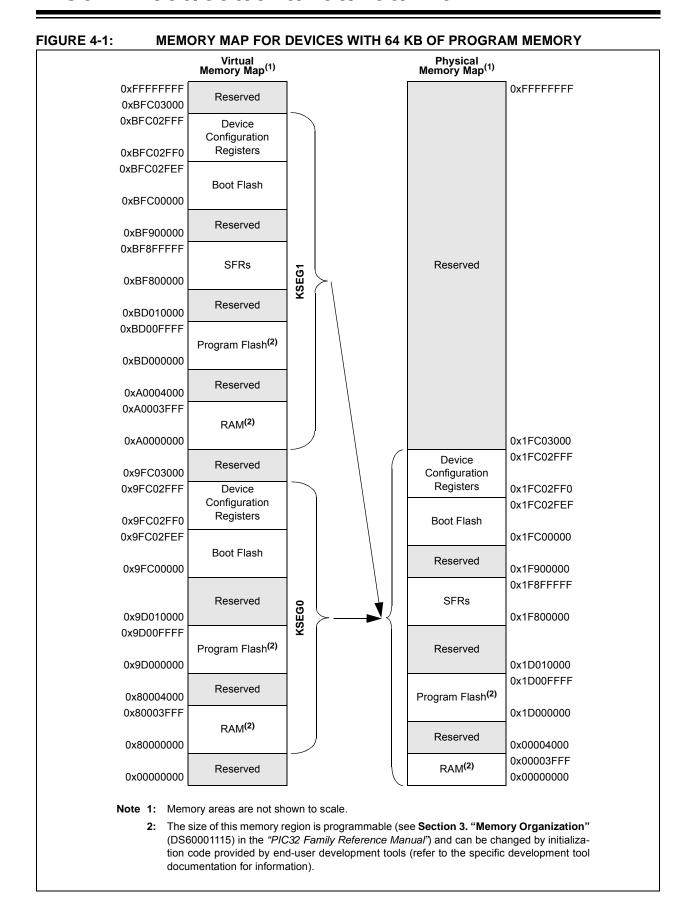

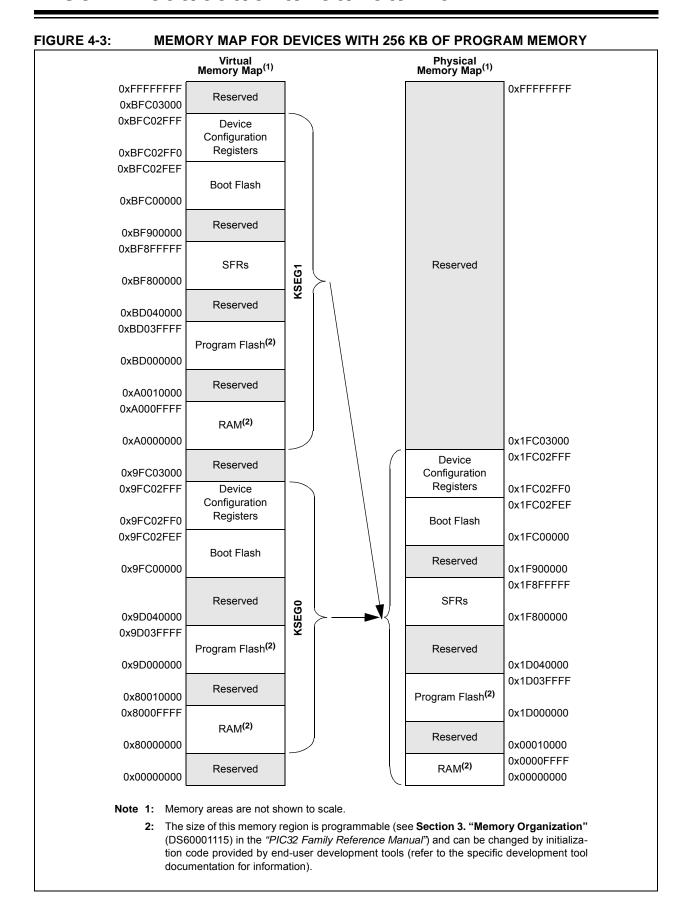

| 4.0  | Memory Organization                                |     |

| 5.0  | Flash Program Memory                               |     |

| 6.0  | Resets                                             |     |

| 7.0  | Interrupt Controller                               |     |

| 8.0  | Oscillator Configuration                           |     |

| 9.0  | Prefetch Cache                                     |     |

| 10.0 | Direct Memory Access (DMA) Controller              |     |

| 11.0 | USB On-The-Go (OTG)                                | 113 |

|      | I/O Ports                                          |     |

| 13.0 | Timer1                                             | 167 |

| 14.0 | Timer2/3, Timer4/5                                 | 171 |

|      | Watchdog Timer (WDT)                               |     |

|      | Input Capture                                      |     |

| 17.0 | Output Compare                                     | 185 |

| 18.0 | Serial Peripheral Interface (SPI)                  | 189 |

| 19.0 | Inter-Integrated Circuit (I <sup>2</sup> C)        | 197 |

| 20.0 | Universal Asynchronous Receiver Transmitter (UART) | 205 |

| 21.0 | Parallel Master Port (PMP)                         | 213 |

| 22.0 | Real-Time Clock and Calendar (RTCC)                | 223 |

| 23.0 | 10-bit Analog-to-Digital Converter (ADC)           | 233 |

|      | Comparator                                         |     |

| 25.0 | Comparator Voltage Reference (CVREF)               | 247 |

| 26.0 | Charge Time Measurement Unit (CTMU)                | 251 |

| 27.0 | Power-Saving Features                              | 257 |

| 28.0 | Special Features                                   | 261 |

|      | Instruction Set                                    |     |

| 30.0 | Development Support                                | 275 |

|      | Electrical Characteristics                         |     |

|      | DC and AC Device Characteristics Graphs            |     |

|      | Packaging Information                              |     |

|      | Microchip Web Site                                 |     |

|      | omer Change Notification Service                   |     |

| Cust | omer Support                                       | 359 |

| Prod | uct Identification System                          | 360 |

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### **Errata**

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- · Microchip's Worldwide Web site; http://www.microchip.com

- · Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                        | er                       |                                                     |             |                |                                                                              |  |  |

|----------|------------------------|--------------------------|-----------------------------------------------------|-------------|----------------|------------------------------------------------------------------------------|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP          | 124-pin<br>VTLA                                     | Pin<br>Type | Buffer<br>Type | Description                                                                  |  |  |

| CTED4    | 22                     | 33                       | B19                                                 | I           | ST             | CTMU External Edge Input 4                                                   |  |  |

| CTED5    | 29                     | 43                       | B24                                                 | I           | ST             | CTMU External Edge Input 5                                                   |  |  |

| CTED6    | 30                     | 44                       | A29                                                 | I           | ST             | CTMU External Edge Input 6                                                   |  |  |

| CTED7    | _                      | 9                        | B5                                                  | I           | ST             | CTMU External Edge Input 7                                                   |  |  |

| CTED8    | _                      | 92                       | A62                                                 | I           | ST             | CTMU External Edge Input 8                                                   |  |  |

| CTED9    | _                      | 60                       | A40                                                 | I           | ST             | CTMU External Edge Input 9                                                   |  |  |

| CTED10   | 21                     | 32                       | A23                                                 | I           | ST             | CTMU External Edge Input 10                                                  |  |  |

| CTED11   | 23                     | 34                       | A24                                                 | I           | ST             | CTMU External Edge Input 11                                                  |  |  |

| CTED12   | 15                     | 24                       | A15                                                 | I           | ST             | CTMU External Edge Input 12                                                  |  |  |

| CTED13   | 14                     | 23                       | B13                                                 | I           | ST             | CTMU External Edge Input 13                                                  |  |  |

| MCLR     | 7                      | 13                       | В7                                                  | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device.   |  |  |

| AVDD     | 19                     | 30                       | A22                                                 | Р           | Р              | Positive supply for analog modules. This pin must be connected at all times. |  |  |

| AVss     | 20                     | 31                       | B18                                                 | Р           | Р              | Ground reference for analog modules                                          |  |  |

| VDD      | 10, 26, 38,<br>57      | 2, 16, 37,<br>46, 62, 86 | B1, A10, A14,<br>B21, A30,<br>A41, A48,<br>A59, B53 | Р           | _              | Positive supply for peripheral logic and I/O pins                            |  |  |

| VCAP     | 56                     | 85                       | B48                                                 | Р           |                | Capacitor for Internal Voltage Regulator                                     |  |  |

| Vss      | 9, 25, 41              | 15, 36, 45,<br>65, 75    | A3, B8, B12,<br>A25, B25,<br>A43, B41,<br>A63       | Р           | _              | Ground reference for logic and I/O pins                                      |  |  |

| VREF+    | 16                     | 29                       | B17                                                 | I           | Analog         | Analog Voltage Reference (High) Input                                        |  |  |

| VREF-    | 15                     | 28                       | A21                                                 | ı           | Analog         | Analog Voltage Reference (Low) Input                                         |  |  |

**Legend:** CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

TTL = TTL input buffer

Analog = Analog input

O = Output

P = Power I = Input

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices.

REGISTER 9-6: CHEW1: CACHE WORD 1

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31.24        | CHEW1<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 22:46        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        | CHEW1<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | CHEW1<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          |                   |                   |                   | CHEW1             | <7:0>             |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

### REGISTER 9-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        | CHEW2<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        | CHEW2<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | CHEW2<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

|              |                   |                   |                   | CHEW2             | <7:0>             |                   |                  |                  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

#### REGISTER 10-2: DMASTAT: DMA STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | -                 | -                 | _                 | _                 | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

|              | _                 | _                 | _                 | _                 | RDWR              | DMACH<2:0>        |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-4 **Unimplemented:** Read as '0' bit 3 **RDWR:** Read/Write Status bit

1 = Last DMA bus access was a read0 = Last DMA bus access was a write

bit 2-0 DMACH<2:0>: DMA Channel bits

These bits contain the value of the most recent active DMA channel.

### REGISTER 10-3: DMAADDR: DMA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 31:24        |                   | DMAADDR<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |

| 22.40        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23:16        | DMAADDR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 15:8         | DMAADDR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

|              |                   |                   |                   | DMAADD            | R<7:0>            |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-0 DMAADDR<31:0>: DMA Module Address bits

These bits contain the address of the most recent DMA access.

#### REGISTER 11-1: U10TGIR: USB OTG INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 |                   | -                 | -                 | -                 | _                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | -                 |                   | -                 | -                 | -                 | _                 | -                | _                |

| 7.0          | R/WC-0, HS        | U-0              | R/WC-0, HS       |

| 7:0          | IDIF              | T1MSECIF          | LSTATEIF          | ACTVIF            | SESVDIF           | SESENDIF          | _                | VBUSVDIF         |

**Legend:** WC = Write '1' to clear HS = Hardware Settable bit

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 IDIF: ID State Change Indicator bit

1 = Change in ID state is detected

0 = No change in ID state is detected

bit 6 T1MSECIF: 1 Millisecond Timer bit

1 = 1 millisecond timer has expired

0 = 1 millisecond timer has not expired

bit 5 LSTATEIF: Line State Stable Indicator bit

1 = USB line state has been stable for 1millisecond, but different from last time

0 = USB line state has not been stable for 1 millisecond

bit 4 ACTVIF: Bus Activity Indicator bit

1 = Activity on the D+, D-, ID or VBUS pins has caused the device to wake-up

0 = Activity has not been detected

bit 3 **SESVDIF:** Session Valid Change Indicator bit

1 = VBUS voltage has dropped below the session end level

0 = VBUS voltage has not dropped below the session end level

bit 2 SESENDIF: B-Device VBUS Change Indicator bit

1 = A change on the session end input was detected

0 = No change on the session end input was detected

bit 1 Unimplemented: Read as '0'

bit 0 **VBUSVDIF:** A-Device VBUS Change Indicator bit

1 = Change on the session valid input is detected

0 = No change on the session valid input is detected

#### REGISTER 11-5: U1PWRC: USB POWER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0 U-0           |                        | U-0               | U-0              | U-0              |

| 31.24        | _                 | -                 | -                 | _                 |                        | 1                 | _                |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |

| 7:0          | UACTPND           | _                 | _                 | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 **UACTPND:** USB Activity Pending bit

1 = USB bus activity has been detected; but an interrupt is pending, it has not been generated yet

0 = An interrupt is not pending

bit 6-5 **Unimplemented:** Read as '0'

bit 4 USLPGRD: USB Sleep Entry Guard bit

1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

0 = USB module does not block Sleep entry

bit 3 **USBBUSY:** USB Module Busy bit<sup>(1)</sup>

1 = USB module is active or disabled, but not ready to be enabled

0 = USB module is not active and is ready to be enabled

**Note:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all

USB module registers produce undefined results.

bit 2 Unimplemented: Read as '0'

bit 1 USUSPEND: USB Suspend Mode bit

1 = USB module is placed in Suspend mode

(The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

0 = USB module operates normally

bit 0 USBPWR: USB Operation Enable bit

1 = USB module is turned on

0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

© 2012-2016 Microchip Technology Inc.

TABLE 12-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| SS                          |                       |               |             | Bits  |            |            |       |       |            |            |      |      |      |      |      |           |        |      |            |

|-----------------------------|-----------------------|---------------|-------------|-------|------------|------------|-------|-------|------------|------------|------|------|------|------|------|-----------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15       | 30/14 | 29/13      | 28/12      | 27/11 | 26/10 | 25/9       | 24/8       | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2      | 17/1   | 16/0 | All Resets |

| FB90                        | RPC4R <sup>(1)</sup>  | 31:16         |             | _     | _          | _          |       | _     | _          | _          | _    |      |      | _    |      | _         | _      | _    | 0000       |

| 1 500                       | 141 0 111             | 15:0          |             | _     | _          |            |       | _     |            |            |      |      | _    | _    |      | RPC4      | <3:0>  |      | 0000       |

| FBB4                        | RPC13R                | 31:16         | _           | _     | _          |            |       | _     |            | _          | _    | _    |      | _    | _    |           | _      | _    | 0000       |

|                             | 0.0                   | 15:0          | _           | _     | _          | _          | _     | _     | _          | _          | _    | _    | _    | _    |      | RPC1:     | 3<3:0> |      | 0000       |

| FBB8                        | RPC14R                | 31:16         | _           | _     | _          |            |       | _     |            | _          |      | _    |      | _    | _    | _         |        | _    | 0000       |

|                             |                       | 15:0          |             | _     | _          |            |       | _     |            |            |      |      |      | _    |      | RPC1      | 4<3:0> |      | 0000       |

| FBC0                        | RPD0R                 | 31:16<br>15:0 | _           | _     | _          | _          | _     | _     | _          | _          | _    | _    | _    | _    | _    | RPD0      |        | _    | 0000       |

|                             |                       | 31:16         |             | _     | _          | _          | _     | _     |            |            |      |      |      | _    |      | RPDU      | ×3.0>  | _    | 0000       |

| FBC4                        | RPD1R                 | 15:0          |             |       | _          |            | _     |       |            |            |      |      |      | _    | -    | RPD1      | <3:0>  | _    | 0000       |

|                             |                       | 31:16         |             |       |            |            |       |       |            |            |      |      |      |      | _    | KFD1      | -5.02  | _    | 0000       |

| FBC8                        | RPD2R                 | 15:0          | _           | _     | _          |            |       | _     |            |            |      |      |      | _    |      | RPD2      | 2<3:0> |      | 0000       |

|                             |                       | 31:16         | _           | _     | _          |            |       | _     |            | _          |      | _    |      | _    | _    | —         | _      | _    | 0000       |

| FBCC                        | RPD3R                 | 15:0          | _           | _     | _          | _          |       | _     | _          | _          |      | _    | _    | _    |      | RPD3      | <3:0>  |      | 0000       |

|                             |                       | 31:16         | _           | _     | _          | _          | _     | _     | _          | _          | _    | _    | _    | _    | _    | _         | _      | _    | 0000       |

| FBD0                        | RPD4R                 | 15:0          | _           | _     | _          | _          | _     | _     | _          | _          | _    | _    |      | _    |      | RPD4      | <3:0>  |      | 0000       |

| EDD4                        | DDDED                 | 31:16         | _           | _     | _          | _          | _     | _     | _          | _          | _    | _    | _    | _    | _    | _         | _      | _    | 0000       |

| FBD4                        | RPD5R                 | 15:0          | -           | _     | _          | _          | _     | _     | _          | _          | _    | -    | _    | _    |      | RPD5      | <3:0>  |      | 0000       |

| FBE0                        | RPD8R                 | 31:16         |             | _     | _          | _          | _     | _     | _          | _          | _    |      | ı    | _    | Ī    |           | _      | _    | 0000       |

| FBEU                        | KPDOK                 | 15:0          |             | _     | _          | _          | -     | _     | _          |            | _    |      | _    | _    |      | RPD8      | <3:0>  |      | 0000       |

| FBE4                        | RPD9R                 | 31:16         | _           | _     | _          | _          | _     | _     | _          | _          | _    | _    | _    | _    | _    | _         | _      | _    | 0000       |

| 1 DL4                       | IXI Daix              | 15:0          |             | _     | _          | _          | _     | _     | _          | _          | _    |      | _    | _    |      | RPD9      | <3:0>  |      | 0000       |

| FBE8                        | RPD10R                | 31:16         |             | _     | _          |            |       | _     |            |            |      |      |      | _    | _    |           |        | _    | 0000       |

| . 520                       | 5                     | 15:0          | _           | _     | _          |            |       | _     |            | _          | _    | _    |      | _    |      | RPD1      | 0<3:0> |      | 0000       |

| FBEC                        | RPD11R                | 31:16         | _           | _     | _          | _          | _     | _     | _          | _          | _    | _    | _    | _    | _    |           |        | _    | 0000       |

|                             |                       | 15:0          |             | _     | _          |            |       |       |            |            |      |      |      | _    |      | RPD1      | 1<3:0> |      | 0000       |

| FBF0                        | RPD12R <sup>(1)</sup> | 31:16         |             | _     | _          |            |       | _     |            |            |      |      |      | _    | _    | —<br>DDD4 | -      | _    | 0000       |

|                             |                       | 15:0          |             | _     | _          |            | _     | _     |            | _          |      | _    | -    | _    |      | RPD1:     | 2<3:0> |      | 0000       |

| FBF8                        | RPD14R <sup>(1)</sup> | 31:16<br>15:0 |             |       |            |            |       |       |            |            |      |      |      | _    | _    | RPD1      | 1<3:0> | _    | 0000       |

|                             |                       | 31:16         |             |       |            |            |       |       |            |            |      |      |      |      |      | ררטוי     | +>3.0/ | _    | 0000       |

| FBFC                        | RPD15R <sup>(1)</sup> | 15:0          | _           | _     | _          |            |       |       |            |            |      |      |      | _    | _    | RPD1      | 5<3:0> | _    | 0000       |

| -                           |                       | 31:16         |             |       |            |            |       |       |            |            |      |      |      |      | _    | _         |        | _    | 0000       |

| FC0C                        | RPE3R                 | 15:0          |             | _     | _          | _          |       | _     | _          | _          |      | _    |      |      |      | RPE3      | <3:0>  |      | 0000       |

| Logondu                     |                       |               | roluo on Bo |       | nimplement | od road or |       |       | chown in h | ovadaaimal |      |      |      |      |      | IN LO     |        |      | 3000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

This register is not available on 64-pin devices.

This register is only available on devices without a USB module.

This register is not available on 64-pin devices with a USB module.

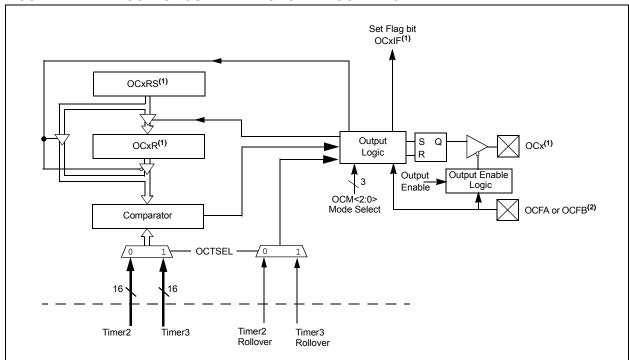

### 17.0 OUTPUT COMPARE

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 16. "Output Compare"** (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are key features of this module:

- · Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- · Single and Dual Compare modes

- Single and continuous output pulse generation

- · Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

#### FIGURE 17-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

- **Note 1:** Where 'x' is shown, reference is made to the registers associated with the respective output compare channels, 1 through 5.

- 2: The OCFA pin controls the OC1-OC4 channels. The OCFB pin controls the OC5 channel.

### **REGISTER 18-1: SPIXCON: SPI CONTROL REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 31:24        | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31.24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN             | FRMSYPW           | FRMCNT<2:0>       |                  | >                     |

| 22:46        | R/W-0                  | U-0                | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |

| 23:16        | MCLKSEL <sup>(2)</sup> | _                  | _                 | _                 | _                 | _                 | SPIFE            | ENHBUF <sup>(2)</sup> |

| 15:0         | R/W-0                  | U-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | ON <sup>(1)</sup>      | _                  | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |

| 7:0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

|              | SSEN                   | CKP <sup>(4)</sup> | MSTEN             | DISSDI            | STXISE            | L<1:0>            | SRXISEL<1:0>     |                       |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FRMEN: Framed SPI Support bit

1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

0 = Framed SPI support is disabled

bit 30 FRMSYNC: Frame Sync Pulse Direction Control on SSx pin bit (Framed SPI mode only)

1 = Frame sync pulse input (Slave mode)

0 = Frame sync pulse output (Master mode)

bit 29 **FRMPOL:** Frame Sync Polarity bit (Framed SPI mode only)

1 = Frame pulse is active-high

0 = Frame pulse is active-low

bit 28 MSSEN: Master Mode Slave Select Enable bit

1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

0 = Slave select SPI support is disabled.

bit 27 FRMSYPW: Frame Sync Pulse Width bit

1 = Frame sync pulse is one character wide

0 = Frame sync pulse is one clock wide

bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in FRAMED\_SYNC mode.

111 = Reserved; do not use

110 = Reserved; do not use

101 = Generate a frame sync pulse on every 32 data characters

100 = Generate a frame sync pulse on every 16 data characters

011 = Generate a frame sync pulse on every 8 data characters

010 = Generate a frame sync pulse on every 4 data characters

001 = Generate a frame sync pulse on every 2 data characters

000 = Generate a frame sync pulse on every data character **MCLKSEL**: Master Clock Enable bit<sup>(2)</sup>

1 = REFCLK is used by the Baud Rate Generator

0 = PBCLK is used by the Baud Rate Generator

bit 22-18 Unimplemented: Read as '0'

bit 23

**Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: This bit can only be written when the ON bit = 0.

3: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

**4:** When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

#### REGISTER 22-1: RTCCON: RTC CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------------|------------------|--|--|--|

| 31:24        | U-0                     | U-0               | U-0               | U-0               | U-0                    | U-0               | R/W-0                  | R/W-0            |  |  |  |

| 31.24        | _                       |                   |                   | _                 |                        |                   | CAL<9:8>               |                  |  |  |  |

| 23:16        | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0             | R/W-0                  | R/W-0            |  |  |  |

| 23.10        | CAL<7:0>                |                   |                   |                   |                        |                   |                        |                  |  |  |  |

| 15:8         | R/W-0                   | U-0               | R/W-0             | U-0               | U-0                    | U-0               | U-0                    | U-0              |  |  |  |

| 15.6         | ON <sup>(1,2)</sup>     | _                 | SIDL              | _                 | _                      | _                 | _                      | _                |  |  |  |

| 7:0          | R/W-0                   | R-0               | U-0               | U-0               | R/W-0                  | R-0               | R-0                    | R/W-0            |  |  |  |

| 7:0          | RTSECSEL <sup>(3)</sup> | RTCCLKON          | _                 | _                 | RTCWREN <sup>(4)</sup> | RTCSYNC           | HALFSEC <sup>(5)</sup> | RTCOE            |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-26 Unimplemented: Read as '0'

bit 25-16 CAL<9:0>: RTC Drift Calibration bits, which contain a signed 10-bit integer value

0111111111 = Maximum positive adjustment, adds 511 RTC clock pulses every one minute

•

000000001 = Minimum positive adjustment, adds 1 RTC clock pulse every one minute

0000000000 = No adjustment

1111111111 = Minimum negative adjustment, subtracts 1 RTC clock pulse every one minute

•

100000000 = Maximum negative adjustment, subtracts 512 clock pulses every one minute

bit 15 **ON:** RTCC On bit<sup>(1,2)</sup>

1 = RTCC module is enabled

0 = RTCC module is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Disables the PBCLK to the RTCC when CPU enters in Idle mode

0 = Continue normal operation in Idle mode

bit 12-8 Unimplemented: Read as '0'

bit 7 RTSECSEL: RTCC Seconds Clock Output Select bit<sup>(3)</sup>

1 = RTCC Seconds Clock is selected for the RTCC pin

0 = RTCC Alarm Pulse is selected for the RTCC pin

bit 6 RTCCLKON: RTCC Clock Enable Status bit

1 = RTCC Clock is actively running

0 = RTCC Clock is not running

bit 5-4 **Unimplemented:** Read as '0'

**Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **3:** Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- **4:** The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is reset only on a Power-on Reset (POR).

### REGISTER 22-1: RTCCON: RTC CONTROL REGISTER (CONTINUED)

- bit 3 RTCWREN: RTC Value Registers Write Enable bit (4)

- 1 = RTC Value registers can be written to by the user

- 0 = RTC Value registers are locked out from being written to by the user

- bit 2 RTCSYNC: RTCC Value Registers Read Synchronization bit

- 1 = RTC Value registers can change while reading, due to a rollover ripple that results in an invalid data read If the register is read twice and results in the same data, the data can be assumed to be valid

- 0 = RTC Value registers can be read without concern about a rollover ripple

- bit 1 HALFSEC: Half-Second Status bit<sup>(5)</sup>

- 1 = Second half period of a second

- 0 = First half period of a second

- bit 0 RTCOE: RTCC Output Enable bit

- 1 = RTCC clock output is enabled clock presented onto an I/O

- 0 = RTCC clock output is disabled

- **Note 1:** The ON bit is only writable when RTCWREN = 1.

- 2: When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active.

- **4:** The RTCWREN bit can be set only when the write sequence is enabled.

- 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

**Note:** This register is reset only on a Power-on Reset (POR).

### REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits(3)

11111111 = Alarm will trigger 256 times

•

00000000 = Alarm will trigger one time

The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- Note 1: Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

**Note:** This register is reset only on a Power-on Reset (POR).

#### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5                       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-----------------------------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.04        | r-0               | r-1               | r-1                                     | R/P               | r-1               | r-1               | r-1              | R/P              |  |

| 31:24        | _                 | _                 | _                                       | CP                | _                 | _                 | _                | BWP              |  |

| 22:40        | r-1               | r-1               | r-1                                     | r-1               | R/P               | R/P               | R/P              | R/P              |  |

| 23:16        | _                 | _                 | _                                       | _                 | PWP<7:4>          |                   |                  |                  |  |

| 45.0         | R/P               | R/P               | R/P                                     | R/P               | r-1               | r-1               | r-1              | r-1              |  |

| 15:8         |                   | PWP<              | <3:0>                                   |                   | _                 | _                 | _                | _                |  |

| 7:0          | r-1 r-1           |                   | r-1                                     | R/P               | R/P               | R/P               | R/P              | R/P              |  |

|              | _                 | _                 | L<1:0> JTAGEN <sup>(1)</sup> DEBUG<1:0> |                   |                   |                   |                  |                  |  |

Legend:r = Reserved bitP = Programmable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31 Reserved: Write '0' bit 30-29 Reserved: Write '1' bit 28 CP: Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device.

1 = Protection is disabled 0 = Protection is enabled

bit 27-25 Reserved: Write '1'

bit 24 BWP: Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable0 = Boot Flash is not writable

bit 23-20 Reserved: Write '1'

bit 19-12 PWP<7:0>: Program Flash Write-Protect bits

Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages.

11111111 = Disabled 111111110 = 0xBD00 0FFF 111111101 = 0xBD00\_1FFF 111111100 = 0xBD00 2FFF 11111011 = 0xBD00 3FFF 11111010 = 0xBD00\_4FFF 11111001 = 0xBD00\_5FFF 11111000 = 0xBD00 6FFF11110111 = 0xBD00\_7FFF 11110110 = 0xBD00 8FFF 11110101 = 0xBD00 9FFF11110100 = 0xBD00\_AFFF 11110011 = 0xBD00\_BFFF 11110010 = 0xBD00 CFFF11110001 = 0xBD00\_DFFF 11110000 = 0xBD00 EFFF11101111 = 0xBD00 FFFF  $011111111 = 0xBD07_FFFF$

**Note 1:** This bit sets the value for the JTAGEN bit in the CFGCON register.

TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

| DC CHA        | ARACTE | ERISTICS                       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                     |                      |       |                                                                          |  |  |  |

|---------------|--------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|-------|--------------------------------------------------------------------------|--|--|--|

| Param.<br>No. | Symb.  | Characteristics                | Min.                                                                                                                                                                                                                                                     | Typ. <sup>(1)</sup> | Max.                 | Units | Conditions                                                               |  |  |  |

|               |        | Input Leakage Current (Note 3) |                                                                                                                                                                                                                                                          |                     |                      |       |                                                                          |  |  |  |

| DI50          | lıL    | I/O Ports                      | _                                                                                                                                                                                                                                                        | _                   | <u>+</u> 1           | μА    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance                               |  |  |  |

| DI51          |        | Analog Input Pins              | _                                                                                                                                                                                                                                                        | _                   | <u>+</u> 1           | μА    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance                               |  |  |  |

| DI55          |        | MCLR(2)                        | _                                                                                                                                                                                                                                                        | _                   | <u>+</u> 1           | μА    | $Vss \leq Vpin \leq Vdd$                                                 |  |  |  |

| DI56          |        | OSC1                           | _                                                                                                                                                                                                                                                        | _                   | <u>+</u> 1           | μА    | VSS ≤ VPIN ≤ VDD,<br>XT and HS modes                                     |  |  |  |

|               |        |                                |                                                                                                                                                                                                                                                          |                     |                      |       | Pins with Analog functions.<br>Exceptions: [N/A] = 0 mA<br>max           |  |  |  |

| DI60a         | licl   | Input Low Injection<br>Current | 0                                                                                                                                                                                                                                                        | _                   | <sub>-5</sub> (7,10) | mA    | Digital 5V tolerant designated pins. Exceptions:<br>[N/A] = 0 mA max     |  |  |  |

|               |        |                                |                                                                                                                                                                                                                                                          |                     |                      |       | Digital non-5V tolerant designated pins. Exceptions:<br>[N/A] = 0 mA max |  |  |  |

- **Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the user-selectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

- 7: VIL source < (Vss 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- **10:** Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS 0.3)).

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ Vsource ≤ (VDD + 0.3), injection current = 0.

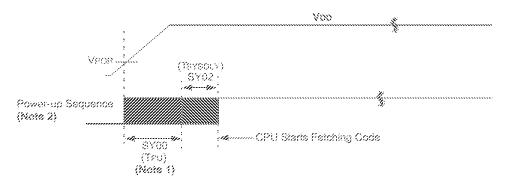

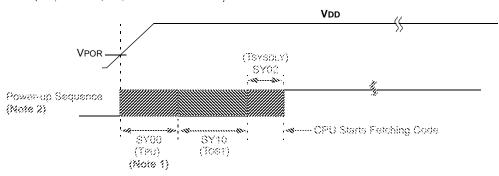

### FIGURE 31-4: POWER-ON RESET TIMING CHARACTERISTICS

Internal Voltage Regulator Enabled

Clock Sources = (FRC, FRCDIV, FRCDIV16, FRCPLL, EC, ECPLL and LPRC)

Internal Voltage Regulator Enabled Clock Sources = (HS, HSPLL, XT, XTPLL and Sosc)

Note 1: The power-up period will be extended if the power-up sequence completes before the device exits from BOR (VDD < VDDMIN).

2: Includes interval voltage regulator stabilization delay.