Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

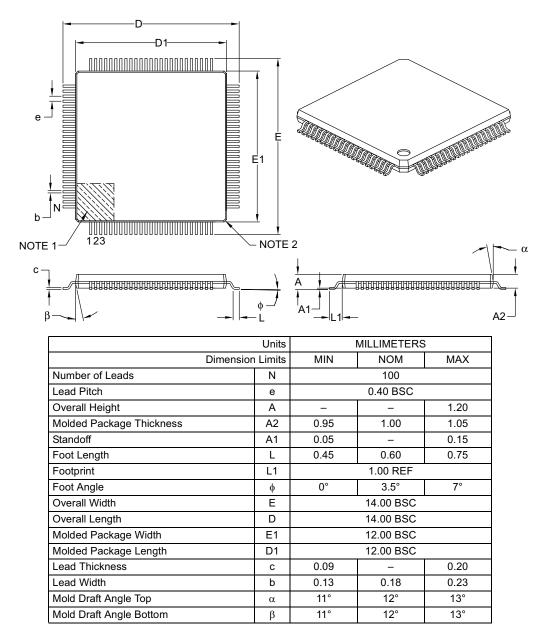

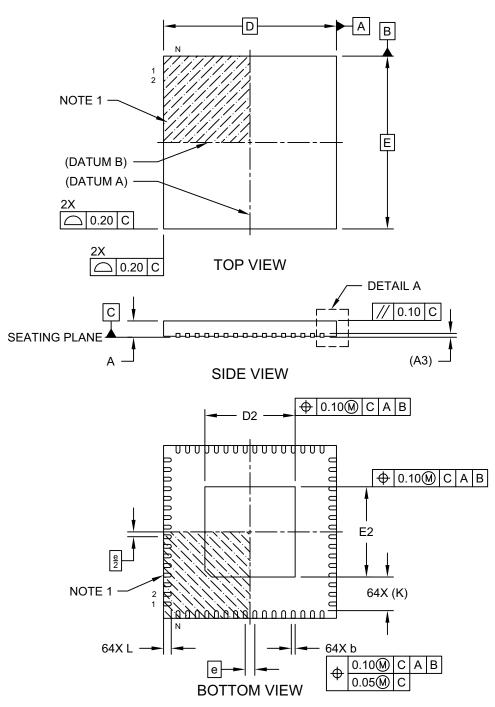

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f256l-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

## 2.1 Basic Connection Requirements

Getting started with the PIC32MX330/350/370/430/ 450/470 family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.8 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

| ILCI01011    |                   |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 |                   | —                 | _                 | —                 |                  | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23:16        | _                 | _                 | —                 | —                 | _                 |                   | _                | SS0              |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | —                 | MVEC              | —                 |                   | TPC<2:0>         |                  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| Logona.           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-17 Unimplemented: Read as '0'

- bit 16 SS0: Single Vector Shadow Register Set bit

- 1 = Single vector is presented with a shadow register set

- 0 = Single vector is not presented with a shadow register set

#### bit 15-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multi Vector Configuration bit

- 1 = Interrupt controller configured for multi vectored mode

- 0 = Interrupt controller configured for single vectored mode

#### bit 11 Unimplemented: Read as '0'

- bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

- 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

- 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

- 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

- 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer 000 = Disables Interrupt Proximity timer

- bit 7-5 **Unimplemented:** Read as '0'

- bit 4 **INT4EP:** External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |

| 15.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | -                 | _                 | _                 | _                 |                   | _                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 |                   |                   | TUN<              | 5:0> <b>(1)</b>   |                  |                  |

## REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

| Legend:           | y = Value set from Configuration bits on POR |                                    |                    |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized nor tested.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 31:24        |                   |                   |                   | CHEW3<            | :31:24>           |                   |                  |                  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 23:16        | CHEW3<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |

| 15:8         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 10.0         | CHEW3<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |

| 7:0          |                   |                   | •                 | CHEW3             | 8<7:0>            |                   |                  |                  |  |

## **REGISTER 9-8:** CHEW3: CACHE WORD 3

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-0 **CHEW3<31:0>:** Word 3 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

Note: This register is a window into the cache data array and is readable only if the device is not code-protected.

### REGISTER 9-9: CHELRU: CACHE LRU REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |  |

| 31.24        | —                 | —                 | -                 | —                 | —                 | -                 | -                | CHELRU<24>       |  |

| 23:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 23.10        | CHELRU<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         |                   |                   |                   | CHELR             | U<15:8>           |                   |                  |                  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |

| 7.0          |                   |                   |                   | CHELF             | RU<7:0>           |                   |                  |                  |  |

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-25 Unimplemented: Write '0'; ignore read

bit 24-0 **CHELRU<24:0>:** Cache Least Recently Used State Encoding bits Indicates the pseudo-LRU state of the cache.

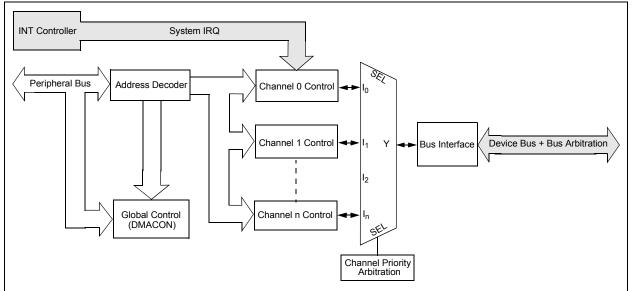

## 10.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32 (such as Peripheral Bus (PBUS) devices: SPI, UART, PMP, etc.) or memory itself.

Following are some of the key features of the DMA controller module:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

## FIGURE 10-1: DMA BLOCK DIAGRAM

## PIC32MX330/350/370/430/450/470

#### REGISTER 11-7: U1IE: USB INTERRUPT ENABLE REGISTER

|              |                   | •                 |                   |                   |                   |                   |                       |                         |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

| 31:24        | U-0                   | U-0                     |

| 31.24        | -                 | —                 | —                 | -                 | —                 | —                 | -                     | —                       |

| 23:16        | U-0                   | U-0                     |

| 23.10        | -                 | —                 | —                 | -                 | —                 | —                 | -                     | —                       |

| 15:8         | U-0                   | U-0                     |

| 15.0         |                   | _                 | —                 | _                 | —                 | _                 | _                     | —                       |

|              | R/W-0                 | R/W-0                   |

| 7:0          | OTALLIE           | ATTACHIE          | RESUMEIE          |                   | TONIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup>   |

|              | STALLIE           | ALIACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SUFIE             | UEKRIE"               | DETACHIE <sup>(3)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | <b>STALLIE:</b> STALL Handshake Interrupt Enable bit<br>1 = STALL interrupt is enabled<br>0 = STALL interrupt is disabled         |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ATTACHIE: ATTACH Interrupt Enable bit<br>1 = ATTACH interrupt is enabled<br>0 = ATTACH interrupt is disabled                      |

| bit 5 | <b>RESUMEIE:</b> RESUME Interrupt Enable bit<br>1 = RESUME interrupt is enabled<br>0 = RESUME interrupt is disabled               |

| bit 4 | IDLEIE: Idle Detect Interrupt Enable bit<br>1 = Idle interrupt is enabled<br>0 = Idle interrupt is disabled                       |

| bit 3 | <b>TRNIE:</b> Token Processing Complete Interrupt Enable bit<br>1 = TRNIF interrupt is enabled<br>0 = TRNIF interrupt is disabled |

| bit 2 | <b>SOFIE:</b> SOF Token Interrupt Enable bit<br>1 = SOFIF interrupt is enabled<br>0 = SOFIF interrupt is disabled                 |

| bit 1 | UERRIE: USB Error Interrupt Enable bit <sup>(1)</sup><br>1 = USB Error interrupt is enabled                                       |

- 1 = USB Error interrupt is enabled 0 = USB Error interrupt is disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt is enabled

- 0 = URSTIF interrupt is disabled

- DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt is enabled

- 0 = DATTCHIF interrupt is disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

- 2: Device mode.

- 3: Host mode.

## 12.4 Control Registers

|                             | PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY |           |               |               |       |       |       |               |              |      |              |              |              |              |              |              |              |              |               |

|-----------------------------|-------------------------------------------------------------------------------------|-----------|---------------|---------------|-------|-------|-------|---------------|--------------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess (                       |                                                                                     | Ð         |               |               |       |       |       |               |              | Bi   | ts           |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup>                                                     | Bit Range | 31/15         | 30/14         | 29/13 | 28/12 | 27/11 | 26/10         | 25/9         | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6000                        | ANSELA                                                                              | 31:16     | —             | —             | —     | —     | _     | —             | —            | _    | —            | —            | —            | _            | —            | —            | —            | _            | 0000          |

| 0000                        | ANOLLA                                                                              | 15:0      | —             | —             | _     | —     | _     | ANSELA10      | ANSELA9      | _    |              | —            | _            | _            | _            |              | _            | _            | 0060          |

| 6010                        | TRISA                                                                               | 31:16     | —             | —             | _     | —     | _     | —             | —            | _    | —            | —            | _            | _            | _            | —            | _            |              | 0000          |

|                             |                                                                                     | 15:0      | TRISA15       | TRISA14       | —     | —     | _     | TRISA10       | TRISA9       | —    | TRISA7       | TRISA6       | TRISA5       | TRISA4       | TRISA3       | TRISA2       | TRISA1       | TRISA0       | xxxx          |

| 6020                        | PORTA                                                                               | 31:16     | —             | —             | _     | —     |       | —             |              |      |              | —            | _            | _            | _            |              | _            | —            | 0000          |

|                             | _                                                                                   | 15:0      | RA15          | RA14          | —     | —     | —     | RA10          | RA9          | —    | RA7          | RA6          | RA5          | RA4          | RA3          | RA2          | RA1          | RA0          | xxxx          |

| 6030                        | LATA                                                                                | 31:16     |               |               | —     | —     | _     | _             |              | _    |              |              | _            |              | —            |              | _            | _            | 0000          |

|                             |                                                                                     | 15:0      | LATA15        | LATA14        | —     | —     | _     | LATA10        | LATA9        | _    | LATA7        | LATA6        | LATA5        | LATA4        | LATA3        | LATA2        | LATA1        | LATA0        | xxxx          |

| 6040                        | ODCA                                                                                | 31:16     |               |               | —     | —     | _     | _             |              | _    |              |              | _            |              | —            |              | _            | _            | 0000          |

|                             |                                                                                     | 15:0      | ODCA15        | ODCA14        | _     | —     | _     | ODCA10        | ODCA9        | _    | ODCA7        | ODCA6        | ODCA5        | ODCA4        | ODCA3        | ODCA2        | ODCA1        | ODCA0        | xxxx          |

| 6050                        | CNPUA                                                                               | 31:16     | —             | —             | _     | —     | _     | —             | —            | _    | —            | —            | —            | _            | —            | —            | —            | —            | 0000          |

|                             |                                                                                     |           | CNPUA15       | CNPUA14       |       |       | _     | CNPUA10       | CNPUA9       | _    | CNPUA7       | CNPUA6       | CNPUA5       | CNPUA4       | CNPUA3       | CNPUA2       | CNPUA1       | CNPUA0       | _             |

| 6060                        | CNPDA                                                                               | 31:16     |               | —             |       | —     |       |               | —            |      |              | —            | —            |              | —            | —            | —            | —            | 0000          |

|                             |                                                                                     |           | CNPDA15       | -             | _     | —     | _     | CNPDA10       | CNPDA9       |      | CNPDA7       | CNPDA6       | CNPDA5       | CNPDA4       | CNPDA3       | CNPDA2       | CNPDA1       | CNPDA0       |               |

| 6070                        | CNCONA                                                                              | 31:16     | -             |               | -     |       |       | —             | _            |      | _            | —            |              | _            |              | _            |              | _            | 0000          |

|                             |                                                                                     | 15:0      | ON            |               | SIDL  | —     |       | —             |              |      |              |              |              | _            |              | _            |              | _            | 0000          |

| 6080                        | CNENA                                                                               | 31:16     |               |               |       |       |       |               |              |      |              |              |              |              |              | -            |              |              | 0000          |

|                             |                                                                                     | 15:0      | CNIEA15       |               |       |       |       | CNIEA10       | CNIEA9       |      | CNIEA7       | CNIEA6       | CNIEA5       | CNIEA4       | CNIEA3       | CNIEA2       | CNIEA1       | CNIEA0       | XXXX          |

| 6090                        | CNSTATA                                                                             | 31:16     |               |               |       | _     | _     |               |              |      |              |              |              |              |              |              |              |              | 0000          |

| 0000                        | CHOININ                                                                             | 15:0      | CN<br>STATA15 | CN<br>STATA14 | -     | —     | —     | CN<br>STATA10 | CN<br>STATA9 |      | CN<br>STATA7 | CN<br>STATA6 | CN<br>STATA5 | CN<br>STATA4 | CN<br>STATA3 | CN<br>STATA2 | CN<br>STATA1 | CN<br>STATA0 | xxxx          |

## TABLE 12-3:PORTA REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,<br/>PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

## TABLE 12-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                       |               |       |       |       |       |       |       |      | Bi   | its  |      |      |      |      |           |             |      |            |

|-----------------------------|-----------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-----------|-------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2      | 17/1        | 16/0 | All Resets |

| FB90                        | RPC4R <sup>(1)</sup>  | 31:16<br>15:0 |       |       |       | _     |       | _     |      |      |      | _    |      |      | —    | —<br>RPC4 | —<br><3:0>  | —    | 0000       |

| FBB4                        | RPC13R                | 31:16         | _     | —     |       |       |       |       | _    |      |      | _    | —    | _    | —    | —         | _           |      | 0000       |

| 1001                        |                       | 15:0          | _     |       | _     |       |       | _     |      | _    | _    | _    | —    | _    |      | RPC1      |             |      | 0000       |

| FBB8                        | RPC14R                | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      |      |      |      | RPC1      | —<br>4<3:0> | -    | 0000       |

| FBC0                        | RPD0R                 | 31:16         | —     | —     | —     | —     | _     | —     | —    | _    | —    | —    | —    | —    | —    |           |             | —    | 0000       |

| 1 000                       | IN DOIN               | 15:0<br>31:16 |       |       | _     | _     |       | _     | _    |      |      | _    |      | _    | _    | RPDO      | )<3:0>      | _    | 0000       |

| FBC4                        | RPD1R                 | 15:0          |       |       |       |       |       |       | _    |      |      |      | _    |      | _    | RPD1      | <3:0>       | —    | 0000       |

| FBC8                        | RPD2R                 | 31:16         | _     | -     | —     | —     | _     | —     | —    | _    | _    | —    | —    | —    | —    | —         | —           | —    | 0000       |

| FBC0                        | RPDZR                 | 15:0          | _     | —     | —     | —     | —     | —     | _    | —    | _    | —    | _    | —    |      | RPD2      | 2<3:0>      |      | 0000       |

| FBCC                        | RPD3R                 | 31:16<br>15:0 |       |       | _     | _     |       | _     |      |      |      | _    |      | _    | —    | RPD3      | —<br><3·0>  | _    | 0000       |

|                             |                       | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | — —       | _           |      | 0000       |

| FBD0                        | RPD4R                 | 15:0          | _     | —     |       | —     | _     |       | —    | —    | _    |      | —    |      |      | RPD4      | <3:0>       |      | 0000       |

| FBD4                        | RPD5R                 | 31:16         | _     | —     | —     | —     | —     | —     | _    | —    |      | —    | _    | —    | —    | —         | _           | —    | 0000       |

| TDD4                        |                       | 15:0          |       |       |       |       | _     |       |      | —    |      |      | _    |      |      | RPD5      | 5<3:0>      |      | 0000       |

| FBE0                        | RPD8R                 | 31:16<br>15:0 | -     |       |       |       |       | _     |      |      |      |      |      |      |      | PPD8      | —<br>3<3:0> |      | 0000       |

|                             |                       | 31:16         |       |       |       |       |       |       |      |      |      |      | _    |      | _    | — —       |             | _    | 0000       |

| FBE4                        | RPD9R                 | 15:0          | _     | —     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPDS      | <3:0>       |      | 0000       |

| FBE8                        | RPD10R                | 31:16         | _     | —     | —     | _     | —     | —     | _    | —    | _    | _    | _    | _    | —    | —         | _           | _    | 0000       |

| TDEO                        |                       | 15:0          |       |       |       |       | _     |       | —    | —    |      |      | —    |      |      | RPD1      | 0<3:0>      |      | 0000       |

| FBEC                        | RPD11R                | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      |      |      | —    | RPD1      | —<br>1<3:0> | —    | 0000       |

| 5550                        |                       | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | —         | _           |      | 0000       |

| FBF0                        | RPD12R <sup>(1)</sup> | 15:0          |       | _     | —     | —     |       | —     | —    | —    |      | —    | _    | —    |      | RPD1      | 2<3:0>      |      | 0000       |

| FBF8                        | RPD14R <sup>(1)</sup> | 31:16         | _     | —     | —     | —     | —     | —     | _    | —    |      | —    | _    | —    | —    | —         | _           | —    | 0000       |

| . 5. 0                      |                       | 15:0          |       | -     |       | —     | —     |       | —    | —    | _    |      | —    |      |      | RPD1      | 4<3:0>      |      | 0000       |

| FBFC                        | RPD15R <sup>(1)</sup> | 31:16<br>15:0 | -     | -     | _     | _     | -     | _     | _    |      |      | _    | _    | _    | —    | RPD1      | —<br>5<3:0> | —    | 0000       |

| 5000                        | DDEAD                 | 31:16         | _     | -     | —     | —     | _     | —     | _    | _    | _    | —    | _    | —    | —    | _         | _           | —    | 0000       |

| FC0C                        | RPE3R                 | 15:0          |       |       |       | —     | _     |       | —    | —    | _    |      | _    |      |      | RPE3      | <3:0>       |      | 0000       |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is only available on devices without a USB module.

3: This register is not available on 64-pin devices with a USB module.

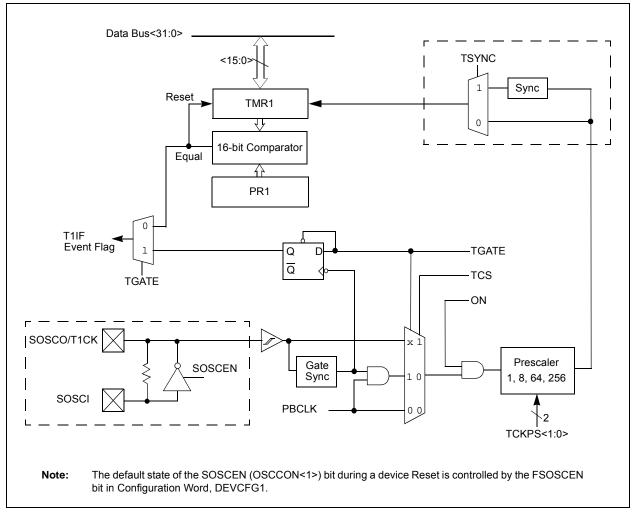

## 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a freerunning interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (SOSC) for Real-Time Clock (RTC) applications. The following modes are supported:

- Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

### 13.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

## PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|--|--|--|--|

| 31:24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |  |

| 31.24        | —                    |                   |                     |                   | —                  |                   | -                  | _                |  |  |  |  |

| 00.40        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |  |

| 23:16        | —                    | -                 | —                   | —                 | —                  | —                 | —                  | —                |  |  |  |  |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |  |

| 15:8         | ON <sup>(1,3)</sup>  | _                 | SIDL <sup>(4)</sup> | _                 | —                  | _                 | _                  | —                |  |  |  |  |

| 7.0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |  |  |  |  |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(          | 3)                | T32 <sup>(2)</sup> |                   | TCS <sup>(3)</sup> | _                |  |  |  |  |

#### REGISTER 14-1: TxCON: TYPE B TIMER CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1,3)</sup>

- 1 = Module is enabled

- 0 = Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit<sup>(4)</sup>

- 1 = Discontinue operation when device enters Idle mode0 = Continue operation even in Idle mode

#### bit 12-8 Unimplemented: Read as '0'

- bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

- When TCS = 1:

This bit is ignored and is read as '0'.

When TCS = 0:

- 1 = Gated time accumulation is enabled

- 0 = Gated time accumulation is disabled

#### bit 6-4 TCKPS<2:0>: Timer Input Clock Prescale Select bits<sup>(3)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

- 000 = 1:1 prescale value

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3 and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

## 21.1 Control Registers

## TABLE 21-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | 6                                                                                            |                 |       |                                                                       |       |         |        |        | Bi     | ts      |        |       |      |      |      |      |      |            |

|-----------------------------|---------------------------------|----------------------------------------------------------------------------------------------|-----------------|-------|-----------------------------------------------------------------------|-------|---------|--------|--------|--------|---------|--------|-------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range                                                                                    | 31/15           | 30/14 | 29/13                                                                 | 28/12 | 27/11   | 26/10  | 25/9   | 24/8   | 23/7    | 22/6   | 21/5  | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 7000                        | PMCON                           | 31:16                                                                                        |                 | _     | _                                                                     | —     | —       | —      | _      | _      |         | _      | _     | —    | _    | _    | —    | _    | 0000       |

| 1000                        |                                 | 15:0                                                                                         | ON              | _     | SIDL                                                                  | ADRMU | JX<1:0> | PMPTTL | PTWREN | PTRDEN | CSF     | <1:0>  | ALP   | CS2P | CS1P | _    | WRSP | RDSP | 0000       |

| 7010                        | PMMODE                          | 31:16                                                                                        | —               | _     | _                                                                     | _     | _       | —      | _      | —      | _       | —      | _     | _    | _    | _    | _    | -    | 0000       |

| 7010                        |                                 | 15:0                                                                                         | BUSY            | IRQM  | IRQM<1:0> INCM<1:0> MODE16 MODE<1:0> WAITB<1:0> WAITM<3:0> WAITE<1:0> |       |         |        |        |        |         |        | <1:0> | 0000 |      |      |      |      |            |

| 7020                        | PMADDR                          | 31:16                                                                                        | _               | -     |                                                                       | _     | _       | _      |        | _      | _       | _      |       | _    | _    |      | _    |      | 0000       |

| 7020                        | PINADUR                         | 15:0                                                                                         | CS2             | CS1   |                                                                       |       |         |        |        |        | ADDR    | <13:0> |       |      |      |      |      |      | 0000       |

| 7030                        | PMDOUT                          | 31:16                                                                                        |                 |       |                                                                       |       |         |        |        | DATAOU | T-31.0> |        |       |      |      |      |      |      | 0000       |

| 7030                        | FINIDOUT                        | 15:0                                                                                         |                 |       |                                                                       |       |         |        |        | DAIAOU | 1~31.02 |        |       |      |      |      |      |      | 0000       |

| 7040                        | PMDIN                           | 31:16                                                                                        |                 |       |                                                                       |       |         |        |        | DATAIN | <31.0>  |        |       |      |      |      |      |      | 0000       |

| 7040                        |                                 | 15:0                                                                                         |                 |       |                                                                       |       |         |        |        | DATAIN | ~51.02  |        |       |      |      |      |      |      | 0000       |

| 7050                        | PMAEN                           | 31:16                                                                                        | _               | —     | -                                                                     | —     | —       | _      | _      | —      | —       | —      | _     | —    | —    | _    | _    | —    | 0000       |

| 7050                        | FINALIN                         | 15:0                                                                                         | PTEN<15:0> 0000 |       |                                                                       |       |         |        |        |        |         | 0000   |       |      |      |      |      |      |            |

| 7060                        | PMSTAT                          | 31:16                                                                                        | _               | —     | —                                                                     | _     | _       | _      | —      | —      | _       | _      | —     | _    | -    | —    | _    | —    | 0000       |

| 1000                        | FINISTAL                        | 15:0                                                                                         | IBF             | IBOV  | _                                                                     | _     | IB3F    | IB2F   | IB1F   | IB0F   | OBE     | OBUF   | _     | _    | OB3E | OB2E | OB1E | OB0E | BFBF       |

| Legend                      | 4                               | inknown value on Reset: — = unimplemented, read as '0' Reset values are shown in bexadecimal |                 |       |                                                                       |       |         |        |        |        |         |        |       |      |      |      |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                     | —                     | _                 | _                 | _                 | —                 | _                | —                |  |  |

| 00.40        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                     | —                     | _                 | _                 | —                 | —                 | —                | —                |  |  |

|              | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CS2 <sup>(1)</sup>    | CS1 <sup>(3)</sup>    | )                 |                   |                   |                   |                  |                  |  |  |

|              | ADDR15 <sup>(2)</sup> | ADDR14 <sup>(4)</sup> |                   |                   | ADDR              | <13.02            |                  |                  |  |  |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

|              | ADDR<7:0>             |                       |                   |                   |                   |                   |                  |                  |  |  |

#### REGISTER 21-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | /ritable bit U = Unimplemented bit, read as '0' |                    |  |  |

|-------------------|------------------|-------------------------------------------------|--------------------|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                            | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 CS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 ADDR<15>: Destination Address bit 15<sup>(2)</sup>

- bit 14 CS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Destination Address bit 14<sup>(4)</sup>

- bit 13-0 ADDR<13:0>: Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- 3: When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

|              |                   | ICDAIL. N         |                   |                   |                                         |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                   | YEAR1             | 0<3:0>            |                   |                                         | YEAR0             | 1<3:0>           |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                   | MONTH             | 10<3:0>           |                   | MONTH01<3:0>                            |                   |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   | DAY10             | <3:0>             |                   |                                         | DAY01             | <3:0>            |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x R/W-x                             |                   | R/W-x            | R/W-x            |  |  |

| 7:0          |                   | _                 | _                 | —                 | – WDAY01<3:                             |                   |                  |                  |  |  |

|              |                   |                   |                   |                   | •                                       |                   |                  |                  |  |  |

| Legend:      |                   |                   |                   |                   |                                         |                   |                  |                  |  |  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimplemented bit, read as '0'      |                   |                  |                  |  |  |

| -n = Value   | e at POR          |                   | '1' = Bit is se   | et                | '0' = Bit is cleared x = Bit is unknown |                   |                  |                  |  |  |

## REGISTER 22-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digits

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1s place digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1s place digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 51.24        | EDG1MOD           | EDG1POL           |                   | EDG1S               | EDG2STAT          | EDG1STAT          |                        |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | _                 | —                 |                        |                  |

| 15:0         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 15:8         | ON                | —                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 7:0          |                   |                   | IRNG              | <1:0>               |                   |                   |                        |                  |

#### REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER

#### Legend:

| 5                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31 EDG1MOD: Edge 1 Edge Sampling Select bit

1 = Input is edge-sensitive

0 = Input is level-sensitive

bit 30 EDG1POL: Edge 1 Polarity Select bit

1 = Edge 1 programmed for a positive edge response

0 = Edge 1 programmed for a negative edge response

#### bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

#### 1111 = Reserved

1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected

## 0000 = Timer1 Event is selected

## bit 25 EDG2STAT: Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control edge source

- 1 = Edge 2 has occurred

- 0 = Edge 2 has not occurred

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-42) in Section 31.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

## 27.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN bit (OSCCON<4>) is clear and a  $\tt WAIT$  instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

#### 27.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The peripheral bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

## 30.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 30.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

### 30.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 30.9 PICkit 3 In-Circuit Debugger/ Programmer

The MPLAB PICkit 3 allows debugging and programming of PIC and dsPIC Flash microcontrollers at a most affordable price point using the powerful graphical user interface of the MPLAB IDE. The MPLAB PICkit 3 is connected to the design engineer's PC using a fullspeed USB interface and can be connected to the target via a Microchip debug (RJ-11) connector (compatible with MPLAB ICD 3 and MPLAB REAL ICE). The connector uses two device I/O pins and the Reset line to implement in-circuit debugging and In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>).

## 30.10 MPLAB PM3 Device Programmer

The MPLAB PM3 Device Programmer is a universal, CE compliant device programmer with programmable voltage verification at VDDMIN and VDDMAX for maximum reliability. It features a large LCD display (128 x 64) for menus and error messages, and a modular, detachable socket assembly to support various package types. The ICSP cable assembly is included as a standard item. In Stand-Alone mode, the MPLAB PM3 Device Programmer can read, verify and program PIC devices without a PC connection. It can also set code protection in this mode. The MPLAB PM3 connects to the host PC via an RS-232 or USB cable. The MPLAB PM3 has high-speed communications and optimized algorithms for quick programming of large memory devices, and incorporates an MMC card for file storage and data applications.

## TABLE 31-33: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE) (CONTINUED)

| AC CHA        | RACTER  | ISTICS                 |                        | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |       |                                        |  |  |

|---------------|---------|------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------------------|--|--|

| Param.<br>No. | Symbol  | Charac                 | teristics              | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                 | Max. | Units | Conditions                             |  |  |

| IM34          | THD:STO | Stop Condition         | 100 kHz mode           | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                                                                     |      | ns    | —                                      |  |  |

|               |         | Hold Time              | 400 kHz mode           | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                                                                     | —    | ns    |                                        |  |  |

|               |         |                        | 1 MHz mode<br>(Note 2) | Трв * (BRG + 2)                                                                                                                                                                                                                                                                                                                                     | —    | ns    |                                        |  |  |

| IM40          | TAA:SCL | Output Valid           | 100 kHz mode           | —                                                                                                                                                                                                                                                                                                                                                   | 3500 | ns    | —                                      |  |  |

|               |         | from Clock             | 400 kHz mode           | —                                                                                                                                                                                                                                                                                                                                                   | 1000 | ns    | —                                      |  |  |

|               |         |                        | 1 MHz mode<br>(Note 2) | —                                                                                                                                                                                                                                                                                                                                                   | 350  | ns    | —                                      |  |  |

| IM45          | TBF:SDA | Bus Free Time          | 100 kHz mode           | 4.7                                                                                                                                                                                                                                                                                                                                                 | —    | μS    | The amount of time the                 |  |  |

|               |         |                        | 400 kHz mode           | 1.3                                                                                                                                                                                                                                                                                                                                                 | —    | μS    | bus must be free                       |  |  |