Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

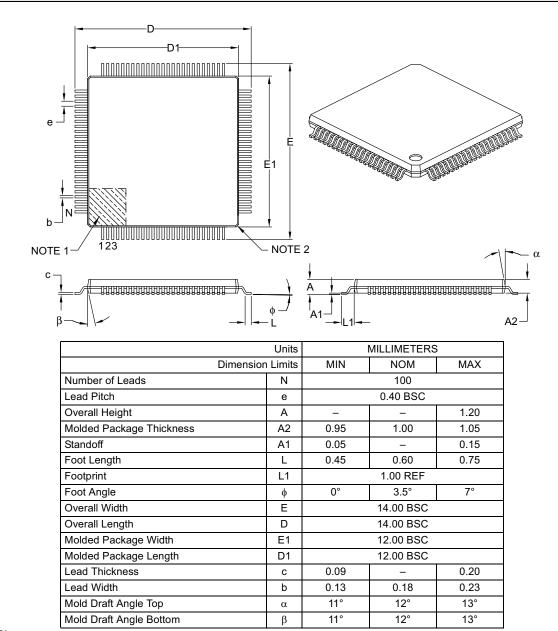

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx350f256lt-i-pf |

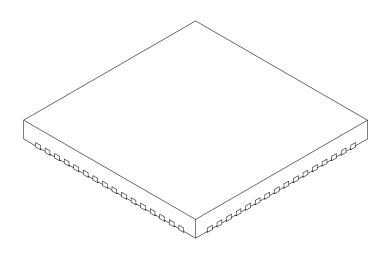

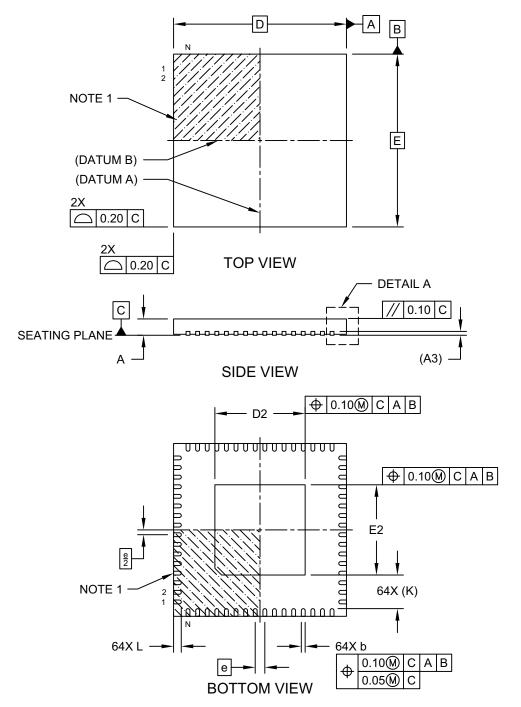

### TABLE 3: PIN NAMES FOR 64-PIN DEVICES

64-PIN QFN<sup>(1,2)</sup> AND TQFP<sup>(1,2)</sup> (TOP VIEW)

PIC32MX430F064H PIC32MX450F128H PIC32MX450F256H PIC32MX470F512H

64 1

QFN<sup>(3)</sup>

**TQFP**

| Pin # | Full Pin Name                              |

|-------|--------------------------------------------|

| 1     | AN22/RPE5/PMD5/RE5                         |

| 2     | AN23/PMD6/RE6                              |

| 3     | AN27/PMD7/RE7                              |

| 4     | AN16/C1IND/RPG6/SCK2/PMA5/RG6              |

| 5     | AN17/C1INC/RPG7/PMA4/RG7                   |

| 6     | AN18/C2IND/RPG8/PMA3/RG8                   |

| 7     | MCLR                                       |

| 8     | AN19/C2INC/RPG9/PMA2/RG9                   |

| 9     | Vss                                        |

| 10    | VDD                                        |

| 11    | AN5/C1INA/RPB5/VBUSON/RB5                  |

| 12    | AN4/C1INB/RB4                              |

| 13    | PGED3/AN3/C2INA/RPB3/RB3                   |

| 14    | PGEC3/AN2/C2INB/RPB2/CTED13/RB2            |

| 15    | PGEC1/VREF-/CVREF-/AN1/RPB1/CTED12/RB1     |

| 16    | PGED1/VREF+/CVREF+/AN0/RPB0/PMA6/RB0       |

| 17    | PGEC2/AN6/RPB6/RB6                         |

| 18    | PGED2/AN7/RPB7/CTED3//RB7                  |

| 19    | AVDD                                       |

| 20    | AVss                                       |

| 21    | AN8/RPB8/CTED10//RB8                       |

| 22    | AN9/RPB9/CTED4/PMA7/RB9                    |

| 23    | TMS/Cvrefout/AN10/RPB10/CTED11//PMA13/RB10 |

| 24    | TDO/AN11/PMA12/RB11                        |

| 25    | Vss                                        |

| 26    | VDD                                        |

| 27    | TCK/AN12/PMA11/RB12                        |

| 28    | TDI/AN13/PMA10/RB13                        |

| 29    | AN14/RPB14/CTED5/PMA1/RB14                 |

| 30    | AN15/RPB15/OCFB/CTED6/PMA0/RB15            |

| 31    | RPF4/SDA2/PMA9/RF4                         |

| 32    | RPF5/SCL2/PMA8/RF5                         |

|       | ·                                          |

| Pin # | Full Pin Name         |

|-------|-----------------------|

| 33    | USBID/RF3             |

| 34    | VBUS                  |

| 35    | Vusb3v3               |

| 36    | D-                    |

| 37    | D+                    |

| 38    | VDD                   |

| 39    | OSC1/CLKI/RC12        |

| 40    | OSC2/CLKO/RC15        |

| 41    | Vss                   |

| 42    | RPD8/RTCC/RD8         |

| 43    | RPD9/SDA1/RD9         |

| 44    | RPD10/SCL1/PMCS2/RD10 |

| 45    | RPD11/PMCS1/RD11      |

| 46    | RPD0/INT0/RD0         |

| 47    | SOSCI/RPC13/RC13      |

| 48    | SOSCO/RPC14/T1CK/RC14 |

| 49    | AN24/RPD1/RD1         |

| 50    | AN25/RPD2/SCK1/RD2    |

| 51    | AN26/RPD3/RD3         |

| 52    | RPD4/PMWR/RD4         |

| 53    | RPD5/PMRD/RD5         |

| 54    | RD6                   |

| 55    | RD7                   |

| 56    | VCAP                  |

| 57    | VDD                   |

| 58    | RPF0/RF0              |

| 59    | RPF1/RF1              |

| 60    | PMD0/RE0              |

| 61    | PMD1/RE1              |

| 62    | AN20/PMD2/RE2         |

| 63    | RPE3/CTPLS/PMD3/RE3   |

| 64    | AN21/PMD4/RE4         |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 12.0 "I/O Ports" for more information.

- 3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

### REGISTER 4-5: BMXDRMSZ: DATA RAM SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24:24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 31:24        |                   |                   |                   | BMXDRM            | /ISZ<31:24>       |                   |                  |                  |  |  |  |  |

| 22.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 23:16        | BMXDRMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 15:8         |                   |                   |                   | BMXDRI            | MSZ<15:8>         |                   |                  |                  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 7:0          |                   |                   |                   | BMXDR             | MSZ<7:0>          |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

### bit 31-0 BMXDRMSZ<31:0>: Data RAM Memory (DRM) Size bits

Static value that indicates the size of the Data RAM in bytes:

0x00004000 = Device has 16 KB RAM 0x00008000 = Device has 32 KB RAM 0x00010000 = Device has 64 KB RAM

0x00020000 = Device has 128 KB RAM

## REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | -                 | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | _                 | _                 | _                 | _                 | 3A<19:16>         |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |

| 15:8         |                   |                   |                   | BMXPU             | PBA<15:8>         |                   |                  |                  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | BMXPU             | PBA<7:0>          |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

bit 10-0 BMXPUPBA<10:0>: Read-Only bits

Value is always '0', which forces 2 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXPFMSZ.

### 6.0 RESETS

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

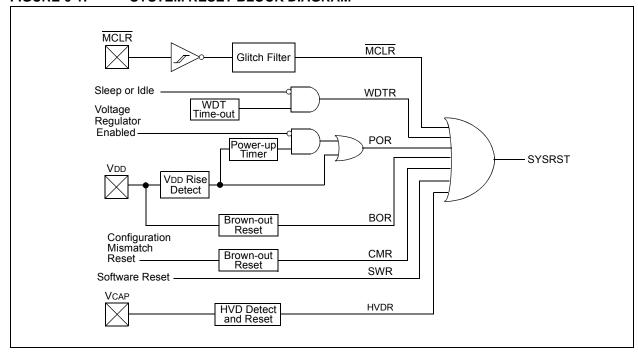

The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- · POR: Power-on Reset

- MCLR: Master Clear Reset pin

- · SWR: Software Reset

- · WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- · CMR: Configuration Mismatch Reset

- HVDR: High Voltage Detect Reset

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

## 9.2 Control Registers

## TABLE 9-1: PREFETCH REGISTER MAP

|                             | LE 9-1.               |               | VELFIC        |                    | O 1 E 1 1 11 | 17 11      |             |                                           |            |            |        |      |       |            |        |       |          |        |            |

|-----------------------------|-----------------------|---------------|---------------|--------------------|--------------|------------|-------------|-------------------------------------------|------------|------------|--------|------|-------|------------|--------|-------|----------|--------|------------|

| SS                          |                       |               |               |                    |              |            |             |                                           |            | Bit        | s      |      |       |            |        |       |          |        |            |

| Virtual Address<br>(BF88_#) | Register<br>Name      | Bit Range     | 31/15         | 30/14              | 29/13        | 28/12      | 27/11       | 26/10                                     | 25/9       | 24/8       | 23/7   | 22/6 | 21/5  | 20/4       | 19/3   | 18/2  | 17/1     | 16/0   | All Resets |

|                             | CHECON <sup>(1)</sup> | 31:16         | _             | _                  | _            | _          | _           | _                                         | _          | _          |        | _    | _     | _          | _      | _     | _        | CHECOH | 0000       |

| +000                        | CITLOON               | 15:0          |               | _                  | _            | _          | _           | _                                         | DCSZ       | Z<1:0>     | ı      | _    | PREFE | N<1:0>     | _      | P     | FMWS<2:0 | )>     | 0007       |

| 4010                        | CHEACC <sup>(1)</sup> |               | CHEWEN        | _                  | _            | _          | _           | _                                         | _          | _          | _      | _    | _     | _          | _      | _     | _        | _      | 0000       |

|                             |                       | 15:0          | _             |                    | _            | _          | _           | _                                         | _          | _          | -      | _    | _     | _          |        | CHEID | X<3:0>   |        | 00xx       |

| 4020                        | CHETAG <sup>(1)</sup> |               | LTAGBOOT      |                    |              |            |             |                                           |            |            |        |      |       |            |        |       |          |        |            |

|                             |                       | 15:0          |               |                    |              |            |             | LTAG<                                     | 15:4>      |            |        | 1    |       |            | LVALID | LLOCK | LTYPE    |        | xxx2       |

| 4030                        | CHEMSK <sup>(1)</sup> | 31:16         | _             | _                  | _            | _          |             | —<br>************************************ | _          | _          | _      | _    | _     | _          | _      | _     | _        |        | 0000       |

|                             |                       |               |               |                    |              |            | LN          | //ASK<15:5                                | >          |            |        |      |       |            | _      | _     | _        |        | xxxx       |

| 4040                        | CHEW0                 | 31:16<br>15:0 |               |                    |              |            |             |                                           |            | CHEW0      | <31:0> |      |       |            |        |       |          |        | XXXX       |

|                             |                       | 31:16         |               |                    |              |            |             |                                           |            |            |        |      |       |            |        |       |          |        | xxxx       |

| 4050                        | CHEW1                 | 15:0          |               |                    |              |            |             |                                           |            | CHEW1      | <31:0> |      |       |            |        |       |          |        | XXXX       |

|                             |                       | 31:16         |               |                    |              |            |             |                                           |            |            |        |      |       |            |        |       |          |        | xxxx       |

| 4060                        | CHEW2                 | 15:0          |               |                    |              |            |             |                                           |            | CHEW2      | <31:0> |      |       |            |        |       |          |        | xxxx       |

|                             |                       | 31:16         |               |                    |              |            |             |                                           |            |            |        |      |       |            |        |       |          |        | xxxx       |

| 4070                        | CHEW3                 | 15:0          |               |                    |              |            |             |                                           |            | CHEW3      | <31:0> |      |       |            |        |       |          |        | xxxx       |

| 4000                        | CUEL DU               | 31:16         | _             | _                  | _            | _          | _           | _                                         | _          |            |        |      | CH    | IELRU<24:1 | 6>     |       |          |        | 0000       |

| 4080                        | CHELRU                | 15:0          | •             |                    |              | •          | •           | •                                         | •          | CHELRU     | <15:0> |      |       |            |        |       |          |        | 0000       |

| 4090                        | CHEHIT                | 31:16         |               |                    |              |            |             |                                           |            | CHEHIT     | <31·0> |      |       |            |        |       |          |        | xxxx       |

| 4090                        | CHEITH                | 15:0          |               | CHEHIT<31:0> xxxxx |              |            |             |                                           |            |            |        |      |       | xxxx       |        |       |          |        |            |

| 40A0                        | CHEMIS                | 31:16         |               | CHEMIS<31:0>       |              |            |             |                                           |            |            |        |      |       |            |        |       |          |        |            |

|                             |                       | 15:0          |               | xxxx               |              |            |             |                                           |            |            |        |      |       |            |        |       |          |        |            |

| 40C0                        | CHEPFABT              | 31:16         |               | CHEPFABT<31:0>     |              |            |             |                                           |            |            |        |      |       |            |        |       |          |        |            |

| Legen                       | d                     | 15:0          | n value on Re |                    | ınimnlaman   | tod road a | a 'o' Basat | values are                                | ahaun in h | ovadocimal |        |      |       |            |        |       |          |        | XXXX       |

PIC32MX330/350/370/430/450/470

**Legend:** x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

### REGISTER 9-1: CHECON: CACHE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| 00:40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | CHECOH           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | DCSZ             | <b>′</b> <1:0>   |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-1             | R/W-1            | R/W-1            |

| 7:0          |                   | _                 | PREFE             | :N<1:0>           | _                 | F                 | PFMWS<2:0>       | •                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-17 Unimplemented: Write '0'; ignore read

bit 16 CHECOH: Cache Coherency Setting on a PFM Program Cycle bit

1 = Invalidate all data and instruction lines

0 = Invalidate all data lnes and instruction lines that are not locked

bit 15-10 Unimplemented: Write '0'; ignore read

bit 9-8 DCSZ<1:0>: Data Cache Size in Lines bits

11 = Enable data caching with a size of 4 Lines

10 = Enable data caching with a size of 2 Lines

01 = Enable data caching with a size of 1 Line

00 = Disable data caching

Changing these bits induce all lines to be reinitialized to the "invalid" state.

bit 7-6 **Unimplemented:** Write '0'; ignore read

bit 5-4 **PREFEN<1:0>:** Predictive Prefetch Enable bits

11 = Enable predictive prefetch for both cacheable and non-cacheable regions

10 = Enable predictive prefetch for non-cacheable regions only

01 = Enable predictive prefetch for cacheable regions only

00 = Disable predictive prefetch

bit 3 Unimplemented: Write '0'; ignore read

bit 2-0 **PFMWS<2:0>:** PFM Access Time Defined in Terms of SYSLK Wait States bits

111 = Seven Wait states

110 = Six Wait states

101 = Five Wait states

100 = Four Wait states

011 = Three Wait states

010 = Two Wait states

001 = One Wait state

000 = Zero Wait state

### REGISTER 10-8: DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                 | _                 |                      | _                 | _                | _                |

| 22:46        | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |

| 23:16        |                   |                   |                   | CHAIRQ<           | <7:0> <sup>(1)</sup> |                   |                  |                  |

| 15:8         | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1                | R/W-1             | R/W-1            | R/W-1            |

| 15.6         |                   |                   |                   | CHSIRQ<           | <7:0> <sup>(1)</sup> |                   |                  |                  |

| 7:0          | S-0               | S-0               | R/W-0             | R/W-0             | R/W-0                | U-0               | U-0              | U-0              |

| 7.0          | CFORCE            | CABORT            | PATEN             | SIRQEN            | AIRQEN               | _                 | _                | _                |

Legend:S = Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-24 Unimplemented: Read as '0'

bit 23-16 CHAIRQ<7:0>: Channel Transfer Abort IRQ bits(1)

11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag

•

•

00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag

00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag

bit 15-8 CHSIRQ<7:0>: Channel Transfer Start IRQ bits(1)

11111111 = Interrupt 255 will initiate a DMA transfer

•

•

00000001 = Interrupt 1 will initiate a DMA transfer 00000000 = Interrupt 0 will initiate a DMA transfer

bit 7 CFORCE: DMA Forced Transfer bit

1 = A DMA transfer is forced to begin when this bit is written to a '1'

0 = This bit always reads '0'

bit 6 CABORT: DMA Abort Transfer bit

1 = A DMA transfer is aborted when this bit is written to a '1'

0 = This bit always reads '0'

bit 5 PATEN: Channel Pattern Match Abort Enable bit

1 = Abort transfer and clear CHEN on pattern match

0 = Pattern match is disabled

bit 4 SIRQEN: Channel Start IRQ Enable bit

1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs

0 = Interrupt number CHSIRQ is ignored and does not start a transfer

bit 3 AIRQEN: Channel Abort IRQ Enable bit

1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

bit 2-0 Unimplemented: Read as '0'

Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

### **Control Registers** 11.1

## TABLE 11-1: USB REGISTER MAP

| SS                          |                                 |               |       |       |       |       |       |       |      |      | Bit                         | s             |                   |                   |              |               |                 |                    |            |

|-----------------------------|---------------------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|-----------------------------|---------------|-------------------|-------------------|--------------|---------------|-----------------|--------------------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7                        | 22/6          | 21/5              | 20/4              | 19/3         | 18/2          | 17/1            | 16/0               | All Resets |

| 5040                        | U1OTGIR <sup>(2)</sup>          | 31:16<br>15:0 | _     |       |       |       | _     | _     | _    | _    | —<br>IDIF                   | —<br>T1MSECIF | —<br>LSTATEIF     | —<br>ACTVIF       | —<br>SESVDIF | —<br>SESENDIF | _               | -<br>VBUSVDIF      | 0000       |

| 5050                        | U1OTGIE                         | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _                           | _             | _                 | _                 | _            | _             | _               | _                  | 0000       |

| 5060                        | U1OTGSTAT <sup>(3)</sup>        | 15:0<br>31:16 | _     |       |       |       | _     | _     | _    | _    | IDIE —                      | T1MSECIE —    | LSTATEIE —        | ACTVIE —          | SESVDIE —    | SESENDIE<br>— |                 | VBUSVDIE —         | 0000       |

| 5000                        | UTUTGSTAT!                      | 15:0<br>31:16 |       |       |       |       | _     | _     | _    | _    | ID                          |               | LSTATE            | _                 | SESVD        | SESEND        |                 | VBUSVD             | 0000       |

| 5070                        | U10TGCON                        | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | DPPULUP                     |               | DPPULDWN          | DMPULDWN          | VBUSON       | OTGEN         | VBUSCHG         | VBUSDIS            | 0000       |

| 5080                        | U1PWRC                          | 31:16<br>15:0 | _     |       | _     |       | _     | _     | _    | _    | —<br>UACTPND <sup>(4)</sup> | _             |                   | —<br>USLPGRD      | —<br>USBBUSY | _             | —<br>USUSPEND   | USBPWR             | 0000       |

|                             |                                 | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _                           | _             | _                 | _                 | _            | _             | _               | _                  | 0000       |

| 5200                        | U1IR <sup>(2)</sup>             | 15:0          |       | _     | 1     | _     | _     | _     | _    | _    | STALLIF                     | ATTACHIF      | RESUMEIF          | IDLEIF            | TRNIF        | SOFIF         | UERRIF          | URSTIF<br>DETACHIF | 0000       |

|                             |                                 | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _                           | _             | _                 | _                 | _            | _             | _               | _                  | 0000       |

| 5210                        | U1IE                            | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | STALLIE                     | ATTACHIE      | RESUMEIE          | IDLEIE            | TRNIE        | SOFIE         | UERRIE          | URSTIE DETACHIE    | 0000       |

|                             |                                 | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _                           | _             | _                 | _                 | _            | _             | _               | _                  | 0000       |

| 5220                        | U1EIR <sup>(2)</sup>            | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | BTSEF                       | BMXEF         | DMAEF             | BTOEF             | DFN8EF       | CRC16EF       | CRC5EF<br>EOFEF | PIDEF              | 0000       |

|                             |                                 | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _                           | _             | -                 | _                 | _            | _             | _               | _                  | 0000       |

| 5230                        | U1EIE                           | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | BTSEE                       | BMXEE         | DMAEE             | BTOEE             | DFN8EE       | CRC16EE       | CRC5EE<br>EOFEE | PIDEE              | 0000       |

| 5240                        | U1STAT <sup>(3)</sup>           | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _                           | _             | _                 | _                 | _            | _             | _               | _                  | 0000       |

| 0240                        | 0101711                         | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    |                             |               | T<3:0>            |                   | DIR          | PPBI          | _               | _                  | 0000       |

| 5050                        | 1140011                         | 31:16         |       |       |       |       |       |       | _    | _    |                             | _             | —                 | _                 | _            | _             | _               |                    | 0000       |

| 5250                        | U1CON                           | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | JSTATE                      | SE0           | PKTDIS<br>TOKBUSY | USBRST            | HOSTEN       | RESUME        | PPBRST          | USBEN<br>SOFEN     | 0000       |

| 5260                        | U1ADDR                          | 31:16         | _     |       | _     |       |       | _     | _    | _    | _                           | _             | _                 | _                 | _            | _             | _               | _                  | 0000       |

|                             |                                 | 15:0          | _     |       | _     |       |       |       | _    | _    | LSPDEN                      |               |                   | DE                | VADDR<6:     | 0>            |                 |                    | 0000       |

| 5270                        | U1BDTP1                         | 31:16         |       | _     | _     | _     | _     | _     | _    | _    | _                           | _             | _                 | —<br> TPTRL<15:9> | _            | _             | _               | _                  | 0000       |

|                             |                                 | 15:0          |       |       | _     |       | —     |       | _    |      |                             |               | BL                | 11F1KL<15:9>      | •            |               |                 | _                  | 0000       |

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information. Note 1:

<sup>2:</sup> This register does not have associated SET and INV registers.

This register does not have associated CLR, SET and INV registers.

Reset value for this bit is undefined.

## REGISTER 11-6: U1IR: USB INTERRUPT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-----------------------|-------------------------|-------------------|----------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0               | U-0                   | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 31.24        | _                 | _                     | _                       | _                 | _                    | _                 | _                     | _                       |

| 23:16        | U-0               | U-0                   | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 23.10        | _                 | _                     | _                       | _                 | _                    | _                 | _                     | _                       |

| 15:8         | U-0               | U-0                   | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 13.6         | _                 | _                     | _                       | _                 |                      | _                 | _                     | _                       |

|              | R/WC-0, HS        | R/WC-0, HS            | R/WC-0, HS              | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS        | R-0                   | R/WC-0, HS              |

| 7:0          | STALLIF           | лтта Сыі <b>с</b> (1) | RESUMEIF <sup>(2)</sup> | IDLEIF            | TRNIF <sup>(3)</sup> | SOFIF             | UERRIF <sup>(4)</sup> | URSTIF <sup>(5)</sup>   |

|              | JIALLIF           | AT IACITIES           | KLOOMEIL                | IDLEIF            | TIMINIE .            | 3011              | OLIVINI.,             | DETACHIF <sup>(6)</sup> |

Legend:WC = Write '1' to clearHS = Hardware Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

### bit 31-8 Unimplemented: Read as '0'

- bit 7 **STALLIF:** STALL Handshake Interrupt bit

- 1 = In Host mode, a STALL handshake was received during the handshake phase of the transaction In Device mode, a STALL handshake was transmitted during the handshake phase of the transaction

- 0 = STALL handshake has not been sent

- bit 6 **ATTACHIF:** Peripheral Attach Interrupt bit<sup>(1)</sup>

- 1 = Peripheral attachment was detected by the USB module

- 0 = Peripheral attachment was not detected

- bit 5 **RESUMEIF:** Resume Interrupt bit<sup>(2)</sup>

- 1 = K-State is observed on the D+ or D- pin for 2.5 μs

- 0 = K-State is not observed

- bit 4 **IDLEIF:** Idle Detect Interrupt bit

- 1 = Idle condition detected (constant Idle state of 3 ms or more)

- 0 = No Idle condition detected

- bit 3 **TRNIF:** Token Processing Complete Interrupt bit<sup>(3)</sup>

- 1 = Processing of current token is complete; a read of the U1STAT register will provide endpoint information

- 0 = Processing of current token not complete

- bit 2 **SOFIF:** SOF Token Interrupt bit

- 1 = SOF token received by the peripheral or the SOF threshold reached by the host

- 0 = SOF token was not received nor threshold reached

- bit 1 **UERRIF:** USB Error Condition Interrupt bit<sup>(4)</sup>

- 1 = Unmasked error condition has occurred

- 0 = Unmasked error condition has not occurred

- bit 0 **URSTIF:** USB Reset Interrupt bit (Device mode)<sup>(5)</sup>

- 1 = Valid USB Reset has occurred

- 0 = No USB Reset has occurred

- bit 0 **DETACHIF:** USB Detach Interrupt bit (Host mode)<sup>(6)</sup>

- 1 = Peripheral detachment was detected by the USB module

- 0 = Peripheral detachment was not detected

- Note 1: This bit is valid only if the HOSTEN bit is set (see Register 11-11), there is no activity on the USB for 2.5 μs, and the current bus state is not SE0.

- 2: When not in Suspend mode, this interrupt should be disabled.

- 3: Clearing this bit will cause the STAT FIFO to advance.

- 4: Only error conditions enabled through the U1EIE register will set this bit.

- 5: Device mode.

- 6: Host mode.

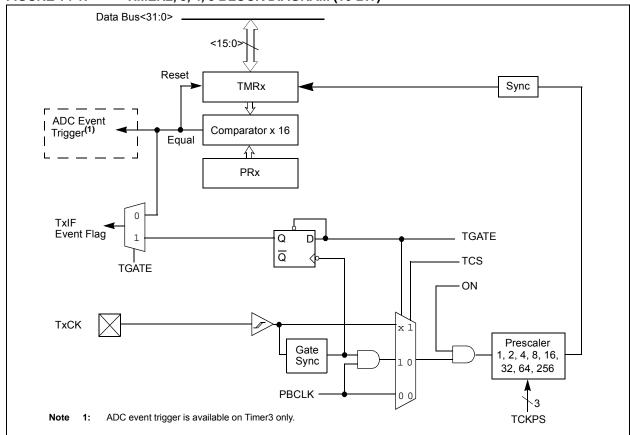

## 14.0 TIMER2/3, TIMER4/5

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14.** "**Timers**" (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32MX330/350/370/430/450/470 family of devices features four synchronous 16-bit timers (default) that can operate as a free-running interval timer for various timing applications and counting external events. The following modes are supported:

- · Synchronous internal 16-bit timer

- · Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- Synchronous external 32-bit timer

Note:

In this chapter, references to registers, TxCON, TMRx and PRx, use 'x' to represent Timer2 through 5 in 16-bit modes. In 32-bit modes, 'x' represents Timer2 or 4; 'y' represents Timer3 or 5.

## 14.1 Additional Supported Features

- · Selectable clock prescaler

- · Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/ 3 in 32-bit mode)

- Fast bit manipulation using CLR, SET, and INV registers

FIGURE 14-1: TIMER2, 3, 4, 5 BLOCK DIAGRAM (16-BIT)

## 19.1 Control Registers

TABLE 19-1: I2C1 AND I2C2 REGISTER MAP

| ess                         |                                 |               |         |        |        |          |        |       |        | Bi        | ts      |             |            |            |            |       |         |      | ,,         |

|-----------------------------|---------------------------------|---------------|---------|--------|--------|----------|--------|-------|--------|-----------|---------|-------------|------------|------------|------------|-------|---------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15   | 30/14  | 29/13  | 28/12    | 27/11  | 26/10 | 25/9   | 24/8      | 23/7    | 22/6        | 21/5       | 20/4       | 19/3       | 18/2  | 17/1    | 16/0 | All Resets |

| 5000                        | I2C1CON                         | 31:16         |         | _      | _      | _        | _      | _     | _      | _         | _       | _           | _          | _          | _          | _     | _       | _    | 0000       |

| 0000                        | 12010011                        | 15:0          | ON      | _      | SIDL   | SCLREL   | STRICT | A10M  | DISSLW | SMEN      | GCEN    | STREN       | ACKDT      | ACKEN      | RCEN       | PEN   | RSEN    | SEN  | BFFF       |

| 5010                        | I2C1STAT                        | 31:16         |         | _      |        | _        |        | _     | _      | _         |         | _           | _          | _          | _          | _     | _       | _    | 0000       |

|                             |                                 |               | ACKSTAT | TRSTAT |        | _        |        | BCL   | GCSTAT | ADD10     | IWCOL   | I2COV       | D_A        | Р          | S          | R_W   | RBF     | TBF  | 0000       |

| 5020                        | I2C1ADD                         | 31:16         | _       | _      |        | _        |        |       | _      | _         |         | _           | _          | _          | _          | _     | _       | _    | 0000       |

|                             |                                 | 15:0          | _       | _      | _      | _        | _      | _     |        |           |         |             | Address    | Register   |            |       |         |      | 0000       |

| 5030                        | I2C1MSK                         | 31:16         |         | _      | _      | _        | _      | _     | _      | _         | _       | _           |            |            | _          | _     | _       | _    | 0000       |

|                             |                                 | 15:0          | _       |        |        | _        |        |       |        |           |         |             | Address Ma | sk Registe | •          |       | ı       |      | 0000       |

| 5040                        | I2C1BRG                         | 31:16         |         | _      | _      | _        |        | _     | _      | _         |         |             |            | _          | _          | _     | _       | _    | 0000       |

|                             |                                 | 15:0          | _       | _      |        | _        |        |       |        |           | Вац     | ıd Rate Ger | erator Reg |            |            |       |         |      | 0000       |

| 5050                        | I2C1TRN                         | 31:16         | _       |        | _      | _        | _      | _     | _      |           |         | _           |            |            | De minte m | _     | _       | _    | 0000       |

|                             |                                 | 15:0<br>31:16 |         |        |        | _        |        |       | _      | _         |         |             |            | Transmit   | Register   | _     |         | _    | 0000       |

| 5060                        | I2C1RCV                         | 15:0          | _       |        |        | _        |        |       | _      | _         |         | _           | _          | Dagaina    | Dogister.  | _     | _       | _    | 0000       |

|                             |                                 | 31:16         | _       |        |        | _        |        |       | _      | _         |         |             |            | Receive    | Register — | _     | _       | _    | 0000       |

| 5100                        | I2C2CON                         | 15:0          | ON      |        | SIDL   | SCLREL   | STRICT | A10M  | DISSLW | SMEN      | GCEN    | STREN       | ACKDT      | ACKEN      | RCEN       | PEN   | RSEN    | SEN  | BFFF       |

|                             |                                 | 31:16         |         |        | - OIDL | - OCENEE |        |       |        | OIVILIN — | - OCLIV | - OTKLIN    | AOND1      | ACKLIN     | - INOLIN   | - LIN | - NOLIV | —    | 0000       |

| 5110                        | I2C2STAT                        |               | ACKSTAT | TRSTAT |        | _        |        | BCL   | GCSTAT | ADD10     | IWCOL   | I2COV       | DΑ         | Р          | S          | R W   | RBF     | TBF  | 0000       |

|                             |                                 | 31:16         |         | _      |        | _        |        | _     | _      | _         | _       | _           |            | _          |            |       | _       |      | 0000       |

| 5120                        | I2C2ADD                         | 15:0          | _       | _      | _      | _        | _      |       |        |           |         |             | Address    | Register   |            |       |         |      | 0000       |

|                             |                                 | 31:16         | _       | _      | -      | _        | _      | _     | _      | _         | _       | _           | _          | _          | _          | _     | _       | _    | 0000       |

| 5130                        | I2C2MSK                         | 15:0          | _       | _      | _      | _        | _      | _     |        |           |         |             | Address Ma | sk Registe | •          |       |         |      | 0000       |

| 5446                        | IOCODD C                        | 31:16         | _       | _      | _      | _        | _      | _     | _      | _         | _       | _           | _          | _          | _          | _     | _       | _    | 0000       |

| 5140                        | I2C2BRG                         | 15:0          | _       | _      | _      | _        |        |       |        |           | Bau     | d Rate Ger  | erator Reg | ister      |            |       |         |      | 0000       |

| E1E0                        | IOCOTON                         | 31:16         | _       | _      | -      | _        | -      | _     | _      | _         | _       | _           | _          | _          | _          | _     | _       | _    | 0000       |

| 5150                        | I2C2TRN                         | 15:0          | _       | _      | -      | _        | _      | _     | _      |           |         |             |            | Transmit   | Register   |       |         |      | 0000       |

| 5160                        | I2C2RCV                         | 31:16         | _       | _      | 1      | _        | _      |       | _      | 1         | _       | _           |            | _          | _          | _     | _       | _    | 0000       |

| 0100                        | IZUZRUV                         | 15:0          | _       | _      | I      | _        | -      |       | _      | I         |         |             |            | Receive    | Register   |       |         |      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| PIC32IVIX | (330/350 | 0/3/0/43 | 30/450/4 | 170 |  |

|-----------|----------|----------|----------|-----|--|

| NOTES:    |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

# 30.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM™ and dsPICDEM™ demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELoQ® security ICs, CAN, IrDA®, PowerSmart battery management, SEEVAL® evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

### 30.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

### TABLE 31-19: PLL CLOCK TIMING SPECIFICATIONS

|                    | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                                                               |  |  |  |

|--------------------|-----------------------------------------------------------------------|---------------------------------------------------------------|--|--|--|

| AC CHARACTERISTICS | Operating temperature                                                 | $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial           |  |  |  |

|                    |                                                                       | -40°C ≤ TA ≤ +85°C for Industrial                             |  |  |  |

|                    |                                                                       | $-40^{\circ}$ C $\leq$ TA $\leq$ +105 $^{\circ}$ C for V-temp |  |  |  |

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup>                                      | Min.  | Typical | Max.  | Units | Conditions                        |

|---------------|--------|---------------------------------------------------------------------|-------|---------|-------|-------|-----------------------------------|

| OS50          | FPLLI  | PLL Voltage Controlled<br>Oscillator (VCO) Input<br>Frequency Range | 3.92  | _       | 5     | MHz   | ECPLL, HSPLL, XTPLL, FRCPLL modes |

| OS51a         | Fsys   | On-Chip VCO System Frequency                                        | 60    | _       | 120   | MHz   | Commercial devices                |

| OS51b         |        |                                                                     | 60    | _       | 100   | MHz   | Industrial devices                |

| OS51c         |        |                                                                     | 60    | _       | 80    | MHz   | V-temp devices                    |

| OS52          | TLOCK  | PLL Start-up Time (Lock Time)                                       | _     | _       | 2     | ms    | _                                 |

| OS53          | DCLK   | CLKO Stability <sup>(2)</sup> (Period Jitter or Cumulative)         | -0.25 | _       | +0.25 | %     | Measured over 100 ms period       |

- Note 1: These parameters are characterized, but not tested in manufacturing.

- **2:** This jitter specification is based on clock-cycle by clock-cycle measurements. To get the effective jitter for individual time-bases on communication clocks, use the following formula:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{SYSCLK}{Communication Clock}}}$$

For example, if SYSCLK = 40 MHz and SPI bit rate = 20 MHz, the effective jitter is as follows:

$$Effective Jitter = \frac{D_{CLK}}{\sqrt{\frac{40}{20}}} = \frac{D_{CLK}}{1.41}$$

### **TABLE 31-20: INTERNAL FRC ACCURACY**

| AC CHA                                          | RACTERISTICS    | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |         |      |                    |   |  |  |

|-------------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|--------------------|---|--|--|

| Param.<br>No.                                   | Characteristics | Min.                                                                                                                                                                                                                                                     | Typical | Max. | . Units Conditions |   |  |  |

| Internal FRC Accuracy @ 8.00 MHz <sup>(1)</sup> |                 |                                                                                                                                                                                                                                                          |         |      |                    |   |  |  |

| F20b                                            | FRC             | -0.9                                                                                                                                                                                                                                                     | _       | +0.9 | %                  | _ |  |  |

Note 1: Frequency calibrated at 25°C and 3.3V. The TUN bits can be used to compensate for temperature drift.

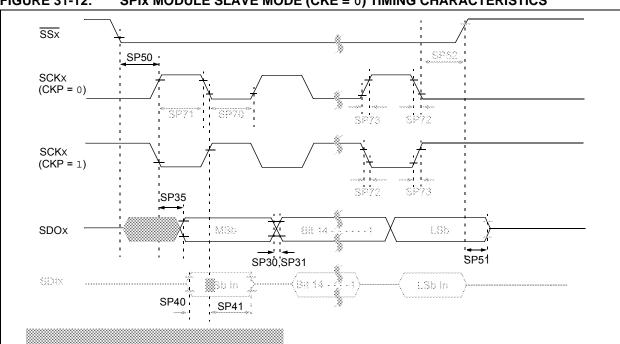

FIGURE 31-12: SPIX MODULE SLAVE MODE (CKE = 0) TIMING CHARACTERISTICS

TABLE 31-31: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                           |                                                 | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                     |      |       |                    |  |

|--------------------|---------------------------|-------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------|-------|--------------------|--|

| Param.<br>No.      | Symbol Characteristics(') |                                                 |                                                                                                                                                                                                                                                          | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |  |

| SP70               | TscL                      | SCKx Input Low Time (Note 3)                    | Tsck/2                                                                                                                                                                                                                                                   | _                   |      | ns    | _                  |  |

| SP71               | TscH                      | SCKx Input High Time (Note 3)                   | Tsck/2                                                                                                                                                                                                                                                   | _                   |      | ns    | _                  |  |

| SP72               | TscF                      | SCKx Input Fall Time                            | _                                                                                                                                                                                                                                                        | _                   | _    | ns    | See parameter DO32 |  |

| SP73               | TscR                      | SCKx Input Rise Time                            | _                                                                                                                                                                                                                                                        | _                   | _    | ns    | See parameter DO31 |  |

| SP30               | TDOF                      | SDOx Data Output Fall Time (Note 4)             | _                                                                                                                                                                                                                                                        | _                   | -    | ns    | See parameter DO32 |  |

| SP31               | TDOR                      | SDOx Data Output Rise Time (Note 4)             | _                                                                                                                                                                                                                                                        | _                   | _    | ns    | See parameter DO31 |  |

| SP35               | TscH2DoV,                 | SDOx Data Output Valid after                    | _                                                                                                                                                                                                                                                        | _                   | 15   | ns    | VDD > 2.7V         |  |

|                    | TscL2DoV                  | SCKx Edge                                       | _                                                                                                                                                                                                                                                        | _                   | 20   | ns    | VDD < 2.7V         |  |

| SP40               | TDIV2SCH,<br>TDIV2SCL     | Setup Time of SDIx Data Input to SCKx Edge      | 10                                                                                                                                                                                                                                                       |                     | _    | ns    | _                  |  |

| SP41               | TscH2DIL,<br>TscL2DIL     | Hold Time of SDIx Data Input to SCKx Edge       | 10                                                                                                                                                                                                                                                       |                     | _    | ns    | _                  |  |

| SP50               | TssL2scH,<br>TssL2scL     | SSx ↓ to SCKx ↑ or SCKx Input                   | 175                                                                                                                                                                                                                                                      | _                   | _    | ns    | _                  |  |

| SP51               | TssH2DoZ                  | SSx ↑ to SDOx Output<br>High-Impedance (Note 3) | 5                                                                                                                                                                                                                                                        | _                   | 25   | ns    | _                  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

- **2:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 40 ns.

- 4: Assumes 50 pF load on all SPIx pins.

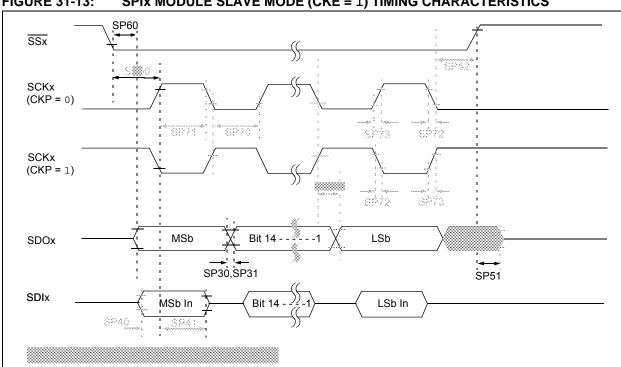

FIGURE 31-13: SPIX MODULE SLAVE MODE (CKE = 1) TIMING CHARACTERISTICS

TABLE 31-32: SPIx MODULE SLAVE MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHARACTERISTICS |                       |                                            |                                                |   |    |    |                    |  |

|--------------------|-----------------------|--------------------------------------------|------------------------------------------------|---|----|----|--------------------|--|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>             | Min. Typical <sup>(2)</sup> Max. Units Conditi |   |    |    |                    |  |

| SP70               | TscL                  | SCKx Input Low Time (Note 3)               | Tsck/2                                         | _ |    | ns | _                  |  |

| SP71               | TscH                  | SCKx Input High Time (Note 3)              | Tsck/2                                         | _ | _  | ns | _                  |  |

| SP72               | TscF                  | SCKx Input Fall Time                       | _                                              | 5 | 10 | ns | _                  |  |

| SP73               | TscR                  | SCKx Input Rise Time                       | _                                              | 5 | 10 | ns | _                  |  |

| SP30               | TDOF                  | SDOx Data Output Fall Time (Note 4)        | _                                              |   | 1  | ns | See parameter DO32 |  |

| SP31               | TDOR                  | SDOx Data Output Rise Time (Note 4)        | _                                              | _ | _  | ns | See parameter DO31 |  |

| SP35               | TscH2DoV,             | •                                          | _                                              | _ | 20 | ns | VDD > 2.7V         |  |

|                    | TscL2DoV              | SCKx Edge                                  | _                                              | _ | 30 | ns | VDD < 2.7V         |  |

| SP40               | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge | 10                                             | _ | _  | ns | _                  |  |

| SP41               | TscH2DIL,<br>TscL2DIL | Hold Time of SDIx Data Input to SCKx Edge  | 10                                             | _ | _  | ns | _                  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

- Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The minimum clock period for SCKx is 40 ns.

- 4: Assumes 50 pF load on all SPIx pins.

TABLE 31-34: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE)

| AC CHA        | RACTERIS            |                            | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)  Operating temperature $0^{\circ}\text{C} \leq \text{TA} \leq +70^{\circ}\text{C}$ for Commercial $-40^{\circ}\text{C} \leq \text{TA} \leq +85^{\circ}\text{C}$ for Industrial $-40^{\circ}\text{C} \leq \text{TA} \leq +105^{\circ}\text{C}$ for V-temp |                 |      |       |                                            |

|---------------|---------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------|-------|--------------------------------------------|

| Param.<br>No. | Symbol              | Charact                    | eristics                                                                                                                                                                                                                                                                                                                       | Min. Max. Units |      | Units | Conditions                                 |

| IS10          | S10 TLO:SCL Clock L |                            | 100 kHz mode                                                                                                                                                                                                                                                                                                                   | 4.7             | _    | μS    | PBCLK must operate at a minimum of 800 kHz |

|               |                     |                            | 400 kHz mode                                                                                                                                                                                                                                                                                                                   | 1.3             | _    | μS    | PBCLK must operate at a minimum of 3.2 MHz |

|               |                     |                            | 1 MHz mode (Note 1)                                                                                                                                                                                                                                                                                                            | 0.5             | _    | μS    | _                                          |

| IS11          | THI:SCL             | Clock High Time            | 100 kHz mode                                                                                                                                                                                                                                                                                                                   | 4.0             | _    | μS    | PBCLK must operate at a minimum of 800 kHz |

|               |                     |                            | 400 kHz mode                                                                                                                                                                                                                                                                                                                   | 0.6             | _    | μS    | PBCLK must operate at a minimum of 3.2 MHz |

|               |                     |                            | 1 MHz mode (Note 1)                                                                                                                                                                                                                                                                                                            | 0.5             | _    | μS    | _                                          |

| IS20          | TF:SCL              | SDAx and SCLx<br>Fall Time | 100 kHz mode                                                                                                                                                                                                                                                                                                                   |                 | 300  | ns    | CB is specified to be from                 |

|               |                     |                            | 400 kHz mode                                                                                                                                                                                                                                                                                                                   | 20 + 0.1 Св     | 300  | ns    | 10 to 400 pF                               |

|               |                     |                            | 1 MHz mode (Note 1)                                                                                                                                                                                                                                                                                                            | _               | 100  | ns    |                                            |

| IS21          | TR:SCL              | SDAx and SCLx<br>Rise Time | 100 kHz mode                                                                                                                                                                                                                                                                                                                   | _               | 1000 | ns    | CB is specified to be from                 |

|               |                     |                            | 400 kHz mode                                                                                                                                                                                                                                                                                                                   | 20 + 0.1 CB     | 300  | ns    | 10 to 400 pF                               |

|               |                     |                            | 1 MHz mode (Note 1)                                                                                                                                                                                                                                                                                                            | _               | 300  | ns    |                                            |

| IS25          | TSU:DAT             | Data Input<br>Setup Time   | 100 kHz mode                                                                                                                                                                                                                                                                                                                   | 250             | _    | ns    | _                                          |

|               |                     |                            | 400 kHz mode                                                                                                                                                                                                                                                                                                                   | 100             | _    | ns    |                                            |

|               |                     |                            | 1 MHz mode (Note 1)                                                                                                                                                                                                                                                                                                            | 100             | _    | ns    |                                            |

| IS26          | THD:DAT             | •                          | 100 kHz mode                                                                                                                                                                                                                                                                                                                   | 0               | _    | ns    | _                                          |