Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 51                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 128K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx370f512h-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 7: PIN NAMES FOR 124-PIN DEVICES

| 124               | -PIN VTLA (BOTTOM VIEW) <sup>(1,2,3,4)</sup>                             | 17       |                   |          |            | A        | 34                        |

|-------------------|--------------------------------------------------------------------------|----------|-------------------|----------|------------|----------|---------------------------|

|                   | A                                                                        | 17       | l                 | B13      | B29        |          | Conductive<br>Thermal Pad |

|                   | PIC32MX430F064L<br>PIC32MX450F128L<br>PIC32MX450F256L<br>PIC32MX470F512L |          |                   | B1<br>Bt | 56         | B41      | A51                       |

|                   |                                                                          |          | A1                |          |            |          |                           |

|                   | Polarit                                                                  | y Indica | ator              | A        | 68         |          |                           |

| Package<br>Bump # | Full Pin Name                                                            |          | Package<br>Bump # |          |            | Full Pin | Name                      |

| A1                | No Connect                                                               |          | A38               | D-       |            |          |                           |

| A2                | RG15                                                                     |          | A39               | SCL2/F   | RA2        |          |                           |

| A3                | Vss                                                                      |          | A40               | TDI/CT   | ED9/RA4    |          |                           |

| A4                | AN23/PMD6/RE6                                                            |          | A41               | Vdd      |            |          |                           |

| A5                | RPC1/RC1                                                                 |          | A42               |          | CLKO/RC15  |          |                           |

| A6                | RPC3/RC3                                                                 |          | A43               | Vss      |            |          |                           |

| A7                | AN16/C1IND/RPG6/SCK2/PMA5/RG6                                            |          | A44               | SDA1/F   | RPA15/RA15 | 5        |                           |

| A8                | AN18/C2IND/RPG8/PMA3/RG8                                                 |          | A45               | RPD9/F   | 209        |          |                           |

| A9                | AN19/C2INC/RPG9/PMA2/RG9                                                 |          | A46               |          | PMCS1/RD   | 11       |                           |

| A10               | VDD                                                                      |          | A47               |          | RPC13/RC   |          |                           |

| A11               | RPE8/RE8                                                                 |          | A48               | VDD      |            |          |                           |

| A12               | AN5/C1INA/RPB5/VBUSON/RB5                                                |          | A49               | No Cor   | nect       |          |                           |

| A13               | PGED3/AN3/C2INA/RPB3/RB3                                                 |          | A50               | No Cor   |            |          |                           |

| A14               | VDD                                                                      |          | A51               | No Cor   | nect       |          |                           |

| A15               | PGEC1/AN1/RPB1/CTED12/RB1                                                |          | A52               |          | RPD1/RD1   |          |                           |

| A16               | No Connect                                                               |          | A53               | AN26/F   | RPD3/RD3   |          |                           |

| A17               | No Connect                                                               |          | A54               | PMD13    |            |          |                           |

| A18               | No Connect                                                               |          | A55               | -        | PMRD/RD5   |          |                           |

| A19               | No Connect                                                               |          | A56               | PMD15    | -          |          |                           |

| A20               | PGEC2/AN6/RPB6/RB6                                                       |          | A50<br>A57        | No Cor   |            |          |                           |

| A20<br>A21        | VREF-/CVREF-/PMA7/RA9                                                    | _        |                   | No Cor   |            |          |                           |

| A21<br>A22        | AVDD                                                                     | _        | A58<br>A59        | VDD      |            |          |                           |

| A22<br>A23        | AN8/RPB8/CTED10/RB8                                                      | $\dashv$ | A59<br>A60        |          | MD10/RF1   |          |                           |

| A23<br>A24        | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                    | _        | A60<br>A61        | -        | PMD8/RG0   |          |                           |

| A24<br>A25        | Vss                                                                      | _        | A61<br>A62        |          | TED8/RA7   |          |                           |

| A25               | TCK/CTED2/RA1                                                            | _        | A62               | Vss      |            |          |                           |

| A20               | RPF12/RF12                                                               |          | A64               | PMD1/    | RF1        |          |                           |

| A28               | AN13/PMA10/RB13                                                          | $\dashv$ | A65               | TRD1/F   |            |          |                           |

| A29               | AN15/RPB15/OCFB/CTED6/PMA0/RB15                                          | -        | A66               |          | MD2/RE2    |          |                           |

| A30               | VDD                                                                      |          | A67               | _        | MD2/RE2    |          |                           |

| A31               | RPD15/RD15                                                               | -        | A68               | No Cor   |            |          |                           |

| A32               | RPF5/PMA8/RF5                                                            |          | B1                | VDD      |            |          |                           |

| A33               | No Connect                                                               | $\dashv$ | B1<br>B2          |          | RPE5/PMD5  | /RE5     |                           |

| A33<br>A34        | No Connect                                                               | _        | B2<br>B3          | -        | MD7/RE7    |          |                           |

| A34<br>A35        | USBID/RF3                                                                | _        | B3<br>B4          | RPC2/F   |            |          |                           |

| A35<br>A36        | RPF2/RF2                                                                 | _        |                   |          | CTED7/RC4  |          |                           |

| 700               |                                                                          | 1        | B5                |          |            |          |                           |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: Shaded package bumps are 5V tolerant.

4: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

# PIC32MX330/350/370/430/450/470

NOTES:

## 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

## 2.1 Basic Connection Requirements

Getting started with the PIC32MX330/350/370/430/ 450/470 family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.8 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

## 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 31:24        | BMXPFMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22:16        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 15:8         | BMXPFMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 7:0          |                   |                   |                   | BMXPF             | MSZ<7:0>          |                   |                  |                  |  |  |  |

## REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

## Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes: 0x00010000 = Device has 64 KB Flash 0x00020000 = Device has 128 KB Flash 0x00040000 = Device has 256 KB Flash 0x00080000 = Device has 512 KB Flash

## REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

|              |                   |                   |                   | . ,               |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 24.24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 31:24        | BMXBOOTSZ<31:24>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 23:16        | BMXBOOTSZ<23:16>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 15:8         |                   |                   |                   | BMXBOC            | )TSZ<15:8>        |                   |                  |                  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 7:0          |                   |                   |                   | BMXBO             | OTSZ<7:0>         |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 **BMXBOOTSZ<31:0>:** Boot Flash Memory (BFM) Size bits Static value that indicates the size of the Boot PFM in bytes: 0x00003000 = Device has 12 KB Boot Flash

## TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 3 REGISTER MAP (CONTINUED)

| ess                         |                                 | Ċ,                |        | Bits  |       |       |        |       |      |        |         |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|-------------------|--------|-------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range         | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH2CPTR                        | 31:16             | —      | _     | —     | —     |        | —     | —    | —      | _       | —      | —      | _      | _      | _      | —      | —      | 0000       |

| 0200                        | DONZOLIK                        | 15:0 CHCPTR<15:0> |        |       |       |       |        |       |      | 0000   |         |        |        |        |        |        |        |        |            |

| 3290                        | DCH2DAT                         | 31:16             | —      | —     | —     | _     | —      | _     | —    | —      | _       | —      | —      | —      | _      | _      | —      | _      | 0000       |

| 3290                        | DCHZDAI                         | 15:0              | -      |       | _     | —     | —      |       | —    | _      |         |        |        | CHPDA  | T<7:0> |        |        |        | 0000       |

| 32A0                        | DCH3CON                         | 31:16             | _      | _     | _     | —     | _      |       | _    | _      | _       |        | _      | _      |        | _      | _      | —      | 0000       |

| 32AU                        | DCH3CON                         | 15:0              | CHBUSY | -     | —     | —     | —      | -     | _    | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | -      | CHEDET | CHPR   | l<1:0> | 0000       |

| 32B0                        | DCH3ECON                        | 31:16             | —      | —     | —     | —     | _      | _     | —    | —      |         |        |        | CHAIR  | Q<7:0> |        |        |        | 00FF       |

| 0200                        | DONOLOON                        | 15:0              |        |       |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN | _      | —      | —      | FFF8       |

| 32C0                        | DCH3INT                         | 31:16             | _      | —     | _     | —     | —      | _     | _    | _      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE |            |

| 0200                        | 2 0110111                       | 15:0              | —      | —     | —     | —     | —      | _     | —    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF |            |

| 32D0                        | DCH3SSA                         | 31:16             |        |       |       |       |        |       |      | CHSSA  | <31:0>  |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0              |        |       |       |       |        |       |      |        |         |        |        |        |        |        |        |        | 0000       |

| 32E0                        | DCH3DSA                         | 31:16<br>15:0     |        |       |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16             | _      | _     | _     |       |        | _     | _    |        |         | _      | _      |        | _      |        |        |        | 0000       |

| 32F0                        | DCH3SSIZ                        | 15:0              |        |       |       |       |        |       |      | CHSSIZ | 2<15:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16             | _      | _     | _     | _     |        | _     |      | _      | _       | _      | _      | _      | _      | _      |        |        | 0000       |

| 3300                        | DCH3DSIZ                        | 15:0              |        |       |       |       |        |       |      | CHDSIZ | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 0040                        | DOLIGODTO                       | 31:16             | _      | _     | —     | _     | _      | _     | _    | —      | _       | _      | —      | _      | _      | _      | _      |        | 0000       |

| 3310                        | DCH3SPTR                        | 15:0              |        |       |       |       |        |       |      | CHSPT  | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 2220                        | DCH3DPTR                        | 31:16             | —      | —     | —     | —     | _      | —     | _    | —      | —       | —      | —      | —      | —      | —      | _      | _      | 0000       |

| 3320                        | DCH3DFTK                        | 15:0              |        |       | -     |       |        |       | -    | CHDPT  | R<15:0> |        | _      |        |        |        | -      |        | 0000       |

| 3330                        | DCH3CSIZ                        | 31:16             | —      | —     | —     | —     | _      | _     | —    | —      | —       | —      | —      | _      | —      | —      | —      | —      | 0000       |

| 0000                        | DOLIDOOIT                       | 15:0              |        |       |       |       |        |       |      | CHCSIZ | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3340                        | DCH3CPTR                        | 31:16             | —      | —     | —     | —     | —      | —     | —    | —      | —       | —      | —      | _      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0              |        |       |       |       |        |       |      | CHCPT  | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 3350                        | DCH3DAT                         | 31:16             | _      | —     | —     |       | _      | —     | —    |        | _       | —      | —      |        | —      | —      | —      |        | 0000       |

|                             |                                 | 15:0              | —      | —     | —     | —     | —      | —     | —    | —      |         |        |        | CHPDA  | 1<7:0> |        |        |        | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Note 1:

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | DCRCDATA<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | DCRCDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   | DCRCDATA<7:0>     |                   |                   |                   |                   |                  |                  |  |  |  |  |

## REGISTER 10-5: DCRCDATA: DMA CRC DATA REGISTER

## Legend:

| Legena:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

## bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

## REGISTER 10-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | 4 DCRCXOR<31:24>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   |                   |                   | DCRCXO            | R<7:0>            |                   |                  |                  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

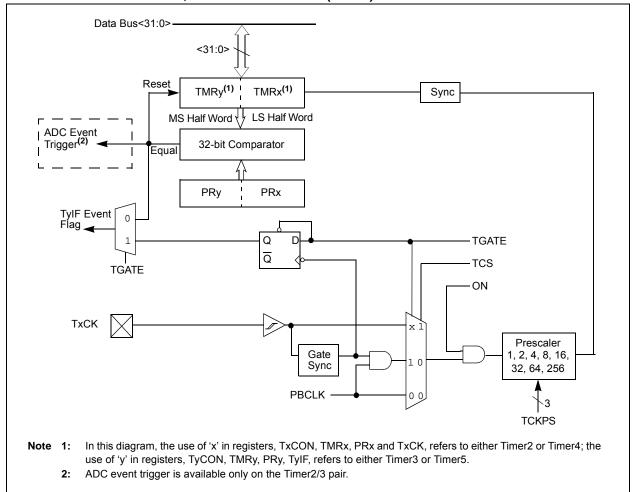

## FIGURE 14-2: TIMER2/3, 4/5 BLOCK DIAGRAM (32-BIT)<sup>(1)</sup>

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0 |  |  |  |

|--------------|----------------------|-------------------|---------------------|-------------------|--------------------|-------------------|--------------------|------------------|--|--|--|

| 31:24        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |

| 31.24        | —                    |                   | _                   | _                 |                    |                   | _                  | _                |  |  |  |

| 00.40        | U-0                  | U-0               | U-0                 | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |

| 23:16        | —                    | -                 | —                   | —                 | -                  | —                 | —                  | —                |  |  |  |

| 45.0         | R/W-0                | U-0               | R/W-0               | U-0               | U-0                | U-0               | U-0                | U-0              |  |  |  |

| 15:8         | ON <sup>(1,3)</sup>  | _                 | SIDL <sup>(4)</sup> | —                 | _                  | _                 | —                  | —                |  |  |  |

| 7.0          | R/W-0                | R/W-0             | R/W-0               | R/W-0             | R/W-0              | U-0               | R/W-0              | U-0              |  |  |  |

| 7:0          | TGATE <sup>(3)</sup> | Т                 | CKPS<2:0>(3         | 3)                | T32 <sup>(2)</sup> |                   | TCS <sup>(3)</sup> | _                |  |  |  |

## REGISTER 14-1: TxCON: TYPE B TIMER CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

## bit 31-16 **Unimplemented:** Read as '0'

- bit 15 **ON:** Timer On bit<sup>(1,3)</sup>

- 1 = Module is enabled

- 0 = Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit<sup>(4)</sup>

- 1 = Discontinue operation when device enters Idle mode 0 = Continue operation even in Idle mode

### bit 12-8 Unimplemented: Read as '0'

- bit 7 **TGATE:** Timer Gated Time Accumulation Enable bit<sup>(3)</sup>

- When TCS = 1:

This bit is ignored and is read as '0'.

When TCS = 0:

- 1 = Gated time accumulation is enabled

- 0 = Gated time accumulation is disabled

### bit 6-4 TCKPS<2:0>: Timer Input Clock Prescale Select bits<sup>(3)</sup>

- 111 = 1:256 prescale value

- 110 = 1:64 prescale value

- 101 = 1:32 prescale value

- 100 = 1:16 prescale value

- 011 = 1:8 prescale value

- 010 = 1:4 prescale value

- 001 = 1:2 prescale value

- 000 = 1:1 prescale value

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3 and Timer5). All timer functions are set through the even numbered timers.

- 4: While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

## REGISTER 18-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)

- bit 4 **DISSDI:** Disable SDI bit 1 = SDI pin is not used by the SPI module (pin is controlled by PORT function)

- 0 = SDI pin is controlled by the SPI module

- bit 3-2 STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

## REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER (CONTINUED)

| <ul> <li>1 = Indicates that a Stop bit has been detected last         0 = Stop bit was not detected last         Hardware set or clear when Start, Repeated Start or Stop detected.     </li> <li>5: Start bit         1 = Indicates that a Start (or Repeated Start) bit has been detected last         0 = Start bit was not detected last         Hardware set or clear when Start, Repeated Start or Stop detected.     </li> <li>bit 2         R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave)         1 = Read – indicates data transfer is output from slave         0 = Write – indicates data transfer is input to slave         Hardware set or clear after reception of I<sup>2</sup>C device address byte.     </li> <li>bit 1         RBF: Receive Buffer Full Status bit         1 = Receive complete, I2CxRCV is full         0 = Receive not complete, I2CxRCV is empty         Hardware set when I2CxRCV is written with received byte. Hardware clear when software         reads I2CxRCV.     </li> <li>bit 0         TBF: Transmit Buffer Full Status bit         1 = Transmit in progress         I2CxTRN is full         </li> </ul> | bit 4 | P: Stop bit                                                                       |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|-----------------------------------------------------------------------------------|

| <ul> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>bit 3 S: Start bit <ol> <li>= Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>= Start bit was not detected last</li> <li>Hardware set or clear when Start, Repeated Start or Stop detected.</li> </ol> </li> <li>bit 2 R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave) <ol> <li>= Read – indicates data transfer is output from slave</li> <li>Write – indicates data transfer is input to slave</li> <li>Write – indicates data transfer is of I<sup>2</sup>C device address byte.</li> </ol> </li> <li>bit 1 RBF: Receive Buffer Full Status bit <ol> <li>= Receive not complete, I2CxRCV is full</li> <li>= Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ol> </li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                         |       | 1 = Indicates that a Stop bit has been detected last                              |

| bit 3       S: Start bit         1 = Indicates that a Start (or Repeated Start) bit has been detected last         0 = Start bit was not detected last         Hardware set or clear when Start, Repeated Start or Stop detected.         bit 2       R_W: Read/Write Information bit (when operating as I <sup>2</sup> C slave)         1 = Read – indicates data transfer is output from slave         0 = Write – indicates data transfer is input to slave         Hardware set or clear after reception of I <sup>2</sup> C device address byte.         bit 1       RBF: Receive Buffer Full Status bit         1 = Receive complete, I2CxRCV is full       0 = Receive not complete, I2CxRCV is empty         Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.         bit 0       TBF: Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                  |       |                                                                                   |

| <ul> <li>1 = Indicates that a Start (or Repeated Start) bit has been detected last</li> <li>0 = Start bit was not detected last<br/>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>bit 2 R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave<br/>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 RBF: Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty<br/>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br/>reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                   |       | Hardware set or clear when Start, Repeated Start or Stop detected.                |

| <ul> <li>0 = Start bit was not detected last<br/>Hardware set or clear when Start, Repeated Start or Stop detected.</li> <li>bit 2 R_W: Read/Write Information bit (when operating as I<sup>2</sup>C slave)         <ol> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> </ol> </li> <li>bit 1 RBF: Receive Buffer Full Status bit         <ol> <li>= Receive complete, I2CxRCV is full</li> <li>= Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> </ol> </li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                            | bit 3 | S: Start bit                                                                      |

| bit 2 <b>R_W:</b> Read/Write Information bit (when operating as I²C slave)1 = Read – indicates data transfer is output from slave0 = Write – indicates data transfer is input to slaveHardware set or clear after reception of I²C device address byte.bit 1 <b>RBF:</b> Receive Buffer Full Status bit1 = Receive complete, I2CxRCV is full0 = Receive not complete, I2CxRCV is emptyHardware set when I2CxRCV is written with received byte. Hardware clear when softwarebit 0 <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |       |                                                                                   |

| <ul> <li>1 = Read – indicates data transfer is output from slave</li> <li>0 = Write – indicates data transfer is input to slave</li> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 RBF: Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |       | Hardware set or clear when Start, Repeated Start or Stop detected.                |

| <ul> <li>0 = Write – indicates data transfer is input to slave<br/>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 <b>RBF:</b> Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty<br/>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br/>reads I2CxRCV.</li> <li>bit 0 <b>TBF:</b> Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 2 | <b>R_W:</b> Read/Write Information bit (when operating as I <sup>2</sup> C slave) |

| <ul> <li>Hardware set or clear after reception of I<sup>2</sup>C device address byte.</li> <li>bit 1 <b>RBF:</b> Receive Buffer Full Status bit</li> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> <li>bit 0 <b>TBF:</b> Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |       | 1 = Read – indicates data transfer is output from slave                           |

| bit 1 <b>RBF:</b> Receive Buffer Full Status bit         1 = Receive complete, I2CxRCV is full         0 = Receive not complete, I2CxRCV is empty         Hardware set when I2CxRCV is written with received byte. Hardware clear when software         reads I2CxRCV.         bit 0 <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |       |                                                                                   |

| <ul> <li>1 = Receive complete, I2CxRCV is full</li> <li>0 = Receive not complete, I2CxRCV is empty</li> <li>Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | Hardware set or clear after reception of I <sup>2</sup> C device address byte.    |

| <ul> <li>0 = Receive not complete, I2CxRCV is empty<br/>Hardware set when I2CxRCV is written with received byte. Hardware clear when software<br/>reads I2CxRCV.</li> <li>bit 0 TBF: Transmit Buffer Full Status bit</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | bit 1 | RBF: Receive Buffer Full Status bit                                               |

| Hardware set when I2CxRCV is written with received byte. Hardware clear when software reads I2CxRCV.         bit 0 <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |       | 1 = Receive complete, I2CxRCV is full                                             |

| reads I2CxRCV.<br>bit 0 <b>TBF:</b> Transmit Buffer Full Status bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |       | 0 = Receive not complete, I2CxRCV is empty                                        |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       |                                                                                   |

| 1 = Transmit in progress I2CxTRN is full                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | bit 0 | TBF: Transmit Buffer Full Status bit                                              |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |       | 1 = Transmit in progress, I2CxTRN is full                                         |

| 0 = Transmit complete, I2CxTRN is empty                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |       | 0 = Transmit complete, I2CxTRN is empty                                           |

Hardware set when software writes I2CxTRN. Hardware clear at completion of data transmission.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | —                | —                |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | —                 | _                 | -                 | —                 | _                 | _                 | —                | —                |  |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |  |

| 15:8         | IBF               | IBOV              | _                 | —                 | IB3F              | IB2F              | IB1F             | IB0F             |  |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |  |

| 7:0          | OBE               | OBUF              |                   | _                 | OB3E              | OB2E              | OB1E             | OB0E             |  |

## REGISTER 21-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | HS = Set by Hardware | SC = Cleared by software  |                    |

|-------------------|----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 IBF: Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)0 = No overflow occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 IBxF: Input Buffer 'x' Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31:24        | -                 | —                 | —                 | —                 | _                 | _                 |                  | —                |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23:16        | -                 | —                 | —                 | —                 | _                 | _                 |                  | —                |  |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.0         | -                 | —                 | SIDL              | —                 | _                 | _                 |                  | —                |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0              |  |

| 7:0          |                   | _                 |                   |                   |                   |                   | C2OUT            | C1OUT            |  |

## REGISTER 24-2: CMSTAT: COMPARATOR STATUS REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

### bit 31-14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in IDLE Control bit

1 = All Comparator modules are disabled in IDLE mode

0 = All Comparator modules continue to operate in the IDLE mode

- bit 12-2 Unimplemented: Read as '0'

- bit 1 **C2OUT:** Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

## bit 0 C1OUT: Comparator Output bit

- 1 = Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2            | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------------------|------------------|------------------|

| 04.04        | r-1                   | r-1               | r-1               | r-1               | r-1               | r-1                          | r-1              | r-1              |

| 31:24        |                       | _                 | _                 | _                 | _                 | —                            | _                | —                |

| 00.40        | r-1                   | r-1               | r-1               | r-1               | r-1               | R/P                          | R/P              | R/P              |

| 23:16        |                       | —                 | _                 | _                 | _                 | FPLLODIV<2:0>                |                  |                  |

| 45.0         | R/P                   | r-1               | r-1               | r-1               | r-1               | R/P                          | R/P              | R/P              |

| 15:8         | UPLLEN <sup>(1)</sup> | _                 | _                 | _                 | _                 | UPLLIDIV<2:0> <sup>(1)</sup> |                  |                  |

| 7:0          | r-1                   | R/P-1             | R/P               | R/P-1             | r-1               | R/P                          | R/P              | R/P              |

|              | _                     | FPLLMUL<2:0>      |                   |                   | _                 | F                            | PLLIDIV<2:0      | >                |

#### **DEVCFG2: DEVICE CONFIGURATION WORD 2 REGISTER 28-3:**

| Legend:           | r = Reserved bit | P = Programmable bit      |                    |  |

|-------------------|------------------|---------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

### bit 31-19 Reserved: Write '1'

bit 15

bit 7

bit 18-16 FPLLODIV<2:0>: Default PLL Output Divisor bits

- 111 = PLL output divided by 256 110 = PLL output divided by 64 101 = PLL output divided by 32 100 = PLL output divided by 16 011 = PLL output divided by 8 010 = PLL output divided by 4 001 = PLL output divided by 2 000 = PLL output divided by 1 UPLLEN: USB PLL Enable bit<sup>(1)</sup> 1 = Disable and bypass USB PLL 0 = Enable USB PLL bit 14-11 Reserved: Write '1' bit 10-8 UPLLIDIV<2:0>: USB PLL Input Divider bits<sup>(1)</sup> 111 = 12x divider 110 = 10x divider 101 = 6x divider100 = 5x divider 011 = 4x divider 010 = 3x divider 001 = 2x divider 000 = 1x dividerReserved: Write '1' bit 6-4 FPLLMUL<2:0>: PLL Multiplier bits 111 = 24x multiplier 110 = 21x multiplier 101 = 20x multiplier 100 = 19x multiplier 011 = 18x multiplier 010 = 17x multiplier 001 = 16x multiplier 000 = 15x multiplier

- bit 3 Reserved: Write '1'

Note 1: This bit is available on PIC32MX4XX devices only.

## 29.0 INSTRUCTION SET

The PIC32MX330/350/370/430/450/470 family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

Note: Refer to "MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set" at www.imgtec.com for more information.

## 31.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX330/350/370/430/450/470 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MX330/350/370/430/450/470 devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

## **Absolute Maximum Ratings**

## (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +105°C           |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             |                          |

| Voltage on VDD with respect to Vss                                              |                          |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 2.3V$ (Note 3) | -0.3V to +6.0V           |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | -0.3V to +5.5V           |

| Maximum current out of Vss pin(s)                                               | 200 mA                   |

| Maximum current into VDD pin(s) (Note 2)                                        | 200 mA                   |

| Maximum output current sourced/sunk by any 4x I/O pin                           | 15 mA                    |

| Maximum output current sourced/sunk by any 8x I/O pin                           | 25 mA                    |

| Maximum current sunk by all ports                                               | 150 mA                   |

| Maximum current sourced by all ports (Note 2)                                   | 150 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

- 3: See the "Device Pin Tables" section for the 5V tolerant pins.

| DC CHARACTERISTICS |        |                                                                     | $\begin{tabular}{lllllllllllllllllllllllllllllllllll$ |         |       |       |            |  |

|--------------------|--------|---------------------------------------------------------------------|-------------------------------------------------------|---------|-------|-------|------------|--|

| Param.<br>No.      | Symbol | Characteristics                                                     | Min.                                                  | Typical | Max.  | Units | Conditions |  |

| Operating Voltage  |        |                                                                     |                                                       |         |       |       |            |  |

| DC10               | Vdd    | Supply Voltage                                                      | 2.3                                                   | _       | 3.6   | V     | —          |  |

| DC12               | Vdr    | RAM Data Retention Voltage (Note 1)                                 | 1.75                                                  | —       | _     | V     | _          |  |

| DC16               | VPOR   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal    | 1.75                                                  | _       | 2.1   | V     | _          |  |

| DC17               | SVDD   | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal | 0.00005                                               | _       | 0.115 | V/µs  | _          |  |

## TABLE 31-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

# PIC32MX330/350/370/430/450/470

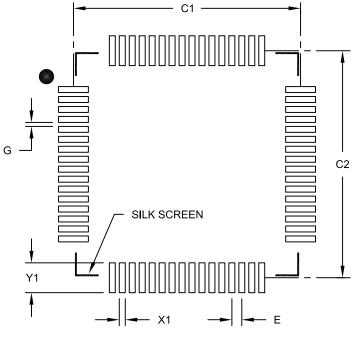

64-Lead Plastic Thin Quad Flatpack (PT) 10x10x1 mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging