Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Detelle                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Details                    |                                                                                 |

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 51                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EPROM Size                 | -                                                                               |

| RAM Size                   | 128K x 8                                                                        |

| /oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx370f512ht-v-mr |

#### 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming™ (ICSP™) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB® ICD 3 or MPLAB REAL ICE™.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site

- "Using MPLAB® ICD 3" (poster) DS50001765

- "MPLAB® ICD 3 Design Advisory" DS50001764

- "MPLAB® REAL ICE™ In-Circuit Debugger User's Guide" DS50001616

- "Using MPLAB® REAL ICE™ Emulator" (poster) DS50001749

#### 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

#### 2.7 Trace

The trace pins can be connected to a hardware trace-enabled programmer to provide a compressed real-time instruction trace. When used for trace, the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

#### 2.8 External Oscillator Pins

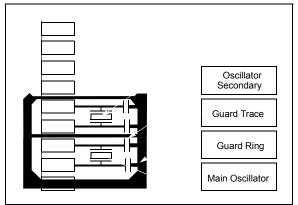

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

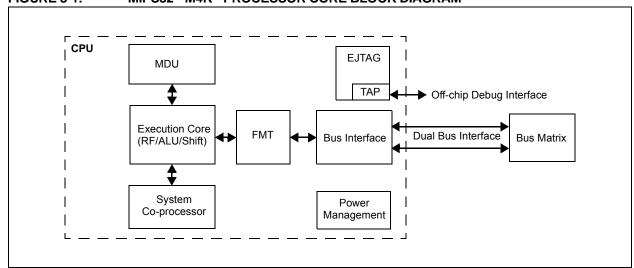

#### 3.0 CPU

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at http://www.imgtec.com.

The the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX330/350/370/430/450/470 device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

#### 3.1 Features

- · 5-stage pipeline

- · 32-bit address and data paths

- MIPS32® Enhanced Architecture (Release 2):

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> Code Compression:

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) Mechanism:

- · Simple Dual Bus Interface:

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- Autonomous Multiply/Divide Unit (MDU):

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (rs) sign extension-dependent)

- · Power Control:

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- · EJTAG Debug and Instruction Trace:

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

FIGURE 3-1: MIPS32® M4K® PROCESSOR CORE BLOCK DIAGRAM

## 7.1 Interrupts Control Registers

### TABLE 7-2: INTERRUPT REGISTER MAP

| ess                         |                  |               |        |        |         |         |             |         |            | Bits    |          |                       |                       |                      |           |                      |        |        |               |

|-----------------------------|------------------|---------------|--------|--------|---------|---------|-------------|---------|------------|---------|----------|-----------------------|-----------------------|----------------------|-----------|----------------------|--------|--------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range     | 31/15  | 30/14  | 29/13   | 28/12   | 27/11       | 26/10   | 25/9       | 24/8    | 23/7     | 22/6                  | 21/5                  | 20/4                 | 19/3      | 18/2                 | 17/1   | 16/0   | All<br>Resets |

| 1000                        | INTCON           | 31:16         | _      | _      | _       | _       |             | 1       | _          | 1       | _        | _                     | _                     | _                    | _         | _                    | _      | SS0    | 0000          |

| 1000                        | INTCON           | 15:0          | _      | _      | _       | MVEC    | -           |         | TPC<2:0>   |         | _        | _                     | _                     | INT4EP               | INT3EP    | INT2EP               | INT1EP | INT0EP | 0000          |

| 1010                        | INTSTAT          | 31:16         | _      | _      | _       | _       | _           |         | _          | _       | _        | _                     | _                     | _                    | _         | _                    | _      | _      | 0000          |

| 1010                        |                  | 15:0          | _      | _      | _       | _       | _           |         | SRIPL<2:0> |         | _        | _                     |                       |                      | VEC<5:    | )>                   |        |        | 0000          |

| 1020                        | IPTMR            | 31:16<br>15:0 |        |        |         |         |             |         |            | IPTMR<3 | 31:0>    |                       |                       |                      |           |                      |        |        | 0000          |

| 4000                        | IFS0             | 31:16         | FCEIF  | RTCCIF | FSCMIF  | AD1IF   | OC5IF       | IC5IF   | IC5EIF     | T5IF    | INT4IF   | OC4IF                 | IC4IF                 | IC4EIF               | T4IF      | INT3IF               | OC3IF  | IC3IF  | 0000          |

| 1030                        | IF50             | 15:0          | IC3EIF | T3IF   | INT2IF  | OC2IF   | IC2IF       | IC2EIF  | T2IF       | INT1IF  | OC1IF    | IC1IF                 | IC1EIF                | T1IF                 | INT0IF    | CS1IF                | CS0IF  | CTIF   | 0000          |

| 1010                        | IE04             | 31:16         | U3RXIF | U3EIF  | I2C2MIF | I2C2SIF | I2C2BIF     | U2TXIF  | U2RXIF     | U2EIF   | SPI2TXIF | SPI2RXIF              | SPI2EIF               | PMPEIF               | PMPIF     | CNGIF                | CNFIF  | CNEIF  | 0000          |

| 1040                        | IFS1             | 15:0          | CNDIF  | CNCIF  | CNBIF   | CNAIF   | I2C1MIF     | I2C1SIF | I2C1BIF    | U1TXIF  | U1RXIF   | U1EIF                 | SPI1TXIF              | SPI1RXIF             | SPI1EIF   | USBIF <sup>(2)</sup> | CMP2IF | CMP1IF | 0000          |

| 1050                        | IFS2             | 31:16         | _      | _      | _       | _       | _           | _       | _          | _       | _        | _                     | _                     | _                    | _         | _                    | _      | _      | 0000          |

| 1050                        | IF52             | 15:0          | _      | _      | _       | _       | DMA3IF      | DMA2IF  | DMA1IF     | DMA0IF  | CTMUIF   | U5TXIF <sup>(1)</sup> | U5RXIF <sup>(1)</sup> | U5EIF <sup>(1)</sup> | U4TXIF    | U4RXIF               | U4EIF  | U3TXIF | 0000          |

| 1060                        | IEC0             | 31:16         | FCEIE  | RTCCIE | FSCMIE  | AD1IE   | OC5IE       | IC5IE   | IC5EIE     | T5IE    | INT4IE   | OC4IE                 | IC4IE                 | IC4EIE               | T4IE      | INT3IE               | OC3IE  | IC3IE  | 0000          |

| 1000                        | IECU             | 15:0          | IC3EIE | T3IE   | INT2IE  | OC2IE   | IC2IE       | IC2EIE  | T2IE       | INT1IE  | OC1IE    | IC1IE                 | IC1EIE                | T1IE                 | INT0IE    | CS1IE                | CS0IE  | CTIE   | 0000          |

| 1070                        | IEC1             | 31:16         | U3RXIE | U3EIE  | I2C2MIE | I2C2SIE | I2C2BIE     | U2TXIE  | U2RXIE     | U2EIE   | SPI2TXIE | SPI2RXIE              | SPI2EIE               | PMPEIE               | PMPIE     | CNGIE                | CNFIE  | CNEIE  | 0000          |

| 1070                        | IECT             | 15:0          | CNDIE  | CNCIE  | CNBIE   | CNAIE   | I2C1MIE     | I2C1SIE | I2C1BIE    | U1TXIE  | U1RXIE   | U1EIE                 | SPI1TXIE              | SPI1RXIE             | SPI1EIE   | USBIE <sup>(2)</sup> | CMP2IE | CMP1IE | 0000          |

| 1080                        | IEC2             | 31:16         |        | _      | _       | -       | -           | _       | _          | _       | _        | _                     | _                     | _                    | _         | _                    | _      | _      | 0000          |

| 1000                        | IECZ             | 15:0          |        | _      | _       | -       | DMA3IE      | DMA2IE  | DMA1IE     | DMA0IE  | CTMUIE   | U5TXIE <sup>(1)</sup> | U5RXIE <sup>(1)</sup> | U5EIE <sup>(1)</sup> | U4TXIE    | U4RXIE               | U4EIE  | U3TXIE | 0000          |

| 1090                        | IPC0             | 31:16         |        | _      | _       |         | INT0IP<2:0> |         | INT0IS     | <1:0>   | _        | _                     | _                     | С                    | S1IP<2:0> |                      | CS1IS  | S<1:0> | 0000          |

| 1090                        | IFCU             | 15:0          | _      | _      | _       |         | CS0IP<2:0>  |         | CS0IS      | <1:0>   | _        | _                     | _                     | (                    | CTIP<2:0> |                      | CTIS   | <1:0>  | 0000          |

| 10A0                        | IPC1             | 31:16         |        | _      | _       |         | INT1IP<2:0> |         | INT1IS     | <1:0>   | _        | _                     | _                     | О                    | C1IP<2:0> |                      | OC1IS  | S<1:0> | 0000          |

| IUAU                        | IPC1             | 15:0          |        | _      | _       |         | IC1IP<2:0>  |         | IC1IS      | <1:0>   | _        | _                     | _                     | -                    | T1IP<2:0> |                      | T1IS   | <1:0>  | 0000          |

| 4000                        | IDCO             | 31:16         |        | _      | _       |         | INT2IP<2:0> |         | INT2IS     | <1:0>   | _        | _                     | _                     | О                    | C2IP<2:0> |                      | OC2IS  | S<1:0> | 0000          |

| 10B0                        | IPC2             | 15:0          | _      | _      | _       |         | IC2IP<2:0>  |         | IC2IS      | <1:0>   | _        | _                     | _                     | -                    | T2IP<2:0> |                      | T2IS   | <1:0>  | 0000          |

| 10C0                        | IPC3             | 31:16         | _      | _      | _       |         | INT3IP<2:0> |         | INT3IS     | <1:0>   | _        | _                     | _                     | О                    | C3IP<2:0> |                      | OC3IS  | S<1:0> | 0000          |

| 1000                        | IPC3             | 15:0          | _      | _      | _       |         | IC3IP<2:0>  |         | IC3IS      | <1:0>   | _        | _                     | _                     | -                    | T3IP<2:0> |                      | T3IS   | <1:0>  | 0000          |

| 1000                        | IDC4             | 31:16         | _      | _      | _       |         | INT4IP<2:0> |         | INT4IS     | <1:0>   | _        | _                     | _                     | О                    | C4IP<2:0> |                      | OC4IS  | S<1:0> | 0000          |

| 10D0                        | IPC4             | 15:0          | _      | _      | _       |         | IC4IP<2:0>  |         | IC4IS<     | <1:0>   | _        | _                     | _                     | -                    | T4IP<2:0> |                      | T4IS   | <1:0>  | 0000          |

| 1050                        | IDCE             | 31:16         | _      | _      | _       |         | AD1IP<2:0>  |         | AD1IS      | <1:0>   | _        | _                     | _                     | О                    | C5IP<2:0> |                      | OC5IS  | S<1:0> | 0000          |

| 10E0                        | IPC5             | 15:0          | _      | _      | _       |         | IC5IP<2:0>  |         | IC5IS<     | <1:0>   | _        | _                     | _                     | -                    | T5IP<2:0> |                      | T5IS-  | <1:0>  | 0000          |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on 100-pin devices.

2: This bit is only implemented on devices with a USB module.

| O   |

|-----|

| S   |

| 8   |

| 2   |

| 8   |

| FF  |

| င္က |

| ğ   |

| 9   |

| ű   |

|     |

| TARIF 10-3. | DMA CHANNEL   | <b>0 THROUGH CHANNEL</b> | 3 REGISTER MAP |

|-------------|---------------|--------------------------|----------------|

| IADLL IU-J. | DIVIA CHANNEL | U IIINOUGII CHAMME       | JILGIJILK WAF  |

| ess                         |                                 |               | Bits   |       |       |       |        |       |      |                                        |               |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------|-------|-------|-------|--------|-------|------|----------------------------------------|---------------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8                                   | 23/7          | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

| 0000                        | DOLLOCON                        | 31:16         | _      | _     | _     | _     |        | _     | _    | _                                      | _             | _      | _      |        | _      | _      | _      | _      | 0000       |

| 3060                        | DCH0CON                         | 15:0          | CHBUSY | _     | _     | _     | -      | _     | _    | CHCHNS                                 | CHEN          | CHAED  | CHCHN  | CHAEN  | _      | CHEDET | CHPR   | I<1:0> | 0000       |

| 3070 [                      | DCH0ECON                        | 31:16         | _      | _     | _     | _     | -      | _     | _    | _                                      |               |        |        | CHAIR  | Q<7:0> |        |        |        | 00FF       |

| 3070                        | DCHOLCON                        | 15:0          |        |       |       | CHSIR | Q<7:0> |       |      |                                        | CFORCE        | CABORT | PATEN  | SIRQEN | AIRQEN | _      | _      | _      | FFF8       |

| 3080                        | DCH0INT                         | 31:16         | _      |       | _     | _     | _      | _     | _    | _                                      | CHSDIE        | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0000                        |                                 | 15:0          | _      | _     | _     | _     | _      | _     | _    | _                                      | CHSDIF        | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3090                        | DCH0SSA                         | 31:16         |        |       |       |       |        |       |      | CHSSA                                  | \<31:0>       |        |        |        |        |        |        |        | 0000       |

| 0000                        |                                 | 15:0          |        |       |       |       |        |       |      | 000,                                   |               |        |        |        |        |        |        |        | 0000       |

| 30A0                        | DCH0DSA                         | 31:16         |        |       |       |       |        |       |      | CHDSA                                  | A<31:0>       |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      |                                        | 1             |        |        |        |        |        |        |        | 0000       |

| 30B0                        | DCH0SSIZ                        | 31:16         | _      | _     | _     | _     | _      | _     | _    |                                        |               | _      | _      | _      | _      | _      | _      | _      | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | CHSSI                                  | Z<15:0>       |        |        |        |        |        |        |        | 0000       |

| 30C0                        | DCH0DSIZ                        | 31:16         | _      | _     | _     | _     | _      | _     | _    | —————————————————————————————————————— | 7 - 45 0:     | _      | _      | _      | _      | _      | _      | _      | 0000       |

| -                           |                                 | 15:0          |        |       |       |       |        |       |      | CHDSI                                  | Z<15:0>       |        |        |        |        |        |        |        | 0000       |

| 30D0                        | DCH0SPTR                        | 31:16         | _      |       | _     | _     | _      | _     | _    | - CHODE                                | —<br>D 445-05 | _      | _      | _      | _      | _      | _      | _      | 0000       |

|                             |                                 | 15:0          |        |       |       |       |        |       |      | CHSPT                                  | K<15:0>       |        |        |        |        |        |        |        | 0000       |

| 30E0                        | DCH0DPTR                        | 31:16<br>15:0 | _      |       | _     | _     |        | _     | _    | CHDPT                                  | D<15:0>       | _      | _      | _      | _      | _      | _      | _      | 0000       |

|                             |                                 | 31:16         | _ [    |       |       |       |        |       |      | CODFI                                  | K 15.02       |        |        |        |        |        |        | _      | 0000       |

| 30F0                        | DCH0CSIZ                        | 15:0          | _      |       | _     | _     | _      | _     | _    | CHCSIZ                                 | 7<15:0>       | _      | _      |        | _      | _      | _      | _      | 0000       |

| +                           |                                 | 31:16         | _ [    |       | _     | _     | _      | _     | _    |                                        |               | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3100                        | DCH0CPTR                        | 15:0          |        |       |       |       |        |       |      | CHCPT                                  | R<15:0>       |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         | _      |       | _     | _     | _      | _     | _    | <u> </u>                               | _             | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3110                        | DCH0DAT                         | 15:0          | _      |       | _     | _     | _      |       |      |                                        |               |        |        | CHPDA  |        |        |        |        | 0000       |

|                             |                                 | 31:16         | _      | _     | _     | _     | _      | _     | _    | _                                      | _             | _      | _      | _      | _      | _      | _      | _      | 0000       |

| 3120                        | DCH1CON                         |               | CHBUSY | _     | _     | _     | -      | _     | _    | CHCHNS                                 | CHEN          | CHAED  | CHCHN  | CHAEN  | _      | CHEDET | CHPR   | I<1:0> | 0000       |

| 0400                        | 5011150011                      | 31:16         | _      | _     | _     | _     | _      | _     | _    | _                                      |               | Į.     | Į.     | CHAIR  | Q<7:0> |        |        |        | 00FF       |

| 3130 [                      | DCH1ECON                        | 15:0          |        |       |       | CHSIR | Q<7:0> |       |      |                                        | CFORCE        | CABORT | PATEN  | SIRQEN | AIRQEN | _      | _      | _      | FFF8       |

| 2140                        | DOLIAINT                        | 31:16         | _      | _     | _     | _     | _      | _     | _    | _                                      | CHSDIE        | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE | 0000       |

| 3140                        | DCH1INT                         | 15:0          | _      |       |       |       |        |       |      |                                        | CHSDIF        | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3150                        | DCH1SSA                         | 31:16         |        |       |       |       |        |       |      | CHEST                                  | \<31:0>       |        |        |        |        |        |        |        | 0000       |

| 3130                        | БСПІЗЗА                         | 15:0          |        |       |       |       |        |       |      | UH33F                                  | 1-01.0-       |        |        |        |        |        |        |        | 0000       |

| 3160                        | DCH1DSA                         | 31:16         |        |       |       |       |        |       |      | CHDS/                                  | \<31:0>       |        |        |        |        |        |        |        | 0000       |

| 3100                        | DOITIDGA                        | 15:0          |        |       |       |       |        |       |      | CUDSF                                  | 7-01.0-       |        |        |        |        |        |        |        | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

REGISTER 10-1: DMACON: DMA CONTROLLER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

| 22.46        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | SUSPEND           | DMABUSY <sup>(1)</sup> | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: DMA On bit<sup>(1)</sup>

1 = DMA module is enabled0 = DMA module is disabled

bit 14-13 **Unimplemented:** Read as '0' bit 12 **SUSPEND:** DMA Suspend bit

1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

0 = DMA operates normally

bit 11 **DMABUSY:** DMA Module Busy bit<sup>(1)</sup>

1 = DMA module is active

0 = DMA module is disabled and not actively transferring data

bit 10-0 Unimplemented: Read as '0'

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| TABLE 11-1: | USB REGIS | STER MAP | (CONTINUED) | ) |

|-------------|-----------|----------|-------------|---|

|-------------|-----------|----------|-------------|---|

| ess                         |                                 |           |       | Bits  |       |       |       |       |      |      |      |      |      |          |        |        |         |        |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | _     | _     | _     | _     | _     | _     | _    |      | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 3390                        | OILF9                           | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53A0                        | U1EP10                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | -    | _    | _    | _        | _      | _      | _       |        | 0000       |

| 33A0                        | OTEFIO                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     | _     | _     | _     | _     | _     | _     | _    |      | ı    | -    | _    | _        | -      | -      |         | ı      | 0000       |

| 3360                        | UIEFII                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     | _     | _     | _     | _     | _     | _     | _    |      | ı    | -    | _    | _        | -      | -      |         | ı      | 0000       |

| 3300                        | OTEF 12                         | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | ı    | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 3300                        | OTEF 13                         | 15:0      | _     | _     | _     | _     | _     | _     | _    |      | ı    | -    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        | LIAEDAA                         | 31:16     | _     | _     | _     | _     |       | _     | _    | _    | -    | _    | _    | _        | -      | _      | 1       | -      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| E2E0                        | LIAEDAE                         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

- 2: This register does not have associated SET and INV registers.

- 3: This register does not have associated CLR, SET and INV registers.

- 4: Reset value for this bit is undefined.

TABLE 12-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range |       |       |       |       |       |       | Bits |      |      |      |      |      |      |       |        |      |            |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| >                           |                      | Bit F     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FC14 RP                     | PE5R                 | 31:16     | _     |       | _     |       |       |       | _    |      |      | _    |      |      |      | _     |        |      | 0000       |

| 1014 KF                     | IFLOR                | 15:0      | _     |       | _     | _     | -     | _     | _    | _    | _    | _    | _    | _    |      | RPE5  | <3:0>  |      | 0000       |

| FC20 RP                     | PE8R <sup>(1)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1 020 KF                    | IF LOIK.             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPE8  | <3:0>  |      | 0000       |

| FC24 RP                     | PE9R <sup>(1)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1024 10                     | II LOIV              | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPE9  | <3:0>  |      | 0000       |

| FC40 RP                     | PF0R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1040 10                     | 11 010               | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF0  | <3:0>  |      | 0000       |

| FC44 RP                     | PF1R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1044 KF                     | IFI IIX              | 15:0      | _     | _     | _     | _     | _     |       | _    | _    |      | _    |      | _    |      | RPF1  | <3:0>  |      | 0000       |

| FC48 RP                     | PF2R <sup>(3)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1040 10                     | 11 21(               | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF2  | <3:0>  |      | 0000       |

| FC4C RP                     | PF3R <sup>(2)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1 040 11                    | ar r orc             | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF3  | <3:0>  |      | 0000       |

| FC50 RP                     | PF4R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1 030 111                   | 11 711               | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF4  | <3:0>  |      | 0000       |

| FC54 RP                     | PF5R                 | 31:16     | _     | _     | _     | _     | _     |       | _    | _    |      | _    |      | _    | _    | _     | _      | _    | 0000       |

| 1 004 111                   | 11 010               | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF5  | <3:0>  |      | 0000       |

| FC58 RP                     | PF6R <sup>(2)</sup>  | 31:16     | _     | _     | _     | _     | _     |       | _    | _    |      | _    |      | _    | _    | _     | _      | _    | 0000       |

| 1 030 111                   | ar rock.             | 15:0      | _     | _     | _     | _     | _     |       | _    | _    |      | _    |      | _    |      | RPF6  | <3:0>  |      | 0000       |

| FC60 RP                     | PF8R <sup>(1)</sup>  | 31:16     | _     | _     | _     | _     | -     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1 C00   KF                  | TI OK,               | 15:0      | _     | _     | _     | _     | _     |       | _    | _    |      | _    |      | _    |      | RPF8  | <3:0>  |      | 0000       |

| FC70 RP                     | PF12R <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     |       | _    | _    |      | _    |      | _    | _    | _     | _      | _    | 0000       |

| 1070   10                   | 11 1211              | 15:0      | _     | _     | _     | _     | -     | _     | _    | _    | _    | _    | _    | _    |      | RPF12 | 2<3:0> |      | 0000       |

| FC74 RP                     | PF13R <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     |       | _    | _    |      | _    |      | _    | _    | _     | _      | _    | 0000       |

| 1074 10                     | 11 101(              | 15:0      | _     | _     | _     | _     | _     |       | _    | _    |      | _    |      | _    |      | RPF13 | 3<3:0> |      | 0000       |

| FC80 RP                     | PG0R <sup>(1)</sup>  | 31:16     | _     |       | _     | _     | -     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | -    | 0000       |

| 1 C00 KF                    | r Gur.               | 15:0      | _     | _     | _     | _     | _     |       | _    | _    |      | _    |      | _    |      | RPG0  | <3:0>  |      | 0000       |

| FC84 RP                     | PG1R <sup>(1)</sup>  | 31:16     | _     | -     | _     | _     | -     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1 004 KF                    | a GIK.               | 15:0      | _     | _     | _     | _     | -     | _     | _    | _    |      | _    | _    | -    |      | RPG1  | <3:0>  |      | 0000       |

| ECOO DE                     | DCSD                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      |      | 0000       |

| FC98 RP                     | PG6R                 | 15:0      | _     | _     |       | _     | _     | _     |      | _    |      |      |      | _    |      | RPG6  | <3:0>  |      | 0000       |

| ECOC DE                     | DC7D                 | 31:16     | _     |       | _     | _     |       | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      |      | 0000       |

| FC9C RP                     | PG7R                 | 15:0      | _     | -     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPG7  | <3:0>  |      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

<sup>2:</sup> This register is only available on devices without a USB module.

<sup>3:</sup> This register is not available on 64-pin devices with a USB module.

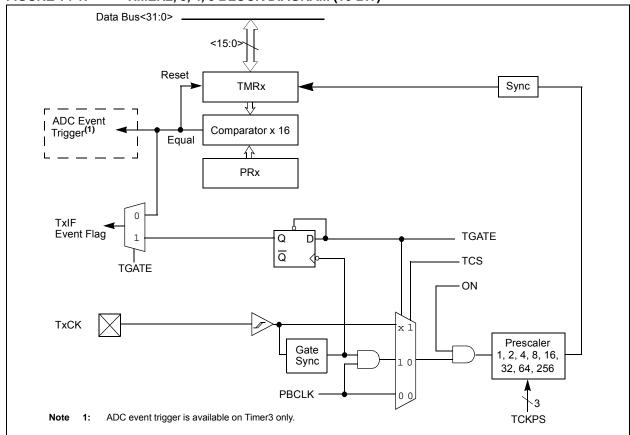

#### 14.0 TIMER2/3, TIMER4/5

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14.** "**Timers**" (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32MX330/350/370/430/450/470 family of devices features four synchronous 16-bit timers (default) that can operate as a free-running interval timer for various timing applications and counting external events. The following modes are supported:

- · Synchronous internal 16-bit timer

- · Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- Synchronous external 32-bit timer

Note:

In this chapter, references to registers, TxCON, TMRx and PRx, use 'x' to represent Timer2 through 5 in 16-bit modes. In 32-bit modes, 'x' represents Timer2 or 4; 'y' represents Timer3 or 5.

#### 14.1 Additional Supported Features

- · Selectable clock prescaler

- · Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/ 3 in 32-bit mode)

- Fast bit manipulation using CLR, SET, and INV registers

FIGURE 14-1: TIMER2, 3, 4, 5 BLOCK DIAGRAM (16-BIT)

| PIC32M2 | X330/35 | 0/3/0/4 | 130/450 | /4/0 |  |

|---------|---------|---------|---------|------|--|

| NOTES:  |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

|         |         |         |         |      |  |

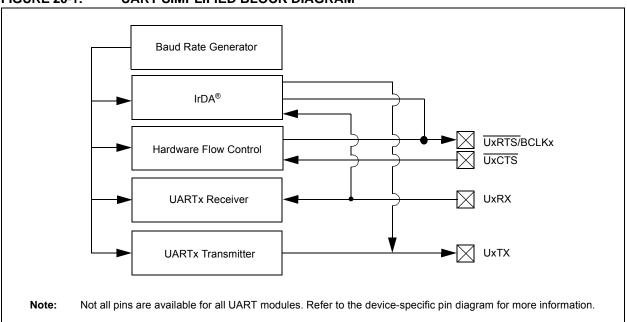

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 21. "Universal Asynchronous Receiver Transmitter (UART)"** (DS60001107), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The UART module is one of the serial I/O modules available in the PIC32MX330/350/370/430/450/470 family of devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN and IrDA®. The module also supports the hardware flow control option, with UXCTS and UXRTS pins, and also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- · Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 76 bps to 30 Mbps at 120 MHz

- 8-level deep First-In-First-Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- Loopback mode for diagnostic support

- · LIN Protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 20-1 illustrates a simplified block diagram of the UART

FIGURE 20-1: UART SIMPLIFIED BLOCK DIAGRAM

### REGISTER 21-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | -                 | _                 | _                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | -                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              | _                 | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

Legend:HS = Set by HardwareSC = Cleared by softwareR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 IBF: Input Buffer Full Status bit

1 = All writable input buffer registers are full

0 = Some or all of the writable input buffer registers are empty

bit 14 IBOV: Input Buffer Overflow Status bit

1 = A write attempt to a full input byte buffer occurred (must be cleared in software)

0 = No overflow occurred

bit 13-12 Unimplemented: Read as '0'

bit 11-8 IBxF: Input Buffer 'x' Status Full bits

1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

0 = Input Buffer does not contain any unread data

bit 7 **OBE:** Output Buffer Empty Status bit

1 = All readable output buffer registers are empty

0 = Some or all of the readable output buffer registers are full

bit 6 **OBUF:** Output Buffer Underflow Status bit

1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

bit 5-4 Unimplemented: Read as '0'

bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

1 = Output buffer is empty (writing data to the buffer will clear this bit)

0 = Output buffer contains data that has not been transmitted

#### REGISTER 22-4: RTCDATE: RTC DATE VALUE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-x             | R/W-x              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   | YEAR1              | 0<3:0>            |                   |                   | YEAR0             | 1<3:0>           |                  |

| 22.46        | R/W-x             | R/W-x              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:16        |                   | MONTH <sup>2</sup> | 10<3:0>           |                   |                   | MONTH             | 01<3:0>          |                  |

| 45.0         | R/W-x             | R/W-x              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   | DAY10              | <3:0>             |                   |                   | DAY01             | <3:0>            |                  |

| 7.0          | U-0               | U-0                | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          | _                 | _                  | _                 | _                 |                   | WDAYO             | 1<3:0>           |                  |

#### Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digits

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1s place digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 DAY01<3:0>: Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1s place digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

| ess                         | Register<br>Name | Bit Range | Bits                                   |                                    |       |       |       |       |       |       |      |      |      |      | s    |      |      |      |      |

|-----------------------------|------------------|-----------|----------------------------------------|------------------------------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|------|

| Virtual Address<br>(BF80_#) |                  |           | Bit Rang                               | Bit Rang                           | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 |

| 9110                        | ADC1BUFA         | 31:16     |                                        | ADC Result Word A (ADC1BUFA<31:0>) |       |       |       |       |       |       |      |      |      |      | 0000 |      |      |      |      |

|                             |                  | 15:0      |                                        |                                    |       |       |       |       |       |       |      |      |      | 0000 |      |      |      |      |      |

| 9120                        | ADC1BUFB         | 31:16     | ADC Result Word B (ADC1BUFB<31:0>)     |                                    |       |       |       |       |       |       |      | 0000 |      |      |      |      |      |      |      |

|                             |                  | 15:0      |                                        | 0000                               |       |       |       |       |       |       |      |      | 0000 |      |      |      |      |      |      |

| 0420                        | ADC1BUFC         | 31:16     | ADC Result Word C (ADC1BUFC<31:0>)     |                                    |       |       |       |       |       |       |      |      | 0000 |      |      |      |      |      |      |

| 9130                        | ADCIBUFC         | 15:0      | ADC RESult World C (ADC IBDFC < 51.02) |                                    |       |       |       |       |       |       |      | 0000 |      |      |      |      |      |      |      |

| 04.40                       | ADC1BUFD         | 31:16     | 01                                     |                                    |       |       |       |       |       |       |      |      | 0000 |      |      |      |      |      |      |

| 9140                        |                  | 15:0      | ADC Result Word D (ADC1BUFD<31:0>)     |                                    |       |       |       |       |       |       |      | 0000 |      |      |      |      |      |      |      |

|                             | ADC1BUFE         | 31:16     |                                        |                                    |       |       |       |       |       |       |      |      | 0000 |      |      |      |      |      |      |

| 9150                        |                  | 15:0      | ADC Result Word E (ADC1BUFE<31:0>)     |                                    |       |       |       |       |       |       |      | 0000 |      |      |      |      |      |      |      |

|                             |                  | 31:16     |                                        |                                    |       |       |       |       |       |       |      |      |      |      |      |      |      |      | 0000 |

| 9160                        | ADC1BUFF         | 15:0      | ADC Result Word F (ADC1BUFF<31:0>)     |                                    |       |       |       |       |       |       |      | 0000 |      |      |      |      |      |      |      |

| <u> </u>                    |                  |           |                                        |                                    |       |       |       |       |       |       |      |      |      |      |      |      |      |      |      |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for details

#### REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

- bit 10 EDGSEQEN: Edge Sequence Enable bit

- 1 = Edge 1 must occur before Edge 2 can occur

- 0 = No edge sequence is needed

- bit 9 **IDISSEN:** Analog Current Source Control bit<sup>(2)</sup>

- 1 = Analog current source output is grounded

- 0 = Analog current source output is not grounded

- bit 8 **CTTRIG:** Trigger Control bit

- 1 = Trigger output is enabled

- 0 = Trigger output is disabled

- bit 7-2 ITRIM<5:0>: Current Source Trim bits

- 011111 = Maximum positive change from nominal current

011110

•

000001 = Minimum positive change from nominal current

000000 = Nominal current output specified by IRNG<1:0>

111111 = Minimum negative change from nominal current

.

100010

100001 = Maximum negative change from nominal current

bit 1-0 IRNG<1:0>: Current Range Select bits<sup>(3)</sup>

- 11 = 100 times base current

- 10 = 10 times base current

- 01 = Base current level

- 00 = 1000 times base current(4)

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-42) in **Section 31.0 "Electrical Characteristics"** for current values.

- **4:** This bit setting is not available for the CTMU temperature diode.

#### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

bit 11-5 Reserved: Write '1'

bit 4-3 ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits

11 = PGEC1/PGED1 pair is used 10 = PGEC2/PGED2 pair is used 01 = PGEC3/PGED3 pair is used

00 = Reserved

bit 2 **JTAGEN:** JTAG Enable bit<sup>(1)</sup>

1 = JTAG is enabled 0 = JTAG is disabled

bit 1-0 **DEBUG<1:0>:** Background Debugger Enable bits (forced to '11' if code-protect is enabled)

1x = Debugger is disabled 0x = Debugger is enabled

Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

#### **REGISTER 28-5: CFGCON: CONFIGURATION CONTROL REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-----------------------|------------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | _                     | _                      | _                 | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | -                     | _                      | -                 | _                 | _                | _                |

| 45.0         | U-0               | U-0               | R/W-0                 | R/W-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | ı                 | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> | 1                 |                   |                  | _                |

| 7.0          | U-0               | U-0               | U-0                   | U-0                    | R/W-0             | R/W-0             | U-0              | R/W-1            |

| 7:0          | _                 |                   |                       | _                      | JTAGEN            | TROEN             |                  | TDOEN            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-14 Unimplemented: Read as '0'

bit 13 **IOLOCK:** Peripheral Pin Select Lock bit<sup>(1)</sup>

${\tt 1}$  = Peripheral Pin Select is locked. Writes to PPS registers is not allowed

0 = Peripheral Pin Select is not locked. Writes to PPS registers is allowed

bit 12 **PMDLOCK:** Peripheral Module Disable bit<sup>(1)</sup>

1 = Peripheral module is locked. Writes to PMD registers is not allowed

0 = Peripheral module is not locked. Writes to PMD registers is allowed

bit 11-4 Unimplemented: Read as '0'

bit 3 JTAGEN: JTAG Port Enable bit

1 = Enable the JTAG port

0 = Disable the JTAG port

bit 2 TROEN: Trace Output Enable bit

1 = Enable trace outputs and start trace clock (trace probe must be present)

0 = Disable trace outputs and stop trace clock

bit 1 **Unimplemented:** Read as '0'

bit 0 TDOEN: TDO Enable for 2-Wire JTAG

1 = 2-wire JTAG protocol uses TDO

0 = 2-wire JTAG protocol does not use TDO

Note 1: To change this bit, the unlock sequence must be performed. Refer to **Section 6. "Oscillator"** (DS60001112) in the "PIC32 Family Reference Manual" for details.

TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

| DC CHA        | ARACTE               | ERISTICS                       | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                     |                      |       |                                                                          |  |  |

|---------------|----------------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|-------|--------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symb Characteristics |                                | Min.                                                                                                                                                                                                                                                     | Typ. <sup>(1)</sup> | Max.                 | Units | Conditions                                                               |  |  |

|               |                      | Input Leakage Current (Note 3) |                                                                                                                                                                                                                                                          |                     |                      |       |                                                                          |  |  |

| DI50          | lıL                  | I/O Ports                      | _                                                                                                                                                                                                                                                        | _                   | <u>+</u> 1           | μА    | Vss ≤ VPIN ≤ VDD,<br>Pin at high-impedance                               |  |  |

| DI51          |                      | Analog Input Pins              | _                                                                                                                                                                                                                                                        | _                   | <u>+</u> 1           | μА    | $Vss \leq VPIN \leq VDD, \\ Pin at high-impedance$                       |  |  |

| DI55          |                      | MCLR(2)                        | _                                                                                                                                                                                                                                                        | _                   | <u>+</u> 1           | μΑ    | $Vss \leq VPIN \leq VDD$                                                 |  |  |

| DI56          |                      | OSC1                           | _                                                                                                                                                                                                                                                        | _                   | <u>+</u> 1           | μА    | $VSS \leq VPIN \leq VDD, \\ XT \ and \ HS \ modes$                       |  |  |

|               |                      |                                |                                                                                                                                                                                                                                                          |                     |                      |       | Pins with Analog functions.<br>Exceptions: [N/A] = 0 mA<br>max           |  |  |

| DI60a         | licl                 | Input Low Injection<br>Current | 0                                                                                                                                                                                                                                                        | _                   | -5 <sup>(7,10)</sup> | mA    | Digital 5V tolerant designated pins. Exceptions:<br>[N/A] = 0 mA max     |  |  |

|               |                      |                                |                                                                                                                                                                                                                                                          |                     |                      |       | Digital non-5V tolerant designated pins. Exceptions:<br>[N/A] = 0 mA max |  |  |

- **Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the user-selectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

- 7: VIL source < (Vss 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- **10:** Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS 0.3)).

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ Vsource ≤ (VDD + 0.3), injection current = 0.

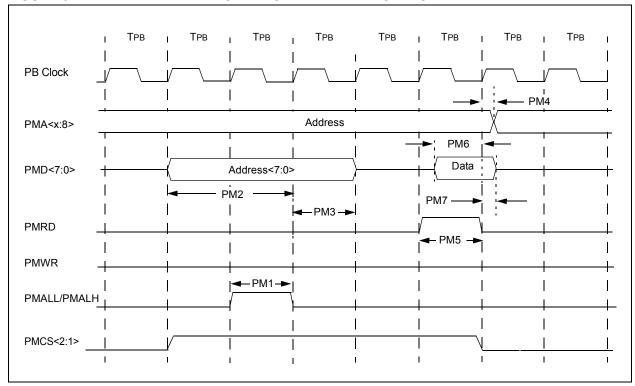

FIGURE 31-21: PARALLEL MASTER PORT READ TIMING DIAGRAM

TABLE 31-39: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

| AC CHA        | ARACTER | ISTICS                                                               | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |       |      |       |            |  |  |

|---------------|---------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                                     | Тур.  | Max. | Units | Conditions |  |  |

| PM1           | TLAT    | PMALL/PMALH Pulse Width                                              |                                                                                                                                                                                                                                                          | 1 Трв |      | _     | _          |  |  |

| PM2           | TADSU   | Address Out Valid to PMALL/<br>PMALH Invalid (address setup<br>time) | _                                                                                                                                                                                                                                                        | 2 Трв | _    | _     | _          |  |  |

| PM3           | TADHOLD | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | _                                                                                                                                                                                                                                                        | 1 Трв | _    | _     | _          |  |  |

| PM4           | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                                                                                                                        | _     | _    | ns    | _          |  |  |

| PM5           | TRD     | PMRD Pulse Width                                                     | _                                                                                                                                                                                                                                                        | 1 Трв | _    | _     | _          |  |  |

| PM6           | Tosu    | PMRD or PMENB Active to Data In Valid (data setup time)              | 15                                                                                                                                                                                                                                                       | _     | _    | ns    | _          |  |  |

| PM7           | TDHOLD  | PMRD or PMENB Inactive to Data In Invalid (data hold time)           | 1 Трв                                                                                                                                                                                                                                                    | _     | _    |       | PMP Clock  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

## Revision D (March 2015)

This revision includes the following updates, as listed in Table A-3.

TABLE A-3: MAJOR SECTION UPDATES