Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                           |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 128K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx370f512l-v-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4: PIN NAMES FOR 100-PIN DEVICES (CONTINUED)

| 10                                           | 100-PIN TQFP (TOP VIEW) <sup>(1,2,3)</sup>                                                                                                          |                                                    |                                                                                                                                               |  |  |  |  |  |  |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                              | PIC32MX330F064L<br>PIC32MX350F128L<br>PIC32MX350F256L<br>PIC32MX370F512L                                                                            |                                                    |                                                                                                                                               |  |  |  |  |  |  |

|                                              |                                                                                                                                                     |                                                    | 100 1                                                                                                                                         |  |  |  |  |  |  |

| Pin #                                        | Full Pin Name                                                                                                                                       | Pin #                                              | Full Pin Name                                                                                                                                 |  |  |  |  |  |  |

| 71                                           | RPD11/PMCS1/RD11                                                                                                                                    | 86                                                 | Vdd                                                                                                                                           |  |  |  |  |  |  |

| 72                                           | RPD0/RD0                                                                                                                                            | 87                                                 | RPF0/PMD11/RF0                                                                                                                                |  |  |  |  |  |  |

| 73                                           | SOSCI/RPC13/RC13                                                                                                                                    |                                                    |                                                                                                                                               |  |  |  |  |  |  |

|                                              |                                                                                                                                                     | 88                                                 | RPF1/PMD10/RF1                                                                                                                                |  |  |  |  |  |  |

| 74                                           | SOSCO/RPC14/T1CK/RC14                                                                                                                               | 88                                                 | RPF1/PMD10/RF1<br>RPG1/PMD9/RG1                                                                                                               |  |  |  |  |  |  |

| 74<br>75                                     |                                                                                                                                                     |                                                    |                                                                                                                                               |  |  |  |  |  |  |

|                                              | SOSCO/RPC14/T1CK/RC14                                                                                                                               | 89                                                 | RPG1/PMD9/RG1                                                                                                                                 |  |  |  |  |  |  |

| 75                                           | SOSCO/RPC14/T1CK/RC14<br>Vss                                                                                                                        | 89<br>90                                           | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0                                                                                                                |  |  |  |  |  |  |

| 75<br>76                                     | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1                                                                                                       | 89<br>90<br>91                                     | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6                                                                                                   |  |  |  |  |  |  |

| 75<br>76<br>77                               | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1<br>AN25/RPD2/RD2                                                                                      | 89<br>90<br>91<br>92                               | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6<br>TRD3/CTED8/RA7                                                                                 |  |  |  |  |  |  |

| 75<br>76<br>77<br>78                         | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1<br>AN25/RPD2/RD2<br>AN26/RPD3/RD3                                                                     | 89<br>90<br>91<br>92<br>93                         | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6<br>TRD3/CTED8/RA7<br>PMD0/RE0                                                                     |  |  |  |  |  |  |

| 75<br>76<br>77<br>78<br>79                   | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1<br>AN25/RPD2/RD2<br>AN26/RPD3/RD3<br>RPD12/PMD12/RD12<br>PMD13/RD13<br>RPD4/PMWR/RD4                  | 89<br>90<br>91<br>92<br>93<br>94                   | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6<br>TRD3/CTED8/RA7<br>PMD0/RE0<br>PMD1/RE1<br>TRD2/RG14<br>TRD1/RG12                               |  |  |  |  |  |  |

| 75<br>76<br>77<br>78<br>79<br>80             | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1<br>AN25/RPD2/RD2<br>AN26/RPD3/RD3<br>RPD12/PMD12/RD12<br>PMD13/RD13                                   | 89<br>90<br>91<br>92<br>93<br>94<br>95             | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6<br>TRD3/CTED8/RA7<br>PMD0/RE0<br>PMD1/RE1<br>TRD2/RG14                                            |  |  |  |  |  |  |

| 75<br>76<br>77<br>78<br>79<br>80<br>81       | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1<br>AN25/RPD2/RD2<br>AN26/RPD3/RD3<br>RPD12/PMD12/RD12<br>PMD13/RD13<br>RPD4/PMWR/RD4                  | 89<br>90<br>91<br>92<br>93<br>94<br>95<br>96       | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6<br>TRD3/CTED8/RA7<br>PMD0/RE0<br>PMD1/RE1<br>TRD2/RG14<br>TRD1/RG12<br>TRD0/RG13<br>AN20/PMD2/RE2 |  |  |  |  |  |  |

| 75<br>76<br>77<br>78<br>79<br>80<br>81<br>82 | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1<br>AN25/RPD2/RD2<br>AN26/RPD3/RD3<br>RPD12/PMD12/RD12<br>PMD13/RD13<br>RPD4/PMWR/RD4<br>RPD5/PMRD/RD5 | 89<br>90<br>91<br>92<br>93<br>94<br>95<br>96<br>97 | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6<br>TRD3/CTED8/RA7<br>PMD0/RE0<br>PMD1/RE1<br>TRD2/RG14<br>TRD1/RG12<br>TRD0/RG13                  |  |  |  |  |  |  |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx), with the exception of RF6, can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: RPF6 (pin 55) and RPF7 (pin 54) are only remappable for input functions.

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS

|          |                        | Pin Numb        | er                                |             |                |                                                                                                                                                                                                   |  |

|----------|------------------------|-----------------|-----------------------------------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA                   | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                       |  |

| AN0      | 16                     | 25              | B14                               |             | Analog         |                                                                                                                                                                                                   |  |

| AN1      | 15                     | 24              | A15                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN2      | 14                     | 23              | B13                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN3      | 13                     | 22              | A13                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN4      | 12                     | 21              | B11                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN5      | 11                     | 20              | A12                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN6      | 17                     | 26              | A20                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN7      | 18                     | 27              | B16                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN8      | 21                     | 32              | A23                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN9      | 22                     | 33              | B19                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN10     | 23                     | 34              | A24                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN11     | 24                     | 35              | B20                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN12     | 27                     | 41              | B23                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN13     | 28                     | 42              | A28                               | I           | Analog         | Analog input channels.                                                                                                                                                                            |  |

| AN14     | 29                     | 43              | B24                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN15     | 30                     | 44              | A29                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN16     | 4                      | 10              | A7                                | I           | Analog         |                                                                                                                                                                                                   |  |

| AN17     | 5                      | 11              | B6                                | I           | Analog         |                                                                                                                                                                                                   |  |

| AN18     | 6                      | 12              | A8                                | I           | Analog         |                                                                                                                                                                                                   |  |

| AN19     | 8                      | 14              | A9                                | I           | Analog         |                                                                                                                                                                                                   |  |

| AN20     | 62                     | 98              | A66                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN21     | 64                     | 100             | A67                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN22     | 1                      | 3               | B2                                | I           | Analog         |                                                                                                                                                                                                   |  |

| AN23     | 2                      | 4               | A4                                | I           | Analog         |                                                                                                                                                                                                   |  |

| AN24     | 49                     | 76              | A52                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN25     | 50                     | 77              | B42                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN26     | 51                     | 78              | A53                               | I           | Analog         |                                                                                                                                                                                                   |  |

| AN27     | 3                      | 5               | B3                                | I           | Analog         |                                                                                                                                                                                                   |  |

| CLKI     | 39                     | 63              | B34                               | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                            |  |

| CLKO     | 40                     | 64              | A42                               | 0           | _              | Oscillator crystal output. Connects to crystal or reso-<br>nator in Crystal Oscillator mode. Optionally functions<br>as CLKO in RC and EC modes. Always associated<br>with the OSC2 pin function. |  |

| OSC1     | 39                     | 63              | B34                               | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                   |  |

| OSC2     | 40                     | 64              | A42                               | 0           | _              | Oscillator crystal output. Connects to crystal or reso-<br>nator in Crystal Oscillator mode. Optionally functions<br>as CLKO in RC and EC modes.                                                  |  |

| SOSCI    | 47                     | 73              | A47                               | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                    |  |

| SOSCO    | 48                     | 74              | B40                               | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                   |  |

| -        | ST = Schm              |                 | tible input or o<br>out with CMOS |             |                | alog = Analog input P = Power<br>= Output I = Input                                                                                                                                               |  |

TTL = TTL input buffer

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

**3:** This pin is not available on 64-pin devices.

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e<sup>®</sup>, is also available by accessing the CP0 registers, listed in Table 3-2.

| Reserved<br>HWREna<br>BadVAddr <sup>(1)</sup><br>Count <sup>(1)</sup><br>Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup> | Reserved in the PIC32MX330/350/370/430/450/470 family core.         Enables access via the RDHWR instruction to selected hardware registers.         Reports the address for the most recent address-related exception.         Processor cycle count.         Reserved in the PIC32MX330/350/370/430/450/470 family core.         Timer interrupt control. |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BadVAddr <sup>(1)</sup><br>Count <sup>(1)</sup><br>Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                       | Reports the address for the most recent address-related exception.<br>Processor cycle count.<br>Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                 |

| Count <sup>(1)</sup><br>Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                                                  | Processor cycle count.<br>Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                       |

| Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                                                                          | Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                                                 |

| Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                                                                                      |                                                                                                                                                                                                                                                                                                                                                             |

| Status <sup>(1)</sup>                                                                                                                | Timer interrupt control.                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                             |

| (4)                                                                                                                                  | Processor status and control.                                                                                                                                                                                                                                                                                                                               |

| IntCtl <sup>(1)</sup>                                                                                                                | Interrupt system status and control.                                                                                                                                                                                                                                                                                                                        |

| SRSCtl <sup>(1)</sup>                                                                                                                | Shadow register set status and control.                                                                                                                                                                                                                                                                                                                     |

| SRSMap <sup>(1)</sup>                                                                                                                | Provides mapping from vectored interrupt to a shadow set.                                                                                                                                                                                                                                                                                                   |

| Cause <sup>(1)</sup>                                                                                                                 | Cause of last general exception.                                                                                                                                                                                                                                                                                                                            |

| EPC <sup>(1)</sup>                                                                                                                   | Program counter at last exception.                                                                                                                                                                                                                                                                                                                          |

| PRId                                                                                                                                 | Processor identification and revision.                                                                                                                                                                                                                                                                                                                      |

| EBASE                                                                                                                                | Exception vector base register.                                                                                                                                                                                                                                                                                                                             |

| Config                                                                                                                               | Configuration register.                                                                                                                                                                                                                                                                                                                                     |

| Config1                                                                                                                              | Configuration register 1.                                                                                                                                                                                                                                                                                                                                   |

| Config2                                                                                                                              | Configuration register 2.                                                                                                                                                                                                                                                                                                                                   |

| Config3                                                                                                                              | Configuration register 3.                                                                                                                                                                                                                                                                                                                                   |

| Reserved                                                                                                                             | Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                                                 |

| Debug <sup>(2)</sup>                                                                                                                 | Debug control and exception status.                                                                                                                                                                                                                                                                                                                         |

| DEPC <sup>(2)</sup>                                                                                                                  | Program counter at last debug exception.                                                                                                                                                                                                                                                                                                                    |

| Reserved                                                                                                                             | Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                                                 |

| ErrorEPC <sup>(1)</sup>                                                                                                              | Program counter at last error.                                                                                                                                                                                                                                                                                                                              |

| DESAVE <sup>(2)</sup>                                                                                                                | Debug handler scratchpad register.                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                      | RSMap <sup>(1)</sup><br>Cause <sup>(1)</sup><br>PC <sup>(1)</sup><br>PRId<br>BASE<br>Config<br>Config1<br>Config2<br>Config3<br>Reserved<br>Debug <sup>(2)</sup><br>DEPC <sup>(2)</sup><br>Reserved<br>ErrorEPC <sup>(1)</sup>                                                                                                                              |

TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used during debug.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   |                   |                   |                   | _                 |                   | -                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | -                 | -                 | -                 | _                 | —                 | _                | _                |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         |                   |                   |                   | <10:3>            |                   |                   |                  |                  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          |                   | _MASK<2:0>        |                   | _                 | _                 | _                 | _                | —                |

### REGISTER 9-4: CHEMSK: CACHE TAG MASK REGISTER

## Legend:

| Logonal           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Write '0'; ignore read

- bit 15-5 LMASK<10:0>: Line Mask bits

- 1 = Enables mask logic to force a match on the corresponding bit position in the LTAG<19:0> bits (CHETAG<23:4>) and the physical address.

- 0 = Only writeable for values of CHEIDX<3:0> bits (CHEACC<3:0>) equal to 0x0A and 0x0B. Disables mask logic.

- bit 4-0 Unimplemented: Write '0'; ignore read

|              |                   |                   | ••••              | •                 |                   |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        | CHEW0<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        | CHEW0<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | CHEW0<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          |                   |                   | •                 | CHEWO             | )<7:0>            |                   |                  |                  |  |  |

#### REGISTER 9-5: CHEW0: CACHE WORD 0

| Legend:           |                                                     |                      |                    |  |

|-------------------|-----------------------------------------------------|----------------------|--------------------|--|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |  |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |  |

bit 31-0 **CHEW0<31:0>:** Word 0 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

# PIC32MX330/350/370/430/450/470

#### REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|---------------------|

| 04.04        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0               |

| 31:24        | —                 | —                     | BYTC              | <1:0>             | WBO <sup>(1)</sup> | _                 | _                | BITO <sup>(1)</sup> |

| 00.40        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0                 |

| 23:16        | —                 | —                     | —                 | _                 | _                  | _                 | _                | -                   |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0               |

| 15:8         | —                 | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                     |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0               |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            |                   | _                  | (                 | CRCCH<2:0>       |                     |

## Legend:

| Legena.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit<sup>(1)</sup>

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

#### <u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

#### bit 23-13 Unimplemented: Read as '0'

bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(1)</sup>

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial - 1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

## REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6                                     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------|-------------------|-------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

|           |                   |                                                       |                   |                   |                   |                   |                  |                  |  |  |

| 31:24     | K/W-U             | R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 R/W-0 |                   |                   |                   |                   |                  |                  |  |  |

| 22:16     | R/W-0             | R/W-0                                                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16     | CHSSA<23:16>      |                                                       |                   |                   |                   |                   |                  |                  |  |  |

| 15:8      | R/W-0             | R/W-0                                                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 10.0      | CHSSA<15:8>       |                                                       |                   |                   |                   |                   |                  |                  |  |  |

| 7:0       | R/W-0             | R/W-0                                                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0       |                   |                                                       |                   | CHSSA             | <7:0>             |                   |                  |                  |  |  |

## REGISTER 10-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0

CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

Note: This must be the physical address of the source.

#### **REGISTER 10-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 31:24        | CHDSA<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 23:10        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |  |  |  |  |  |

| Legend:           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-0 **CHDSA<31:0>:** Channel Destination Start Address bits Channel destination start address.

$\ensuremath{\textbf{Note:}}$  This must be the physical address of the destination.

# PIC32MX330/350/370/430/450/470

#### REGISTER 11-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 |                   |                   |                   | _                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 |                   |                   |                   | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | —                 |                   |                   |                   | _                 | _                | _                |

| 7:0          | R-x               | R-x               | R-x               | R-x               | R-x               | R-x               | U-0              | U-0              |

| 7.0          |                   | ENDP              | T<3:0>            |                   | DIR               | PPBI              |                  | _                |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the BDT, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 . . 0001 = Endpoint 1 0000 = Endpoint 0

- bit 3 **DIR:** Last BD Direction Indicator bit

- 1 = Last transaction was a transmit transfer (TX)

- 0 = Last transaction was a receive transfer (RX)

- bit 2 **PPBI:** Ping-Pong BD Pointer Indicator bit

- 1 = The last transaction was to the ODD BD bank

- 0 = The last transaction was to the EVEN BD bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF bit (U1IR<3>) is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

## TABLE 12-2: OUTPUT PIN SELECTION (CONTINUED)

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection        |

|----------------------|----------|-------------|----------------------------------------------|

| RPD9                 | RPD9R    | RPD9R<3:0>  | 0000 = No Connect                            |

| RPG6                 | RPG6R    | RPG6R<3:0>  | 0001 = U3RTS                                 |

| RPB8                 | RPB8R    | RPB8R<3:0>  | 0010 = U4TX                                  |

| RPB15                | RPB15R   | RPB15R<3:0> | 0011 = REFCLKO<br>0100 = U5TX <sup>(4)</sup> |

| RPD4                 | RPD4R    | RPD4R<3:0>  | 0100 = 001 x 0                               |

| RPB0                 | RPB0R    | RPB0R<3:0>  | 0110 = Reserved                              |

| RPE3                 | RPE3R    | RPE3R<3:0>  | 0111 = <u>SS1</u>                            |

| RPB7                 | RPB7R    | RPB7R<3:0>  | 1000 <b>= SDO1</b>                           |

| RPB2                 | RPB2R    | RPB2R<3:0>  | 1001 = Reserved                              |

| RPF12 <sup>(4)</sup> | RPF12R   | RPF12R<3:0> | 1010 = Reserved                              |

| RPD12 <sup>(4)</sup> | RPD12R   | RPD12R<3:0> |                                              |

| RPF8 <sup>(4)</sup>  | RPF8R    | RPF8R<3:0>  | 1100 - Reserved                              |

| RPC3 <sup>(4)</sup>  | RPC3R    | RPC3R<3:0>  | 1110 = Reserved                              |

| RPE9 <sup>(4)</sup>  | RPE9R    | RPE9R<3:0>  | 1111 = Reserved                              |

| RPD1                 | RPD1R    | RPD1R<3:0>  | 0000 = No Connect                            |

| RPG9                 | RPG9R    | RPG9R<3:0>  | 0001 = U2RTS                                 |

| RPB14                | RPB14R   | RPB14R<3:0> | 0010 = Reserved<br>0011 = U1RTS              |

| RPD0                 | RPD0R    | RPD0R<3:0>  | $0100 = U5TX^{(4)}$                          |

| RPD8                 | RPD8R    | RPD8R<3:0>  | 0101 = Reserved                              |

| RPB6                 | RPB6R    | RPB6R<3:0>  | 0110 = <u>SS2</u>                            |

| RPD5                 | RPD5R    | RPD5R<3:0>  | 0111 = Reserved<br>1000 = SDO1               |

| RPF3 <sup>(3)</sup>  | RPF3R    | RPF3R<3:0>  | 1000 = SDOT                                  |

| RPF6 <sup>(1)</sup>  | RPF6R    | RPF6R<3:0>  | 1010 = Reserved                              |

| RPF13 <sup>(4)</sup> | RPF13R   | RPF13R<3:0> | 1011 = OC2                                   |

| RPC2 <sup>(4)</sup>  | RPC2R    | RPC2R<3:0>  | 1100 = OC1<br>1101 = Reserved                |

| RPE8 <sup>(4)</sup>  | RPE8R    | RPE8R<3:0>  | 1110 = Reserved                              |

| RPF2 <sup>(5)</sup>  | RPF2R    | RPF2R<3:0>  | 1111 = Reserved                              |

**Note 1:** This selection is only available on General Purpose devices.

**2:** This selection is only available on 64-pin General Purpose devices.

3: This selection is only available on 100-pin General Purpose devices.

4: This selection is only available on 100-pin USB and General Purpose devices.

5: This selection is not available on 64-pin USB devices.

|                             |                                 | <u> </u>  | IC32MX        | 430F064       | 4L, PIC3      | 2MX450        | F128L | , PIC32 | MX450F       | 256L, A      | ND PIC3      | 32MX470      | F512L | DEVIC | ES ONL             | Y                  |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|-------|---------|--------------|--------------|--------------|--------------|-------|-------|--------------------|--------------------|--------------|--------------|---------------|

| ess                         |                                 |           |               |               |               |               |       |         |              | Bit          | s            |              |       |       |                    |                    |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11 | 26/10   | 25/9         | 24/8         | 23/7         | 22/6         | 21/5  | 20/4  | 19/3               | 18/2               | 17/1         | 16/0         | All<br>Resets |

| 6600                        | ANSELG                          | 31:16     | —             | —             | —             | —             | _     | _       |              |              | _            |              |       | —     |                    | _                  | —            | —            | 0000          |

| 0000                        | ANOLLO                          | 15:0      | —             | —             | —             | —             | —     | _       | ANSELG9      | ANSELG8      | ANSELG7      | ANSELG6      | —     | —     |                    | _                  | —            | —            | 01C0          |

| 6610                        | TRISG                           | 31:16     | —             | —             | —             | —             | —     | —       | —            | —            | —            | —            | —     | —     |                    | —                  | —            | —            | 0000          |

| 00.0                        |                                 | 15:0      | TRISG15       | TRISG14       | TRISG13       | TRISG12       | —     | —       | TRISG9       | TRISG8       | TRISG7       | TRISG6       | —     | —     | TRISG3             | TRISG2             | TRISG1       | TRISG0       | xxxx          |

| 6620                        | PORTG                           | 31:16     | _             |               |               | —             | _     | _       | —            | _            | —            | —            | _     | —     | —                  | —                  | —            | —            | 0000          |

| 0020                        |                                 | 15:0      | RG15          | RG14          | RG13          | RG12          | —     | —       | RG9          | RG8          | RG7          | RG6          | —     | —     | RG3 <sup>(2)</sup> | RG2 <sup>(2)</sup> | RG1          | RG0          | xxxx          |

| 6630                        | LATG                            | 31:16     | _             |               |               | -             | _     | —       | —            | —            | —            | —            | —     | —     | -                  | —                  | —            | —            | 0000          |

|                             |                                 | 15:0      | LATG15        | LATG14        | LATG13        | LATG12        | _     | —       | LATG9        | LATG8        | LATG7        | LATG6        | —     | —     | LATG3              | LATG2              | LATG1        | LATG0        | xxxx          |

| 6640                        | ODCG                            | 31:16     | —             | _             | _             | —             | —     | _       | —            | —            | —            | —            | —     | —     |                    | -                  | —            | —            | 0000          |

|                             |                                 | 15:0      | ODCG15        | ODCG14        | ODCG13        | ODCG12        | —     | _       | ODCG9        | ODCG8        | ODCG7        | ODCG6        | —     | —     | ODCG3              | ODCG2              | ODCG1        | ODCG0        | xxxx          |

| 6650                        | CNPUG                           | 31:16     | —             | _             | _             | —             | —     | _       | —            | —            | —            | —            | —     | —     |                    | -                  | —            | —            | 0000          |

|                             |                                 |           | CNPUG15       | CNPUG14       | CNPUG13       | CNPUG12       | —     | —       | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | _     | —     | CNPUG3             | CNPUG2             | CNPUG1       | CNPUG0       |               |

| 6660                        | CNPDG                           | 31:16     | —             | —             | —             | —             | —     | —       | —            |              | —            | —            | _     | —     | —                  | —                  | —            | —            | 0000          |

|                             |                                 |           | CNPDG15       | CNPDG14       | CNPDG13       | CNPDG12       | —     | —       | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       | _     | —     | CNPDG3             | CNPDG2             | CNPDG1       | CNPDG0       |               |

| 6670                        | CNCONG                          | 31:16     | -             | _             | -             | -             | _     | _       | _            | _            | _            | _            | _     | -     |                    | _                  | _            | -            | 0000          |

|                             |                                 | 15:0      | ON            | _             | SIDL          | -             | _     | _       | _            | _            | _            | _            | _     | -     |                    | _                  | _            | -            | 0000          |

| 6680                        | CNENG                           | 31:16     | -             | -             | -             | -             | _     | _       | -            | -            | -            | -            | _     | _     | -                  | -                  | -            | -            | 0000          |

|                             |                                 | 15:0      | CNIEG15       | CNIEG14       | CNIEG13       | CNIEG12       | _     | _       | CNIEG9       | CNIEG8       | CNIEG7       | CNIEG6       | _     | _     | CNIEG3             | CNIEG2             | CNIEG1       | CNIEG0       | xxxx          |

| 0000                        |                                 | 31:16     | -             | -             | -             | -             | _     | —       | —            | _            | —            | —            | _     | —     | —                  | —                  | —            | —            | 0000          |

| 6690                        | CNSTATG                         | 15:0      | CN<br>STATG15 | CN<br>STATG14 | CN<br>STATG13 | CN<br>STATG12 | —     | _       | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 | —     | —     | CN<br>STATG3       | CN<br>STATG2       | CN<br>STATG1 | CN<br>STATG0 | xxxx          |

# TABLE 12-15: PORTG REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

2: This bit only implemented on devices without a USB module.

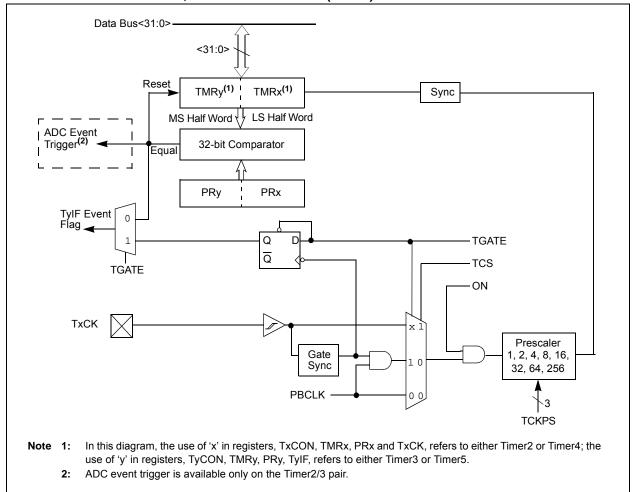

### FIGURE 14-2: TIMER2/3, 4/5 BLOCK DIAGRAM (32-BIT)<sup>(1)</sup>

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 21.24        | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN             | FRMSYPW           | F                 | RMCNT<2:0        | )>                    |

| 00.40        | R/W-0                  | U-0                | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |

| 23:16        | MCLKSEL <sup>(2)</sup> | —                  |                   | _                 | —                 | _                 | SPIFE            | ENHBUF <sup>(2)</sup> |

| 45.0         | R/W-0                  | U-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | ON <sup>(1)</sup> —    |                    | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |

| 7.0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | SSEN                   | CKP <sup>(4)</sup> | MSTEN             | DISSDI            | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |

#### REGISTER 18-1: SPIxCON: SPI CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

bit 31 FRMEN: Framed SPI Support bit

- 1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on <u>SSx</u> pin bit (Framed SPI mode only)

- 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 **FRMPOL:** Frame Sync Polarity bit (Framed SPI mode only)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 **MSSEN:** Master Mode Slave Select Enable bit

- 1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in FRAMED\_SYNC mode.

- 111 = Reserved; do not use

- 110 = Reserved; do not use

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

- 000 = Generate a frame sync pulse on every data character

- bit 23 MCLKSEL: Master Clock Enable bit<sup>(2)</sup>

- 1 = REFCLK is used by the Baud Rate Generator

- 0 = PBCLK is used by the Baud Rate Generator

- bit 22-18 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

# PIC32MX330/350/370/430/450/470

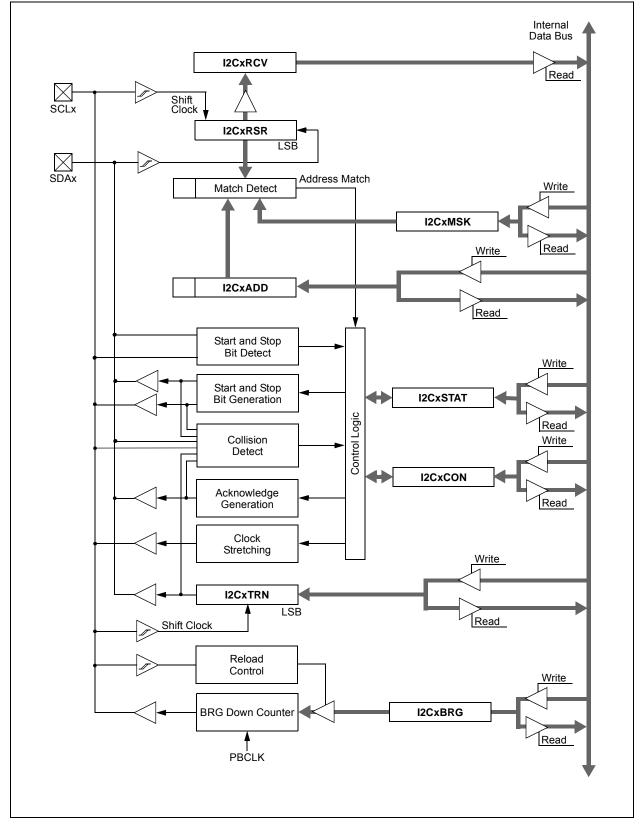

# FIGURE 19-1: I<sup>2</sup>C BLOCK DIAGRAM

# PIC32MX330/350/370/430/450/470

# REGISTER 19-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                 | —                 | _                 | —                 | —                 | —                 | _                | _                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                 | —                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |  |  |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |  |  |  |  |  |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |  |  |  |  |  |

| Legend:           | HC = Cleared in Hardwar | е                                  |                    |  |  |  |

|-------------------|-------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

- 1 = Enables the  $I^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the  $I^2$ C module; all  $I^2$ C pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

bit 12

- 0 = Hold SCLx clock low (clock stretch)

- If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

#### If STREN = 0: