#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32 ® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 128K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                |

| Supplier Device Package    | 124-VTLA (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx370f512lt-i-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

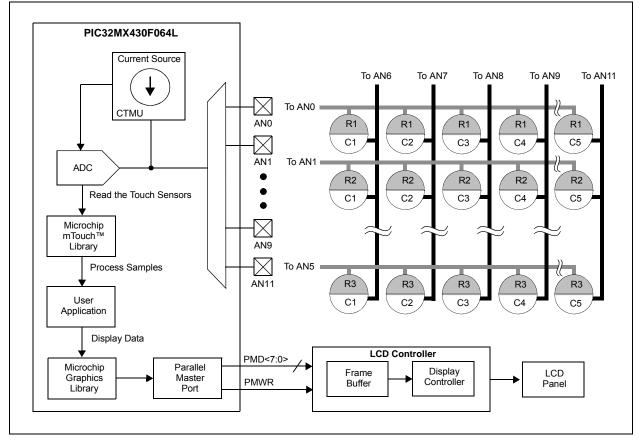

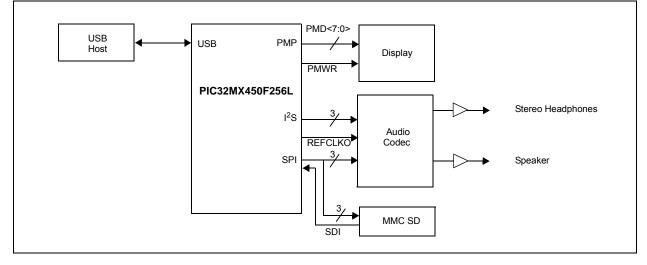

# 2.11 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-6, Figure 2-7, and Figure 2-8.

## FIGURE 2-6: CAPACITIVE TOUCH SENSING WITH GRAPHICS APPLICATION

## FIGURE 2-7: AUDIO PLAYBACK APPLICATION

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error. Fetch reference to protected address.                                                                    |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error. Load reference to protected address.                                                                      |

| AdES      | Store address alignment error. Store to protected address.                                                                              |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

# TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

# 3.3 Power Management

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core offers a number of power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

### 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 27.0 "Power-Saving Features".

## 3.3.2 LOCAL CLOCK GATING

The majority of the power consumed by the PIC32MX330/350/370/430/450/470 family core is in the clock tree and clocking registers. The PIC32MX family uses extensive use of local gated-clocks to reduce this dynamic power consumption.

# 3.4 EJTAG Debug Support

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K<sup>®</sup> core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/ 470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Memory" (DS60001121), Program which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX330/350/370/430/450/470 devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: On PIC32MX330/350/370/430/450/470 devices, the Flash page size is 4 KB and the row size is 512 bytes (1024 IW and 128 IW, respectively).

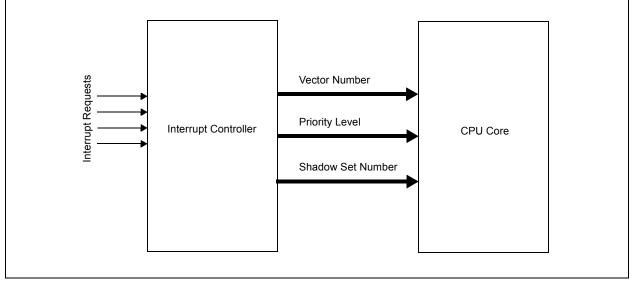

# 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX330/350/370/430/450/470 devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX330/350/370/430/450/470 interrupt module includes the following features:

- Up to 76 interrupt sources

- · Up to 46 interrupt vectors

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- Dedicated shadow set configurable for any priority level (see the FSRSSEL<2:0> bits (DEVCFG3<18:16>) in 28.0 "Special Features" for more information)

- Software can generate any interrupt

- User-configurable interrupt vector table location

- User-configurable interrupt vector spacing

# FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit Bit 29/21/13/5 28/20/12/4 |        | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------------------|--------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0                           | U-0    | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | —                             | _      | _                 |                   | _                | —                |

| 00.40        | U-0               | U-0               | U-0 U-0                       |        | U-0               | U-0               | U-0              | R/W-0            |

| 23:16        | —                 | —                 | —                             | _      | —                 | —                 | _                | CHECOH           |

| 45.0         | U-0               | U-0               | U-0                           | U-0    | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | —                             | -      | —                 |                   | DCSZ             | 2<1:0>           |

| 7.0          | U-0               | U-0               | R/W-0                         | R/W-0  | U-0               | R/W-1 R/W-1       |                  | R/W-1            |

| 7:0          | _                 | —                 | PREFE                         | N<1:0> | _                 | PFMWS<2:0>        |                  | >                |

#### REGISTER 9-1: CHECON: CACHE CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-17 Unimplemented: Write '0'; ignore read

- bit 16 CHECOH: Cache Coherency Setting on a PFM Program Cycle bit

- 1 = Invalidate all data and instruction lines

- 0 = Invalidate all data lnes and instruction lines that are not locked

- bit 15-10 Unimplemented: Write '0'; ignore read

- bit 9-8 DCSZ<1:0>: Data Cache Size in Lines bits

- 11 = Enable data caching with a size of 4 Lines

- 10 = Enable data caching with a size of 2 Lines

- 01 = Enable data caching with a size of 1 Line

- 00 = Disable data caching

Changing these bits induce all lines to be reinitialized to the "invalid" state.

bit 7-6 **Unimplemented:** Write '0'; ignore read

#### bit 5-4 **PREFEN<1:0>:** Predictive Prefetch Enable bits

- 11 = Enable predictive prefetch for both cacheable and non-cacheable regions

- 10 = Enable predictive prefetch for non-cacheable regions only

- 01 = Enable predictive prefetch for cacheable regions only

- 00 = Disable predictive prefetch

- bit 3 Unimplemented: Write '0'; ignore read

#### bit 2-0 PFMWS<2:0>: PFM Access Time Defined in Terms of SYSLK Wait States bits

- 111 = Seven Wait states

- 110 = Six Wait states

- 101 = Five Wait states

- 100 = Four Wait states

- 011 = Three Wait states

- 010 = Two Wait states

- 001 = One Wait state

- 000 = Zero Wait state

'1' = Bit is set

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 04-04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |

| 31:24        | CHEPFABT<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |

| 23:16        | CHEPFABT<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 15:8         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |

|              | CHEPFABT<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |  |

| 7:0          | CHEPFABT<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| Legend       | 1                 |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| R = Rea      | dable bit         |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ad as '0'        |                  |  |  |  |  |  |  |

# REGISTER 9-12: CHEPFABT: PREFETCH CACHE ABORT STATISTICS REGISTER

### bit 31-0 CHEPFABT<31:0>: Prefab Abort Count bits

-n = Value at POR

Incremented each time an automatic prefetch cache is aborted due to a non-sequential instruction fetch, load or store.

'0' = Bit is cleared

x = Bit is unknown

# PIC32MX330/350/370/430/450/470

#### REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |                       |        |       | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |

|--------------|----------------------------------|-----------------------|--------|-------|--------------------|-------------------|------------------|---------------------|

| 04.04        | U-0                              | U-0                   | R/W-0  | R/W-0 | R/W-0              | U-0               | U-0              | R/W-0               |

| 31:24        | —                                | —                     | BYTC   | <1:0> | WBO <sup>(1)</sup> | _                 | _                | BITO <sup>(1)</sup> |

| 23:16        | U-0                              | U-0                   | U-0    | U-0   | U-0                | U-0               | U-0              | U-0                 |

| 23:10        | —                                | —                     | —      | _     | _                  | _                 | _                | -                   |

| 45.0         | U-0                              | U-0                   | U-0    | R/W-0 | R/W-0              | R/W-0             | R/W-0            | R/W-0               |

| 15:8         | —                                | _                     | _      |       |                    | PLEN<4:0>         |                  |                     |

| 7.0          | R/W-0                            | R/W-0                 | R/W-0  | U-0   | U-0                | R/W-0             | R/W-0            | R/W-0               |

| 7:0          | CRCEN                            | CRCAPP <sup>(1)</sup> | CRCTYP |       | _                  | (                 |                  |                     |

# Legend:

| Legena.           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit<sup>(1)</sup>

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

#### <u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

#### bit 23-13 Unimplemented: Read as '0'

bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(1)</sup>

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial - 1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

# 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32 USB module includes the following features:

- USB full-speed support for host and device

- Low-speed host support

- USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, and other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

# PIC32MX330/350/370/430/450/470

#### REGISTER 11-7: U1IE: USB INTERRUPT ENABLE REGISTER

|              |                   | •                 |                   |                   |                   |                   |                                                                                                                                                                                                                                 |                         |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                                                                                                                                                                                                                | Bit<br>24/16/8/0        |

| 31:24        | U-0                                                                                                                                                                                                                             | U-0                     |

| 31:24        | -                 | —                 | —                 | -                 | —                 | —                 | -                                                                                                                                                                                                                               | —                       |

| 23:16        | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0                                                                                                                                                                                                                             | U-0                     |

| 23.10        | -                 | —                 | —                 | -                 | —                 | —                 | -                                                                                                                                                                                                                               | —                       |

| 15:8         | U-0               | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0                                                                                                                                                                                                                             | U-0                     |

| 15.0         | _                 | _                 | —                 | _                 | —                 | _                 | 25/17/9/1         24/1           U-0         U               U-0         U               U-0         U               U-0         U               W-0         U               R/W-0         R/M           LIEBRIE(1)         URS | —                       |

|              | R/W-0                                                                                                                                                                                                                           | R/W-0                   |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          |                   | TRNIE             | SOFIE             | церріе(1)                                                                                                                                                                                                                       | URSTIE <sup>(2)</sup>   |

|              | STALLIE           | ALIACHIE          | RESUMEIE          | IDLEIE            |                   | SOFIE             | UERRIE' /                                                                                                                                                                                                                       | DETACHIE <sup>(3)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | <b>STALLIE:</b> STALL Handshake Interrupt Enable bit<br>1 = STALL interrupt is enabled<br>0 = STALL interrupt is disabled         |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ATTACHIE: ATTACH Interrupt Enable bit<br>1 = ATTACH interrupt is enabled<br>0 = ATTACH interrupt is disabled                      |

| bit 5 | <b>RESUMEIE:</b> RESUME Interrupt Enable bit<br>1 = RESUME interrupt is enabled<br>0 = RESUME interrupt is disabled               |

| bit 4 | IDLEIE: Idle Detect Interrupt Enable bit<br>1 = Idle interrupt is enabled<br>0 = Idle interrupt is disabled                       |

| bit 3 | <b>TRNIE:</b> Token Processing Complete Interrupt Enable bit<br>1 = TRNIF interrupt is enabled<br>0 = TRNIF interrupt is disabled |

| bit 2 | <b>SOFIE:</b> SOF Token Interrupt Enable bit<br>1 = SOFIF interrupt is enabled<br>0 = SOFIF interrupt is disabled                 |

| bit 1 | UERRIE: USB Error Interrupt Enable bit <sup>(1)</sup><br>1 = USB Error interrupt is enabled                                       |

- 1 = USB Error interrupt is enabled 0 = USB Error interrupt is disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt is enabled

- 0 = URSTIF interrupt is disabled

- DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt is enabled

- 0 = DATTCHIF interrupt is disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

- 2: Device mode.

- 3: Host mode.

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Periphera<br>Selection |

|----------------------|----------|-------------|--------------------------------------|

| RPD2                 | RPD2R    | RPD2R<3:0>  | 0000 = No Connect                    |

| RPG8                 | RPG8R    | RPG8R<3:0>  | 0001 = U3TX                          |

| RPF4                 | RPF4R    | RPF4R<3:0>  | 0010 = U4RTS<br>0011 = Reserved      |

| RPD10                | RPD10R   | RPD10R<3:0> | 0100 = Reserved                      |

| RPF1                 | RPF1R    | RPF1R<3:0>  | 0101 = Reserved                      |

| RPB9                 | RPB9R    | RPB9R<3:0>  | 0110 = SDO2                          |

| RPB10                | RPB10R   | RPB10R<3:0> | 0111 = Reserved<br>1000 = Reserved   |

| RPC14                | RPC14R   | RPC14R<3:0> | 1000 = Reserved                      |

| RPB5                 | RPB5R    | RPB5R<3:0>  | 1010 = Reserved                      |

| RPC1 <sup>(4)</sup>  | RPC1R    | RPC1R<3:0>  | 1011 <b>= OC3</b>                    |

| RPD14 <sup>(4)</sup> | RPD14R   | RPD14R<3:0> | 1100 = Reserved<br>1101 = C2OUT      |

| RPG1 <sup>(4)</sup>  | RPG1R    | RPG1R<3:0>  | 1110 = Reserved                      |

| RPA14 <sup>(4)</sup> | RPA14R   | RPA14R<3:0> | 1111 = Reserved                      |

| RPD3                 | RPD3R    | RPD3R<3:0>  | 0000 = No Connect                    |

| RPG7                 | RPG7R    | RPG7R<3:0>  | 0001 = U2TX                          |

| RPF5                 | RPF5R    | RPF5R<3:0>  | 0010 = Reserved                      |

| RPD11                | RPD11R   | RPD11R<3:0> |                                      |

| RPF0                 | RPF0R    | RPF0R<3:0>  | 0100 = 05RTS(*)                      |

| RPB1                 | RPB1R    | RPB1R<3:0>  | 0110 = SDO2                          |

| RPE5                 | RPE5R    | RPE5R<3:0>  | 0111 = Reserved                      |

| RPC13                | RPC13R   | RPC13R<3:0> | 1000 <b>= SDO1</b>                   |

| RPB3                 | RPB3R    | RPB3R<3:0>  | 1001 = Reserved                      |

| RPF3 <sup>(2)</sup>  | RPF3R    | RPF3R<3:0>  | 1010 = Reserved                      |

| RPC4 <sup>(4)</sup>  | RPC4R    | RPC4R<3:0>  | 1011 = OC4<br>1100 = Reserved        |

| RPD15 <sup>(4)</sup> | RPD15R   | RPD15R<3:0> | 1100 - Reserved                      |

| RPG0 <sup>(4)</sup>  | RPG0R    | RPG0R<3:0>  | 1110 = Reserved                      |

| RPA15 <sup>(4)</sup> | RPA15R   | RPA15R<3:0> | 1111 = Reserved                      |

# TABLE 12-2: OUTPUT PIN SELECTION

Note 1: This selection is only available on General Purpose devices.

**2:** This selection is only available on 64-pin General Purpose devices.

3: This selection is only available on 100-pin General Purpose devices.

4: This selection is only available on 100-pin USB and General Purpose devices.

5: This selection is not available on 64-pin USB devices.

|                             | ONLY                            |           |       |       |               |               |       |       |      |              |              |        |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|---------------|---------------|-------|-------|------|--------------|--------------|--------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                         |                                 |           |       |       |               |               |       |       |      | Bi           | ts           |        |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13         | 28/12         | 27/11 | 26/10 | 25/9 | 24/8         | 23/7         | 22/6   | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6510                        | TRISF                           | 31:16     | _     | _     | _             |               | _     |       | _    |              |              |        | _            |              | -            |              | _            |              | 0000          |

| 0310                        | TRIST                           | 15:0      | _     | —     | TRISF13       | TRISF12       | —     | _     | —    | TRISF8       | TRISF7       | TRISF6 | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | xxxx          |

| 6520                        | PORTF                           | 31:16     | —     | —     | —             | —             | _     | -     | —    | -            | -            | -      | —            | _            | _            | -            | _            | -            | 0000          |

| 0520                        | TOKI                            | 15:0      | —     | —     | RF13          | RF12          | _     | -     | —    | RF8          | RF7          | RF6    | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | xxxx          |

| 6530                        | LATF                            | 31:16     | —     | —     | —             | —             | _     | -     | —    | -            | -            | -      | —            | _            | _            | -            | _            | -            | 0000          |

| 0000                        | LAII                            | 15:0      | —     | —     | LATF13        | LATF12        | _     | -     | —    | LATF8        | LATF7        | LATF6  | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | _     |       | —             | —             | —     | _     |      | _            | _            |        | —            | _            | _            | _            |              |              | 0000          |

| 0040                        | 0001                            | 15:0      | _     |       | ODCF13        | ODCF12        | —     | _     |      | ODCF8        | ODCF7        | ODCF6  | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | xxxx          |

| 6550                        | CNPUF                           | 31:16     | —     |       | —             | —             | —     | —     |      | —            | —            | —      | —            | —            | —            | —            | —            | _            | 0000          |

| 0000                        |                                 | 15:0      | —     | —     | CNPUF13       | CNPUF12       | —     | —     | —    | CNPUF8       | CNPUF7       | CNPUF6 | CNPUF5       | CNPUF4       | CNPDF3       | CNPUF2       | CNPUF1       | CNPUF0       | xxxx          |

| 6560                        | CNPDF                           | 31:16     | —     | —     | —             | —             | —     | _     | —    | —            | _            | _      | —            | _            | —            | _            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | —     | CNPDF13       | CNPDF12       | —     | -     | —    | CNPDF8       | CNPDF7       | CNPDF6 | CNPDF5       | CNPDF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | xxxx          |

| 6570                        | CNCONF                          | 31:16     | —     | —     | —             | —             | —     | -     | —    | -            | -            | _      | —            | _            | —            | -            | —            | —            | 0000          |

|                             |                                 | 15:0      | ON    | —     | SIDL          | —             | —     | -     | —    | -            | -            | _      | —            | _            | —            | -            | —            | —            | 0000          |

| 6580                        | CNENF                           | 31:16     | —     | —     | —             | —             | —     | -     | —    | -            | -            | _      | —            | _            | —            | -            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | —     | CNIEF13       | CNIEF12       | —     | -     | —    | CNIEF8       | CNIEF7       | _      | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | xxxx          |

|                             |                                 | 31:16     | —     | —     | —             | —             | —     | -     | —    | -            | -            | _      | —            | _            | -            | -            | —            | —            | 0000          |

| 6590                        | CNSTATF                         | 15:0      | _     | —     | CN<br>STATF13 | CN<br>STATF12 | _     | _     | —    | CN<br>STATF8 | CN<br>STATF7 | _      | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | xxxx          |

TABLE 12-11: PORTF REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, AND PIC32MX370F512L DEVICES

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

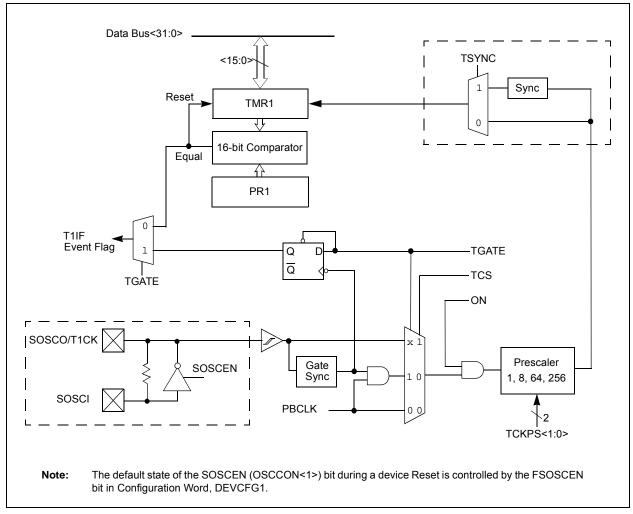

# 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a freerunning interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- · Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

## 13.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

# 20.2 Timing Diagrams

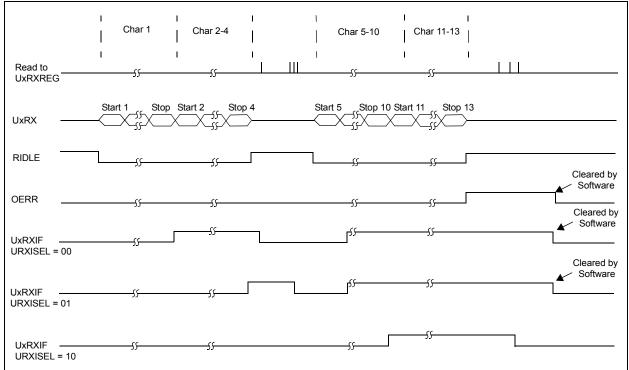

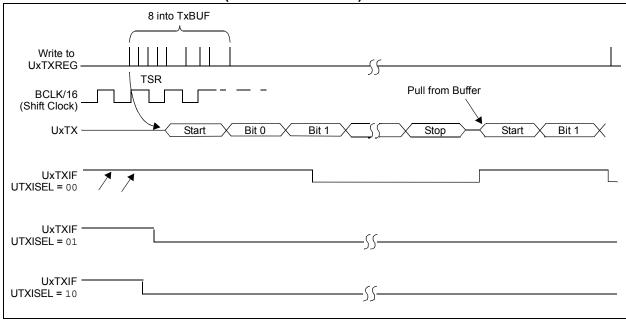

Figure 20-2 and Figure 20-3 illustrate typical receive and transmit timing for the UART module.

# FIGURE 20-2: UART RECEPTION

#### FIGURE 20-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

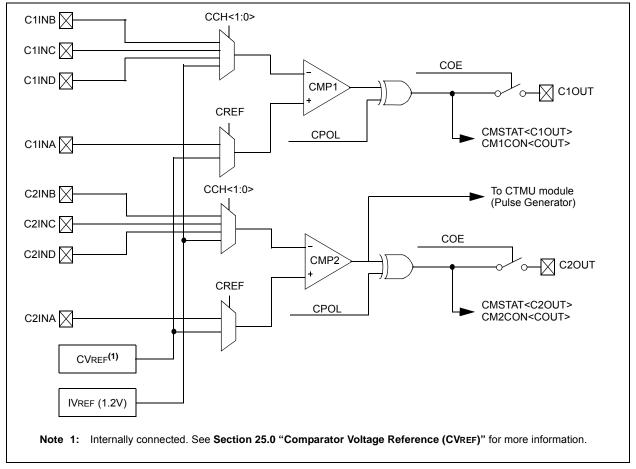

# 24.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer Section 19. to "Comparator" (DS60001110), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Analog Comparator module contains two comparators that can be configured in a variety of ways.

The following are key features of this module:

- · Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be Inverted

- Selectable interrupt generation

A block diagram of the comparator module is provided in Figure 24-1.

#### FIGURE 24-1: COMPARATOR BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | _                 | -                 | -                 | —                 | _                 | —                | _                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   | _                 | _                 | _                 | —                 |                   | _                | -                |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | _                 | —                 | _                 | _                | _                |  |  |

| 7.0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | _                 | CVROE             | CVRR              | CVRSS             | CVR<3:0>          |                   |                  |                  |  |  |

### **REGISTER 25-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator Voltage Reference On bit<sup>(1)</sup>

- 1 = Module is enabled

Setting this bit does not affect other bits in the register.

- 0 = Module is disabled and does not consume current

- Clearing this bit does not affect the other bits in the register.

- bit 14-7 Unimplemented: Read as '0'

- bit 6 **CVROE:** CVREFOUT Enable bit

- 1 = Voltage level is output on CVREFOUT pin

- 0 = Voltage level is disconnected from CVREFOUT pin

- bit 5 CVRR: CVREF Range Selection bit

- 1 = 0 to 0.67 CVRSRC, with CVRSRC/24 step size

- 0 = 0.25 CVRSRC to 0.75 CVRSRC, with CVRSRC/32 step size

- bit 4 **CVRSS:** CVREF Source Selection bit

- 1 = Comparator voltage reference source, CVRSRC = (VREF+) (VREF-)

- 0 = Comparator voltage reference source, CVRSRC = AVDD AVSS

bit 3-0 **CVR<3:0>:** CVREF Value Selection  $0 \le CVR<3:0> \le 15$  bits

$\frac{\text{When CVRR = 1:}}{\text{CVREF = (CVR<3:0>/24) \bullet (CVRSRC)}}$  $\frac{\text{When CVRR = 0:}}{\text{CVREF = 1/4 \bullet (CVRSRC) + (CVR<3:0>/32) \bullet (CVRSRC)}}$

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

NOTES:

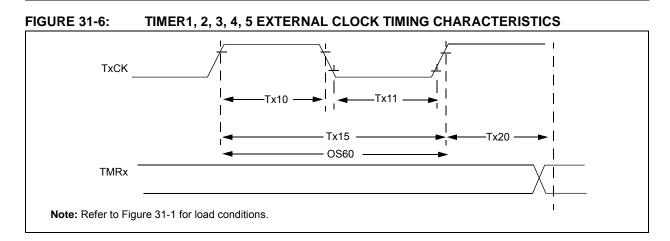

# TABLE 31-24: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

| AC CHARACTERISTICS |           |                                                                                                     |                              | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                                            |         |      |       |                               |  |

|--------------------|-----------|-----------------------------------------------------------------------------------------------------|------------------------------|------------------------------------------------------|--------------------------------------------|---------|------|-------|-------------------------------|--|

| Param.<br>No.      | Symbol    | Characteristics <sup>(2)</sup>                                                                      |                              |                                                      | Min.                                       | Typical | Max. | Units | Conditions                    |  |

| -                  |           | TxCK<br>High Time                                                                                   | Synchronous, with prescaler  |                                                      | [(12.5 ns or 1 Трв)/N]<br>+ 25 ns          | —       | —    | ns    | Must also meet parameter TA15 |  |

|                    |           |                                                                                                     | Asynchronous, with prescaler |                                                      | 10                                         | —       | —    | ns    | _                             |  |

| TA11 TTXL          |           | TxCK<br>Low Time                                                                                    | Synchronous, with prescaler  |                                                      | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns          | —       | _    | ns    | Must also meet parameter TA15 |  |

|                    |           |                                                                                                     | Asynchronous, with prescaler |                                                      | 10                                         | _       | _    | ns    | —                             |  |

| TA15               | ΤτχΡ      | TxCK<br>Input Period                                                                                | Synchronous, with prescaler  |                                                      | [(Greater of 25 ns or<br>2 Трв)/N] + 30 ns | —       | _    | ns    | VDD > 2.7V                    |  |

|                    |           |                                                                                                     |                              |                                                      | [(Greater of 25 ns or<br>2 TPB)/N] + 50 ns | —       | _    | ns    | VDD < 2.7V                    |  |

|                    |           |                                                                                                     | Asynchronous with prescaler  |                                                      | 20                                         | —       | _    | ns    | VDD > 2.7V<br>(Note 3)        |  |

|                    |           |                                                                                                     |                              |                                                      | 50 –                                       |         | _    | ns    | VDD < 2.7V<br><b>(Note 3)</b> |  |

| OS60               | FT1       | SOSC1/T1CK Oscillator<br>Input Frequency Range<br>(oscillator enabled by set<br>TCS bit (T1CON<1>)) |                              |                                                      | 32                                         | _       | 100  | kHz   | _                             |  |

| TA20               | TCKEXTMRL | Delay from External TxC<br>Clock Edge to Timer<br>Increment                                         |                              | CK                                                   | _                                          |         | 1    | Трв   | —                             |  |

Note 1: Timer1 is a Type A.

**2:** This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).

# PIC32MX330/350/370/430/450/470

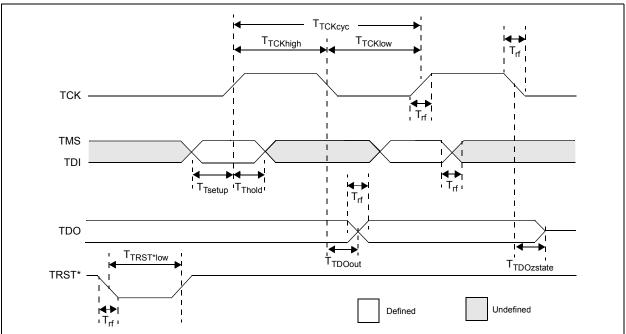

## FIGURE 31-23: EJTAG TIMING CHARACTERISTICS

#### TABLE 31-43: EJTAG TIMING REQUIREMENTS

| AC CHARACTERISTICS |            |                                                  | Standard Operating Co<br>(unless otherwise state<br>Operating temperature |      |       |            |

|--------------------|------------|--------------------------------------------------|---------------------------------------------------------------------------|------|-------|------------|

| Param.<br>No.      | Symbol     | Description <sup>(1)</sup>                       | Min.                                                                      | Max. | Units | Conditions |

| EJ1                | Ттсксүс    | TCK Cycle Time                                   | 25                                                                        | —    | ns    | —          |

| EJ2                | Ттскнідн   | TCK High Time                                    | 10                                                                        | —    | ns    | —          |

| EJ3                | TTCKLOW    | TCK Low Time                                     | 10                                                                        | —    | ns    | —          |

| EJ4                | TTSETUP    | TAP Signals Setup Time Before<br>Rising TCK      | 5                                                                         | —    | ns    | _          |

| EJ5                | TTHOLD     | TAP Signals Hold Time After<br>Rising TCK        | 3                                                                         | _    | ns    | —          |

| EJ6                | Ττροουτ    | TDO Output Delay Time from<br>Falling TCK        |                                                                           | 5    | ns    | —          |

| EJ7                | TTDOZSTATE | TDO 3-State Delay Time from<br>Falling TCK       |                                                                           | 5    | ns    | _          |

| EJ8                | TTRSTLOW   | TRST Low Time                                    | 25                                                                        | —    | ns    |            |

| EJ9                | Trf        | TAP Signals Rise/Fall Time, All Input and Output |                                                                           |      | ns    | _          |

Note 1: These parameters are characterized, but not tested in manufacturing.

NOTES:

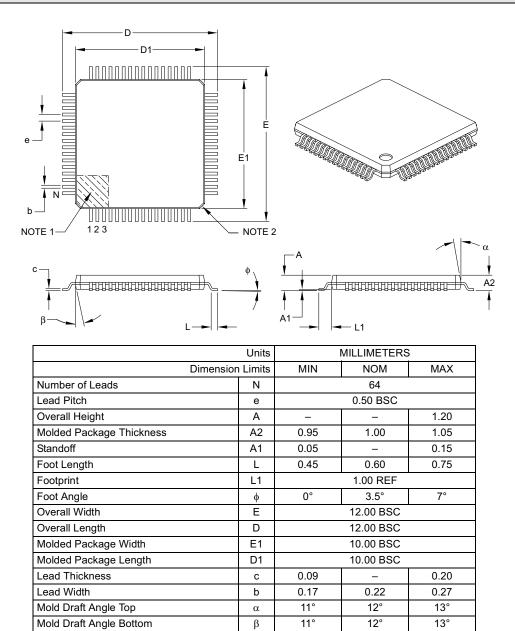

# 33.2 Package Details

The following sections give the technical details of the packages.

# 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B