Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART                            |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 128K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx370f512lt-v-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

# 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e<sup>®</sup>, is also available by accessing the CP0 registers, listed in Table 3-2.

| Reserved<br>HWREna<br>BadVAddr <sup>(1)</sup><br>Count <sup>(1)</sup><br>Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup> | Reserved in the PIC32MX330/350/370/430/450/470 family core.         Enables access via the RDHWR instruction to selected hardware registers.         Reports the address for the most recent address-related exception.         Processor cycle count.         Reserved in the PIC32MX330/350/370/430/450/470 family core.         Timer interrupt control. |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BadVAddr <sup>(1)</sup><br>Count <sup>(1)</sup><br>Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                       | Reports the address for the most recent address-related exception.<br>Processor cycle count.<br>Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                 |

| Count <sup>(1)</sup><br>Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                                                  | Processor cycle count.<br>Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                       |

| Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                                                                          | Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                                                 |

| Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                                                                                      |                                                                                                                                                                                                                                                                                                                                                             |

| Status <sup>(1)</sup>                                                                                                                | Timer interrupt control.                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                             |

| (4)                                                                                                                                  | Processor status and control.                                                                                                                                                                                                                                                                                                                               |

| IntCtl <sup>(1)</sup>                                                                                                                | Interrupt system status and control.                                                                                                                                                                                                                                                                                                                        |

| SRSCtl <sup>(1)</sup>                                                                                                                | Shadow register set status and control.                                                                                                                                                                                                                                                                                                                     |

| SRSMap <sup>(1)</sup>                                                                                                                | Provides mapping from vectored interrupt to a shadow set.                                                                                                                                                                                                                                                                                                   |

| Cause <sup>(1)</sup>                                                                                                                 | Cause of last general exception.                                                                                                                                                                                                                                                                                                                            |

| EPC <sup>(1)</sup>                                                                                                                   | Program counter at last exception.                                                                                                                                                                                                                                                                                                                          |

| PRId                                                                                                                                 | Processor identification and revision.                                                                                                                                                                                                                                                                                                                      |

| EBASE                                                                                                                                | Exception vector base register.                                                                                                                                                                                                                                                                                                                             |

| Config                                                                                                                               | Configuration register.                                                                                                                                                                                                                                                                                                                                     |

| Config1                                                                                                                              | Configuration register 1.                                                                                                                                                                                                                                                                                                                                   |

| Config2                                                                                                                              | Configuration register 2.                                                                                                                                                                                                                                                                                                                                   |

| Config3                                                                                                                              | Configuration register 3.                                                                                                                                                                                                                                                                                                                                   |

| Reserved                                                                                                                             | Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                                                 |

| Debug <sup>(2)</sup>                                                                                                                 | Debug control and exception status.                                                                                                                                                                                                                                                                                                                         |

| DEPC <sup>(2)</sup>                                                                                                                  | Program counter at last debug exception.                                                                                                                                                                                                                                                                                                                    |

| Reserved                                                                                                                             | Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                                                 |

| ErrorEPC <sup>(1)</sup>                                                                                                              | Program counter at last error.                                                                                                                                                                                                                                                                                                                              |

| DESAVE <sup>(2)</sup>                                                                                                                | Debug handler scratchpad register.                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                      | RSMap <sup>(1)</sup><br>Cause <sup>(1)</sup><br>PC <sup>(1)</sup><br>PRId<br>BASE<br>Config<br>Config1<br>Config2<br>Config3<br>Reserved<br>Debug <sup>(2)</sup><br>DEPC <sup>(2)</sup><br>Reserved<br>ErrorEPC <sup>(1)</sup>                                                                                                                              |

TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used during debug.

# 4.2 Bus Matrix Registers

# TABLE 4-2: BUS MATRIX REGISTER MAP

|                             |                         | -         |                     |                         |       |       |       |           |      |      |      |               |      |           |           |           |          |          |               |

|-----------------------------|-------------------------|-----------|---------------------|-------------------------|-------|-------|-------|-----------|------|------|------|---------------|------|-----------|-----------|-----------|----------|----------|---------------|

| ress                        | 2                       | e         |                     |                         |       |       |       |           |      |      |      | Bits          |      |           |           |           |          |          |               |

| Virtual Address<br>(BF88_#) | Register<br>Name        | Bit Range | 31/15               | 30/14                   | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8 | 23/7 | 22/6          | 21/5 | 20/4      | 19/3      | 18/2      | 17/1     | 16/0     | All<br>Resets |

| 2000                        | BMXCON <sup>(1)</sup>   | 31:16     | —                   |                         |       |       |       | BMXCHEDMA |      |      | —    | —             |      | BMXERRIXI | BMXERRICD | BMXERRDMA | BMXERRDS | BMXERRIS | 041F          |

| 2000                        | BIVIACON                | 15:0      | _                   | BMXWSDRM BMXARB<2:0> 00 |       |       |       |           |      |      |      | 0047          |      |           |           |           |          |          |               |

| 2010                        | BMXDKPBA <sup>(1)</sup> | 31:16     | _                   | _                       | -     | -     |       | —         | _    |      | _    | _             | _    | —         | -         | _         | —        | —        | 0000          |

| 2010                        | DIVIADIAL DA            | 15:0      |                     | BMXDKPBA<15:0> 0000     |       |       |       |           |      |      |      |               |      |           |           |           |          |          |               |

| 2020                        | BMXDUDBA <sup>(1)</sup> | 31:16     | —                   | _                       | —     | —     | —     | —         | —    | —    | —    | _             | _    | —         | —         | _         | _        | —        | 0000          |

| 2020                        |                         | 15:0      | BMXDUDBA<15:0> 0000 |                         |       |       |       |           |      |      |      | 0000          |      |           |           |           |          |          |               |

| 2030                        | BMXDUPBA <sup>(1)</sup> | 31:16     | _                   | _                       | —     | —     | _     | —         | _    | —    | _    | _             | _    | —         | —         | —         |          | —        | 0000          |

| 2000                        | 5                       | 15:0      |                     |                         |       |       |       |           |      |      | BM   | XDUPBA<15:0>  | •    |           |           |           |          |          | 0000          |

| 2040                        | BMXDRMSZ                | 31:16     |                     |                         |       |       |       |           |      |      | BM   | XDRMSZ<31:0>  |      |           |           |           |          |          | xxxx          |

|                             |                         | 15:0      |                     | 1                       |       |       |       |           |      |      |      |               |      |           |           |           |          |          | xxxx          |

| 2050                        | BMXPUPBA <sup>(1)</sup> | 31:16     | —                   | _                       | —     | —     | —     | -         | —    | —    | —    | —             | —    | —         |           | BMXPUPBA  | <19:16>  |          | 0000          |

|                             |                         | 15:0      |                     |                         |       |       |       |           |      |      | BM   | XPUPBA<15:0>  |      |           |           |           |          |          | 0000          |

| 2060                        | BMXPFMSZ                | 31:16     |                     |                         |       |       |       |           |      |      | BM   | XPFMSZ<31:0>  |      |           |           |           |          |          | XXXX          |

|                             |                         | 15:0      |                     |                         |       |       |       |           |      |      |      |               |      |           |           |           |          |          | XXXX          |

| 2070                        | BMXBOOTSZ               | 31:16     |                     |                         |       |       |       |           |      |      | BMX  | (BOOTSZ<31:0) | >    |           |           |           |          |          | 0000          |

|                             |                         | 15:0      |                     |                         |       |       |       |           |      |      |      |               |      |           |           |           |          |          | 0000          |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Interrupt Source <sup>(1)</sup>    | IRQ # | Vector |               |              | Persistent   |              |           |

|------------------------------------|-------|--------|---------------|--------------|--------------|--------------|-----------|

| Interrupt Source."                 | IKQ # | #      | Flag          | Enable       | Priority     | Sub-priority | Interrupt |

| CNB – PORTB Input Change Interrupt | 45    | 33     | IFS1<13>      | IEC1<13>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CNC – PORTC Input Change Interrupt | 46    | 33     | IFS1<14>      | IEC1<14>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CND – PORTD Input Change Interrupt | 47    | 33     | IFS1<15>      | IEC1<15>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CNE – PORTE Input Change Interrupt | 48    | 33     | IFS1<16>      | IEC1<16>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CNF – PORTF Input Change Interrupt | 49    | 33     | IFS1<17>      | IEC1<17>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CNG – PORTG Input Change Interrupt | 50    | 33     | IFS1<18>      | IEC1<18>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| PMP – Parallel Master Port         | 51    | 34     | IFS1<19>      | IEC1<19>     | IPC8<20:18>  | IPC8<17:16>  | Yes       |

| PMPE – Parallel Master Port Error  | 52    | 34     | IFS1<20>      | IEC1<20>     | IPC8<20:18>  | IPC8<17:16>  | Yes       |

| SPI2E – SPI2 Fault                 | 53    | 35     | IFS1<21>      | IEC1<21>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |

| SPI2RX – SPI2 Receive Done         | 54    | 35     | IFS1<22>      | IEC1<22>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |

| SPI2TX – SPI2 Transfer Done        | 55    | 35     | IFS1<23>      | IEC1<23>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |

| U2E – UART2 Error                  | 56    | 36     | IFS1<24>      | IEC1<24>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |

| U2RX – UART2 Receiver              | 57    | 36     | IFS1<25>      | IEC1<25>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |

| U2TX – UART2 Transmitter           | 58    | 36     | IFS1<26>      | IEC1<26>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |

| I2C2B – I2C2 Bus Collision Event   | 59    | 37     | IFS1<27>      | IEC1<27>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |

| I2C2S – I2C2 Slave Event           | 60    | 37     | IFS1<28>      | IEC1<28>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |

| I2C2M – I2C2 Master Event          | 61    | 37     | IFS1<29>      | IEC1<29>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |

| U3E – UART3 Error                  | 62    | 38     | IFS1<30>      | IEC1<30>     | IPC9<20:18>  | IPC9<17:16>  | Yes       |

| U3RX – UART3 Receiver              | 63    | 38     | IFS1<31>      | IEC1<31>     | IPC9<20:18>  | IPC9<17:16>  | Yes       |

| U3TX – UART3 Transmitter           | 64    | 38     | IFS2<0>       | IEC2<0>      | IPC9<20:18>  | IPC9<17:16>  | Yes       |

| U4E – UART4 Error                  | 65    | 39     | IFS2<1>       | IEC2<1>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |

| U4RX – UART4 Receiver              | 66    | 39     | IFS2<2>       | IEC2<2>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |

| U4TX – UART4 Transmitter           | 67    | 39     | IFS2<3>       | IEC2<3>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |

| U5E – UART5 Error                  | 68    | 40     | IFS2<4>       | IEC2<4>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |

| U5RX – UART5 Receiver              | 69    | 40     | IFS2<5>       | IEC2<5>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |

| U5TX – UART5 Transmitter           | 70    | 40     | IFS2<6>       | IEC2<6>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |

| CTMU – CTMU Event                  | 71    | 41     | IFS2<7>       | IEC2<7>      | IPC10<12:10> | IPC10<9:8>   | Yes       |

| DMA0 – DMA Channel 0               | 72    | 42     | IFS2<8>       | IEC2<8>      | IPC10<20:18> | IPC10<17:16> | No        |

| DMA1 – DMA Channel 1               | 73    | 43     | IFS2<9>       | IEC2<9>      | IPC10<28:26> | IPC10<25:24> | No        |

| DMA2 – DMA Channel 2               | 74    | 44     | IFS2<10>      | IEC2<10>     | IPC11<4:2>   | IPC11<1:0>   | No        |

| DMA3 – DMA Channel 3               | 75    | 45     | IFS2<11>      | IEC2<11>     | IPC11<12:10> | IPC11<9:8>   | No        |

|                                    |       | Lowe   | st Natural Or | der Priority |              |              |           |

## TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX330/350/370/430/450/470 Controller Family Features" for the list of available peripherals.

# TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 3 REGISTER MAP (CONTINUED)

| ess                         |                                 | Ċ,            |        |             |       |       |        |       |      | Bi     | ts      |        |        |        |        |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------|-------------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|--------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14       | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3   | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH2CPTR                        | 31:16         | —      | _           | —     | —     |        | —     | —    | —      | _       | —      | —      | _      | _      | _      | —      | —      | 0000       |

| 0200                        | DONZOLIK                        | 15:0          |        |             |       |       |        |       |      | CHCPT  | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 3290                        | DCH2DAT                         | 31:16         | —      | —           | —     | _     | —      | _     | —    | —      | _       | —      | —      | _      | _      | _      | —      | _      | 0000       |

| 3290                        | DCHZDAI                         | 15:0          | -      |             | _     | —     | —      |       | —    | _      |         |        |        | CHPDA  | T<7:0> |        |        |        | 0000       |

| 32A0                        | DCH3CON                         | 31:16         | _      | _           | _     | —     | _      |       | _    | _      | _       |        | _      | _      |        | _      | _      | —      | 0000       |

| 32AU                        | DCH3CON                         | 15:0          | CHBUSY | -           | —     | —     | —      | -     | _    | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | -      | CHEDET | CHPR   | l<1:0> | 0000       |

| 32B0                        | DCH3ECON                        | 31:16         | —      |             |       |       |        |       |      |        |         |        | 00FF   |        |        |        |        |        |            |

| 0200                        | DONOLOON                        | 15:0          |        |             |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN | _      | —      | —      | FFF8       |

| 32C0                        | DCH3INT                         | 31:16         | _      | —           | _     | —     | _      | _     | _    | _      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE | CHCCIE | CHTAIE | CHERIE |            |

| 0200                        | 20110111                        | 15:0          | —      | —           | —     | —     | —      | _     | —    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF | CHCCIF | CHTAIF | CHERIF |            |

| 32D0                        | DCH3SSA                         | 31:16         |        | CHSSA<31:0> |       |       |        |       |      |        |         |        |        |        |        |        |        |        |            |

|                             |                                 | 15:0          |        |             |       |       |        |       |      |        |         |        |        |        |        |        |        |        | 0000       |

| 32E0                        | DCH3DSA                         | 31:16<br>15:0 |        |             |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         | _      | _           | _     |       |        | _     | _    |        |         | _      | _      |        | _      |        |        |        | 0000       |

| 32F0                        | DCH3SSIZ                        | 15:0          |        |             |       |       |        |       |      | CHSSIZ | 2<15:0> |        |        |        |        |        |        |        | 0000       |

|                             |                                 | 31:16         | _      | _           | _     | _     |        | _     |      | _      | _       | _      | _      | _      | _      | _      |        |        | 0000       |

| 3300                        | DCH3DSIZ                        | 15:0          |        |             |       |       |        |       |      | CHDSIZ | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 0040                        | DOLIGODTO                       | 31:16         | _      | _           | —     | _     | _      | _     | _    | —      | _       | _      | —      | _      | _      | _      | _      |        | 0000       |

| 3310                        | DCH3SPTR                        | 15:0          |        |             |       |       |        |       |      | CHSPT  | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 2220                        | DCH3DPTR                        | 31:16         | —      | —           | —     | —     | _      | —     | _    | —      | —       | —      | —      | —      | —      | —      | _      | _      | 0000       |

| 3320                        | DCH3DFTK                        | 15:0          |        |             | -     |       |        |       | -    | CHDPT  | R<15:0> |        | _      |        |        |        | -      |        | 0000       |

| 3330                        | DCH3CSIZ                        | 31:16         | —      | —           | —     | —     | _      | _     | —    | —      | —       | —      | —      | _      | —      | —      | —      | —      | 0000       |

| 0000                        | DOLIDOOIT                       | 15:0          |        |             |       |       |        |       |      | CHCSIZ | 2<15:0> |        |        |        |        |        |        |        | 0000       |

| 3340                        | DCH3CPTR                        | 31:16         | —      | —           | —     | —     | —      | —     | —    | —      | —       | —      | —      | _      | —      | —      | —      | —      | 0000       |

|                             |                                 | 15:0          |        |             |       |       |        |       |      | CHCPT  | R<15:0> |        |        |        |        |        |        |        | 0000       |

| 3350                        | DCH3DAT                         | 31:16         | _      | —           | —     |       | _      | —     | —    |        | _       | —      | —      |        | —      | —      | —      |        | 0000       |

|                             |                                 | 15:0          | —      | —           | —     | —     | —      | —     | —    | —      |         |        |        | CHPDA  | 1<7:0> |        |        |        | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Note 1:

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   |                   |                   |                   |                   | —                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   |                   |                   |                   |                   | —                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | -                 | -                 | —                 | —                 | -                 | —                 | —                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

## REGISTER 11-4: U10TGCON: USB OTG CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

| bit 7 | DPPULUP: D+ Pull-Up Enable bit |

|-------|--------------------------------|

|       |                                |

- 1 = D+ data line pull-up resistor is enabled

- 0 = D+ data line pull-up resistor is disabled

### bit 6 **DMPULUP:** D- Pull-Up Enable bit

- 1 = D- data line pull-up resistor is enabled

- 0 = D- data line pull-up resistor is disabled

# bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

- 1 = D+ data line pull-down resistor is enabled

- 0 = D+ data line pull-down resistor is disabled

### bit 4 DMPULDWN: D- Pull-Down Enable bit

- 1 = D- data line pull-down resistor is enabled

- 0 = D- data line pull-down resistor is disabled

- bit 3 **VBUSON:** VBUS Power-on bit

- 1 = VBUS line is powered

- 0 = VBUS line is not powered

- bit 2 OTGEN: OTG Functionality Enable bit

- 1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

- 0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

## bit 1 VBUSCHG: VBUS Charge Enable bit

- 1 = VBUS line is charged through a pull-up resistor

- 0 = VBUS line is not charged through a resistor

### bit 0 VBUSDIS: VBUS Discharge Enable bit

- 1 = VBUS line is discharged through a pull-down resistor

- 0 = VBUS line is not discharged through a resistor

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 |                   | —                 | _                      | —                 | —                | _                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | —                 | —                 |                   | —                 | _                      | —                 | —                | _                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | —                 | —                 |                   | —                 | _                      | —                 | —                | _                |  |  |  |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |  |  |  |

| 7.0          | UACTPND           | _                 |                   | USLPGRD           | USBBUSY <sup>(1)</sup> |                   | USUSPEND         | USBPWR           |  |  |  |

## REGISTER 11-5: U1PWRC: USB POWER CONTROL REGISTER

## Legend:

| zogonai                           |                  |                            |                    |

|-----------------------------------|------------------|----------------------------|--------------------|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

## bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; but an interrupt is pending, it has not been generated yet

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- **Note:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                              | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------|------------------|

| 31:24        | U-0                                           | U-0              |

|              |                   | —                 | —                 | —                 |                   | —                 | —                                             | —                |

| 00.16        | U-0                                           | U-0              |

| 23:16        |                   |                   | _                 | _                 | _                 | _                 | _                                             | —                |

| 15:8         | U-0                                           | U-0              |

| 10.0         | _                 | _                 | _                 | _                 |                   | _                 | _                                             | —                |

|              | R/W-0                                         | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup><br>EOFEE <sup>(2)</sup> | PIDEE            |

## REGISTER 11-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

#### Legend:

| a Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|---------------------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR               | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

### bit 31-8 Unimplemented: Read as '0'

| bit 7 | <b>BTSEE:</b> Bit Stuff Error Interrupt Enable bit |

|-------|----------------------------------------------------|

|       |                                                    |

- 1 = BTSEF interrupt is enabled

- 0 = BTSEF interrupt is disabled

- bit 6 BMXEE: Bus Matrix Error Interrupt Enable bit

- 1 = BMXEF interrupt is enabled

- 0 = BMXEF interrupt is disabled

- bit 5 **DMAEE:** DMA Error Interrupt Enable bit

- 1 = DMAEF interrupt is enabled

- 0 = DMAEF interrupt is disabled

- bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

- 1 = BTOEF interrupt is enabled

- 0 = BTOEF interrupt is disabled

- bit 3 **DFN8EE:** Data Field Size Error Interrupt Enable bit

- 1 = DFN8EF interrupt is enabled

- 0 = DFN8EF interrupt is disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

## Note 1: Device mode.

2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

# PIC32MX330/350/370/430/450/470

## REGISTER 11-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 |      |        |     |     | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|------|--------|-----|-----|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0  | U-0    | U-0 | U-0 | U-0               | U-0              | U-0              |

| 31.24        |                   | —    |        |     |     | _                 | _                | _                |

| 23:16        | U-0               | U-0  | U-0    | U-0 | U-0 | U-0               | U-0              | U-0              |

| 23.10        |                   | —    |        |     |     | _                 | _                | _                |

| 15:8         | U-0               | U-0  | U-0    | U-0 | U-0 | U-0               | U-0              | U-0              |

| 15.0         |                   | —    |        |     |     | _                 | _                | _                |

| 7:0          | R-x               | R-x  | R-x    | R-x | R-x | R-x               | U-0              | U-0              |

| 7:0          |                   | ENDP | T<3:0> |     | DIR | PPBI              |                  | _                |

## Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the BDT, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 . . 0001 = Endpoint 1 0000 = Endpoint 0

- bit 3 **DIR:** Last BD Direction Indicator bit

- 1 = Last transaction was a transmit transfer (TX)

- 0 = Last transaction was a receive transfer (RX)

- bit 2 PPBI: Ping-Pong BD Pointer Indicator bit

- 1 = The last transaction was to the ODD BD bank

- 0 = The last transaction was to the EVEN BD bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF bit (U1IR<3>) is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | —                 | —                 |                   | —                 | —                 | -                | —                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                 | —                 | —                 | -                 | —                 | _                 | -                | —                |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0         | _                 | —                 | —                 | -                 | —                 | _                 | -                | —                |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | BDTPTR            | H<23:16>          |                   |                  |                  |  |  |  |  |

# REGISTER 11-18: U1BDTP2: USB BDT PAGE 2 REGISTER

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRH<23:16>:** BDT Base Address bits This 8-bit value provides address bits 23 through 16 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

|              | COSTER 11-19. UIBUTF3. USB BUT FAGE 3 REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|--------------|------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                              | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 21.24        | U-0                                            | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                                              | —                 | _                 | —                 | -                 | _                 | —                | —                |  |  |  |  |

| 00.40        | U-0                                            | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | —                                              | —                 | _                 | —                 | -                 | _                 | —                | —                |  |  |  |  |

| 15.0         | U-0                                            | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | —                                              | —                 | _                 | —                 | -                 | _                 | —                | —                |  |  |  |  |

| 7:0          | R/W-0                                          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                                                |                   |                   | BDTPTR            | U<31:24>          |                   |                  |                  |  |  |  |  |

# REGISTER 11-19: U1BDTP3: USB BDT PAGE 3 REGISTER

| Legend:           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRU<31:24>: BDT Base Address bits

This 8-bit value provides address bits 31 through 24 of the BDT base address, defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

# 12.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only options.

Peripheral pin select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. Peripheral pin select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

## 12.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

# 12.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the peripheral pin select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the peripheral pin select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral. When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

## 12.3.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

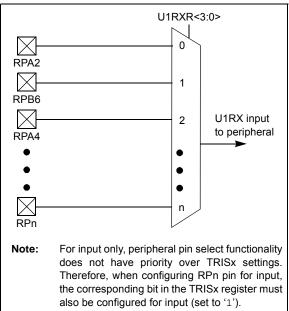

## 12.3.4 INPUT MAPPING

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 12-1, are used to configure peripheral input mapping (see Register 12-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 12-1.

For example, Figure 12-2 illustrates the remappable pin selection for the U1RX input.

# FIGURE 12-2:

REMAPPABLE INPUT EXAMPLE FOR U1RX

# TABLE 12-1: INPUT PIN SELECTION

| Peripheral Pin | [pin name]R SFR       | [pin name]R bits | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection                                      |

|----------------|-----------------------|------------------|-----------------------------------------------------------------------------------------|

| INT3           | INT3R                 | INT3R<3:0>       | 0000 = RPD2<br>0001 = RPG8                                                              |

| T2CK           | T2CKR                 | T2CKR<3:0>       | 0010 = RPF4<br>0011 = RPD10                                                             |

| IC3            | IC3R                  | IC3R<3:0>        | 0100 = RPF1<br>0101 = RPB9                                                              |

| U1RX           | U1RXR                 | U1RXR<3:0>       |                                                                                         |

| U2RX           | U2RXR                 | U2RXR<3:0>       | 1000 - RFB3<br>1001 = Reserved<br>1010 = RPC1 <sup>(3)</sup>                            |

| U5CTS          | U5CTSR <sup>(3)</sup> | U5CTSR<3:0>      | $\frac{1011}{1011} = \text{RPD14(3)}$<br>1100 = RPG1(3)                                 |

| REFCLKI        | REFCLKIR              | REFCLKIR<3:0>    | 1101 = RPA14 <sup>(3)</sup><br>1110 = Reserved<br>1111 = RPF2 <sup>(1)</sup>            |

| INT4           | INT4R                 | INT4R<3:0>       | 0000 = RPD3<br>0001 = RPG7                                                              |

| T5CK           | T5CKR                 | T5CKR<3:0>       | 0010 = RPF5<br>0011 = RPD11                                                             |

| IC4            | IC4R                  | IC4R<3:0>        | 0100 = RPF0<br>0101 = RPB1                                                              |

| U3RX           | U3RXR                 | U3RXR<3:0>       |                                                                                         |

| U4CTS          | U4CTSR                | U4CTSR<3:0>      | 1000 = Ri B3<br>1001 = Reserved<br>1010 = RPC4 <sup>(3)</sup>                           |

| SDI1           | SDI1R                 | SDI1R<3:0>       | 1011 = RPD15 <sup>(3)</sup><br>1100 = RPG0 <sup>(3)</sup>                               |

| SDI2           | SDI2R                 | SDI2R<3:0>       | 1101 = RPA15 <sup>(3)</sup><br>1110 = RPF2 <sup>(1)</sup><br>1111 = RPF7 <sup>(2)</sup> |

| INT2           | INT2R                 | INT2R<3:0>       | 0000 = RPD9<br>0001 = RPG6                                                              |

| T4CK           | T4CKR                 | T4CKR<3:0>       | 0010 = RPB8<br>0011 = RPB15                                                             |

| IC2            | IC2R                  | IC2R<3:0>        | 0100 = RPD4<br>0101 = RPB0                                                              |

| IC5            | IC5R                  | IC5R<3:0>        |                                                                                         |

| U1CTS          | U1CTSR                | U1CTSR<3:0>      | 1000 = Reserved<br>1001 = RPF12 <sup>(3)</sup><br>1010 = RPD12 <sup>(3)</sup>           |

| U2CTS          | U2CTSR                | U2CTSR<3:0>      | 1011 = RPF8 <sup>(3)</sup><br>1100 = RPC3 <sup>(3)</sup>                                |

| SS1            | SS1R                  | SS1R<3:0>        | 1101 = RPE9 <sup>(3)</sup><br>1110 = Reserved                                           |

|                |                       |                  | 1111 <b>= RPB2</b>                                                                      |

**Note 1:** This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

3: This selection is not available on 64-pin USB and General Purpose devices.

4: This selection is only available on General Purpose devices.

# 12.4 Control Registers

|                             | PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY |           |               |               |       |       |       |               |              |      |              |              |              |              |              |              |              |              |               |

|-----------------------------|-------------------------------------------------------------------------------------|-----------|---------------|---------------|-------|-------|-------|---------------|--------------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess)                        |                                                                                     | Ð         |               |               |       |       |       |               |              | Bi   | ts           |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup>                                                     | Bit Range | 31/15         | 30/14         | 29/13 | 28/12 | 27/11 | 26/10         | 25/9         | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6000                        | 6000 ANSELA                                                                         | 31:16     | —             | —             | -     | —     | —     | -             | —            | —    | —            | —            | —            | _            | —            | —            | -            | -            | 0000          |

| 0000                        |                                                                                     | 15:0      | —             | —             | —     | —     | —     | ANSELA10      | ANSELA9      | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0060          |

| 6010                        | TRISA                                                                               | 31:16     | _             | —             | _     | —     | _     | —             | —            | —    | —            | —            | —            |              | —            | —            | _            | _            | 0000          |

|                             |                                                                                     | 15:0      | TRISA15       | TRISA14       | _     | —     | _     | TRISA10       | TRISA9       | _    | TRISA7       | TRISA6       | TRISA5       | TRISA4       | TRISA3       | TRISA2       | TRISA1       | TRISA0       | xxxx          |

| 6020                        | PORTA                                                                               | 31:16     | —             | —             |       | —     |       | -             | —            | _    |              |              | —            | —            | —            |              | _            | _            | 0000          |

|                             |                                                                                     | 15:0      | RA15          | RA14          |       | —     | _     | RA10          | RA9          | _    | RA7          | RA6          | RA5          | RA4          | RA3          | RA2          | RA1          | RA0          | xxxx          |

| 6030                        | LATA                                                                                | 31:16     |               | _             |       | —     |       | —             | _            | _    |              |              |              |              |              |              | _            | _            | 0000          |

|                             |                                                                                     | 15:0      | LATA15        | LATA14        |       | —     |       | LATA10        | LATA9        | _    | LATA7        | LATA6        | LATA5        | LATA4        | LATA3        | LATA2        | LATA1        | LATA0        | xxxx          |

| 6040                        | ODCA                                                                                | 31:16     |               | _             |       | —     |       | —             | _            | _    |              |              |              |              |              |              | _            | _            | 0000          |

|                             |                                                                                     | 15:0      | ODCA15        | ODCA14        |       | —     |       | ODCA10        | ODCA9        | _    | ODCA7        | ODCA6        | ODCA5        | ODCA4        | ODCA3        | ODCA2        | ODCA1        | ODCA0        | xxxx          |

| 6050                        | CNPUA                                                                               | 31:16     | —             | —             |       | —     |       | -             | —            | _    |              |              | —            | —            | —            |              | _            | _            | 0000          |

|                             |                                                                                     |           | CNPUA15       | CNPUA14       |       | —     |       | CNPUA10       | CNPUA9       | _    | CNPUA7       | CNPUA6       | CNPUA5       | CNPUA4       | CNPUA3       | CNPUA2       | CNPUA1       | CNPUA0       | xxxx          |

| 6060                        | CNPDA                                                                               | 31:16     |               | _             |       | —     |       | —             | _            | _    |              |              |              |              |              |              | _            | _            | 0000          |

|                             | -                                                                                   |           | CNPDA15       | CNPDA14       | _     | —     | —     | CNPDA10       | CNPDA9       | —    | CNPDA7       | CNPDA6       | CNPDA5       | CNPDA4       | CNPDA3       | CNPDA2       | CNPDA1       | CNPDA0       | -             |

| 6070                        | CNCONA                                                                              | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                                                                     | 15:0      | ON            | _             | SIDL  | —     |       | _             | —            | _    |              |              | _            | _            |              |              |              |              | 0000          |

| 6080                        | CNENA                                                                               | 31:16     | —             | —             |       | —     | _     | -             | —            | _    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                                                                     | 15:0      | CNIEA15       | CNIEA14       |       | —     | _     | CNIEA10       | CNIEA9       | _    | CNIEA7       | CNIEA6       | CNIEA5       | CNIEA4       | CNIEA3       | CNIEA2       | CNIEA1       | CNIEA0       | xxxx          |

|                             | 01107171                                                                            | 31:16     | —             | —             |       | —     |       |               | —            | _    |              |              | —            | —            | —            |              | _            | _            | 0000          |

| 6090                        | CNSTATA                                                                             | 15:0      | CN<br>STATA15 | CN<br>STATA14 | _     | —     | _     | CN<br>STATA10 | CN<br>STATA9 | _    | CN<br>STATA7 | CN<br>STATA6 | CN<br>STATA5 | CN<br>STATA4 | CN<br>STATA3 | CN<br>STATA2 | CN<br>STATA1 | CN<br>STATA0 | xxxx          |

# TABLE 12-3:PORTA REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

PIC32MX330/350/370/430/450/470

NOTES:

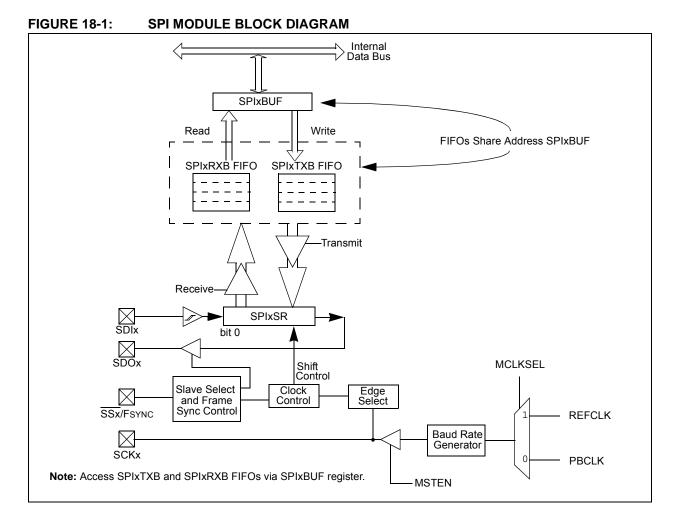

# 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. Some of the key features of the SPI module are:

- · Master and Slave modes support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- Operation during CPU Sleep and Idle mode

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5  | Bit<br>28/20/12/4   | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|--------------------|---------------------|---------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0                | U-0                 | U-0                 | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                  | —                   | _                   | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0                | U-0                 | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                  | —                   | —                   | _                 | —                | _                |

| 15:8         | R/W-0             | U-0               | R/W-0              | R/W-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | ON <sup>(1)</sup> | —                 | SIDL               | ADRMUX<1:0>         |                     | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0             | R/W-0              | R/W-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<1:0>(2)       |                   | ALP <sup>(2)</sup> | CS2P <sup>(2)</sup> | CS1P <sup>(2)</sup> |                   | WRSP             | RDSP             |

## REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER

#### Legend:

| R = Readable bit  | Readable bit W = Writable bit |                      | read as '0'        |

|-------------------|-------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set              | '0' = Bit is cleared | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

- 1 = PMP is enabled

- 0 = PMP is disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = Lower 8 bits of address are multiplexed on PMD<15:0> pins

- 10 = All 16 bits of address are multiplexed on PMD<7:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

- 00 = Address and data appear on separate pins

- bit 10 PMPTTL: PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port is enabled

- 0 = PMWR/PMENB port is disabled

- bit 8 PTRDEN: Read/Write Strobe Port Enable bit

- 1 = PMRD/PMWR port is enabled

- 0 = PMRD/PMWR port is disabled

- bit 7-6 **CSF<1:0>:** Chip Select Function bits<sup>(2)</sup>

- 11 = Reserved

- 10 = PMCS1 and PMCS2 function as Chip Select

- 01 = PMCS1 functions as address bit 14; PMCS2 functions as Chip Select