Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 49                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx430f064ht-v-pt |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 5: PIN NAMES FOR 100-PIN DEVICES

100-PIN TQFP (TOP VIEW)(1,2)

PIC32MX430F064L PIC32MX450F128L PIC32MX450F256L PIC32MX470F512L

100

1

| Pin# | Full Pin Name                         |

|------|---------------------------------------|

| 1    | RG15                                  |

| 2    | Vpp                                   |

|      | AN22/RPE5/PMD5/RE5                    |

| 3    |                                       |

| 4    | AN23/PMD6/RE6                         |

| 5    | AN27/PMD7/RE7                         |

| 6    | RPC1/RC1                              |

| 7    | RPC2/RC2                              |

| 8    | RPC3/RC3                              |

| 9    | RPC4/CTED7/RC4                        |

| 10   | AN16/C1IND/RPG6/SCK2/PMA5/RG6         |

| 11   | AN17/C1INC/RPG7/PMA4/RG7              |

| 12   | AN18/C2IND/RPG8/PMA3/RG8              |

| 13   | MCLR                                  |

| 14   | AN19/C2INC/RPG9/PMA2/RG9              |

| 15   | Vss                                   |

| 16   | VDD                                   |

| 17   | TMS/CTED1/RA0                         |

| 18   | RPE8/RE8                              |

| 19   | RPE9/RE9                              |

| 20   | AN5/C1INA/RPB5/VBuson/RB5             |

| 21   | AN4/C1INB/RB4                         |

| 22   | PGED3/AN3/C2INA/RPB3/RB3              |

| 23   | PGEC3/AN2/C2INB/RPB2/CTED13/RB2       |

| 24   | PGEC1/AN1/RPB1/CTED12/RB1             |

| 25   | PGED1/AN0/RPB0/RB0                    |

| 26   | PGEC2/AN6/RPB6/RB6                    |

| 27   | PGED2/AN7/RPB7/CTED3/RB7              |

| 28   | VREF-/CVREF-/PMA7/RA9                 |

| 29   | VREF+/CVREF+/PMA6/RA10                |

| 30   | AVDD                                  |

| 31   | AVss                                  |

| 32   | AN8/RPB8/CTED10/RB8                   |

| 33   | AN9/RPB9/CTED4/RB9                    |

| 34   | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 |

| 35   | AN11/PMA12/RB11                       |

| Pin # | Full Pin Name                   |

|-------|---------------------------------|

| 36    | Vss                             |

| 37    | VDD                             |

| 38    | TCK/CTED2/RA1                   |

| 39    | RPF13/RF13                      |

| 40    | RPF12/RF12                      |

| 41    | AN12/PMA11/RB12                 |

| 42    | AN13/PMA10/RB13                 |

| 43    | AN14/RPB14/CTED5/PMA1/RB14      |

| 44    | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 45    | Vss                             |

| 46    | VDD                             |

| 47    | RPD14/RD14                      |

| 48    | RPD15/RD15                      |

| 49    | RPF4/PMA9/RF4                   |

| 50    | RPF5/PMA8/RF5                   |

| 51    | USBID/RF3                       |

| 52    | RPF2/RF2                        |

| 53    | RPF8/RF8                        |

| 54    | VBUS                            |

| 55    | Vusb3v3                         |

| 56    | D-                              |

| 57    | D+                              |

| 58    | SCL2/RA2                        |

| 59    | SDA2/RA3                        |

| 60    | TDI/CTED9/RA4                   |

| 61    | TDO/RA5                         |

| 62    | VDD                             |

| 63    | OSC1/CLKI/RC12                  |

| 64    | OSC2/CLKO/RC15                  |

| 65    | Vss                             |

| 66    | SCL1/RPA14/RA14                 |

| 67    | SDA1/RPA15/RA15                 |

| 68    | RPD8/RTCC/RD8                   |

| 69    | RPD9/RD9                        |

| 70    | RPD10/SCK1/PMCS2/RD10           |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 12.0 "I/O Ports" for more information.

### TABLE 5: PIN NAMES FOR 100-PIN DEVICES (CONTINUED)

100-PIN TQFP (TOP VIEW)(1,2)

PIC32MX430F064L PIC32MX450F128L PIC32MX450F256L PIC32MX470F512L

100

1

| Pin# | Full Pin Name         |

|------|-----------------------|

| 71   | RPD11/PMCS1/RD11      |

| 72   | RPD0/INT0/RD0         |

| 73   | SOSCI/RPC13/RC13      |

| 74   | SOSCO/RPC14/T1CK/RC14 |

| 75   | Vss                   |

| 76   | AN24/RPD1/RD1         |

| 77   | AN25/RPD2/RD2         |

| 78   | AN26/RPD3/RD3         |

| 79   | RPD12/PMD12/RD12      |

| 80   | PMD13/RD13            |

| 81   | RPD4/PMWR/RD4         |

| 82   | RPD5/PMRD/RD5         |

| 83   | PMD14/RD6             |

| 84   | PMD15/RD7             |

| 85   | VCAP                  |

| Pin # | Full Pin Name       |

|-------|---------------------|

| 86    | VDD                 |

| 87    | RPF0/PMD11/RF0      |

| 88    | RPF1/PMD10/RF1      |

| 89    | RPG1/PMD9/RG1       |

| 90    | RPG0/PMD8/RG0       |

| 91    | TRCLK/RA6           |

| 92    | TRD3/CTED8/RA7      |

| 93    | PMD0/RE0            |

| 94    | PMD1/RE1            |

| 95    | TRD2/RG14           |

| 96    | TRD1/RG12           |

| 97    | TRD0/RG13           |

| 98    | AN20/CTPLS/PMD2/RE2 |

| 99    | RPE3/PMD3/RE3       |

| 100   | AN21/PMD4/RE4       |

### Note 1:

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 12.0 "I/O Ports" for more information

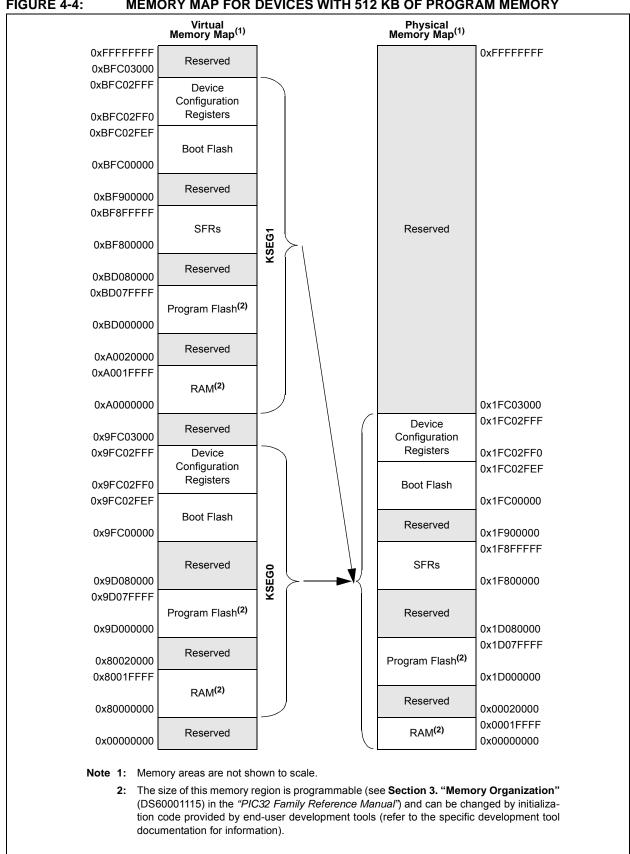

FIGURE 4-4: MEMORY MAP FOR DEVICES WITH 512 KB OF PROGRAM MEMORY

REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | -                 | -                 | _                 | -                 |                   | _                | _                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8         |                   | BMXDUPBA<15:8>    |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

|              |                   |                   |                   | BMXDU             | PBA<7:0>          |                   | _                |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 BMXDUPBA<9:0>: Read-Only bits

Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 31:24        | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0                | U-0                |

| 31.24        | _                 | _                 | HVDR              | _                 | _                 | _                 | _                  | _                  |

| 23:16        | U-0                | U-0                |

| 23.10        | _                 | _                 | _                 | _                 | -                 | -                 | _                  | _                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 13.6         | _                 | _                 | _                 | _                 | -                 | -                 | CMR                | VREGS              |

| 7:0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7.0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

Legend:HS = Set by hardwareR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29 HVDR: High Voltage Detect Reset Flag bit

1 = High Voltage Detect (HVD) Reset has occurred

0 = HVD Reset has not occurred

bit 28-10 Unimplemented: Read as '0'

bit 9 **CMR:** Configuration Mismatch Reset Flag bit

1 = Configuration mismatch Reset has occurred

0 = Configuration mismatch Reset has not occurred

bit 8 **VREGS:** Voltage Regulator Standby Enable bit

1 = Regulator is enabled and is on during Sleep mode

0 = Regulator is set to Stand-by Tracking mode

bit 7 **EXTR:** External Reset (MCLR) Pin Flag bit

1 = Master Clear (pin) Reset has occurred

0 = Master Clear (pin) Reset has not occurred

bit 6 **SWR:** Software Reset Flag bit

1 = Software Reset was executed

0 = Software Reset as not executed

bit 5 Unimplemented: Read as '0'

bit 4 WDTO: Watchdog Timer Time-out Flag bit

1 = WDT Time-out has occurred

0 = WDT Time-out has not occurred

bit 3 SLEEP: Wake From Sleep Flag bit

1 = Device was in Sleep mode

0 = Device was not in Sleep mode

bit 2 **IDLE:** Wake From Idle Flag bit

1 = Device was in Idle mode

0 = Device was not in Idle mode

bit 1 **BOR:** Brown-out Reset Flag bit<sup>(1)</sup>

1 = Brown-out Reset has occurred

0 = Brown-out Reset has not occurred

bit 0 **POR:** Power-on Reset Flag bit<sup>(1)</sup>

1 = Power-on Reset has occurred

0 = Power-on Reset has not occurred

Note 1: User software must clear this bit to view next detection.

#### REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                    |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                    |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                    |

|              | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | SWRST <sup>(1)</sup> |

**Legend:** HC = Cleared by hardware

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-1 Unimplemented: Read as '0'

bit 0 **SWRST:** Software Reset Trigger bit<sup>(1)</sup>

1 = Enable software Reset event

0 = No effect

**Note 1:** The system unlock sequence must be performed before the SWRST bit can be written. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

REGISTER 9-6: CHEW1: CACHE WORD 1

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 31.24        |                   | CHEW1<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22:46        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 23:16        | CHEW1<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 15:8         | CHEW1<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 7:0          |                   |                   |                   | CHEW1             | <7:0>             |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

#### REGISTER 9-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 31:24        |                   | CHEW2<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22:46        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 23:16        | CHEW2<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 15:8         | CHEW2<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

|              |                   |                   |                   | CHEW2             | <7:0>             |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

REGISTER 11-4: U10TGCON: USB OTG CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 **DPPULUP:** D+ Pull-Up Enable bit

1 = D+ data line pull-up resistor is enabled

0 = D+ data line pull-up resistor is disabled

bit 6 **DMPULUP:** D- Pull-Up Enable bit

1 = D- data line pull-up resistor is enabled

0 = D- data line pull-up resistor is disabled

bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

1 = D+ data line pull-down resistor is enabled

0 = D+ data line pull-down resistor is disabled

bit 4 DMPULDWN: D- Pull-Down Enable bit

1 = D- data line pull-down resistor is enabled

0 = D- data line pull-down resistor is disabled

bit 3 VBUSON: VBUS Power-on bit

1 = VBUS line is powered

0 = VBUS line is not powered

bit 2 OTGEN: OTG Functionality Enable bit

1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

bit 1 VBUSCHG: VBUS Charge Enable bit

1 = VBUS line is charged through a pull-up resistor

0 = VBUS line is not charged through a resistor

bit 0 VBUSDIS: VBUS Discharge Enable bit

1 = VBUS line is discharged through a pull-down resistor

0 = VBUS line is not discharged through a resistor

### REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

bit 1 PPBRST: Ping-Pong Buffers Reset bit

1 = Reset all Even/Odd buffer pointers to the EVEN BD banks

0 = Even/Odd buffer pointers not being Reset

bit 0 USBEN: USB Module Enable bit (4)

1 = USB module and supporting circuitry is enabled0 = USB module and supporting circuitry is disabled

**SOFEN:** SOF Enable bit<sup>(5)</sup>

1 = SOF token sent every 1 ms

0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set the RESUME bit for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

#### REGISTER 11-12: U1ADDR: USB ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                 | -                 | -                 | -                 | 1                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | -                 | _                 | _                 | -                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | LSPDEN            |                   |                   | D                 | EVADDR<6:0        | >                 |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 LSPDEN: Low Speed Enable Indicator bit

1 = Next token command to be executed at Low Speed0 = Next token command to be executed at Full Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

#### REGISTER 11-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | -                 | _                 | _                 | _                 | -                 | _                 | _                | _                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.6         | 1                 | -                 | _                 | _                 | -                 | _                 | -                | -                |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          | FRML<7:0>         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 FRML<7:0>: The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

### 13.2 Control Registers

### TABLE 13-1: TIMER1 REGISTER MAP

|                           | 0                               |           |       | ERT RESISTER MAI |       |       |       |       |      |      |        |      |       |        |      |       |      |      |           |

|---------------------------|---------------------------------|-----------|-------|------------------|-------|-------|-------|-------|------|------|--------|------|-------|--------|------|-------|------|------|-----------|

| ess                       |                                 | 0         |       |                  |       |       |       |       |      | Ві   | ts     |      |       |        |      |       |      |      | S.        |

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14            | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5  | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Reset |

| 0600                      | T1CON                           | 31:16     | _     | _                | _     | _     | _     | _     | _    | _    | _      | _    | _     | _      | _    | _     | _    | _    | 0000      |

| 0000                      | TICON                           | 15:0      | ON    | _                | SIDL  | TWDIS | TWIP  | _     | _    | _    | TGATE  | _    | TCKPS | S<1:0> | _    | TSYNC | TCS  | _    | 0000      |

| 0610                      | TMR1                            | 31:16     |       |                  | _     | _     | I     | _     | _    | _    | _      |      | _     | -      | _    | _     | -    | -    | 0000      |

| 0010                      | TIVITY                          | 15:0      |       |                  |       |       |       |       |      | TMR1 | <15:0> |      |       |        |      |       |      |      | 0000      |

| 0620                      | PR1                             | 31:16     | _     | 1                | -     | _     | I     | -     | -    | -    | _      | -    | _     | I      | _    | _     | I    | -    | 0000      |

| 0020                      | 1 181                           | 15:0      |       |                  |       |       |       |       |      | PR1< | 15:0>  |      |       |        |      |       |      |      | FFFF      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

PIC32MX330/350/370/430/450/470

#### **Control Registers** 17.1

### TABLE 17-1: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |               |            |       |           |       |       |        |      | Bi    | ts     |        |           |            |        |      |               |      | ,,         |

|-----------------------------|---------------------------------|---------------|------------|-------|-----------|-------|-------|--------|------|-------|--------|--------|-----------|------------|--------|------|---------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15      | 30/14 | 29/13     | 28/12 | 27/11 | 26/10  | 25/9 | 24/8  | 23/7   | 22/6   | 21/5      | 20/4       | 19/3   | 18/2 | 17/1          | 16/0 | All Resets |

|                             | OC1CON                          | 31:16<br>15:0 | —<br>ON    | _     | —<br>SIDL | _     | _     | _<br>_ |      | _     | _      | _<br>_ | —<br>OC32 | —<br>OCFLT | OCTSEL | _    | —<br>OCM<2:0> | _    | 0000       |

| 3010                        | OC1R                            | 31:16<br>15:0 | OC1R<31:0> |       |           |       |       |        |      |       |        |        |           | xxxx       |        |      |               |      |            |

| 3020                        | OC1RS                           | 31:16<br>15:0 |            |       |           |       |       |        |      | OC1RS | <31:0> |        |           |            |        |      |               |      | xxxx       |

| 3200                        | OC2CON                          | 31:16<br>15:0 | —<br>ON    | _     | —<br>SIDL | _     | _     |        | _    | _     | _      | _      | —<br>OC32 | OCFLT      | OCTSEL | _    | OCM<2:0>      | _    | 0000       |

| 3210                        | OC2R                            | 31:16<br>15:0 | 011        |       | O.B.L     |       |       |        |      | OC2R  |        |        | 0002      | 00.21      | OOTOLL |      |               |      | xxxx       |

| 3220                        | OC2RS                           | 31:16<br>15:0 |            |       |           |       |       |        |      | OC2RS | <31:0> |        |           |            |        |      |               |      | xxxx       |

| 3400                        | OC3CON                          | 31:16<br>15:0 | ON         |       | —<br>SIDL |       |       |        |      |       |        |        | —<br>OC32 | OCFLT      | OCTSEL | _    | OCM<2:0>      |      | 0000       |

| 3410                        | OC3R                            | 31:16<br>15:0 |            |       | •         |       |       |        |      | OC3R  | <31:0> |        |           | •          | 1      |      |               |      | xxxx       |

| 3420                        | OC3RS                           | 31:16<br>15:0 |            |       |           |       |       |        |      | OC3RS | <31:0> |        |           |            | _      |      |               |      | xxxx       |

| 3600                        | OC4CON                          | 31:16<br>15:0 | ON         | _     | —<br>SIDL | _     |       |        |      | _     |        | _      | —<br>ОС32 | OCFLT      | OCTSEL | _    | OCM<2:0>      | _    | 0000       |

| 3610                        | OC4R                            | 31:16<br>15:0 |            |       |           |       |       |        |      | OC4R  | <31:0> |        |           |            |        |      |               |      | xxxx       |

| 3620                        | OC4RS                           | 31:16<br>15:0 |            |       |           |       |       |        |      | OC4RS | <31:0> |        |           |            |        |      |               |      | xxxx       |

| 3800                        | OC5CON                          | 31:16<br>15:0 | ON         |       | —<br>SIDL |       |       |        |      |       |        |        | —<br>OC32 | OCFLT      | OCTSEL | _    | —<br>OCM<2:0> | _    | 0000       |

| 3810                        | OC5R                            | OC5R<31:0>    |            |       |           |       |       |        |      |       | xxxx   |        |           |            |        |      |               |      |            |

| 3820                        | OC5RS                           | 31:16<br>15:0 |            |       |           |       |       |        |      | OC5RS | <31:0> |        |           |            |        |      |               |      | xxxx       |

PIC32MX330/350/370/430/450/470

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information. Note 1:

### REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|--------------------------|----------------------|--------------------|-------------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0                      | U-0                  | U-0                | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | _                        | _                    | _                  |                         | 1                 | _                 | _                | _                |  |  |  |

| 23:16        | U-0                      | U-0                  | U-0                | U-0                     | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | _                        | _                    | _                  | _                       |                   | _                 | _                | _                |  |  |  |

| 15:8         | R/W-0                    | R/W-0                | R/W-0              | R-0                     | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15.6         | ALRMEN <sup>(1,2)</sup>  | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC <sup>(3)</sup> | (3) AMASK<3:0>(3) |                   |                  |                  |  |  |  |

| 7:0          | R/W-0                    | R/W-0                | R/W-0              | R/W-0                   | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 1.0          | ARPT<7:0> <sup>(3)</sup> |                      |                    |                         |                   |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ALRMEN: Alarm Enable bit (1,2)

1 = Alarm is enabled

0 = Alarm is disabled

bit 14 **CHIME**: Chime Enable bit<sup>(2)</sup>

1 = Chime is enabled - ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

0 = Chime is disabled – ARPT<7:0> stops once it reaches 0x00

bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(2)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse.

When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

bit 12 **ALRMSYNC:** Alarm Sync bit<sup>(3)</sup>

1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read. The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing, which are then synchronized to the PB clock domain

0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is > 32 RTC clocks away from a half-second rollover

bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits(3)

0000 = Every half-second

0001 = Every second

0010 = Every 10 seconds

0011 = Every minute

0100 = Every 10 minutes

0101 = Every hour

0110 = Once a day

0111 = Once a week

1000 = Once a month

1001 = Once a year (except when configured for February 29, once every four years)

1010 = Reserved; do not use

1011 = Reserved; do not use

11xx = Reserved; do not use

Note 1: Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIMF = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

**Note:** This register is reset only on a Power-on Reset (POR).

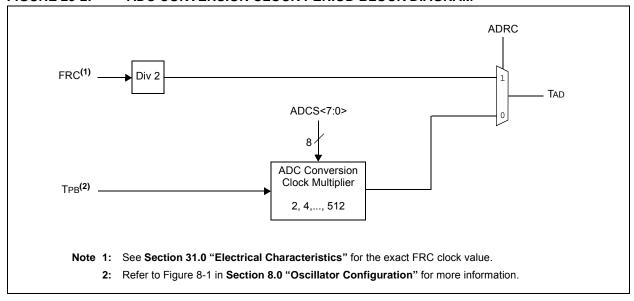

#### FIGURE 23-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

#### REGISTER 28-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/P               | R/P               | R/P               | R/P               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | _                 | _                 | _                | _                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | R/P               | R/P              | R/P              |  |  |  |

| 23.10        | _                 | _                 | _                 | _                 | _                 | FSRSSEL<2:0>      |                  |                  |  |  |  |

| 15:8         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |

| 15.6         |                   |                   |                   | USERID<           | 15:8>             |                   |                  |                  |  |  |  |

| 7:0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |

| 7.0          | USERID<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           | r = Reserved bit | P = Programmable bit                    |

|-------------------|------------------|-----------------------------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared x = Bit is unknown |

bit 31 FVBUSONIO: USB VBUS\_ON Selection bit

1 = VBUSON pin is controlled by the USB module

0 = VBUSON pin is controlled by the port function

bit 30 FUSBIDIO: USB USBID Selection bit

1 = USBID pin is controlled by the USB module

0 = USBID pin is controlled by the port function

bit 29 **IOL1WAY:** Peripheral Pin Select Configuration bit

1 = Allow only one reconfiguration0 = Allow multiple reconfigurations

bit 28 PMDL1WAY: Peripheral Module Disable Configuration bit

1 = Allow only one reconfiguration

0 = Allow multiple reconfigurations

bit 27-19 Unimplemented: Read as '0'

bit 18-16 FSRSSEL<2:0>: Shadow Register Set Priority Select bit

These bits assign an interrupt priority to a shadow register.

111 = Shadow register set used with interrupt priority 7

110 = Shadow register set used with interrupt priority 6

101 = Shadow register set used with interrupt priority 5

100 = Shadow register set used with interrupt priority 4

011 = Shadow register set used with interrupt priority 3

010 = Shadow register set used with interrupt priority 2

001 = Shadow register set used with interrupt priority 1

000 = Shadow register set used with interrupt priority 0

bit 15-0 **USERID<15:0>:** This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG

#### 30.2 MPLAB XC Compilers

The MPLAB XC Compilers are complete ANSI C compilers for all of Microchip's 8, 16, and 32-bit MCU and DSC devices. These compilers provide powerful integration capabilities, superior code optimization and ease of use. MPLAB XC Compilers run on Windows, Linux or MAC OS X.

For easy source level debugging, the compilers provide debug information that is optimized to the MPLAB X IDE.

The free MPLAB XC Compiler editions support all devices and commands, with no time or memory restrictions, and offer sufficient code optimization for most applications.

MPLAB XC Compilers include an assembler, linker and utilities. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. MPLAB XC Compiler uses the assembler to produce its object file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

#### 30.3 MPASM Assembler

The MPASM Assembler is a full-featured, universal macro assembler for PIC10/12/16/18 MCUs.

The MPASM Assembler generates relocatable object files for the MPLINK Object Linker, Intel® standard HEX files, MAP files to detail memory usage and symbol reference, absolute LST files that contain source lines and generated machine code, and COFF files for debugging.

The MPASM Assembler features include:

- · Integration into MPLAB X IDE projects

- User-defined macros to streamline assembly code

- Conditional assembly for multipurpose source files

- Directives that allow complete control over the assembly process

### 30.4 MPLINK Object Linker/ MPLIB Object Librarian

The MPLINK Object Linker combines relocatable objects created by the MPASM Assembler. It can link relocatable objects from precompiled libraries, using directives from a linker script.

The MPLIB Object Librarian manages the creation and modification of library files of precompiled code. When a routine from a library is called from a source file, only the modules that contain that routine will be linked in with the application. This allows large libraries to be used efficiently in many different applications.

The object linker/library features include:

- Efficient linking of single libraries instead of many smaller files

- Enhanced code maintainability by grouping related modules together

- Flexible creation of libraries with easy module listing, replacement, deletion and extraction

# 30.5 MPLAB Assembler, Linker and Librarian for Various Device Families

MPLAB Assembler produces relocatable machine code from symbolic assembly language for PIC24, PIC32 and dsPIC DSC devices. MPLAB XC Compiler uses the assembler to produce its object file. The assembler generates relocatable object files that can then be archived or linked with other relocatable object files and archives to create an executable file. Notable features of the assembler include:

- · Support for the entire device instruction set

- · Support for fixed-point and floating-point data

- · Command-line interface

- · Rich directive set

- · Flexible macro language

- · MPLAB X IDE compatibility

**TABLE 31-18: EXTERNAL CLOCK TIMING REQUIREMENTS**

|               |               |                                                                                                                  | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                        |                                         |            |                                                               |  |  |  |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|------------------------|-----------------------------------------|------------|---------------------------------------------------------------|--|--|--|

| AC CHA        | ARACTE        | RISTICS                                                                                                          | Operating te                                                          | mperature              | $-40^{\circ}\text{C} \le \text{TA} \le$ | ≤ +85°C    | r Commercial<br>for Industrial<br>C for V-temp                |  |  |  |

| Param.<br>No. | Symbol        | Characteristics                                                                                                  | Min.                                                                  | Typical <sup>(1)</sup> | Max.                                    | Units      | Conditions                                                    |  |  |  |

| OS10          | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4                                                               | _<br>_                 | 50<br>50                                | MHz<br>MHz | EC (Note 4)<br>ECPLL (Note 3)                                 |  |  |  |

| OS11          |               | Oscillator Crystal Frequency                                                                                     | 3                                                                     |                        | 10                                      | MHz        | XT (Note 4)                                                   |  |  |  |

| OS12          |               |                                                                                                                  | 4                                                                     | _                      | 10                                      | MHz        | XTPLL<br>(Notes 3,4)                                          |  |  |  |

| OS13          |               |                                                                                                                  | 10                                                                    | -                      | 25                                      | MHz        | HS (Note 4)                                                   |  |  |  |

| OS14          |               |                                                                                                                  | 10                                                                    | _                      | 25                                      | MHz        | HSPLL<br>(Notes 3,4)                                          |  |  |  |

| OS15          |               |                                                                                                                  | 32                                                                    | 32.768                 | 100                                     | kHz        | Sosc (Note 4)                                                 |  |  |  |

| OS20          | Tosc          | Tosc = 1/Fosc = Tcy (Note 2)                                                                                     | _                                                                     | _                      | _                                       | _          | See parameter<br>OS10 for Fosc<br>value                       |  |  |  |

| OS30          | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc                                                           | _                      | _                                       | ns         | EC (Note 4)                                                   |  |  |  |

| OS31          | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | _                                                                     | _                      | 0.05 x Tosc                             | ns         | EC (Note 4)                                                   |  |  |  |

| OS40          | Тоѕт          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                                     | 1024                   | _                                       | Tosc       | (Note 4)                                                      |  |  |  |

| OS41          | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | _                                                                     | 2                      | _                                       | ms         | (Note 4)                                                      |  |  |  |

| OS42          | Gм            | External Oscillator<br>Transconductance (Primary<br>Oscillator only)                                             | _                                                                     | 12                     | _                                       | mA/V       | V <sub>DD</sub> = 3.3V,<br>T <sub>A</sub> = +25°C<br>(Note 4) |  |  |  |

- **Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

- 2: Instruction cycle period (TCY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

- **3:** PLL input requirements: 4 MHz ≤ FPLLIN ≤ 5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

- **4:** This parameter is characterized, but not tested in manufacturing.

TABLE 31-25: TIMER2, 3, 4, 5 EXTERNAL CLOCK TIMING REQUIREMENTS

|                    |          | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) |                                                     |  |  |  |  |

|--------------------|----------|-----------------------------------------------------------------------|-----------------------------------------------------|--|--|--|--|

| AC CHARACTERISTICS | Operatir | ng temperature                                                        | $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial |  |  |  |  |

|                    | -        |                                                                       | -40°C ≤ TA ≤ +85°C for Industrial                   |  |  |  |  |

|                    |          |                                                                       | $-40$ °C $\leq$ TA $\leq$ +105°C for V-temp         |  |  |  |  |

|                    |          |                                                                       |                                                     |  |  |  |  |

| Param.<br>No. | Symbol    | Characteristics <sup>(1)</sup>                            |                             | Min.                                      | Max. | Units | Condit                        | ions                  |

|---------------|-----------|-----------------------------------------------------------|-----------------------------|-------------------------------------------|------|-------|-------------------------------|-----------------------|

| TB10          | ТтхН      | TxCK<br>High Time                                         | Synchronous, with prescaler | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns         | _    |       | Must also meet parameter TB15 | value<br>(1, 2, 4, 8, |

| TB11          | TTXL      | TxCK<br>Low Time                                          | Synchronous, with prescaler | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns         |      | _     | Must also meet parameter TB15 | 16, 32, 64,<br>256)   |

| TB15          | TTxP      | TxCK<br>Input                                             | Synchronous, with prescaler | [(Greater of [(25 ns or 2 TPB)/N] + 30 ns | _    | ns    | VDD > 2.7V                    |                       |

|               |           | Period                                                    |                             | [(Greater of [(25 ns or 2 TPB)/N] + 50 ns | _    | ns    | VDD < 2.7V                    |                       |

| TB20          | TCKEXTMRL | Delay from External TxCK<br>Clock Edge to Timer Increment |                             |                                           | 1    | Трв   | _                             |                       |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

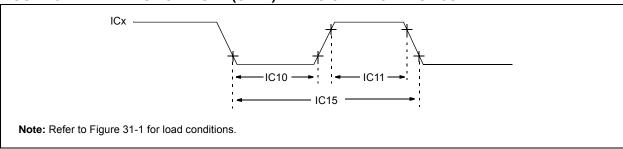

### FIGURE 31-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

#### **TABLE 31-26: INPUT CAPTURE MODULE TIMING REQUIREMENTS**

|        |         |       | Standard O (unless oth |                                   | onditions: 2.3V<br>ed)         | to 3.6V  |           |   |   |  |  |

|--------|---------|-------|------------------------|-----------------------------------|--------------------------------|----------|-----------|---|---|--|--|

| AC CHA | RACTERI | STICS | Operating te           | mperature                         | $0^{\circ}C \leq T_A \leq +70$ |          |           |   |   |  |  |

|        |         |       |                        | -40°C ≤ TA ≤ +85°C for Industrial |                                |          |           |   |   |  |  |

|        |         |       |                        |                                   | $-40^{\circ}C \le TA \le +1$   | 105°C fc | or V-temp | ) |   |  |  |

| Param. |         |       | (1)                    |                                   |                                |          |           |   | _ |  |  |

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup> | Min.                              | Max. | Units | Con                                     | ditions                          |

|---------------|--------|--------------------------------|-----------------------------------|------|-------|-----------------------------------------|----------------------------------|

| IC10          | TccL   | ICx Input Low Time             | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns | _    | ns    | Must also<br>meet<br>parameter<br>IC15. | N = prescale<br>value (1, 4, 16) |

| IC11          | TccH   | ICx Input High Time            | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns |      | ns    | Must also<br>meet<br>parameter<br>IC15. |                                  |

| IC15          | TccP   | ICx Input Period               | [(25 ns or 2 TPB)/N]<br>+ 50 ns   | _    | ns    | _                                       |                                  |

Note 1: These parameters are characterized, but not tested in manufacturing.

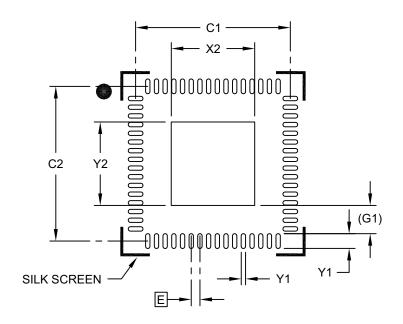

## 64-Lead Very Thin Plastic Quad Flat, No Lead Package (RG) - 9x9x1.0 mm Body [QFN] 4.7x4.7 mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### RECOMMENDED LAND PATTERN

|                                 | MILLIMETERS |          |           |      |  |

|---------------------------------|-------------|----------|-----------|------|--|

| Dimension                       | MIN         | NOM      | MAX       |      |  |

| Contact Pitch                   | E           | 0.50 BSC |           |      |  |

| Optional Center Pad Width       | X2          |          |           | 4.80 |  |

| Optional Center Pad Length      | Y2          |          |           | 4.80 |  |

| Contact Pad Spacing             | C1          |          | 8.90      |      |  |

| Contact Pad Spacing             | C2          |          | 8.90      |      |  |

| Contact Pad Width (X64)         | X1          |          |           | 0.25 |  |

| Contact Pad Length (X64)        | Y1          |          |           | 0.85 |  |

| Contact Pad to Center Pad (X64) | G1          |          | 1.625 REF | ·    |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-2260A

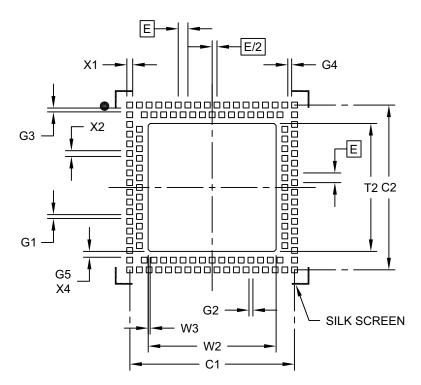

### 124-Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

RECOMMENDED LAND PATTERN

|                                      | Units |          | MILLIMETERS |      |  |

|--------------------------------------|-------|----------|-------------|------|--|

| Dimension Limits                     |       | MIN      | NOM         | MAX  |  |

| Contact Pitch                        | E     | 0.50 BSC |             |      |  |

| Pad Clearance                        | G1    | 0.20     |             |      |  |

| Pad Clearance                        | G2    | 0.20     |             |      |  |

| Pad Clearance                        | G3    | 0.20     |             |      |  |

| Pad Clearance                        | G4    | 0.20     |             |      |  |

| Contact to Center Pad Clearance (X4) | G5    | 0.30     |             |      |  |

| Optional Center Pad Width            | T2    |          |             | 6.60 |  |

| Optional Center Pad Length           | W2    |          |             | 6.60 |  |

| Optional Center Pad Chamfer (X4)     | W3    |          | 0.10        |      |  |

| Contact Pad Spacing                  | C1    |          | 8.50        |      |  |

| Contact Pad Spacing                  | C2    |          | 8.50        |      |  |

| Contact Pad Width (X124)             | X1    |          |             | 0.30 |  |

| Contact Pad Length (X124)            | X2    |          |             | 0.30 |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2193A