#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 64KB (64K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 16K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                |

| Supplier Device Package    | 124-VTLA (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx430f064lt-v-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at **docerrors@microchip.com**. We welcome your feedback.

#### **Most Current Data Sheet**

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

### **Referenced Sources**

This device data sheet is based on the following individual sections of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: | To access the following documents, refer |  |  |  |  |  |

|-------|------------------------------------------|--|--|--|--|--|

|       | to the Documentation > Reference         |  |  |  |  |  |

|       | Manuals section of the Microchip PIC32   |  |  |  |  |  |

|       | website: http://www.microchip.com/pic32. |  |  |  |  |  |

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

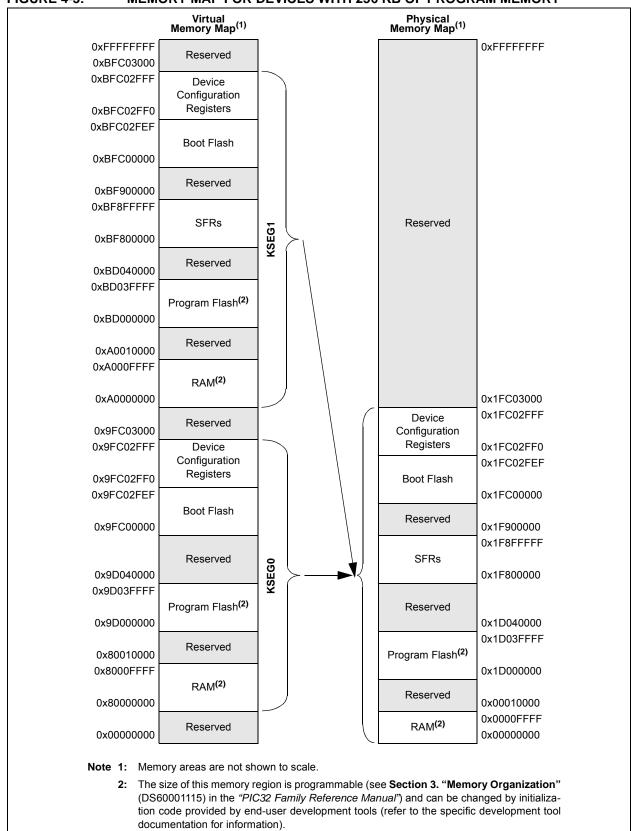

- Section 3. "Memory Organization" (DS60001115)

- Section 4. "Prefetch Cache" (DS60001119)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167)

### 2.11 Typical Application Connection Examples

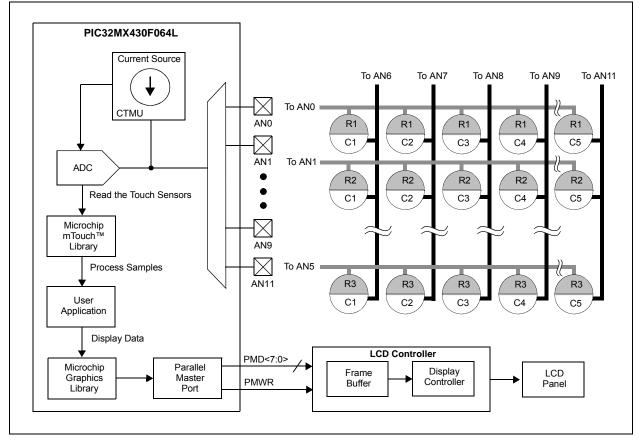

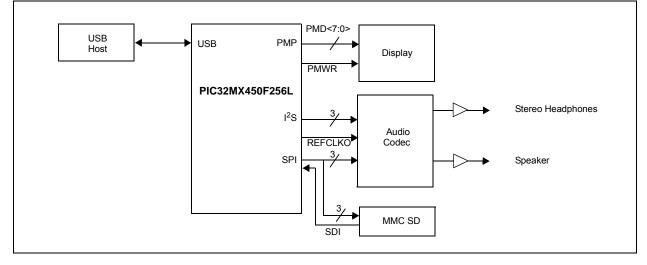

Examples of typical application connections are shown in Figure 2-6, Figure 2-7, and Figure 2-8.

### FIGURE 2-6: CAPACITIVE TOUCH SENSING WITH GRAPHICS APPLICATION

### FIGURE 2-7: AUDIO PLAYBACK APPLICATION

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e<sup>®</sup>, is also available by accessing the CP0 registers, listed in Table 3-2.

| Reserved<br>HWREna<br>BadVAddr <sup>(1)</sup><br>Count <sup>(1)</sup><br>Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup> | Reserved in the PIC32MX330/350/370/430/450/470 family core.         Enables access via the RDHWR instruction to selected hardware registers.         Reports the address for the most recent address-related exception.         Processor cycle count.         Reserved in the PIC32MX330/350/370/430/450/470 family core.         Timer interrupt control. |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BadVAddr <sup>(1)</sup><br>Count <sup>(1)</sup><br>Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                       | Reports the address for the most recent address-related exception.<br>Processor cycle count.<br>Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                 |

| Count <sup>(1)</sup><br>Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                                                  | Processor cycle count.<br>Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                       |

| Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                                                                          | Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                                                 |

| Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                                                                                      |                                                                                                                                                                                                                                                                                                                                                             |

| Status <sup>(1)</sup>                                                                                                                | Timer interrupt control.                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                             |

| (4)                                                                                                                                  | Processor status and control.                                                                                                                                                                                                                                                                                                                               |

| IntCtl <sup>(1)</sup>                                                                                                                | Interrupt system status and control.                                                                                                                                                                                                                                                                                                                        |

| SRSCtl <sup>(1)</sup>                                                                                                                | Shadow register set status and control.                                                                                                                                                                                                                                                                                                                     |

| SRSMap <sup>(1)</sup>                                                                                                                | Provides mapping from vectored interrupt to a shadow set.                                                                                                                                                                                                                                                                                                   |

| Cause <sup>(1)</sup>                                                                                                                 | Cause of last general exception.                                                                                                                                                                                                                                                                                                                            |

| EPC <sup>(1)</sup>                                                                                                                   | Program counter at last exception.                                                                                                                                                                                                                                                                                                                          |

| PRId                                                                                                                                 | Processor identification and revision.                                                                                                                                                                                                                                                                                                                      |

| EBASE                                                                                                                                | Exception vector base register.                                                                                                                                                                                                                                                                                                                             |

| Config                                                                                                                               | Configuration register.                                                                                                                                                                                                                                                                                                                                     |

| Config1                                                                                                                              | Configuration register 1.                                                                                                                                                                                                                                                                                                                                   |

| Config2                                                                                                                              | Configuration register 2.                                                                                                                                                                                                                                                                                                                                   |

| Config3                                                                                                                              | Configuration register 3.                                                                                                                                                                                                                                                                                                                                   |

| Reserved                                                                                                                             | Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                                                 |

| Debug <sup>(2)</sup>                                                                                                                 | Debug control and exception status.                                                                                                                                                                                                                                                                                                                         |

| DEPC <sup>(2)</sup>                                                                                                                  | Program counter at last debug exception.                                                                                                                                                                                                                                                                                                                    |

| Reserved                                                                                                                             | Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                                                 |

| ErrorEPC <sup>(1)</sup>                                                                                                              | Program counter at last error.                                                                                                                                                                                                                                                                                                                              |

| DESAVE <sup>(2)</sup>                                                                                                                | Debug handler scratchpad register.                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                      | RSMap <sup>(1)</sup><br>Cause <sup>(1)</sup><br>PC <sup>(1)</sup><br>PRId<br>BASE<br>Config<br>Config1<br>Config2<br>Config3<br>Reserved<br>Debug <sup>(2)</sup><br>DEPC <sup>(2)</sup><br>Reserved<br>ErrorEPC <sup>(1)</sup>                                                                                                                              |

TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used during debug.

| Interrupt Source <sup>(1)</sup>    | 100 // | Vector |               | Persistent   |              |              |           |

|------------------------------------|--------|--------|---------------|--------------|--------------|--------------|-----------|

| Interrupt Source."                 | IRQ #  | #      | Flag          | Enable       | Priority     | Sub-priority | Interrupt |

| CNB – PORTB Input Change Interrupt |        | 33     | IFS1<13>      | IEC1<13>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CNC – PORTC Input Change Interrupt | 46     | 33     | IFS1<14>      | IEC1<14>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CND – PORTD Input Change Interrupt | 47     | 33     | IFS1<15>      | IEC1<15>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CNE – PORTE Input Change Interrupt | 48     | 33     | IFS1<16>      | IEC1<16>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CNF – PORTF Input Change Interrupt | 49     | 33     | IFS1<17>      | IEC1<17>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| CNG – PORTG Input Change Interrupt | 50     | 33     | IFS1<18>      | IEC1<18>     | IPC8<12:10>  | IPC8<9:8>    | Yes       |

| PMP – Parallel Master Port         | 51     | 34     | IFS1<19>      | IEC1<19>     | IPC8<20:18>  | IPC8<17:16>  | Yes       |

| PMPE – Parallel Master Port Error  | 52     | 34     | IFS1<20>      | IEC1<20>     | IPC8<20:18>  | IPC8<17:16>  | Yes       |

| SPI2E – SPI2 Fault                 | 53     | 35     | IFS1<21>      | IEC1<21>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |

| SPI2RX – SPI2 Receive Done         | 54     | 35     | IFS1<22>      | IEC1<22>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |

| SPI2TX – SPI2 Transfer Done        | 55     | 35     | IFS1<23>      | IEC1<23>     | IPC8<28:26>  | IPC8<25:24>  | Yes       |

| U2E – UART2 Error                  | 56     | 36     | IFS1<24>      | IEC1<24>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |

| U2RX – UART2 Receiver              | 57     | 36     | IFS1<25>      | IEC1<25>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |

| U2TX – UART2 Transmitter           | 58     | 36     | IFS1<26>      | IEC1<26>     | IPC9<4:2>    | IPC9<1:0>    | Yes       |

| I2C2B – I2C2 Bus Collision Event   | 59     | 37     | IFS1<27>      | IEC1<27>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |

| I2C2S – I2C2 Slave Event           | 60     | 37     | IFS1<28>      | IEC1<28>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |

| I2C2M – I2C2 Master Event          | 61     | 37     | IFS1<29>      | IEC1<29>     | IPC9<12:10>  | IPC9<9:8>    | Yes       |

| U3E – UART3 Error                  | 62     | 38     | IFS1<30>      | IEC1<30>     | IPC9<20:18>  | IPC9<17:16>  | Yes       |

| U3RX – UART3 Receiver              | 63     | 38     | IFS1<31>      | IEC1<31>     | IPC9<20:18>  | IPC9<17:16>  | Yes       |

| U3TX – UART3 Transmitter           | 64     | 38     | IFS2<0>       | IEC2<0>      | IPC9<20:18>  | IPC9<17:16>  | Yes       |

| U4E – UART4 Error                  | 65     | 39     | IFS2<1>       | IEC2<1>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |

| U4RX – UART4 Receiver              | 66     | 39     | IFS2<2>       | IEC2<2>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |

| U4TX – UART4 Transmitter           | 67     | 39     | IFS2<3>       | IEC2<3>      | IPC9<28:26>  | IPC9<25:24>  | Yes       |

| U5E – UART5 Error                  | 68     | 40     | IFS2<4>       | IEC2<4>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |

| U5RX – UART5 Receiver              | 69     | 40     | IFS2<5>       | IEC2<5>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |

| U5TX – UART5 Transmitter           | 70     | 40     | IFS2<6>       | IEC2<6>      | IPC10<4:2>   | IPC10<1:0>   | Yes       |

| CTMU – CTMU Event                  | 71     | 41     | IFS2<7>       | IEC2<7>      | IPC10<12:10> | IPC10<9:8>   | Yes       |

| DMA0 – DMA Channel 0               | 72     | 42     | IFS2<8>       | IEC2<8>      | IPC10<20:18> | IPC10<17:16> | No        |

| DMA1 – DMA Channel 1               | 73     | 43     | IFS2<9>       | IEC2<9>      | IPC10<28:26> | IPC10<25:24> | No        |

| DMA2 – DMA Channel 2               | 74     | 44     | IFS2<10>      | IEC2<10>     | IPC11<4:2>   | IPC11<1:0>   | No        |

| DMA3 – DMA Channel 3               | 75     | 45     | IFS2<11>      | IEC2<11>     | IPC11<12:10> | IPC11<9:8>   | No        |

|                                    |        | Lowe   | st Natural Or | der Priority |              |              |           |

#### TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX330/350/370/430/450/470 Controller Family Features" for the list of available peripherals.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 31:24        |                   |                   |                   | CHEW3<            | :31:24>           |                   |                  |                  |  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 23:16        | CHEW3<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 15:8         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 10.0         | CHEW3<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |  |

| 7:0          |                   |                   | •                 | CHEW3<7:0>        |                   |                   |                  |                  |  |  |  |  |  |

### REGISTER 9-8: CHEW3: CACHE WORD 3

| Legend:           |                  |                          |                              |  |  |

|-------------------|------------------|--------------------------|------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | implemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown           |  |  |

# bit 31-0 **CHEW3<31:0>:** Word 3 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

Note: This register is a window into the cache data array and is readable only if the device is not code-protected.

### REGISTER 9-9: CHELRU: CACHE LRU REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R-0              |  |  |

| 31.24        | —                 | —                 | -                 | —                 | —                 | -                 | -                | CHELRU<24>       |  |  |

| 23:16        | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23.10        | CHELRU<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHELRU<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          | CHELRU<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-25 Unimplemented: Write '0'; ignore read

bit 24-0 **CHELRU<24:0>:** Cache Least Recently Used State Encoding bits Indicates the pseudo-LRU state of the cache.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 | _                 | _                | —                |

| 00.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CHSDIE            | CHSHIE            | CHDDIE            | CHDHIE            | CHBCIE            | CHCCIE            | CHTAIE           | CHERIE           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 | _                 | _                 | —                 | —                 | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CHSDIF            | CHSHIF            | CHDDIF            | CHDHIF            | CHBCIF            | CHCCIF            | CHTAIF           | CHERIF           |

|              |                   |                   |                   |                   |                   |                   |                  |                  |

### REGISTER 10-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER

### Legend:

| •                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 31-24  | Unimplemented: Read as '0'                                                                                                                |   |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------|---|

| bit 23     | CHSDIE: Channel Source Done Interrupt Enable bit                                                                                          |   |

|            | <ul><li>1 = Interrupt is enabled</li><li>0 = Interrupt is disabled</li></ul>                                                              |   |

| bit 22     | CHSHIE: Channel Source Half Empty Interrupt Enable bit                                                                                    |   |

|            | 1 = Interrupt is enabled                                                                                                                  |   |

| h:+ 04     | 0 = Interrupt is disabled                                                                                                                 |   |

| bit 21     | <b>CHDDIE:</b> Channel Destination Done Interrupt Enable bit<br>1 = Interrupt is enabled                                                  |   |

|            | 0 = Interrupt is disabled                                                                                                                 |   |

| bit 20     | CHDHIE: Channel Destination Half Full Interrupt Enable bit                                                                                |   |

|            | 1 = Interrupt is enabled                                                                                                                  |   |

|            | 0 = Interrupt is disabled                                                                                                                 |   |

| bit 19     | CHBCIE: Channel Block Transfer Complete Interrupt Enable bit                                                                              |   |

|            | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                           |   |

| bit 18     | CHCCIE: Channel Cell Transfer Complete Interrupt Enable bit                                                                               |   |

| DIL TO     | 1 = Interrupt is enabled                                                                                                                  |   |

|            | 0 = Interrupt is disabled                                                                                                                 |   |

| bit 17     | CHTAIE: Channel Transfer Abort Interrupt Enable bit                                                                                       |   |

|            | 1 = Interrupt is enabled                                                                                                                  |   |

|            | 0 = Interrupt is disabled                                                                                                                 |   |

| bit 16     | CHERIE: Channel Address Error Interrupt Enable bit                                                                                        |   |

|            | <ul> <li>1 = Interrupt is enabled</li> <li>0 = Interrupt is disabled</li> </ul>                                                           |   |

| bit 15-8   | Unimplemented: Read as '0'                                                                                                                |   |

| bit 7      | CHSDIF: Channel Source Done Interrupt Flag bit                                                                                            |   |

|            | 1 = Channel Source Pointer has reached end of source (CHSPTR = CHSSIZ)                                                                    |   |

|            | 0 = No interrupt is pending                                                                                                               |   |

| bit 6      | CHSHIF: Channel Source Half Empty Interrupt Flag bit                                                                                      |   |

|            | 1 = Channel Source Pointer has reached midpoint of source (CHSPTR = CHSSIZ/2)                                                             |   |

|            | 0 = No interrupt is pending                                                                                                               |   |

| bit 5      | <b>CHDDIF:</b> Channel Destination Done Interrupt Flag bit                                                                                |   |

|            | <ul> <li>1 = Channel Destination Pointer has reached end of destination (CHDPTR = CHDSIZ)</li> <li>0 = No interrupt is pending</li> </ul> |   |

|            |                                                                                                                                           |   |

|            |                                                                                                                                           | - |

| © 2012-201 | 16 Microchip Technology Inc. DS                                                                                                           | 6 |

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7                | Bit<br>30/22/14/6          | Bit<br>29/21/13/5    | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |

|--------------|----------------------------------|----------------------------|----------------------|-------------------|-------------------|-----------------------|------------------------|------------------|--|

| 31:24        | U-0                              | U-0                        | U-0                  | U-0               | U-0               | U-0                   | U-0                    | U-0              |  |

| 31.24        | -                                | -                          | -                    | -                 | —                 | -                     | —                      |                  |  |

| 23:16        | U-0                              | U-0                        | U-0                  | U-0               | U-0               | U-0                   | U-0                    | U-0              |  |

| 23.10        | -                                |                            | -                    |                   |                   |                       | —                      |                  |  |

| 15:8         | U-0                              | U-0                        | U-0                  | U-0               | U-0               | U-0                   | U-0                    | U-0              |  |

| 15.6         | -                                | -                          | -                    | -                 | —                 | -                     | —                      | -                |  |

|              | R/WC-0, HS                       | R/WC-0, HS                 | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS            | R/WC-0, HS             | R/WC-0, HS       |  |

| 7:0          | DISEE                            | BMXEF DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | DFN8EF CRC16EF    | CRC5EF <sup>(4)</sup> |                        |                  |  |

|              | BTSEF BMXEF DMAEF <sup>(1)</sup> |                            | DIVIAEL, ,           | BIVEF             | DENOER            | GRUIDEF               | EOFEF <sup>(3,5)</sup> | - PIDEF          |  |

#### REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend: WC = Write '1' to clear |                  | HS = Hardware Settable bit         |                    |  |

|---------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit                | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR               | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 BTSEF: Bit Stuff Error Flag bit

- 1 = Packet is rejected due to bit stuff error

- 0 = Packet is accepted

- bit 6 BMXEF: Bus Matrix Error Flag bit

1 = The base address, of the BDT, or the address of an individual buffer pointed to by a BDT entry, is invalid.

0 = No address error

- bit 5 **DMAEF:** DMA Error Flag bit<sup>(1)</sup> 1 = USB DMA error condition detected

- 0 = No DMA error

- bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

- 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

#### bit 3 **DFN8EF:** Data Field Size Error Flag bit

- 1 = Data field received is not an integral number of bytes

- 0 = Data field received is an integral number of bytes

#### bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet rejected due to CRC16 error

- 0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

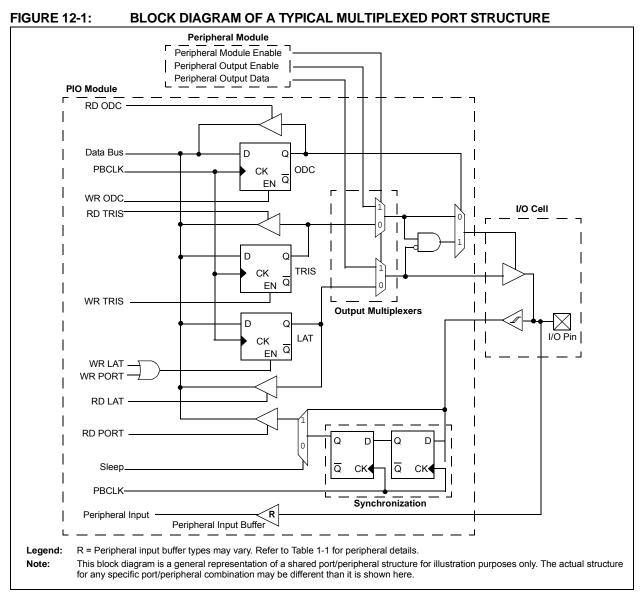

### 12.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate function(s). These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin. Following are key features of this module:

- · Individual output pin open-drain enable/disable

- · Individual input pin weak pull-up and pull-down

- Monitor selective inputs and generate interrupt when change in pin state is detected

- Operation during CPU Sleep and Idle modes

- Fast bit manipulation using CLR, SET, and INV registers

Figure 12-1 illustrates a block diagram of a typical multiplexed I/O port.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                   | —                 | _                 | _                 | _                 | —                 | _                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | —                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          |                     |                   | WDTWINEN          | WDTCLR            |                   |                   |                  |                  |

#### REGISTER 15-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                                    |                    |  |  |

|-------------------|-----------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 WDTCLR: Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 31:24        |                   | _                 | _                 | RXBUFELM<4:0>     |                   |                   |                  |                  |  |  |

| 23:16        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 23.10        |                   | _                 | _                 | TXBUFELM<4:0>     |                   |                   |                  |                  |  |  |

| 15.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |  |

| 15:8         |                   | —                 | -                 | FRMERR            | SPIBUSY           | _                 | _                | SPITUR           |  |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            |                   | SPITBF           | SPIRBF           |  |  |

### REGISTER 18-3: SPIxSTAT: SPI STATUS REGISTER

| Legend: C = Clearable bit |                  | HS = Set in hardware     |                    |  |

|---------------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit          | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR         | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error is detected

- 0 = No Frame error is detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 **SPIRBE:** RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR)

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

### 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/ pic32). The  $I^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard. Figure 19-1 illustrates the  $I^2C$  module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

#### REGISTER 20-1: UxMODE: UARTx MODE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 | _                 | _                | _                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | _                 | —                 | -                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |

### Legend:

| Legena.           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits

- UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal

#### bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- 1 =  $\overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

#### bit 10 Unimplemented: Read as '0'

#### bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up is enabled

- 0 = Wake-up is disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(3)</sup> 11111111 = Alarm will trigger 256 times

0000000 = Alarm will trigger one time

The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

## 31.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX330/350/370/430/450/470 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MX330/350/370/430/450/470 devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

### **Absolute Maximum Ratings**

#### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +105°C           |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             |                          |

| Voltage on VDD with respect to Vss                                              |                          |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 2.3V$ (Note 3) | -0.3V to +6.0V           |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | -0.3V to +3.6V           |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | -0.3V to +5.5V           |

| Maximum current out of Vss pin(s)                                               | 200 mA                   |

| Maximum current into VDD pin(s) (Note 2)                                        | 200 mA                   |

| Maximum output current sourced/sunk by any 4x I/O pin                           | 15 mA                    |

| Maximum output current sourced/sunk by any 8x I/O pin                           | 25 mA                    |

| Maximum current sunk by all ports                                               | 150 mA                   |

| Maximum current sourced by all ports (Note 2)                                   | 150 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

- 3: See the "Device Pin Tables" section for the 5V tolerant pins.

| DC CHA        | RACTE | RISTICS                                                                                                          | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                     |                     |        |                                                   |

|---------------|-------|------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------------------|--------|---------------------------------------------------|

| Param.<br>No. | Symb. | Characteristics                                                                                                  | Min.                                                                                                                                                                                                                                                                                                                                                | Тур. <sup>(1)</sup> | Max.                | Units  | Conditions                                        |

| DI10          | VIL   | Input Low Voltage<br>I/O Pins with PMP<br>I/O Pins                                                               | Vss<br>Vss                                                                                                                                                                                                                                                                                                                                          | _                   | 0.15 VDD<br>0.2 VDD | V<br>V |                                                   |

| DI18          |       | SDAx, SCLx                                                                                                       | Vss                                                                                                                                                                                                                                                                                                                                                 | —                   | 0.3 Vdd             | V      | SMBus disabled<br>(Note 4)                        |

| DI19          |       | SDAx, SCLx                                                                                                       | Vss                                                                                                                                                                                                                                                                                                                                                 |                     | 0.8                 | V      | SMBus enabled<br>(Note 4)                         |

| DI20          | Vih   | Input High Voltage<br>I/O Pins not 5V-tolerant <sup>(5)</sup><br>I/O Pins 5V-tolerant with<br>PMP <sup>(5)</sup> | 0.65 Vdd<br>0.25 Vdd + 0.8V                                                                                                                                                                                                                                                                                                                         | _                   | Vdd<br>5.5          | V<br>V | (Note 4,6)<br>(Note 4,6)                          |

| DI28          |       | I/O Pins 5V-tolerant <sup>(5)</sup><br>SDAx, SCLx                                                                | 0.65 VDD<br>0.65 VDD                                                                                                                                                                                                                                                                                                                                | _                   | 5.5<br>5.5          | V<br>V | SMBus disabled (Note 4,6)                         |

| DI29          |       | SDAx, SCLx                                                                                                       | 2.1                                                                                                                                                                                                                                                                                                                                                 | —                   | 5.5                 | V      | SMBus enabled,<br>2.3V ≤ VPIN ≤ 5.5<br>(Note 4,6) |

| DI30          | ICNPU | Change Notification<br>Pull-up Current                                                                           | —                                                                                                                                                                                                                                                                                                                                                   | —                   | -50                 | μA     | VDD = 3.3V, VPIN = VSS<br>(Note 3,6)              |

| DI31          | ICNPD | Change Notification<br>Pull-down Current <sup>(4)</sup>                                                          | —                                                                                                                                                                                                                                                                                                                                                   | 50                  | —                   | μA     | VDD = 3.3V, VPIN = VDD                            |

### TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

- 7: VIL source < (Vss 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- **10:** Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS 0.3)).

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

# PIC32MX330/350/370/430/450/470

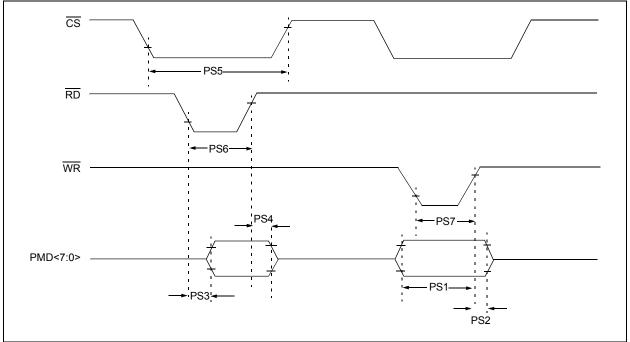

### FIGURE 31-20: PARALLEL SLAVE PORT TIMING

### TABLE 31-38: PARALLEL SLAVE PORT REQUIREMENTS

| AC CHARACTERISTICS |              |                                                                                  | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |            |    |    |   |

|--------------------|--------------|----------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------|----|----|---|

| Para<br>m.No.      | Symbol       | Characteristics <sup>(1)</sup>                                                   | Min.                                                                                                                                                                                                                                                                                                                                               | Conditions |    |    |   |

| PS1                | TdtV2wr<br>H | Data In Valid before $\overline{WR}$ or $\overline{CS}$<br>Inactive (setup time) | 20                                                                                                                                                                                                                                                                                                                                                 |            | _  | ns | _ |

| PS2                | TwrH2dt<br>I | WR or CS Inactive to Data-In Invalid (hold time)                                 | 40                                                                                                                                                                                                                                                                                                                                                 | —          | —  | ns | _ |

| PS3                | TrdL2dt<br>V | RD and CS Active to Data-Out Valid                                               | _                                                                                                                                                                                                                                                                                                                                                  |            | 60 | ns | _ |

| PS4                | TrdH2dtl     | RD Active or CS Inactive to Data-Out Invalid                                     | 0                                                                                                                                                                                                                                                                                                                                                  |            | 10 | ns | _ |

| PS5                | Tcs          | CS Active Time                                                                   | Трв + 40                                                                                                                                                                                                                                                                                                                                           |            | _  | ns | — |

| PS6                | Twr          | WR Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                                                                                           |            | _  | ns | _ |

| PS7                | Trd          | RD Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                                                                                           | _          | _  | ns | _ |

Note 1: These parameters are characterized, but not tested in manufacturing.

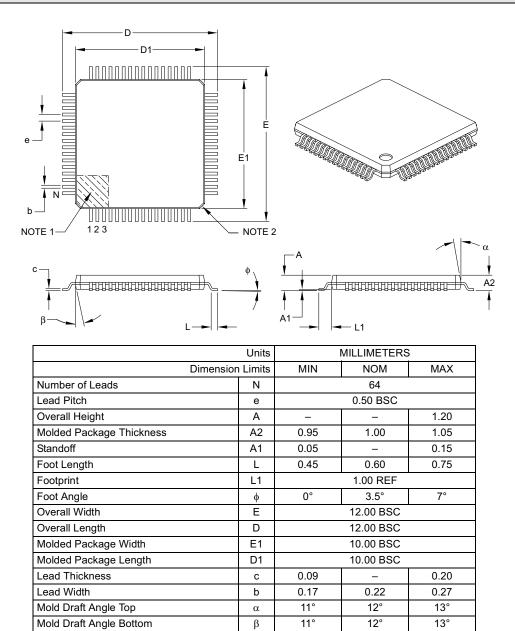

### 33.2 Package Details

The following sections give the technical details of the packages.

### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B