Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| 2 0 0 0 0 0                |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                |                                                                                |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f128h-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 |                  | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | —                 | _                 | _                 | —                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |

| 15:8         |                   |                   |                   | BMXDK             | PBA<15:8>         |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   | BMXDKPBA<7:0>     |                   |                   |                   |                   |                  |                  |  |  |

# REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

### Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 **BMXDKPBA<15:10>:** DRM Kernel Program Base Address bits When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 BMXDKPBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/ 470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Memory" (DS60001121), Program which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX330/350/370/430/450/470 devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: On PIC32MX330/350/370/430/450/470 devices, the Flash page size is 4 KB and the row size is 512 bytes (1024 IW and 128 IW, respectively).

# 6.1 Reset Control Registers

# TABLE 6-1: SYSTEM CONTROL REGISTER MAP

| ess                       |                                 | 6         |       |       |       |       |       |       |      |       | Bits |      |      |      |       |      |      |       | ts                  |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|---------------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Reset           |

| F600                      | RCON                            | 31:16     | _     | —     | HVDR  | _     | —     | —     | _    | _     | —    | _    | _    | —    | —     | _    | _    | —     | 0000                |

| FOUU                      | RCON                            | 15:0      | Ι     | —     |       | _     | _     | _     | CMR  | VREGS | EXTR | SWR  | —    | WDTO | SLEEP | IDLE | BOR  | POR   | xxxx <sup>(2)</sup> |

| E610                      | RSWRST                          | 31:16     | Ι     | —     |       | _     | _     | _     | —    | _     | —    |      | —    | —    | —     | _    | _    | —     | 0000                |

| FUIU                      | ROWROI                          | 15:0      | _     | _     | _     | -     | _     | _     | _    | -     | _    | _    | -    | _    | _     | -    | _    | SWRST | 0000                |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04-04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS9             | IFS8             |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | IFS7              | IFS6              | IFS5              | IFS4              | IFS3              | IFS2              | IFS1             | IFS0             |  |

# REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

# Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IFS31-IFS0: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

# REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC9             | IEC8             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC7              | IEC6              | IEC5              | IEC4              | IEC3              | IEC2              | IEC1             | IEC0             |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IEC31-IEC0: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

# REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN BD banks

- 0 = Even/Odd buffer pointers not being Reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set the RESUME bit for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

|              | -                 |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 |                   | —                 |                   |                   |                  |                  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | -                 | -                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | _                 | —                 | -                 | -                 | —                | —                |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0              | R/W-0            |

| 7:0          | UTEYE             | UOEMON            |                   | USBSIDL           | _                 |                   | _                | UASUSPND         |

## REGISTER 11-20: U1CNFG1: USB CONFIGURATION 1 REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

bit 7 UTEYE: USB Eye-Pattern Test Enable bit

- 1 = Eye-Pattern Test is enabled

- 0 = Eye-Pattern Test is disabled

#### bit 6 **UOEMON:** USB OE Monitor Enable bit

1 = OE signal is active; it indicates intervals during which the D+/D- lines are driving

0 = OE signal is inactive

#### bit 5 Unimplemented: Read as '0'

- bit 4 USBSIDL: Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

#### bit 3-1 Unimplemented: Read as '0'

#### bit 0 UASUSPND: Automatic Suspend Enable bit

- 1 = USB module automatically suspends upon entry to Sleep mode. See the USUSPEND bit (U1PWRC<1>) in Register 11-5.

- 0 = USB module does not automatically suspend upon entry to Sleep mode. Software must use the USUSPEND bit (U1PWRC<1>) to suspend the module, including the USB 48 MHz clock

# 12.1 Parallel I/O (PIO) Ports

All port pins have ten registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

# 12.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the presence of outputs higher than VDD (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Device Pin Tables"** section for the available pins and their functionality.

# 12.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

# 12.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be an NOP.

# 12.1.4 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports allows the PIC32MX330/350/370/430/450/470 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

Each I/O pin also has a weak pull-up and every I/O pin has a weak pull-down connected to it. The pullups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on change notifi-<br>cation pins should always be disabled<br>when the port pin is configured as a digital |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | output. They should also be disabled on                                                                                            |

|       | 5V tolerant pins when the pin voltage can                                                                                          |

|       | exceed VDD.                                                                                                                        |

An additional control register (CNCONx) is shown in Register 12-3.

# 12.2 CLR, SET, and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

# TABLE 12-2: OUTPUT PIN SELECTION (CONTINUED)

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection        |

|----------------------|----------|-------------|----------------------------------------------|

| RPD9                 | RPD9R    | RPD9R<3:0>  | 0000 = No Connect                            |

| RPG6                 | RPG6R    | RPG6R<3:0>  | 0001 = U3RTS                                 |

| RPB8                 | RPB8R    | RPB8R<3:0>  | 0010 = U4TX                                  |

| RPB15                | RPB15R   | RPB15R<3:0> | 0011 = REFCLKO<br>0100 = U5TX <sup>(4)</sup> |

| RPD4                 | RPD4R    | RPD4R<3:0>  | 0100 = 001 x 0                               |

| RPB0                 | RPB0R    | RPB0R<3:0>  | 0110 = Reserved                              |

| RPE3                 | RPE3R    | RPE3R<3:0>  | 0111 = <u>SS1</u>                            |

| RPB7                 | RPB7R    | RPB7R<3:0>  | 1000 <b>= SDO1</b>                           |

| RPB2                 | RPB2R    | RPB2R<3:0>  | 1001 = Reserved                              |

| RPF12 <sup>(4)</sup> | RPF12R   | RPF12R<3:0> | 1010 = Reserved                              |

| RPD12 <sup>(4)</sup> | RPD12R   | RPD12R<3:0> |                                              |

| RPF8 <sup>(4)</sup>  | RPF8R    | RPF8R<3:0>  | 1100 - Reserved                              |

| RPC3 <sup>(4)</sup>  | RPC3R    | RPC3R<3:0>  | 1110 = Reserved                              |

| RPE9 <sup>(4)</sup>  | RPE9R    | RPE9R<3:0>  | 1111 = Reserved                              |

| RPD1                 | RPD1R    | RPD1R<3:0>  | 0000 = No Connect                            |

| RPG9                 | RPG9R    | RPG9R<3:0>  | 0001 = U2RTS                                 |

| RPB14                | RPB14R   | RPB14R<3:0> | 0010 = Reserved<br>0011 = U1RTS              |

| RPD0                 | RPD0R    | RPD0R<3:0>  | $0100 = U5TX^{(4)}$                          |

| RPD8                 | RPD8R    | RPD8R<3:0>  | 0101 = Reserved                              |

| RPB6                 | RPB6R    | RPB6R<3:0>  | 0110 = <u>SS2</u>                            |

| RPD5                 | RPD5R    | RPD5R<3:0>  | 0111 = Reserved<br>1000 = SDO1               |

| RPF3 <sup>(3)</sup>  | RPF3R    | RPF3R<3:0>  | 1000 = SDOT                                  |

| RPF6 <sup>(1)</sup>  | RPF6R    | RPF6R<3:0>  | 1010 = Reserved                              |

| RPF13 <sup>(4)</sup> | RPF13R   | RPF13R<3:0> | 1011 = OC2                                   |

| RPC2 <sup>(4)</sup>  | RPC2R    | RPC2R<3:0>  | 1100 = OC1<br>1101 = Reserved                |

| RPE8 <sup>(4)</sup>  | RPE8R    | RPE8R<3:0>  | 1110 = Reserved                              |

| RPF2 <sup>(5)</sup>  | RPF2R    | RPF2R<3:0>  | 1111 = Reserved                              |

**Note 1:** This selection is only available on General Purpose devices.

**2:** This selection is only available on 64-pin General Purpose devices.

3: This selection is only available on 100-pin General Purpose devices.

4: This selection is only available on 100-pin USB and General Purpose devices.

5: This selection is not available on 64-pin USB devices.

# TABLE 12-17: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| sse                         |                       |           |       |       |       |       |       |       |      | В    | its  |      |      |      |            |             |                   |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------------|-------------|-------------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3       | 18/2        | 17/1              | 16/0 | All Resets |

| FA54                        | U1CTSR                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | —    |            |             |                   | _    | 0000       |

| FA04                        | UICISK                | 15:0      | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    |            | U1CTS       | SR<3:0>           |      | 0000       |

|                             |                       | 31:16     | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    | _          |             | —                 | _    | 0000       |

| FA58                        | U2RXR                 | 15:0      | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    |            | U2RX        | R<3:0>            |      | 0000       |

| FA5C                        | U2CTSR                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _          | _           | _                 | -    | 0000       |

| FASC                        | UZCISK                | 15:0      | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    |            | U2CTS       | SR<3:0>           |      | 0000       |

| FA60                        | <b>U3RXR</b>          | 31:16     | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    | _          |             | —                 | _    | 0000       |

| FAOU                        | USKAR                 | 15:0      | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    |            | U3RX        | R<3:0>            |      | 0000       |

| 5464                        | <b>U3CTSR</b>         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _          | _           | _                 | -    | 0000       |

| FA64                        | USCISK                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |            | U3CTS       | SR<3:0>           |      | 0000       |

| 5400                        | U4RXR                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _          | _           | _                 | -    | 0000       |

| FA68                        | U4RXR                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | U4RXR<3:0> |             |                   | 0000 |            |

| FA6C                        | U4CTSR                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _          | _           | _                 | -    | 0000       |

| FAGC                        | U4CISR                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |            | U4CTS       | SR<3:0>           |      | 0000       |

| FA70                        | U5RXR <sup>(1)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _          | _           | _                 | -    | 0000       |

| FA70                        | USRAR                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | —    | _    | _    | -    |            | U5RX        | R<3:0>            |      | 0000       |

| FA74                        | U5CTSR <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | —    | _    | —    | —    | —    | —    | _          | —           | —                 | -    | 0000       |

| FA74                        | 0501580               | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |            | U5CTS       | SR<3:0>           |      | 0000       |

| 5404                        | SDI1R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _          | _           | _                 | -    | 0000       |

| FA84                        | SDITR                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | —    | _    | _    | -    |            | SDI1F       | R<3:0>            |      | 0000       |

| <b>FA00</b>                 | 0040                  | 31:16     | _     | _     | _     | _     | _     | _     | —    | _    | —    | —    | —    | —    | _          | —           | —                 | -    | 0000       |

| FA88                        | SS1R                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | —    | _    | _    | _    |            | SS1F        | R<3:0>            |      | 0000       |

| FA00                        | SDI2R                 | 31:16     | _     | —     | _     |       | —     | —     |      | —    | -    |      | —    | _    | _          | —           | —                 | _    | 0000       |

| FA90                        | SDIZR                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |            | SDI2F       | R<3:0>            |      | 0000       |

| E404                        | SS2R                  | 31:16     | _     | —     | _     |       | —     | —     |      | —    | -    |      | —    | _    | _          | —           | —                 | _    | 0000       |

| FA94                        | 552R                  | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | —    |            | SS2R<3:0> 0 |                   |      |            |

| FADO                        |                       | 31:16     | _     | —     | _     | _     | —     | —     |      | —    | _    |      | —    | _    | _          | _           | —                 | _    | 0000       |

| FAD0                        | REFCLKIR              | 15:0      | _     | _     | _     | —     | _     | —     | _    | —    | _    | —    | _    | _    |            | REFCL       | <ir<3:0></ir<3:0> |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 |     |     | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-----|-----|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0 | U-0 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _   | _   | —                 | _                 |                   | _                | —                |  |  |

| 23:16        | U-0               | U-0 | U-0 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23.10        |                   | _   | -   | —                 | _                 | _                 | _                | —                |  |  |

| 15.0         | U-0               | U-0 | U-0 | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 15:8         | _                 | _   | _   | —                 | _                 |                   | _                | —                |  |  |

| 7.0          | U-0               | U-0 | U-0 | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | _                 | _   | _   | _                 | [pin name]R<3:0>  |                   |                  |                  |  |  |

# REGISTER 12-1: [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-4 Unimplemented: Read as '0'

# bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 12-1 for input pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

# REGISTER 12-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|----------------------------------|-----|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0                              | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                                | _   | _                 | —                 | _                 | _                 | -                | _                |

| 23:16        | U-0                              | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                                | _   | _                 | —                 | _                 | _                 | -                | _                |

| 45.0         | U-0                              | U-0 | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                                | _   | _                 | —                 | _                 | —                 |                  | _                |

| 7.0          | U-0                              | U-0 | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                                | —   | _                 | —                 |                   | RPnR              | <3:0>            |                  |

# Legend:

| 0                                 |                  |                                    |                    |  |  |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 12-2 for output pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

| Bit<br>Range | Bit<br>31/23/15/7 |     |       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----|-------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0 | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | _   | _     | _                 | _                 |                   | _                | _                |

| 00.40        | U-0               | U-0 | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _   | _     | -                 | _                 | _                 | _                | —                |

| 15.0         | R/W-0             | U-0 | R/W-0 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _   | SIDL  | _                 | _                 |                   | _                | —                |

| 7.0          | U-0               | U-0 | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 |     | _     | _                 | _                 | _                 | _                |                  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = CPU Idle Mode halts CN operation

- 0 = CPU Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

| Bit<br>Range   | Bit<br>31/23/15/7 |         |        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|----------------|-------------------|---------|--------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04          | U-0               | U-0     | U-0    | U-0               | U-0               | U-0               | U-0              | R/W-0            |  |  |  |

| 31:24 —        |                   | —       | _      | _                 | _                 | _                 | _                | ADM_EN           |  |  |  |

| R/W-0 R/W-0    |                   | R/W-0   | R/W-0  | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16          | ADDR<7:0>         |         |        |                   |                   |                   |                  |                  |  |  |  |

| 45.0           | R/W-0             | R/W-0   | R/W-0  | R/W-0             | R/W-0             | R/W-0             | R-0              | R-1              |  |  |  |

| 15:8           | 15:8 UTXISEL<1:0> |         | UTXINV | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |  |  |  |

| 7:0 R/W-0 R/W- |                   | R/W-0   | R/W-0  | R-1               | R-0               | R-0               | R/W-0            | R-0              |  |  |  |

| 7:0            | URXISE            | :L<1:0> | ADDEN  | RIDLE             | PERR              | FERR              | OERR             | URXDA            |  |  |  |

# REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

# Legend:

| Logonal           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-25 Unimplemented: Read as '0'

- bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

- 1 = Automatic Address Detect mode is enabled

- 0 = Automatic Address Detect mode is disabled

- bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

#### bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

- 11 = Reserved, do not use

- 10 = Interrupt is generated and asserted while the transmit buffer is empty

- 01 = Interrupt is generated and asserted when all characters have been transmitted

- 00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

## bit 13 UTXINV: Transmit Polarity Inversion bit

If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

## If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

- 1 = IrDA encoded UxTX Idle state is '1'

- 0 = IrDA encoded UxTX Idle state is '0'

## bit 12 URXEN: Receiver Enable bit

- 1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by the port.

#### bit 11 UTXBRK: Transmit Break bit

- 1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Break transmission is disabled or completed

- bit 10 UTXEN: Transmit Enable bit

- 1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by the port.

#### bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

NOTES:

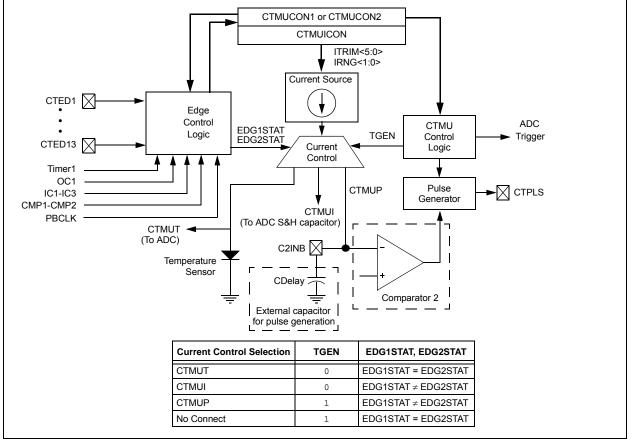

# 26.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

FIGURE 26-1: CTMU BLOCK DIAGRAM

The CTMU module includes the following key features:

- Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- · Control of current source during auto-sampling

- Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 26-1.

# 26.1 Control Register

# TABLE 26-1: CTMU REGISTER MAP

| ess                       |                                 | 0         |                                                                         | Bits                                                                             |  |       |         |  |          |          |         |         |           |       |          |  |   |   |      |

|---------------------------|---------------------------------|-----------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------|--|-------|---------|--|----------|----------|---------|---------|-----------|-------|----------|--|---|---|------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                                                                   | 31/15 30/14 29/13 28/12 27/11 26/10 25/9 24/8 23/7 22/6 21/5 20/4 19/3 18/2 17/1 |  |       |         |  |          |          |         | 16/0    | All Reset |       |          |  |   |   |      |

| 1 200                     | CTMUCON                         | 31:16     | EDG1MOD                                                                 | EDG1POL                                                                          |  | EDG1S | EL<3:0> |  | EDG2STAT | EDG1STAT | EDG2MOD | EDG2POL |           | EDG2S | SEL<3:0> |  | — | _ | 0000 |

| A200                      | CTWOCON                         | 15:0      | ON – CTMUSIDL TGEN EDGEN EDGSEQEN IDISSEN CTTRIG ITRIM<5:0> IRNG<1:0> 0 |                                                                                  |  |       |         |  | 0000     |          |         |         |           |       |          |  |   |   |      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# 27.0 POWER-SAVING FEATURES

| Note: | This data sheet summarizes the features<br>of the PIC32MX330/350/370/430/450/470<br>family of devices. It is not intended to be a<br>comprehensive reference source. To<br>complement the information in this data<br>sheet, refer to <b>Section 10.</b> " <b>Power-</b><br><b>Saving Features</b> " (DS60001130), which<br>is available from the <i>Documentation</i> ><br><i>Reference Manual</i> section of the<br>Microphin PIC22 work arite |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | (www.microchip.com/pic32).                                                                                                                                                                                                                                                                                                                                                                                                                       |

This section describes power-saving features for the PIC32MX330/350/370/430/450/470 family of devices. These PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

# 27.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers.

- LPRC Run mode: the CPU is clocked from the LPRC clock source.

- Sosc Run mode: the CPU is clocked from the Sosc clock source.

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

# 27.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as listed below:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock

running.

• Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

# 27.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

# 27.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is Halted.

- The system clock source is typically shutdown. See Section 27.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection.

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode.

- The BOR circuit remains operative during Sleep mode.

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode.

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep.

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption.

# 27.4.1 CONTROLLING CONFIGURATION CHANGES

Because peripherals can be disabled during run time, some restrictions on disabling peripherals are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to enabled or disabled peripherals:

- Control register lock sequence

- · Configuration bit select lock

# 27.4.1.1 Control Register Lock

Under normal operation, writes to the PMDx registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the PMDLOCK Configuration bit (CFGCON<12>). Setting PMDLOCK prevents writes to the control registers; clearing PMDLOCK allows writes.

To set or clear PMDLOCK, an unlock sequence must be executed. Refer to **Section 6.** "Oscillator" (DS60001112) in the "*PIC32 Family Reference Manual*" for details.

# 27.4.1.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the PMDx registers. The PMDL1WAY Configuration bit (DEVCFG3<28>) blocks the PMDLOCK bit from being cleared after it has been set once. If PMDLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable PMD functionality is to perform a device Reset.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | R/P               | R/P               | R/P               | R/P               | U-0               | U-0               | U-0              | U-0              |

|              | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | _                 |                   | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | R/P               | R/P              | R/P              |

|              | —                 | —                 | —                 | —                 | —                 | FSRSSEL<2:0>      |                  |                  |

| 15:8         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |

|              | USERID<15:8>      |                   |                   |                   |                   |                   |                  |                  |

| 7:0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |

|              | USERID<7:0>       |                   |                   |                   |                   |                   |                  |                  |

# REGISTER 28-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bit   |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31 **FVBUSONIO:** USB VBUS\_ON Selection bit 1 = VBUSON pin is controlled by the USB module

- 0 = VBUSON pin is controlled by the OSB module0 = VBUSON pin is controlled by the port function

- bit 30 **FUSBIDIO:** USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

- bit 29 IOL1WAY: Peripheral Pin Select Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 28 PMDL1WAY: Peripheral Module Disable Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 27-19 Unimplemented: Read as '0'

## bit 18-16 FSRSSEL<2:0>: Shadow Register Set Priority Select bit

These bits assign an interrupt priority to a shadow register.

- 111 = Shadow register set used with interrupt priority 7

- 110 = Shadow register set used with interrupt priority 6

- 101 = Shadow register set used with interrupt priority 5

- 100 = Shadow register set used with interrupt priority 4

- O11 = Shadow register set used with interrupt priority 3

- 010 = Shadow register set used with interrupt priority 2

- 001 = Shadow register set used with interrupt priority 1

- 000 = Shadow register set used with interrupt priority 0

- bit 15-0 USERID<15:0>: This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG

|                    |                     |                                          |                                                                           |                 | -DOWN CURRENT (IPD)<br>nditions: 2.3V to 3.6V (unless otherwise stated) |  |  |

|--------------------|---------------------|------------------------------------------|---------------------------------------------------------------------------|-----------------|-------------------------------------------------------------------------|--|--|

| DC CHARACTERISTICS |                     |                                          | Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial |                 |                                                                         |  |  |

|                    |                     |                                          | $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial                     |                 |                                                                         |  |  |

|                    |                     | -40°C $\leq$ TA $\leq$ +105°C for V-temp |                                                                           |                 |                                                                         |  |  |

| Param. No.         | Typ. <sup>(2)</sup> | Max.                                     | Units                                                                     | s Conditions    |                                                                         |  |  |

| PIC32MX330         | ) Device            | s Only                                   |                                                                           |                 |                                                                         |  |  |

| Power-Down         | n Curren            | it (IPD) (N                              | lote 1)                                                                   |                 |                                                                         |  |  |

| DC40k              | 20                  | 55                                       | μΑ                                                                        | -40°C           |                                                                         |  |  |

| DC40I              | 38                  | 55                                       | μΑ                                                                        | +25°C           | Base Power-Down Current                                                 |  |  |

| DC40n              | 128                 | 167                                      | μΑ                                                                        | +85°C           | Base Power-Down Current                                                 |  |  |

| DC40m              | 261                 | 419                                      | μA                                                                        | +105°C          |                                                                         |  |  |

| PIC32MX430         | ) Device            | s Only                                   |                                                                           |                 |                                                                         |  |  |

| Power-Down         | n Curren            | it (IPD) (N                              | lote 1)                                                                   |                 |                                                                         |  |  |

| DC40k              | 12                  | 28                                       | μΑ                                                                        | -40°C           |                                                                         |  |  |

| DC40I              | 21                  | 28                                       | μΑ                                                                        | +25°C           | Base Power-Down Current                                                 |  |  |

| DC40n              | 128                 | 167                                      | μΑ                                                                        | +85°C           |                                                                         |  |  |

| DC40m              | 261                 | 419                                      | μA                                                                        | +105°C          |                                                                         |  |  |

| PIC32MX350         | )F128 De            | evices O                                 | nly                                                                       |                 |                                                                         |  |  |

| Power-Down         | n Curren            | t (IPD) (N                               | lote 1)                                                                   |                 |                                                                         |  |  |

| DC40k              | 31                  | 70                                       | μΑ                                                                        | -40°C           |                                                                         |  |  |

| DC40I              | 45                  | 70                                       | μΑ                                                                        | +25°C           | Base Power-Down Current                                                 |  |  |

| DC40n              | 175                 | 280                                      | μΑ                                                                        | +85°C           |                                                                         |  |  |

| DC40m              | 415                 | 600                                      | μA                                                                        | +105°C          |                                                                         |  |  |

| PIC32MX450         | )F128 De            | evices O                                 | nly                                                                       |                 |                                                                         |  |  |

| Power-Down         | n Curren            | t (IPD) (N                               | lote 1)                                                                   |                 |                                                                         |  |  |

| DC40k              | 19                  | 35                                       | μA                                                                        | -40°C           |                                                                         |  |  |

| DC40I              | 28                  | 35                                       | μA                                                                        | +25°C           | Base Power-Down Current                                                 |  |  |

| DC40n              | 175                 | 280                                      | μΑ                                                                        | +85°C           |                                                                         |  |  |

| DC40m              | 415                 | 600                                      | μA                                                                        | +105°C          |                                                                         |  |  |

| Note 1: Th         | ne test co          | onditions                                | for IPD m                                                                 | easurements are | as follows:                                                             |  |  |

#### TABLE 31-7. DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD)

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, program Flash memory Wait states = 7, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

- · WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- Voltage regulator is off during Sleep mode (VREGS bit in the RCON register = 0)

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: 120 MHz commercial devices only (0°C to +70°C).

# **Revision C (October 2013)**

This revision includes the following updates, as listed in Table A-2.

# TABLE A-2: MAJOR SECTION UPDATES

| Section                                                               | Update Description                                                                                                                                                                |  |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| "32-bit Microcontrollers (up to 512<br>KB Flash and 128 KB SRAM) with | The Operating Conditions and Core sections were updated in support of 100 MHz (-40°C to +85°C) devices.                                                                           |  |

| Audio/Graphics/Touch (HMI), USB,<br>and Advanced Analog"              | Added Notes 2 and 3 regarding the conductive thermal pad to the 124-pin VTLA pin diagrams.                                                                                        |  |

| 2.0 "Guidelines for Getting Started                                   | Updated the recommended minimum connection (see Figure 2-1).                                                                                                                      |  |

| with 32-bit MCUs"                                                     | Added 2.10 "Sosc Design Recommendation".                                                                                                                                          |  |

| 20.0 "Parallel Master Port (PMP)"                                     | Updated the Parallel Port Control register, PMCON (see Register 20-1).                                                                                                            |  |

|                                                                       | Updated the Parallel Port Mode register, PMMODE (see Register 20-2).                                                                                                              |  |

|                                                                       | Updated the Parallel Port Pin Enable register, PMAEN (see Register 20-4).                                                                                                         |  |

| 30.0 "Electrical Characteristics"                                     | Removed Note 4 from the Absolute Maximum Ratings.                                                                                                                                 |  |

|                                                                       | The maximum frequency for parameter DC5 In Operating MIPS vs. Voltage was changed to 100 MHz (see Table 30-1).                                                                    |  |

|                                                                       | Parameter DC25a was added to DC Characteristics: Operating Current (IDD) (see Table 30-5).                                                                                        |  |

|                                                                       | Parameter DC34c was added to DC Characteristics: Idle Current (IIDLE) (see Table 30-5).                                                                                           |  |

|                                                                       | Added parameters for PIC32MX370/470 devices and removed Note 5 from DC Characteristics: Power-Down Current (IPD) (see Table 30-7).                                                |  |

|                                                                       | Updated the Minimum, Typical, and Maximum values and added a reference to Note 3 for parameter DI30 (ICNPU) in DC Characteristics: I/O Pin Input Specifications (see Table 30-8). |  |

|                                                                       | The SYSCLK values for all required Flash Wait states were updated (see Table 30-13).                                                                                              |  |

|                                                                       | Added parameter DO50A (Csosc) to the Capacitive Loading Requirements on Output Pins (see Table 30-16).                                                                            |  |

|                                                                       | Updated the maximum values for parameter OS10, and the Characteristics definition of parameter OS42 (GM) in the External Clock Timing Characteristics (see Table 30-17).          |  |

| 31.0 "DC and AC Device<br>Characteristics Graphs"                     | Updated the IPD, IIDLE, and IDD graphs, and added new graphs for the PIC32MX370/470 devices (see Figure 31-5 through Figure 31-13).                                               |  |