Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| etails                  |                                                                                 |

|-------------------------|---------------------------------------------------------------------------------|

| oduct Status            | Active                                                                          |

| ore Processor           | MIPS32® M4K™                                                                    |

| ore Size                | 32-Bit Single-Core                                                              |

|                         | 80MHz                                                                           |

| peed                    |                                                                                 |

| onnectivity             | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| eripherals              | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| umber of I/O            | 49                                                                              |

| ogram Memory Size       | 128KB (128K x 8)                                                                |

| ogram Memory Type       | FLASH                                                                           |

| PROM Size               | -                                                                               |

| M Size                  | 32K x 8                                                                         |

| tage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| ta Converters           | A/D 28x10b                                                                      |

| cillator Type           | Internal                                                                        |

| erating Temperature     | -40°C ~ 85°C (TA)                                                               |

| ounting Type            | Surface Mount                                                                   |

| ckage / Case            | 64-TQFP                                                                         |

| pplier Device Package   | 64-TQFP (10x10)                                                                 |

| rchase URL              | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f128ht-i-pt |

#### TABLE 7: PIN NAMES FOR 124-PIN DEVICES (CONTINUED)

**124-PIN VTLA (BOTTOM VIEW)**(1,2,3,4)

A17

B13 B29 Conductive Thermal Pad

PIC32MX430F064L PIC32MX450F128L PIC32MX450F256L PIC32MX470F512L

B1 B41 B56

<sup>66</sup> A51

Α1

Polarity Indicator

A68

| Package<br>Bump # | Full Pin Name                   |

|-------------------|---------------------------------|

| B7                | MCLR                            |

| B8                | Vss                             |

| B9                | TMS/CTED1/RA0                   |

| B10               | RPE9/RE9                        |

| B11               | AN4/C1INB/RB4                   |

| B12               | Vss                             |

| B13               | PGEC3/AN2/C2INB/RPB2/CTED13/RB2 |

| B14               | PGED1/AN0/RPB0/RB0              |

| B15               | No Connect                      |

| B16               | PGED2/AN7/RPB7/CTED3/RB7        |

| B17               | VREF+/CVREF+/PMA6/RA10          |

| B18               | AVss                            |

| B19               | AN9/RPB9/CTED4/RB9              |

| B20               | AN11/PMA12/RB11                 |

| B21               | VDD                             |

| B22               | RPF13/RF13                      |

| B23               | AN12/PMA11/RB12                 |

| B24               | AN14/RPB14/CTED5/PMA1/RB14      |

| B25               | Vss                             |

| B26               | RPD14/RD14                      |

| B27               | RPF4/PMA9/RF4                   |

| B28               | No Connect                      |

| B29               | RPF8/RF8                        |

| B30               | VUSB3V3                         |

| B31               | D+                              |

| Package<br>Bump # | Full Pin Name                                                                                           |

|-------------------|---------------------------------------------------------------------------------------------------------|

| B32               | SDA2/RA3                                                                                                |

| B33               | TDO/RA5                                                                                                 |

| B34               | OSC1/CLKI/RC12                                                                                          |

| B35               | No Connect                                                                                              |

| B36               | SCL1/RPA14/RA14                                                                                         |

| B37               | RPD8/RTCC/RD8                                                                                           |

| B38               | RPD10/SCK1/PMCS2/RD10                                                                                   |

| B39               | RPD0/INT0/RD0                                                                                           |

| B40               | SOSCO/RPC14/T1CK/RC14                                                                                   |

| B41               | Vss                                                                                                     |

| B42               | AN25/RPD2/RD2                                                                                           |

| B43               | RPD12/PMD12/RD12                                                                                        |

| B44               | RPD4/PMWR/RD4                                                                                           |

| B45               | PMD14/RD6                                                                                               |

| B46               | No Connect                                                                                              |

| B47               | No Connect                                                                                              |

| B48               | VCAP                                                                                                    |

| B49               | RPF0/PMD11/RF0                                                                                          |

| B50               | RPG1/PMD9/RG1                                                                                           |

| B51               | TRCLK/RA6                                                                                               |

| B52               | PMD0/RE0                                                                                                |

| B53               | VDD                                                                                                     |

| B54               | TRD2/RG14                                                                                               |

| B55               | TRD0/RG13                                                                                               |

| B56               | RPE3/CTPLS/PMD3/RE3                                                                                     |

|                   | Bump #  B32 B33 B34 B35 B36 B37 B38 B39 B40 B41 B42 B43 B44 B45 B46 B47 B48 B49 B50 B51 B52 B53 B54 B55 |

- Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

- Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

- 3: Shaded package bumps are 5V tolerant.

- 4: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

#### 1.0 DEVICE OVERVIEW

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This document contains device-specific information for PIC32MX330/350/370/430/450/470 devices.

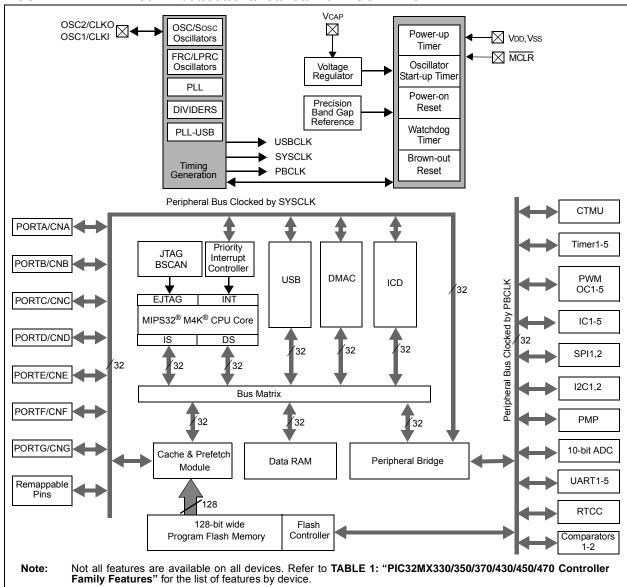

Figure 1-1 illustrates a general block diagram of the core and peripheral modules in the PIC32MX330/350/370/430/450/470 family of devices.

Table 1-1 lists the functions of the various pins shown in the pinout diagrams.

FIGURE 1-1: PIC32MX330/350/370/430/450/470 BLOCK DIAGRAM

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                        | Pin Numb                 | er                                                  |             |                |                                                                              |

|----------|------------------------|--------------------------|-----------------------------------------------------|-------------|----------------|------------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP          | 124-pin<br>VTLA                                     | Pin<br>Type | Buffer<br>Type | Description                                                                  |

| CTED4    | 22                     | 33                       | B19                                                 | I           | ST             | CTMU External Edge Input 4                                                   |

| CTED5    | 29                     | 43                       | B24                                                 | I           | ST             | CTMU External Edge Input 5                                                   |

| CTED6    | 30                     | 44                       | A29                                                 | I           | ST             | CTMU External Edge Input 6                                                   |

| CTED7    | _                      | 9                        | B5                                                  | I           | ST             | CTMU External Edge Input 7                                                   |

| CTED8    | _                      | 92                       | A62                                                 | I           | ST             | CTMU External Edge Input 8                                                   |

| CTED9    | _                      | 60                       | A40                                                 | I           | ST             | CTMU External Edge Input 9                                                   |

| CTED10   | 21                     | 32                       | A23                                                 | I           | ST             | CTMU External Edge Input 10                                                  |

| CTED11   | 23                     | 34                       | A24                                                 | I           | ST             | CTMU External Edge Input 11                                                  |

| CTED12   | 15                     | 24                       | A15                                                 | I           | ST             | CTMU External Edge Input 12                                                  |

| CTED13   | 14                     | 23                       | B13                                                 | I           | ST             | CTMU External Edge Input 13                                                  |

| MCLR     | 7                      | 13                       | В7                                                  | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device.   |

| AVDD     | 19                     | 30                       | A22                                                 | Р           | Р              | Positive supply for analog modules. This pin must be connected at all times. |

| AVss     | 20                     | 31                       | B18                                                 | Р           | Р              | Ground reference for analog modules                                          |

| VDD      | 10, 26, 38,<br>57      | 2, 16, 37,<br>46, 62, 86 | B1, A10, A14,<br>B21, A30,<br>A41, A48,<br>A59, B53 | Р           | _              | Positive supply for peripheral logic and I/O pins                            |

| VCAP     | 56                     | 85                       | B48                                                 | Р           |                | Capacitor for Internal Voltage Regulator                                     |

| Vss      | 9, 25, 41              | 15, 36, 45,<br>65, 75    | A3, B8, B12,<br>A25, B25,<br>A43, B41,<br>A63       | Р           | _              | Ground reference for logic and I/O pins                                      |

| VREF+    | 16                     | 29                       | B17                                                 | I           | Analog         | Analog Voltage Reference (High) Input                                        |

| VREF-    | 15                     | 28                       | A21                                                 | ı           | Analog         | Analog Voltage Reference (Low) Input                                         |

**Legend:** CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

TTL = TTL input buffer

Analog = Analog input

O = Output

P = Power I = Input

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices.

#### REGISTER 4-5: BMXDRMSZ: DATA RAM SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24:24        | R                     | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 31.24        | 31:24 BMXDRMSZ<31:24> |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22.40        | R                     | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 23:16        | BMXDRMSZ<23:16>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R                     | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 15:8         |                       | BMXDRMSZ<15:8>    |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R                     | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 7:0          |                       |                   |                   | BMXDR             | MSZ<7:0>          |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

#### bit 31-0 BMXDRMSZ<31:0>: Data RAM Memory (DRM) Size bits

Static value that indicates the size of the Data RAM in bytes:

0x00004000 = Device has 16 KB RAM 0x00008000 = Device has 32 KB RAM 0x00010000 = Device has 64 KB RAM

0x00020000 = Device has 128 KB RAM

# REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | _                 | _                 | -                 | _                 | _                 | _                 | _                | _                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | _                 | _                 | _                 | _                 | BMXPUPBA<19:16>   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         |                   |                   |                   | BMXPU             | PBA<15:8>         |                   |                  |                  |  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0 R-0 R-0 R-0   |                   |                  |                  |  |  |  |  |

| 7:0          |                   | BMXPUPBA<7:0>     |                   |                   |                   |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

bit 10-0 BMXPUPBA<10:0>: Read-Only bits

Value is always '0', which forces 2 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXPFMSZ.

#### 9.0 PREFETCH CACHE

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 4.** "**Prefetch Cache**" (DS60001119), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

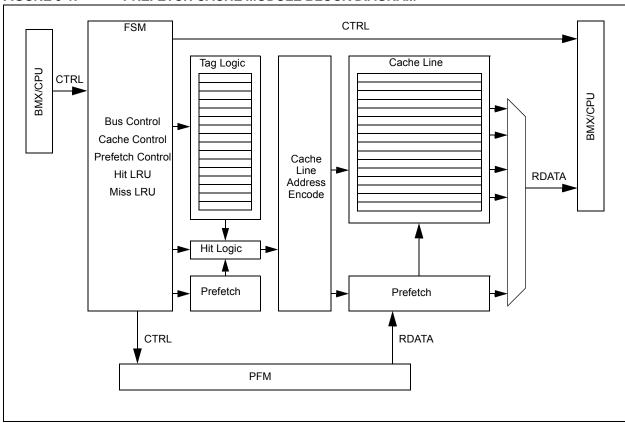

Prefetch cache increases performance for applications executing out of the cacheable program Flash memory regions by implementing instruction caching, constant data caching and instruction prefetching.

#### 9.1 Features

- · 16 fully associative lockable cache lines

- 16-byte cache lines

- · Up to four cache lines allocated to data

- Two cache lines with address mask to hold repeated instructions

- · Pseudo LRU replacement policy

- · All cache lines are software writable

- · 16-byte parallel memory fetch

- · Predictive instruction prefetch

A simplified block diagram of the Prefetch Cache module is illustrated in Figure 9-1.

FIGURE 9-1: PREFETCH CACHE MODULE BLOCK DIAGRAM

REGISTER 9-8: CHEW3: CACHE WORD 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31.24        | CHEW3<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22:46        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEW3<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEW3<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   |                   |                   | CHEW3             | <7:0>             |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 **CHEW3<31:0>:** Word 3 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

**Note:** This register is a window into the cache data array and is readable only if the device is not code-protected.

#### **REGISTER 9-9: CHELRU: CACHE LRU REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7           | .       - |     | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-----------------------------|-----------|-----|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0                         | U-0       | U-0 | U-0               | U-0               | U-0               | U-0              | R-0              |  |  |  |  |

| 31.24        | -                           | _         | _   | _                 | -                 | _                 | -                | CHELRU<24>       |  |  |  |  |

| 23:16        | R-0                         | R-0       | R-0 | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 23.10        | CHELRU<23:16>               |           |     |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R-0                         | R-0       | R-0 | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |

| 15:8         |                             |           |     | CHELR             | U<15:8>           |                   |                  |                  |  |  |  |  |

| 7:0          | R-0 R-0 R-0 R-0 R-0 R-0 R-0 |           |     |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          |                             |           |     | CHELF             | RU<7:0>           |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-25 Unimplemented: Write '0'; ignore read

bit 24-0 CHELRU<24:0>: Cache Least Recently Used State Encoding bits

Indicates the pseudo-LRU state of the cache.

REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 31.24        | -                 | -                 | -                    | -                    | -                 | -                 | _                      | _                |

| 23:16        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 23.10        | -                 | -                 | -                    | -                    | -                 | _                 | _                      | _                |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |

| 15.6         | _                 | _                 | _                    | _                    | _                 | _                 | _                      | _                |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |

|              | DIOLI             | DIVIALI           | DIVIALI              | DIOLIT               | DINOLI            | ONOTOLI           | EOFEF <sup>(3,5)</sup> | IDLI             |

Legend:WC = Write '1' to clearHS = Hardware Settable bitR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 **BTSEF:** Bit Stuff Error Flag bit

1 = Packet is rejected due to bit stuff error

0 = Packet is accepted

bit 6 **BMXEF:** Bus Matrix Error Flag bit

1 = The base address, of the BDT, or the address of an individual buffer pointed to by a BDT entry, is invalid.

0 = No address error

bit 5 **DMAEF:** DMA Error Flag bit<sup>(1)</sup>

1 = USB DMA error condition detected

0 = No DMA error

bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

1 = Bus turnaround time-out has occurred

0 = No bus turnaround time-out

bit 3 DFN8EF: Data Field Size Error Flag bit

1 = Data field received is not an integral number of bytes

0 = Data field received is an integral number of bytes

bit 2 CRC16EF: CRC16 Failure Flag bit

1 = Data packet rejected due to CRC16 error

0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- 2: This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

| IABL | E 12-18: | PER | RIPHERAL PIN SELECT | OUTPUT | REGISTER MAP |

|------|----------|-----|---------------------|--------|--------------|

|      |          |     |                     |        |              |

| SS                          |                       |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |        |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FB38                        | RPA14R <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |       |        |      | 0000       |

| 1 030                       | KFA 14K**             | 15:0      |       | _     | _     | _     |       | _     | _    |      | _    |      | _    | _    |      | RPA14 | l<3:0> |      | 0000       |

| FB3C                        | RPA15R <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1 550                       | KFA ISK.              | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA15 | 5<3:0> |      | 0000       |

| FB40                        | RPB0R                 | 31:16     |       | _     | _     | _     |       | _     | _    |      | _    |      | _    | _    | _    | _     | _      | _    | 0000       |

| 1 540                       | KEBOK                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB0  | <3:0>  |      | 0000       |

| FB44                        | RPB1R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | -     |        | -    | 0000       |

| 1 044                       | KEDIK                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB1  | <3:0>  |      | 0000       |

| FB48                        | RPB2R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | -     |        | -    | 0000       |

| FB40                        | KFB2K                 | 15:0      | 1     | _     |       | _     | -     | _     | _    | -    | _    | -    | _    |      |      | RPB2  | <3:0>  |      | 0000       |

| FB4C                        | RPB3R                 | 31:16     | -     | _     | _     | _     | _     | _     | _    | -    | _    | _    | _    | _    | _    | ı     |        | -    | 0000       |

| FB4C                        | KFB3K                 | 15:0      |       | _     | _     | _     | _     | _     | _    |      | _    | _    | _    |      |      | RPB3  | <3:0>  |      | 0000       |

| FB54                        | RPB5R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB34                        | RPBOR                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB5  | <3:0>  |      | 0000       |

| ED E O                      | RPB6R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB58                        | RPBOR                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB6  | <3:0>  |      | 0000       |

| FB5C                        | RPB7R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FBSC                        | RPB/R                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB7  | <3:0>  |      | 0000       |

| ED.CO                       | DDDOD                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB60                        | RPB8R                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB8  | <3:0>  |      | 0000       |

| EDC4                        | DDDOD                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB64                        | RPB9R                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB9  | <3:0>  |      | 0000       |

| ED.CO                       | DDD40D                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB68                        | RPB10R                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB10 | )<3:0> |      | 0000       |

|                             | 555445                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB78                        | RPB14R                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB14 | 1<3:0> |      | 0000       |

| ED70                        | DDD45D                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB7C                        | RPB15R                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB15 | 5<3:0> |      | 0000       |

|                             | DD0 (D(1)             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB84                        | RPC1R <sup>(1)</sup>  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC1  | <3:0>  |      | 0000       |

|                             | (4)                   | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB88                        | RPC2R <sup>(1)</sup>  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC2  | <3:0>  |      | 0000       |

|                             | (4)                   | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB8C                        | RPC3R <sup>(1)</sup>  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC3  | <3:0>  |      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

<sup>2:</sup> This register is only available on devices without a USB module.

<sup>3:</sup> This register is not available on 64-pin devices with a USB module.

### REGISTER 12-3: CNCONx: CHANGE NOTICE CONTROL FOR PORTX REGISTER (x = A - G)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 | _                 | _                | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 ON: Change Notice (CN) Control ON bit

1 = CN is enabled0 = CN is disabled

bit 14 **Unimplemented:** Read as '0'

bit 13 SIDL: Stop in Idle Control bit

1 = CPU Idle Mode halts CN operation0 = CPU Idle does not affect CN operation

bit 12-0 Unimplemented: Read as '0'

#### 14.0 TIMER2/3, TIMER4/5

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14.** "**Timers**" (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

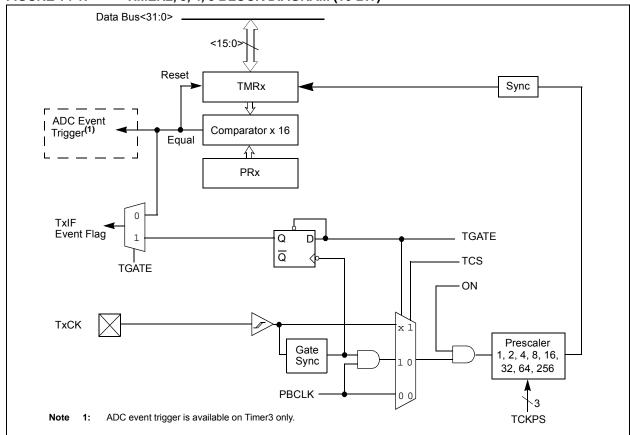

The PIC32MX330/350/370/430/450/470 family of devices features four synchronous 16-bit timers (default) that can operate as a free-running interval timer for various timing applications and counting external events. The following modes are supported:

- · Synchronous internal 16-bit timer

- · Synchronous internal 16-bit gated timer

- · Synchronous external 16-bit timer

Two 32-bit synchronous timers are available by combining Timer2 with Timer3 and Timer4 with Timer5. The 32-bit timers can operate in three modes:

- Synchronous internal 32-bit timer

- · Synchronous internal 32-bit gated timer

- Synchronous external 32-bit timer

Note:

In this chapter, references to registers, TxCON, TMRx and PRx, use 'x' to represent Timer2 through 5 in 16-bit modes. In 32-bit modes, 'x' represents Timer2 or 4; 'y' represents Timer3 or 5.

#### 14.1 Additional Supported Features

- · Selectable clock prescaler

- · Timers operational during CPU idle

- Time base for Input Capture and Output Compare modules (Timer2 and Timer3 only)

- ADC event trigger (Timer3 in 16-bit mode, Timer2/ 3 in 32-bit mode)

- Fast bit manipulation using CLR, SET, and INV registers

FIGURE 14-1: TIMER2, 3, 4, 5 BLOCK DIAGRAM (16-BIT)

#### REGISTER 14-1: TxCON: TYPE B TIMER CONTROL REGISTER (CONTINUED)

bit 3 T32: 32-Bit Timer Mode Select bit<sup>(2)</sup>

1 = Odd numbered and even numbered timers form a 32-bit timer

0 = Odd numbered and even numbered timers form a separate 16-bit timer

bit 2 **Unimplemented:** Read as '0'

bit 1 **TCS**: Timer Clock Source Select bit<sup>(3)</sup>

1 = External clock from TxCK pin

0 = Internal peripheral clock

bit 0 **Unimplemented:** Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit is available only on even numbered timers (Timer2 and Timer4).

- **3:** While operating in 32-bit mode, this bit has no effect for odd numbered timers (Timer3 and Timer5). All timer functions are set through the even numbered timers.

- **4:** While operating in 32-bit mode, this bit must be cleared on odd numbered timers to enable the 32-bit timer in Idle mode.

#### REGISTER 18-2: SPIxCON2: SPI CONTROL REGISTER 2

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3        | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0       |

|--------------|----------------------|-------------------|-------------------|-------------------|--------------------------|-------------------|------------------|------------------------|

| 31:24        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 31.24        | _                    | _                 | _                 | _                 | _                        | _                 | _                | _                      |

| 23:16        | U-0                  | U-0               | U-0               | U-0               | U-0                      | U-0               | U-0              | U-0                    |

| 23.10        | _                    | _                 | _                 | _                 | _                        | _                 | _                | _                      |

| 15:8         | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0                    | R/W-0             | R/W-0            | R/W-0                  |

| 13.6         | SPISGNEXT            | _                 | _                 | FRMERREN          | SPIROVEN                 | SPITUREN          | IGNROV           | IGNTUR                 |

| 7:0          | R/W-0                | U-0               | U-0               | U-0               | R/W-0                    | U-0               | R/W-0            | R/W-0                  |

| 7:0          | AUDEN <sup>(1)</sup> | _                 | _                 | _                 | AUDMONO <sup>(1,2)</sup> | _                 | AUDMOD           | <1:0> <sup>(1,2)</sup> |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 SPISGNEXT: Sign Extend Read Data from the RX FIFO bit

1 = Data from RX FIFO is sign extended

0 = Data from RX FIFO is not sign extened

bit 14-13 Unimplemented: Read as '0'

bit 12 **FRMERREN:** Enable Interrupt Events via FRMERR bit

1 = Frame Error overflow generates error events

0 = Frame Error does not generate error events

bit 11 SPIROVEN: Enable Interrupt Events via SPIROV bit

1 = Receive overflow generates error events

0 = Receive overflow does not generate error events

bit 10 **SPITUREN:** Enable Interrupt Events via SPITUR bit

1 = Transmit Underrun Generates Error Events

0 = Transmit Underrun Does Not Generates Error Events

bit 9 IGNROV: Ignore Receive Overflow bit (for Audio Data Transmissions)

1 = A ROV is not a critical error; during ROV data in the fifo is not overwritten by receive data

0 = A ROV is a critical error which stop SPI operation

bit 8 **IGNTUR:** Ignore Transmit Underrun bit (for Audio Data Transmissions)

1 = A TUR is not a critical error and zeros are transmitted until the SPIxTXB is not empty

0 = A TUR is a critical error which stop SPI operation

bit 7 AUDEN: Enable Audio CODEC Support bit (1)

1 = Audio protocol is enabled

0 = Audio protocol is disabled

bit 6-5 **Unimplemented:** Read as '0'

bit 3 **AUDMONO:** Transmit Audio Data Format bit<sup>(1,2)</sup>

1 = Audio data is mono (Each data word is transmitted on both left and right channels)

0 = Audio data is stereo

bit 2 **Unimplemented:** Read as '0'

bit 1-0 AUDMOD<1:0>: Audio Protocol Mode bit(1,2)

11 = PCM/DSP mode

10 = Right Justified mode

01 = Left Justified mode

$00 = I^2S \text{ mode}$

**Note 1:** This bit can only be written when the ON bit = 0.

2: This bit is only valid for AUDEN = 1.

#### REGISTER 21-2: PMMODE: PARALLEL PORT MODE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|----------------------|-------------------|-------------------|----------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0                  | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                    | _                 | _                 | _                    | _                 | -                | _                |

| 22:46        | U-0               | U-0                  | U-0               | U-0               | U-0                  | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                    | _                 | _                 | _                    | _                 | -                | _                |

| 45.0         | R-0               | R/W-0                | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | BUSY              | IRQM                 | <1:0>             | INCM              | <1:0>                | MODE16            | MODE             | E<1:0>           |

| 7.0          | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0                | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAITB             | <1:0> <sup>(1)</sup> |                   | WAITM             | <3:0> <sup>(1)</sup> |                   | WAITE<1:0>(1)    |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **BUSY:** Busy bit (Master mode only)

1 = Port is busy

0 = Port is not busy

bit 14-13 IRQM<1:0>: Interrupt Request Mode bits

- 11 = Reserved, do not use

- 10 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode) or on a read or write operation when PMA<1:0> =11 (Addressable Slave mode only)

- 01 = Interrupt generated at the end of the read/write cycle

- 00 = No Interrupt generated

- bit 12-11 INCM<1:0>: Increment Mode bits

- 11 = Slave mode read and write buffers auto-increment (MODE<1:0> = 00 only)

- 10 = Decrement ADDR<15:0> by 1 every read/write cycle<sup>(2)</sup>

- 01 = Increment ADDR<15:0> by 1 every read/write cycle(2)

- 00 = No increment or decrement of address

- bit 10 MODE16: 8/16-bit Mode bit

- 1 = 16-bit mode: a read or write to the data register invokes a single 16-bit transfer

- 0 = 8-bit mode: a read or write to the data register invokes a single 8-bit transfer

- bit 9-8 MODE<1:0>: Parallel Port Mode Select bits

- 11 = Master mode 1 (PMCSx, PMRD/PMWR, PMENB, PMA<x:0>, PMD<7:0> and PMD<8:15>(3))

- 10 = Master mode 2 (PMCSx, PMRD, PMWR, PMA<x:0>, PMD<7:0> and PMD<8:15><sup>(3)</sup>)

- 01 = Enhanced Slave mode, control signals (PMRD, PMWR, PMCS, PMD<7:0> and PMA<1:0>)

- 00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS and PMD<7:0>)

- bit 7-6 WAITB<1:0>: Data Setup to Read/Write Strobe Wait States bits(1)

- 11 = Data wait of 4 TPB; multiplexed address phase of 4 TPB

- 10 = Data wait of 3 TPB; multiplexed address phase of 3 TPB

- 01 = Data wait of 2 TPB; multiplexed address phase of 2 TPB

- 00 = Data wait of 1 TPB; multiplexed address phase of 1 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPB cycle for a write operation; WAITB = 1 TPB cycle, WAITE = 0 TPB cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- 3: These pins are active when MODE16 = 1 (16-bit mode).

### REGISTER 21-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | -                 | _                 | -                 | _                 | -                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | -                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              | _                 | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

Legend:HS = Set by HardwareSC = Cleared by softwareR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 IBF: Input Buffer Full Status bit

1 = All writable input buffer registers are full

0 = Some or all of the writable input buffer registers are empty

bit 14 IBOV: Input Buffer Overflow Status bit

1 = A write attempt to a full input byte buffer occurred (must be cleared in software)

0 = No overflow occurred

bit 13-12 Unimplemented: Read as '0'

bit 11-8 IBxF: Input Buffer 'x' Status Full bits

1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

0 = Input Buffer does not contain any unread data

bit 7 **OBE:** Output Buffer Empty Status bit

1 = All readable output buffer registers are empty

0 = Some or all of the readable output buffer registers are full

bit 6 **OBUF:** Output Buffer Underflow Status bit

1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

bit 5-4 Unimplemented: Read as '0'

bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

1 = Output buffer is empty (writing data to the buffer will clear this bit)

0 = Output buffer contains data that has not been transmitted

#### 24.0 **COMPARATOR**

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer Section 19. to "Comparator" (DS60001110), which is available from the Documentation Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

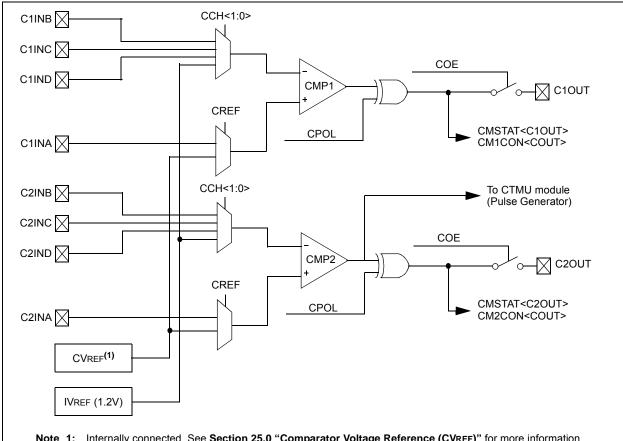

The Analog Comparator module contains two comparators that can be configured in a variety of ways.

The following are key features of this module:

- · Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be Inverted

- · Selectable interrupt generation

A block diagram of the comparator module is provided in Figure 24-1.

#### **FIGURE 24-1: COMPARATOR BLOCK DIAGRAM**

#### REGISTER 28-3: DEVCFG2: DEVICE CONFIGURATION WORD 2

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2            | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------------------|------------------|------------------|--|

| 24.24        | r-1                   | r-1               | r-1               | r-1               | r-1               | r-1                          | r-1              | r-1              |  |

| 31:24        | _                     | _                 | _                 | _                 | _                 | _                            | _                | _                |  |

| 00.40        | r-1                   | r-1               | r-1               | r-1               | r-1               | R/P                          | R/P              | R/P              |  |

| 23:16        | _                     | _                 | _                 | _                 | _                 | FPLLODIV<2:0>                |                  |                  |  |

| 45.0         | R/P                   | r-1               | r-1               | r-1               | r-1               | R/P                          | R/P              | R/P              |  |

| 15:8         | UPLLEN <sup>(1)</sup> | _                 | _                 | _                 | _                 | UPLLIDIV<2:0> <sup>(1)</sup> |                  |                  |  |

| 7:0          | r-1                   | R/P-1             | R/P               | R/P-1             | r-1               | R/P                          | R/P              | R/P              |  |

|              | _                     | F                 | PLLMUL<2:0        | >                 | _                 | FPLLIDIV<2:0>                |                  |                  |  |

| Legend:           | r = Reserved bit | P = Programmable bit     |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

```

bit 31-19 Reserved: Write '1'

```

bit 18-16 FPLLODIV<2:0>: Default PLL Output Divisor bits

111 = PLL output divided by 256

110 = PLL output divided by 64

101 = PLL output divided by 32

100 = PLL output divided by 16

011 = PLL output divided by 8

010 = PLL output divided by 4

001 = PLL output divided by 2

000 = PLL output divided by 1

bit 15 **UPLLEN:** USB PLL Enable bit<sup>(1)</sup>

1 = Disable and bypass USB PLL

0 = Enable USB PLL

bit 14-11 Reserved: Write '1'

bit 10-8 UPLLIDIV<2:0>: USB PLL Input Divider bits(1)

111 = 12x divider

110 = 10x divider

101 = 6x divider

100 = 5x divider

011 = 4x divider

010 = 3x divider

001 = 2x divider

000 = 1x divider

bit 7 Reserved: Write '1'

bit 6-4 FPLLMUL<2:0>: PLL Multiplier bits

111 = 24x multiplier

110 = 21x multiplier

101 = 20x multiplier

100 = 19x multiplier

011 = 18x multiplier

010 = 17x multiplier

001 = 16x multiplier

000 = 15x multiplier

bit 3 Reserved: Write '1'

Note 1: This bit is available on PIC32MX4XX devices only.

TABLE 31-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) (CONTINUED)

| DC CHARACTERISTICS |                     |             |         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)<br>Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                           |  |  |  |  |

|--------------------|---------------------|-------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|--|--|--|--|

| Param. No.         | Typ. <sup>(2)</sup> | Max.        | Units   | Conditions                                                                                                                                                                                                                                                  |                           |  |  |  |  |

| PIC32MX35          | 0F256 D             | evices O    | nly     |                                                                                                                                                                                                                                                             |                           |  |  |  |  |

| Power-Dow          | n Currer            | it (IPD) (N | lote 1) |                                                                                                                                                                                                                                                             |                           |  |  |  |  |

| DC40k              | 38                  | 80          | μА      | -40°C                                                                                                                                                                                                                                                       |                           |  |  |  |  |

| DC40I              | 57                  | 80          | μΑ      | +25°C                                                                                                                                                                                                                                                       | Base Power-Down Current   |  |  |  |  |

| DC40n              | 220                 | 352         | μΑ      | +85°C                                                                                                                                                                                                                                                       | - Base Fower-Down Current |  |  |  |  |

| DC40m              | 513                 | 749         | μA      | +105°C                                                                                                                                                                                                                                                      |                           |  |  |  |  |

| PIC32MX45          | 0F256 De            | evices O    | nly     |                                                                                                                                                                                                                                                             |                           |  |  |  |  |

| Power-Dow          | n Curren            | it (IPD) (N | lote 1) |                                                                                                                                                                                                                                                             |                           |  |  |  |  |

| DC40k              | 26                  | 42          | μА      | -40°C                                                                                                                                                                                                                                                       |                           |  |  |  |  |

| DC40o              | 26                  | 42          | μA      | 0°C <sup>(5)</sup>                                                                                                                                                                                                                                          |                           |  |  |  |  |

| DC40I              | 26                  | 42          | μА      | +25°C                                                                                                                                                                                                                                                       | Base Power-Down Current   |  |  |  |  |

| DC40p              | 250                 | 352         | μA      | +70°C <sup>(5)</sup>                                                                                                                                                                                                                                        | Dase i owei-Down Gunent   |  |  |  |  |

| DC40n              | 250                 | 352         | μА      | +85°C                                                                                                                                                                                                                                                       |                           |  |  |  |  |

| DC40m              | 513                 | 749         | μA      | +105°C                                                                                                                                                                                                                                                      |                           |  |  |  |  |

**Note 1:** The test conditions for IPD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, program Flash memory Wait states = 7, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- Voltage regulator is off during Sleep mode (VREGS bit in the RCON register = 0)

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The  $\Delta$  current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: 120 MHz commercial devices only (0°C to +70°C).

**TABLE 31-41: OTG ELECTRICAL SPECIFICATIONS**

| AC CHA        | AC CHARACTERISTICS |                                   |      |      |      |       |                                                                                   |  |  |

|---------------|--------------------|-----------------------------------|------|------|------|-------|-----------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol             | Characteristics <sup>(1)</sup>    | Min. | Тур. | Max. | Units | Conditions                                                                        |  |  |

| USB313        | VUSB3V3            | USB Voltage                       | 3.0  | _    | 3.6  | V     | Voltage on Vusb3v3<br>must be in this range<br>for proper USB<br>operation        |  |  |

| USB315        | VILUSB             | Input Low Voltage for USB Buffer  | _    | _    | 0.8  | V     | _                                                                                 |  |  |

| USB316        | VIHUSB             | Input High Voltage for USB Buffer | 2.0  | _    | _    | V     | _                                                                                 |  |  |

| USB318        | VDIFS              | Differential Input Sensitivity    | _    | _    | 0.2  | V     | The difference<br>between D+ and D-<br>must exceed this value<br>while VCM is met |  |  |

| USB319        | VCM                | Differential Common Mode Range    | 0.8  | _    | 2.5  | V     | _                                                                                 |  |  |

| USB320        | Zout               | Driver Output Impedance           | 28.0 | _    | 44.0 | Ω     | _                                                                                 |  |  |

| USB321        | Vol                | Voltage Output Low                | 0.0  | _    | 0.3  | V     | 1.425 kΩ load connected to Vusb3V3                                                |  |  |

| USB322        | Vон                | Voltage Output High               | 2.8  | _    | 3.6  | V     | 14.25 kΩ load connected to ground                                                 |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

### **INDEX**

| Α                                             |          | CPU Module2                                        | 7, 35 |

|-----------------------------------------------|----------|----------------------------------------------------|-------|

| AC Characteristics                            | 295      | CTMU                                               |       |

| 10-Bit Conversion Rate Parameters             |          | Registers                                          | . 253 |

| ADC Specifications                            |          | Customer Change Notification Service               | . 359 |

| Analog-to-Digital Conversion Requirements     |          | Customer Notification Service                      |       |

| EJTAG Timing Requirements                     |          | Customer Support                                   | . 359 |

| Internal FRC Accuracy                         |          | D                                                  |       |

| Internal RC Accuracy                          |          |                                                    |       |

| OTG Electrical Specifications                 |          | DC and AC Characteristics                          |       |

| Parallel Master Port Read Requirements        |          | Graphs and Tables                                  |       |

| Parallel Master Port Write                    |          | DC Characteristics                                 |       |

| Parallel Master Port Write Requirements       | 324      | I/O Pin Input Specifications                       |       |

| Parallel Slave Port Requirements              |          | I/O Pin Output Specifications                      |       |

| PLL Clock Timing                              |          | Idle Current (IDLE)                                |       |

| Analog-to-Digital Converter (ADC)             | 233      | Power-Down Current (IPD)                           |       |

| Assembler                                     |          | Program Memory                                     |       |

| MPASM Assembler                               | 276      | Temperature and Voltage Specifications             |       |

| n.                                            |          | Development Support                                |       |

| В                                             |          | Direct Memory Access (DMA) Controller              | 93    |

| Block Diagrams                                |          | E                                                  |       |

| ADC Module                                    |          | Electrical Characteristics                         | 279   |

| Comparator I/O Operating Modes                |          | AC                                                 |       |

| Comparator Voltage Reference                  |          | Errata                                             |       |

| Connections for On-Chip Voltage Regulator     |          | External Clock                                     |       |

| CPU                                           | 35       | Timer1 Timing Requirements                         | . 301 |

| CTMU Configurations                           |          | Timer2, 3, 4, 5 Timing Requirements                |       |

| Time Measurement                              |          | Timing Requirements                                |       |

| DMA                                           |          |                                                    |       |

| I2C Circuit                                   |          | F                                                  |       |

| Input Capture                                 |          | Flash Program Memory                               | 53    |

| Interrupt Controller                          |          | RTSP Operation                                     | 53    |

| JTAG Programming, Debugging and Trace Port    |          | 11                                                 |       |

| Output Compare Module                         |          | н                                                  |       |

| PMP Pinout and Connections to External Device |          | High Voltage Detect (HVD)61, 272                   | , 291 |

| Prefetch Module                               |          | Ī                                                  |       |

| Reset System                                  |          | I                                                  |       |

| RTCC<br>SPI Module                            |          | I/O Ports                                          |       |

| Timer1                                        |          | Parallel I/O (PIO)                                 |       |

| Timer2/3/4/5 (16-Bit)                         |          | Write/Read Timing                                  |       |

| Typical Multiplexed Port Structure            |          | Input Change Notification                          |       |

| UART                                          |          | Instruction Set                                    |       |

| WDT and Power-up Timer                        |          | Inter-Integrated Circuit (I2C                      |       |

| Brown-out Reset (BOR)                         | 177      | Internal Voltage Reference Specifications          |       |

| and On-Chip Voltage Regulator                 | 272      | Internet Address                                   |       |

|                                               | 2. 2     | Interrupt ControllerIRG, Vector and Bit Location   |       |

| C                                             |          | ING, Vector and bit Location                       | 04    |

| C Compilers                                   |          | M                                                  |       |

| MPLAB C18                                     | 276      | Memory Maps                                        |       |

| Charge Time Measurement Unit. See CTMU.       |          | Devices with 128 KB of Program Memory              | 41    |

| Clock Diagram                                 | 74       | Devices with 256 KB of Program Memory              |       |

| Comparator                                    |          | Devices with 512 KB of Program Memory              |       |

| Specifications2                               | 293, 294 | Devices with 64 KB of Program Memory               |       |

| Comparator Module                             | 243      | Memory Organization                                |       |

| Comparator Voltage Reference (CVref           | 247      | Layout                                             |       |

| Configuration Bit                             |          | Microchip Internet Web Site                        |       |

| Configuring Analog Port Pins                  | 138      | MPLAB ASM30 Assembler, Linker, Librarian           |       |

| CPU                                           |          | MPLAB Integrated Development Environment Software. |       |

| Architecture Overview                         | 36       | MPLAB PM3 Device Programmer                        |       |

| Coprocessor 0 Registers                       | 37       | MPLAB REAL ICE In-Circuit Emulator System          |       |

| Core Exception Types                          | 38       | MPLINK Object Linker/MPLIB Object Librarian        |       |

| EJTAG Debug Support                           |          | •                                                  |       |

| Power Management                              | 38       |                                                    |       |

### Worldwide Sales and Service

#### **AMERICAS**

Corporate Office 2355 West Chandler Blvd.

Chandler, AZ 85224-6199

Tel: 480-792-7200 Fax: 480-792-7277 Technical Support:

http://www.microchip.com/

support

Web Address: www.microchip.com

Atlanta

Duluth, GA Tel: 678-957-9614 Fax: 678-957-1455

Austin, TX

Tel: 512-257-3370

**Boston**

Westborough, MA Tel: 774-760-0087 Fax: 774-760-0088

Chicago Itasca, IL

Tel: 630-285-0071 Fax: 630-285-0075

Cleveland

Independence, OH Tel: 216-447-0464 Fax: 216-447-0643

**Dallas**

Addison, TX Tel: 972-818-7423 Fax: 972-818-2924

**Detroit** Novi, MI

Tel: 248-848-4000

Houston, TX Tel: 281-894-5983

Indianapolis Noblesville, IN

Tel: 317-773-8323 Fax: 317-773-5453

Los Angeles

Mission Viejo, CA Tel: 949-462-9523 Fax: 949-462-9608

New York, NY Tel: 631-435-6000

**San Jose, CA** Tel: 408-735-9110

**Canada - Toronto** Tel: 905-695-1980 Fax: 905-695-2078

#### ASIA/PACIFIC

**Asia Pacific Office**

Suites 3707-14, 37th Floor Tower 6, The Gateway Harbour City, Kowloon

**Hong Kong**