Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 49                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-VQFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f128ht-v-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 6: PIN NAMES FOR 124-PIN DEVICES (CONTINUED)

| 124               | -PIN VTLA (BOTTOM VIEW) <sup>(1,2,3,4,5)</sup> A17                       |                   |                  | A34                       |

|-------------------|--------------------------------------------------------------------------|-------------------|------------------|---------------------------|

|                   | AT/                                                                      |                   | B13 B29          | Conductive<br>Thermal Pad |

|                   | PIC32MX330F064L<br>PIC32MX350F128L<br>PIC32MX350F256L<br>PIC32MX370F512L |                   | B1 E<br>B56      | 341<br>A51                |

|                   | Polarity I                                                               | A1<br>tor         | A68              |                           |

| Package<br>Bump # | Full Pin Name                                                            | Package<br>Bump # |                  | Full Pin Name             |

| B7                | MCLR                                                                     | B32               | SDA2/RA3         |                           |

| B8                | Vss                                                                      | B33               | TDO/RA5          |                           |

| B9                | TMS/CTED1/RA0                                                            | B34               | OSC1/CLKI/RC12   |                           |

| B10               | RPE9/RE9                                                                 | B35               | No Connect       |                           |

| B11               | AN4/C1INB/RB4                                                            | B36               | RPA14/RA14       |                           |

| B12               | Vss                                                                      | B37               | RPD8/RTCC/RD8    |                           |

| B13               | PGEC3/AN2/C2INB/RPB2/CTED13/RB2                                          | B38               | RPD10/PMCS2/RD10 | )                         |

| B14               | PGED1/AN0/RPB0/RB0                                                       | B39               | RPD0/RD0         |                           |

| B15               | No Connect                                                               | B40               | SOSCO/RPC14/T1Ck |                           |

| B16               | PGED2/AN7/RPB7/CTED3/RB7                                                 | B41               | Vss              |                           |

| B17               | VREF+/CVREF+/PMA6/RA10                                                   | B42               | AN25/RPD2/RD2    |                           |

| B18               | AVss                                                                     | B43               | RPD12/PMD12/RD12 |                           |

| B19               | AN9/RPB9/CTED4/RB9                                                       | B44               | RPD4/PMWR/RD4    |                           |

| B20               | AN11/PMA12/RB11                                                          | B45               | PMD14/RD6        |                           |

| B21               | VDD                                                                      | B46               | No Connect       |                           |

| B22               | RPF13/RF13                                                               | B47               | No Connect       |                           |

| B23               | AN12/PMA11/RB12                                                          | B48               | VCAP             |                           |

| B24               | AN14/RPB14/CTED5/PMA1/RB14                                               | B49               | RPF0/PMD11/RF0   |                           |

| B25               | Vss                                                                      | B50               | RPG1/PMD9/RG1    |                           |

| B26               | RPD14/RD14                                                               | B51               | TRCLK/RA6        |                           |

| B27               | RPF4/PMA9/RF4                                                            | B52               | PMD0/RE0         |                           |

| B28               | No Connect                                                               | B53               | Vdd              |                           |

| B29               | RPF8/RF8                                                                 | B54               | TRD2/RG14        |                           |

| B30               | RPF6/SCKI/INT0/RF6                                                       | B55               | TRD0/RG13        |                           |

| B31               | SCL1/RG2                                                                 | B56               | RPE3/CTPLS/PMD3/ | RE3                       |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx), with the exception of RF6, can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: RPF6 (bump B30) and RPF7 (bump A37) are only remappable for input functions.

4: Shaded package bumps are 5V tolerant.

5: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

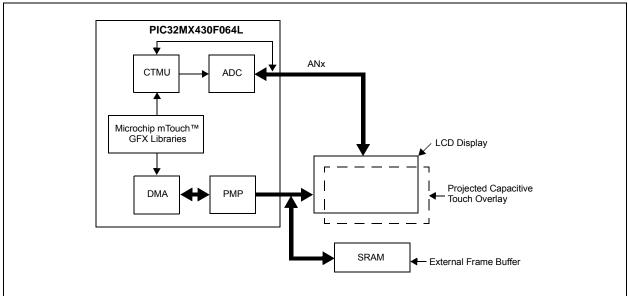

# FIGURE 2-8: LOW-COST CONTROLLERLESS (LCC) GRAPHICS APPLICATION WITH PROJECTED CAPACITIVE TOUCH

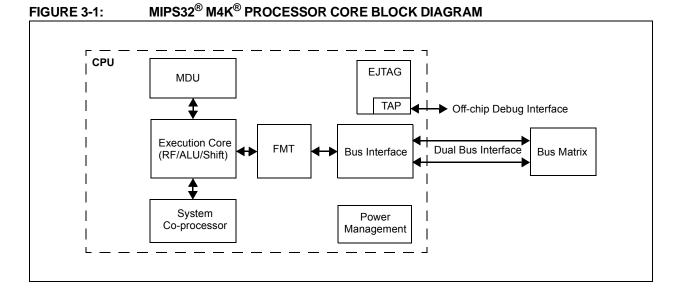

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at http://www.imgtec.com.

The the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX330/350/370/430/450/470 device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

# 3.1 Features

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32<sup>®</sup> Enhanced Architecture (Release 2):

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> Code Compression:

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) Mechanism:

- Simple Dual Bus Interface:

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- Autonomous Multiply/Divide Unit (MDU):

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- · Power Control:

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG Debug and Instruction Trace:

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 31:24        |                   |                   |                   | CHEW1<            | :31:24>           |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 23:16        |                   | CHEW1<23:16>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 15:8         |                   |                   |                   | CHEW1             | <15:8>            |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 7:0          |                   |                   |                   | CHEW1             | <7:0>             |                   |                  |                  |  |  |  |  |

## REGISTER 9-6: CHEW1: CACHE WORD 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

## REGISTER 9-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 31:24        |                   |                   |                   | CHEW2<            | 31:24>            |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 23:16        | CHEW2<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 15:8         |                   |                   |                   | CHEW2             | <15:8>            |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 7:0          |                   |                   |                   | CHEW2             | <7:0>             |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

# **10.1 Control Registers**

## TABLE 10-1: DMA GLOBAL REGISTER MAP

| ess                         |                                 | 0         |       |       |       |         |         |       |      | Bit      | S       |      |      |      |      |      |          |      | ŝ         |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|---------|---------|-------|------|----------|---------|------|------|------|------|------|----------|------|-----------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8     | 23/7    | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | All Reset |

| 2000                        | DMACON                          | 31:16     | -     | _     | -     | —       | —       | _     | —    | —        | —       | —    | _    | —    | -    | —    | —        | _    | 0000      |

| 3000                        | DIVIACON                        | 15:0      | ON    | _     | _     | SUSPEND | DMABUSY | —     | _    | _        | _       | _    | _    | —    | —    | _    | —        | _    | 0000      |

| 2010                        | DMASTAT                         | 31:16     |       | _     | —     | —       | —       | _     | —    | —        | —       | —    | _    | _    | —    | _    | —        | _    | 0000      |

| 3010                        | DIVIASTAT                       | 15:0      |       | _     | —     | —       | —       | _     | —    | —        | —       | —    | _    | _    | RDWR | C    | MACH<2:0 | >    | 0000      |

| 2020                        | DMAADDR                         | 31:16     |       |       |       |         |         |       |      | DMAADD   | D-21.05 |      |      |      |      |      |          |      | 0000      |

| 3020                        | DIVIAADDR                       | 15:0      |       |       |       |         |         |       |      | DIVIAADD | KN01.02 |      |      |      |      |      |          |      | 0000      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

## TABLE 10-2: DMA CRC REGISTER MAP

| ess                         |                                 |           |               |                |       |                     |       |           |      | Bi   | ts        |        | _      |      |      |      |          |      |            |

|-----------------------------|---------------------------------|-----------|---------------|----------------|-------|---------------------|-------|-----------|------|------|-----------|--------|--------|------|------|------|----------|------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14          | 29/13 | 28/12               | 27/11 | 26/10     | 25/9 | 24/8 | 23/7      | 22/6   | 21/5   | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | All Resets |

| 2020                        |                                 | 31:16     | _             | —              | BYTO  | TO<1:0> WBO BITO 00 |       |           |      |      |           |        | 0000   |      |      |      |          |      |            |

| 3030                        | DCRCCON                         | 15:0      | _             | —              | _     |                     |       | PLEN<4:0> |      |      | CRCEN     | CRCAPP | CRCTYP | —    | —    | C    | RCCH<2:0 | >    | 0000       |

| 3040                        | DCRCDATA                        | 31:16     |               |                |       |                     |       |           |      |      | TA -21.05 |        |        |      |      |      |          |      | 0000       |

| 3040                        | DCRCDAIA                        | 15:0      |               | DCRCDATA<31:0> |       |                     |       |           |      |      |           |        |        |      |      |      |          |      |            |

| 2050                        | DCRCXOR                         | 31:16     |               | DCRCXOR<31:0>  |       |                     |       |           |      |      |           |        |        |      |      |      |          |      |            |

| 3050                        | DURUXUR                         | 15:0      | DCRCXOR<31.0> |                |       |                     |       |           |      |      | 0000      |        |        |      |      |      |          |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                     | —                 | _                 | _                 |                   | _                 | -                | —                     |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                   | —                 | _                 | -                 | _                 | —                 | _                | —                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | —                 | _                 | _                 | _                 | _                 | _                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | CHPF             | RI<1:0>               |

### REGISTER 10-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14-9 Unimplemented: Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

## bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 = Channel is disabled

## bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

#### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

0 = Channel is disabled on block transfer complete

## bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

- bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 |                   |                   | —                 |                   | _                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 |                   |                   | —                 | -                 | _                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | _                 | _                 | _                 | —                 | _                 | _                 | -                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | LSPDEN            |                   |                   | D                 | EVADDR<6:0        | >                 |                  |                  |

# REGISTER 11-12: U1ADDR: USB ADDRESS REGISTER

# Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7 **LSPDEN:** Low Speed Enable Indicator bit

1 = Next token command to be executed at Low Speed

0 = Next token command to be executed at Full Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

|              |                   |                   |                   | HOMBER E          |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | -                 | _                 | —                 | _                 | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | _                 | —                 | _                 | —                | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | —                 |                   |                   | —                 | -                 | —                | —                |

| 7.0          | R-0 R-0           |                   | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | FRML              | <7:0>             |                   |                  |                  |

#### REGISTER 11-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

# TABLE 12-17: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| sse                         |                       |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |                   |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|-------------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1              | 16/0 | All Resets |

| FA54                        | U1CTSR                | 31:16     | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | —    |      |       |                   | _    | 0000       |

| FA04                        | UICISK                | 15:0      | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    |      | U1CTS | SR<3:0>           |      | 0000       |

|                             |                       | 31:16     | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    | _    |       | —                 | _    | 0000       |

| FA58                        | U2RXR                 | 15:0      | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    |      | U2RX  | R<3:0>            |      | 0000       |

| FA5C                        | U2CTSR                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _                 | -    | 0000       |

| FASC                        | UZCISK                | 15:0      | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    |      | U2CTS | SR<3:0>           |      | 0000       |

| FA60                        | <b>U3RXR</b>          | 31:16     | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    | _    |       | —                 | _    | 0000       |

| FAOU                        | USKAR                 | 15:0      | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    |      | U3RX  | R<3:0>            |      | 0000       |

| 5464                        | <b>U3CTSR</b>         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _                 | -    | 0000       |

| FA64                        | USCISK                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U3CTS | SR<3:0>           |      | 0000       |

| 5400                        | U4RXR                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _                 | -    | 0000       |

| FA68                        | U4RXR                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U4RX  | R<3:0>            |      | 0000       |

| FA6C                        | U4CTSR                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _                 | -    | 0000       |

| FAGC                        | U4CISR                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U4CTS | SR<3:0>           |      | 0000       |

| FA70                        | U5RXR <sup>(1)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _                 | -    | 0000       |

| FA70                        | USRXR <sup>(1)</sup>  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | —    | _    | _    | -    |      | U5RX  | R<3:0>            |      | 0000       |

| FA74                        | U5CTSR <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | —    | _    | —    | —    | —    | —    | _    | —     | —                 | -    | 0000       |

| FA74                        | 0501580               | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U5CTS | SR<3:0>           |      | 0000       |

| 5404                        | SDI1R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _                 | -    | 0000       |

| FA84                        | SDITR                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | —    | _    | _    | -    |      | SDI1F | R<3:0>            |      | 0000       |

| <b>FA00</b>                 | 0040                  | 31:16     | _     | _     | _     | _     | _     | _     | —    | _    | —    | —    | —    | —    | _    | —     | —                 | -    | 0000       |

| FA88                        | SS1R                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | —    | _    | _    | _    |      | SS1F  | R<3:0>            |      | 0000       |

| FA00                        | SDI2R                 | 31:16     | _     | —     | _     |       | —     | —     |      | —    | -    |      | —    | _    | _    | —     | —                 | _    | 0000       |

| FA90                        | SDIZR                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | SDI2F | R<3:0>            |      | 0000       |

| E404                        | SS2R                  | 31:16     | _     | —     | _     |       | —     | —     |      | —    | -    |      | —    | _    | _    | —     | —                 | _    | 0000       |

| FA94                        | 552R                  | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | —    |      | SS2F  | R<3:0>            |      | 0000       |

| FADO                        |                       | 31:16     | _     | —     | _     | _     | —     | —     |      | —    | _    |      | —    | _    | _    | _     | —                 | _    | 0000       |

| FAD0                        | REFCLKIR              | 15:0      | _     | _     | _     | —     | _     | —     | _    | —    | _    | —    | _    | _    |      | REFCL | <ir<3:0></ir<3:0> |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 | —                 | -                 | _                 | _                 | _                | —                |

| 15.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 |                   | _                | —                |

| 7.0          | U-0 U-0           |                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 |                   | _                 | _                 | _                 | _                 | _                |                  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = CPU Idle Mode halts CN operation

- 0 = CPU Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

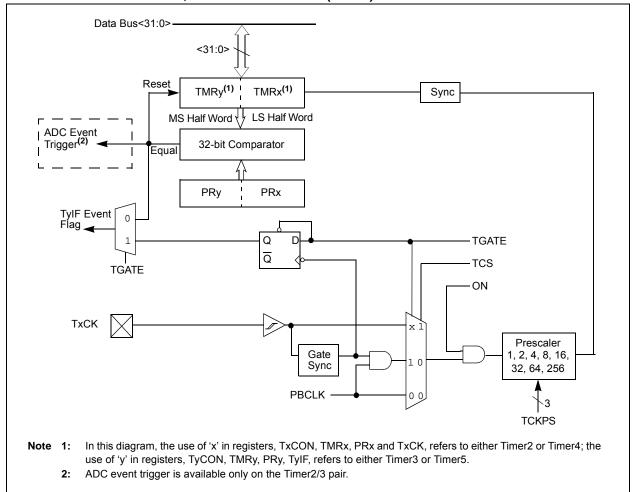

## FIGURE 14-2: TIMER2/3, 4/5 BLOCK DIAGRAM (32-BIT)<sup>(1)</sup>

# 15.1 Watchdog Timer Control Registers

| DS60001185F-page |  |

|------------------|--|

| е<br>—           |  |

| 78               |  |

# TABLE 15-1: WATCHDOG TIMER CONTROL REGISTER MAP

| ess                        |                                 | æ         |       | Bits  |       |       |       |       |      |      |      |      |      |          |      |      |          |        |            |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|------|------|----------|--------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3 | 18/2 | 17/1     | 16/0   | All Resets |

| 0000                       | WDTCON                          | 31:16     | _     | _     | _     | _     | -     | -     | —    | —    | _    | —    | —    | _        | _    | _    | —        | —      | 0000       |

| 0000                       | WDICON                          | 15:0      | ON    |       |       |       | _     | _     | _    | _    |      |      | SI   | VDTPS<4: | )>   |      | WDTWINEN | WDTCLR | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

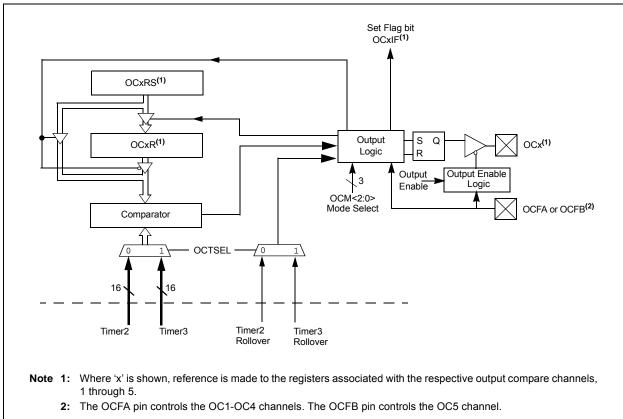

# 17.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Output Compare" (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are key features of this module:

- Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

# FIGURE 17-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

# 22.1 Control Registers

# TABLE 22-1: RTCC REGISTER MAP

| ess                         |                                 | 0         |        |       |         |          | Bits                   |                  |        |      |          |          |       |      |         |         |         |       | 8         |

|-----------------------------|---------------------------------|-----------|--------|-------|---------|----------|------------------------|------------------|--------|------|----------|----------|-------|------|---------|---------|---------|-------|-----------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15  | 30/14 | 29/13   | 28/12    | 27/11                  | 26/10            | 25/9   | 24/8 | 23/7     | 22/6     | 21/5  | 20/4 | 19/3    | 18/2    | 17/1    | 16/0  | All Reset |

| 0200                        | RTCCON                          | 31:16     | _      | _     | _       | -        | _                      | -                |        |      | CAL<9:0> |          |       |      |         |         |         | 0000  |           |

| 0200                        | RICCON                          | 15:0      | ON     | _     | SIDL    | —        | _                      |                  |        |      |          | RTCCLKON | _     | _    | RTCWREN | RTCSYNC | HALFSEC | RTCOE | 0000      |

| 0210                        | RTCALRM                         | 31:16     | —      | _     | _       | —        | _                      | -                |        | _    | —        | _        | _     | _    | —       | _       | —       | —     | 0000      |

| 0210                        | RICALNI                         | 15:0      | ALRMEN | CHIME | PIV     | ALRMSYNC | C AMASK<3:0> ARPT<7:0> |                  |        |      |          |          |       |      | 0000    |         |         |       |           |

| 0220                        | RTCTIME                         | 31:16     |        | HR10  | 0<3:0>  |          |                        | HR01             | <3:0>  |      |          | MIN10<   | 3:0>  |      |         | MIN01   | <3:0>   |       | xxxx      |

| 0220                        |                                 | 15:0      |        | SEC1  | 0<3:0>  |          |                        | SEC07            | 1<3:0> |      | —        | _        | _     | _    | _       | —       | —       | —     | xx00      |

| 0230                        | RTCDATE                         | 31:16     |        | YEAR  | 10<3:0> |          |                        | YEAR0            | 1<3:0> |      |          | MONTH10  | <3:0> |      |         | MONTH   | 01<3:0> |       | xxxx      |

| 0230                        | RIODAIL                         | 15:0      |        | DAY1  | 0<3:0>  |          |                        | DAY01            | 1<3:0> |      | —        | _        | _     | _    |         | WDAY0   | 1<3:0>  |       | xx00      |

| 0240                        | ALRMTIME                        | 31:16     |        | HR10  | 0<3:0>  |          |                        | HR01             | <3:0>  |      |          | MIN10<   | 3:0>  |      |         | MIN01   | <3:0>   |       | xxxx      |

| 0240                        |                                 | 15:0      |        | SEC1  | 0<3:0>  |          |                        | SEC01<3:0> — — — |        |      |          | _        | _     | _    | —       | —       | —       | xx00  |           |

| 0250                        | ALRMDATE                        | 31:16     | —      | _     | _       | _        | —                      | —                | —      | _    |          | MONTH10  | <3:0> |      |         | MONTH   | 01<3:0> |       | 00xx      |

| 0200                        |                                 | 15:0      |        | DAY1  | 0<3:0>  |          | DAY01<3:0>             |                  |        |      | —        | _        | _     | _    |         | WDAY0   | 1<3:0>  |       | xx0x      |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | —                 | —                 | —                 | _                 | _                 |                  | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | —                 | —                 | —                 | _                 | _                 |                  | —                |

| 15:8         | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | -                 | —                 | SIDL              | —                 | _                 | _                 |                  | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R-0              | R-0              |

| 7:0          |                   | _                 |                   |                   |                   |                   | C2OUT            | C1OUT            |

## REGISTER 24-2: CMSTAT: COMPARATOR STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in IDLE Control bit

1 = All Comparator modules are disabled in IDLE mode

0 = All Comparator modules continue to operate in the IDLE mode

- bit 12-2 Unimplemented: Read as '0'

- bit 1 **C2OUT:** Comparator Output bit

- 1 = Output of Comparator 2 is a '1'

- 0 = Output of Comparator 2 is a '0'

## bit 0 C1OUT: Comparator Output bit

- 1 = Output of Comparator 1 is a '1'

- 0 = Output of Comparator 1 is a '0'

# 25.1 Control Register

# TABLE 25-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| ess                       |                                 | e         |       |       |       |       |       |       |      | Bits |      |       |      |       |      |      |      |      | ú         |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------|------|-------|------|------|------|------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 0000                      | CVRCON                          | 31:16     | _     | —     | -     | -     | -     | -     | —    | —    | _    | -     | -    | —     | —    | —    | —    | _    | 0000      |

| 9000                      | UVRCON                          | 15:0      | ON    | —     | _     | _     | —     | —     | —    | —    | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The register in this table has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# TABLE 31-15: COMPARATOR VOLTAGE REFERENCE SPECIFICATIONS

| DC CHA        | RACTERI | STICS                                                        | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |   |                    |     |                                                                  |  |

|---------------|---------|--------------------------------------------------------------|------------------------------------------------------|---|--------------------|-----|------------------------------------------------------------------|--|

| Param.<br>No. | Symbol  | Characteristics                                              | Min. Typ. Max. Units Comments                        |   |                    |     | Comments                                                         |  |

| D312          | TSET    | Internal 4-bit DAC<br>Comparator Reference<br>Settling time. | _                                                    |   | 10                 | μs  | See Note 1                                                       |  |

| D313          | DACREFH | CVREF Input Voltage                                          | AVss                                                 |   | AVDD               | V   | CVRSRC with CVRSS = 0                                            |  |

|               |         | Reference Range                                              | VREF-                                                |   | VREF+              | V   | CVRSRC with CVRSS = 1                                            |  |

| D314          | DVREF   | CVREF Programmable<br>Output Range                           | 0                                                    | _ | 0.625 x<br>DACREFH | V   | 0 to 0.625 DACREFH with<br>DACREFH/24 step size                  |  |

|               |         |                                                              | 0.25 x<br>DACREFH                                    | — | 0.719 x<br>DACREFH | V   | 0.25 x DACREFH to 0.719<br>DACREFH with DACREFH/<br>32 step size |  |

| D315          | DACRES  | Resolution                                                   | _                                                    | _ | DACREFH/24         |     | CVRCON <cvrr> = 1</cvrr>                                         |  |

|               |         |                                                              | —                                                    |   | DACREFH/32         |     | CVRCON <cvrr> = 0</cvrr>                                         |  |

| D316          | DACACC  | Absolute Accuracy <sup>(2)</sup>                             | —                                                    | _ | 1/4                | LSB | DACREFH/24,<br>CVRCON <cvrr> = 1</cvrr>                          |  |

|               |         |                                                              | _                                                    |   | 1/2                | LSB | DACREFH/32,<br>CVRCON <cvrr> = 0</cvrr>                          |  |

**Note 1:** Settling time was measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but is not tested in manufacturing.

2: These parameters are characterized but not tested.

## TABLE 31-16: INTERNAL VOLTAGE REGULATOR SPECIFICATIONS

| DC CHARACTERISTICS |        |                                 | $ \begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array} $ |         |      |       |                                                                                                    |

|--------------------|--------|---------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|----------------------------------------------------------------------------------------------------|

| Param.<br>No.      | Symbol | Characteristics                 | Min.                                                                                                                                                                                                                                                                                                                                                      | Typical | Max. | Units | Comments                                                                                           |

| D321               | Cefc   | External Filter Capacitor Value | 8                                                                                                                                                                                                                                                                                                                                                         | 10      |      | μF    | Capacitor must be low series<br>resistance (3 ohm). Typical<br>voltage on the VCAP pin is<br>1.8V. |

## TABLE 31-18: EXTERNAL CLOCK TIMING REQUIREMENTS

|               |               |                                                                                                                  | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)                                                                                                                                                                     |                        |             |            |                                         |  |

|---------------|---------------|------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|-------------|------------|-----------------------------------------|--|

| AC CHA        | RACTER        | RISTICS                                                                                                          | $\begin{array}{ll} Operating \ temperature & 0^\circ C \leq TA \leq +70^\circ C \ for \ Commercial \\ -40^\circ C \leq TA \leq +85^\circ C \ for \ Industrial \\ -40^\circ C \leq TA \leq +105^\circ C \ for \ V\text{-temp} \end{array}$ |                        |             |            |                                         |  |

| Param.<br>No. | Symbol        | Characteristics                                                                                                  | Min.                                                                                                                                                                                                                                      | Typical <sup>(1)</sup> | Max.        | Units      | Conditions                              |  |

| OS10          | Fosc          | External CLKI Frequency<br>(External clocks allowed only<br>in EC and ECPLL modes)                               | DC<br>4                                                                                                                                                                                                                                   | _                      | 50<br>50    | MHz<br>MHz | EC (Note 4)<br>ECPLL (Note 3)           |  |

| OS11          |               | Oscillator Crystal Frequency                                                                                     | 3                                                                                                                                                                                                                                         |                        | 10          | MHz        | XT (Note 4)                             |  |

| OS12          |               |                                                                                                                  | 4                                                                                                                                                                                                                                         |                        | 10          | MHz        | XTPLL<br>(Notes 3,4)                    |  |

| OS13          |               |                                                                                                                  | 10                                                                                                                                                                                                                                        |                        | 25          | MHz        | HS (Note 4)                             |  |

| OS14          |               |                                                                                                                  | 10                                                                                                                                                                                                                                        | _                      | 25          | MHz        | HSPLL<br>(Notes 3,4)                    |  |

| OS15          |               |                                                                                                                  | 32                                                                                                                                                                                                                                        | 32.768                 | 100         | kHz        | Sosc (Note 4)                           |  |

| OS20          | Tosc          | Tosc = 1/Fosc = Tcy (Note 2)                                                                                     | _                                                                                                                                                                                                                                         | —                      | _           | _          | See parameter<br>OS10 for Fosc<br>value |  |

| OS30          | TosL,<br>TosH | External Clock In (OSC1)<br>High or Low Time                                                                     | 0.45 x Tosc                                                                                                                                                                                                                               |                        | _           | ns         | EC (Note 4)                             |  |

| OS31          | TosR,<br>TosF | External Clock In (OSC1)<br>Rise or Fall Time                                                                    | —                                                                                                                                                                                                                                         | _                      | 0.05 x Tosc | ns         | EC (Note 4)                             |  |

| OS40          | Tost          | Oscillator Start-up Timer Period<br>(Only applies to HS, HSPLL,<br>XT, XTPLL and Sosc Clock<br>Oscillator modes) | _                                                                                                                                                                                                                                         | 1024                   | _           | Tosc       | (Note 4)                                |  |

| OS41          | TFSCM         | Primary Clock Fail Safe<br>Time-out Period                                                                       | —                                                                                                                                                                                                                                         | 2                      | —           | ms         | (Note 4)                                |  |

| OS42          | Gм            | External Oscillator<br>Transconductance (Primary<br>Oscillator only)                                             | _                                                                                                                                                                                                                                         | 12                     | _           | mA/V       | VDD = 3.3V,<br>TA = +25°C<br>(Note 4)   |  |

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are characterized but are not tested.

- 2: Instruction cycle period (TCY) equals the input oscillator time base period. All specified values are based on characterization data for that particular oscillator type under standard operating conditions with the device executing code. Exceeding these specified limits may result in an unstable oscillator operation and/or higher than expected current consumption. All devices are tested to operate at "min." values with an external clock applied to the OSC1/CLKI pin.

- **3:** PLL input requirements: 4 MHz  $\leq$  FPLLIN  $\leq$  5 MHz (use PLL prescaler to reduce Fosc). This parameter is characterized, but tested at 10 MHz only at manufacturing.

- 4: This parameter is characterized, but not tested in manufacturing.

## TABLE 31-25: TIMER2, 3, 4, 5 EXTERNAL CLOCK TIMING REQUIREMENTS

| AC CHARACTERISTICS |           |                          |                                | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                                              |   |     |                                     |                       |  |

|--------------------|-----------|--------------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------|---|-----|-------------------------------------|-----------------------|--|

| Param.<br>No.      | Symbol    | Cha                      | racteristic                    | s <sup>(1)</sup> Min. Max. Units Con                                                                                                                                                                                                                                                                                                                    |                                              |   |     | Condit                              | itions                |  |

| TB10               | ТтхН      | TxCK<br>High Time        | Synchrono<br>prescaler         | ous, with                                                                                                                                                                                                                                                                                                                                               | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns            | — | ns  | Must also meet<br>parameter<br>TB15 | value<br>(1, 2, 4, 8, |  |

| TB11               | ΤτxL      | TxCK<br>Low Time         | Synchronous, with<br>prescaler |                                                                                                                                                                                                                                                                                                                                                         | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns            | — | ns  | Must also meet<br>parameter<br>TB15 | 16, 32, 64,<br>256)   |  |

| TB15               | ΤτχΡ      | TxCK<br>Input            | Synchronous, with<br>prescaler |                                                                                                                                                                                                                                                                                                                                                         | [(Greater of [(25 ns or<br>2 TPB)/N] + 30 ns | — | ns  | VDD > 2.7V                          |                       |  |

|                    |           | Period                   |                                |                                                                                                                                                                                                                                                                                                                                                         | [(Greater of [(25 ns or<br>2 TPB)/N] + 50 ns | — | ns  | VDD < 2.7V                          |                       |  |

| TB20               | TCKEXTMRL | Delay from<br>Clock Edge |                                |                                                                                                                                                                                                                                                                                                                                                         | _                                            | 1 | Трв | _                                   |                       |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

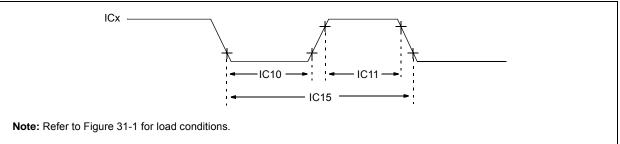

# FIGURE 31-7: INPUT CAPTURE (CAPx) TIMING CHARACTERISTICS

## TABLE 31-26: INPUT CAPTURE MODULE TIMING REQUIREMENTS

| AC CHARACTERISTICS |        |                     | (unless oth                               | perating Conditions: 2.3V<br>erwise stated)<br>mperature $0^{\circ}C \le TA \le +70$<br>$-40^{\circ}C \le TA \le +$<br>$-40^{\circ}C \le TA \le +$ | °C for C<br>85°C for | Industri | al                                      |                                  |  |

|--------------------|--------|---------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|----------|-----------------------------------------|----------------------------------|--|

| Param.<br>No.      | Symbol | Charac              | cteristics <sup>(1)</sup> Min. Max. Units |                                                                                                                                                    |                      |          | Con                                     | Conditions                       |  |

| IC10               | TccL   | ICx Input Low Time  |                                           | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                                                  | _                    | ns       | Must also<br>meet<br>parameter<br>IC15. | N = prescale<br>value (1, 4, 16) |  |

| IC11               | ТссН   | ICx Input High Time |                                           | [(12.5 ns or 1 ТРВ)/N]<br>+ 25 ns                                                                                                                  | _                    | ns       | Must also<br>meet<br>parameter<br>IC15. |                                  |  |

| IC15               | TCCP   | ICx Input           | t Period                                  | [(25 ns or 2 Трв)/N]<br>+ 50 ns                                                                                                                    |                      | ns       |                                         |                                  |  |

**Note 1:** These parameters are characterized, but not tested in manufacturing.

# PIC32MX330/350/370/430/450/470

# 33.1 Package Marking Information (Continued)

64-Lead QFN (9x9x0.9 mm) with 5.40x5.40 Exposed Pad

| <b>2</b>    |

|-------------|

| XXXXXXXXXXX |

| XXXXXXXXXXX |

| XXXXXXXXXXX |

| YYWWNNN     |

|             |

64-Lead QFN (9x9x0.9 mm) with 4.7x4.7 Exposed Pad

| Example                  |  |  |  |  |  |  |

|--------------------------|--|--|--|--|--|--|

| © <b>™</b>               |  |  |  |  |  |  |

| PIC32MX330F<br>064H-I/RG |  |  |  |  |  |  |

| e3                       |  |  |  |  |  |  |

| 0510017                  |  |  |  |  |  |  |

124-Lead VTLA (9x9x0.9 mm)

C XXXXXXXXXXX XXXXXXXXXX XXXXXXXXXX YYWWNNN Example

| Legend | : XXX                                         | Customer-specific information                                                                       |  |  |  |  |  |

|--------|-----------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|

| •      | Y Year code (last digit of calendar year)     |                                                                                                     |  |  |  |  |  |

|        | YY                                            | Year code (last 2 digits of calendar year)                                                          |  |  |  |  |  |

|        | WW Week code (week of January 1 is week '01') |                                                                                                     |  |  |  |  |  |

|        | NNN                                           | Alphanumeric traceability code                                                                      |  |  |  |  |  |

|        |                                               | Pb-free JEDEC designator for Matte Tin (Sn)                                                         |  |  |  |  |  |

|        | *                                             | This package is Pb-free. The Pb-free JEDEC designator (e3)                                          |  |  |  |  |  |

|        |                                               | can be found on the outer packaging for this package. $\smile$                                      |  |  |  |  |  |

| Note:  | In the eve                                    | nt the full Microchip part number cannot be marked on one line, it will                             |  |  |  |  |  |

|        |                                               | d over to the next line, thus limiting the number of available s for customer-specific information. |  |  |  |  |  |

# Revision D (March 2015)

This revision includes the following updates, as listed in Table A-3.

## TABLE A-3: MAJOR SECTION UPDATES

| Section                                                                                                                               | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|