Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 49                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f128ht-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX330/350/370/430/450/470

### 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

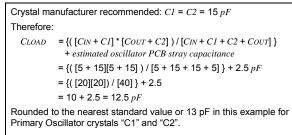

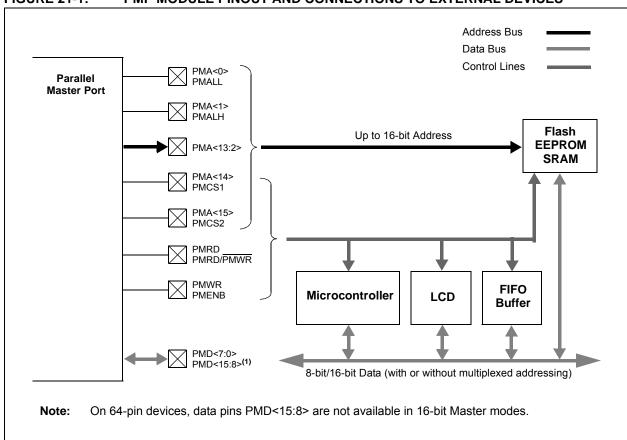

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

### EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator. The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

- Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

#### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

|              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | NVMDA             | TA<31:24>         |                   |                  |                  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | NVMDA             | TA<23:16>         |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | NVMDA             | TA<15:8>          |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | NVMD              | ATA<7:0>          |                   |                  |                  |

#### REGISTER 5-4: NVMDATA: FLASH PROGRAM DATA REGISTER

#### Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

Note: The bits in this register are only reset by a Power-on Reset (POR).

# REGISTER 5-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | NVMSRCA           | DDR<31:24>        | >                 |                  |                  |

| 00.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | NVMSRCA           | DDR<23:16>        | >                 |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         |                   |                   |                   | NVMSRC/           | ADDR<15:8>        |                   |                  |                  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | NVMSRC            | ADDR<7:0>         |                   |                  |                  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

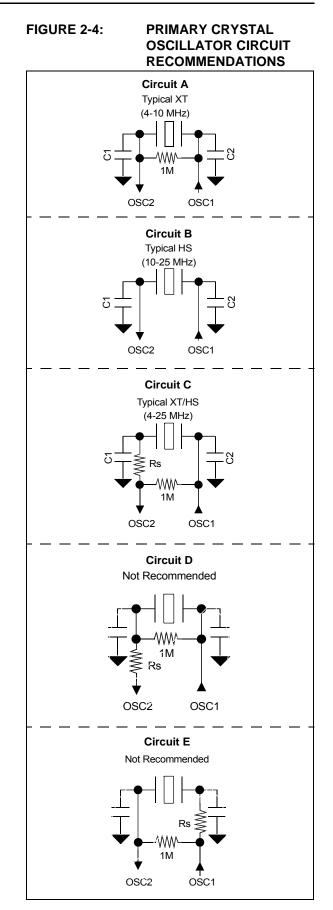

# 10.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32 (such as Peripheral Bus (PBUS) devices: SPI, UART, PMP, etc.) or memory itself.

Following are some of the key features of the DMA controller module:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

# FIGURE 10-1: DMA BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                                        | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------------------------------------|-----------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                                                     | U-0                   |

| 31:24        |                     | —                 | _                 | _                 |                   | _                 | -                                                       | —                     |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                                                     | U-0                   |

| 23:16        | —                   | —                 | _                 | _                 | _                 | —                 | 2 25/17/9/1<br>U-0<br>U-0<br>U-0<br>U-0<br>U-0<br>R/W-0 | —                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                                                     | R/W-0                 |

| 15:8         | CHBUSY              | —                 | _                 | _                 | _                 | _                 | _                                                       | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0                                                   | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | 25/17/9/1<br>U-0<br>U-0<br>U-0<br>U-0<br>U-0<br>R/W-0   | RI<1:0>               |

#### REGISTER 10-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14-9 Unimplemented: Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

#### bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 = Channel is disabled

#### bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

#### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

0 = Channel is disabled on block transfer complete

#### bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

- bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

# REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN BD banks

- 0 = Even/Odd buffer pointers not being Reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set the RESUME bit for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 |                   |                   | —                 |                   | _                 |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 |                   |                   | —                 | -                 | _                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | _                 | _                 | _                 | —                 | _                 | _                 | -                | —                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | LSPDEN            |                   |                   | D                 | EVADDR<6:0        | >                 |                  |                  |

# REGISTER 11-12: U1ADDR: USB ADDRESS REGISTER

# Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7 **LSPDEN:** Low Speed Enable Indicator bit

1 = Next token command to be executed at Low Speed

0 = Next token command to be executed at Full Speed

bit 6-0 **DEVADDR<6:0>:** 7-bit USB Device Address bits

|              |                   |                   |                   | HOMBER E          |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | —                 | _                 | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | _                 | —                 | _                 | —                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 | -                 | -                 | —                 | -                 | —                | —                |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   | FRML              | <7:0>             |                   |                  |                  |

#### REGISTER 11-13: U1FRML: USB FRAME NUMBER LOW REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **FRML<7:0>:** The 11-bit Frame Number Lower bits

The register bits are updated with the current frame number whenever a SOF TOKEN is received.

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | _                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                 |                   |                   |                  | -                |

| 23:16        | U-0               | U-0               | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                 |                   |                   |                  | —                |

| 15:8         | U-0               | U-0               | 30/22/14/6         29/21/13/5         28/20/12/4         27/19/11/3         26/18/10/2         25/17/9/1           U-0         U-0         U-0         U-0         U-0         U-0                   U-0         U-0         U-0         U-0         U-0                    RW-0         U-0         RW-0         RW-0         RW-0         RW-0 <td>U-0</td> | U-0               |                   |                   |                  |                  |

| 15.0         |                   | _                 | -                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | _                 |                   |                   |                  | —                |

| 7:0          | R/W-0             | R/W-0             | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | LSPD              | RETRYDIS          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

#### REGISTER 11-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a low-speed device is enabled

- 0 = Direct connection to a low-speed device is disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NAKed transactions is disabled

- 0 = Retry NAKed transactions is enabled; retry done in hardware

#### bit 5 Unimplemented: Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers; TX and RX transfers also allowed Otherwise, this bit is ignored.

- bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive is enabled

- 0 = Endpoint n receive is disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit is enabled

- 0 = Endpoint n transmit is disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint Handshake is enabled

- 0 = Endpoint Handshake is disabled (typically used for isochronous endpoints)

# 12.4 Control Registers

|                             |                                 | PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY |               |               |       |       |       |               |              |      | ND FICS      |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-------------------------------------------------------------------------------------|---------------|---------------|-------|-------|-------|---------------|--------------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess (                       |                                 | Ð                                                                                   |               |               |       |       |       |               |              | Bi   | ts           |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range                                                                           | 31/15         | 30/14         | 29/13 | 28/12 | 27/11 | 26/10         | 25/9         | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6000                        | ANSELA                          | 31:16                                                                               | —             | —             | —     | —     | _     | —             | —            | _    | —            | —            | —            | _            | —            | —            | —            | _            | 0000          |

| 0000                        | ANOLLA                          | 15:0                                                                                | —             | —             | _     | —     | _     | ANSELA10      | ANSELA9      | _    |              | —            | _            | _            | _            |              | _            | _            | 0060          |

| 6010                        | TRISA                           | 31:16                                                                               | —             | —             | _     | —     | _     | —             | —            | _    | —            | —            | _            | _            | _            | —            | _            |              | 0000          |

|                             |                                 | 15:0                                                                                | TRISA15       | TRISA14       | —     | —     | _     | TRISA10       | TRISA9       | —    | TRISA7       | TRISA6       | TRISA5       | TRISA4       | TRISA3       | TRISA2       | TRISA1       | TRISA0       | xxxx          |

| 6020                        | PORTA                           | 31:16                                                                               | —             | —             | _     | —     |       | —             |              |      |              | —            | _            | _            | _            |              | _            | —            | 0000          |

|                             | _                               | 15:0                                                                                | RA15          | RA14          | —     | —     | —     | RA10          | RA9          | —    | RA7          | RA6          | RA5          | RA4          | RA3          | RA2          | RA1          | RA0          | xxxx          |

| 6030                        | LATA                            | 31:16                                                                               |               |               | —     | —     | _     | _             |              | _    |              |              | _            |              | —            |              | _            | _            | 0000          |

|                             |                                 | 15:0                                                                                | LATA15        | LATA14        | —     | —     | _     | LATA10        | LATA9        | _    | LATA7        | LATA6        | LATA5        | LATA4        | LATA3        | LATA2        | LATA1        | LATA0        | xxxx          |

| 6040                        | ODCA                            | 31:16                                                                               |               |               | —     | —     | _     | _             |              | _    |              |              | _            |              | —            |              | _            | _            | 0000          |

|                             |                                 | 15:0                                                                                | ODCA15        | ODCA14        | _     | —     | _     | ODCA10        | ODCA9        | _    | ODCA7        | ODCA6        | ODCA5        | ODCA4        | ODCA3        | ODCA2        | ODCA1        | ODCA0        | xxxx          |

| 6050                        | CNPUA                           | 31:16                                                                               | —             | —             | _     | —     | _     | —             | —            | _    | —            | —            | —            | _            | —            | —            | —            | —            | 0000          |

|                             |                                 |                                                                                     | CNPUA15       | CNPUA14       |       |       | _     | CNPUA10       | CNPUA9       | _    | CNPUA7       | CNPUA6       | CNPUA5       | CNPUA4       | CNPUA3       | CNPUA2       | CNPUA1       | CNPUA0       | _             |

| 6060                        | CNPDA                           | 31:16                                                                               |               | —             |       | —     |       |               | —            |      |              | —            | —            |              | —            | —            | —            | —            | 0000          |

|                             |                                 |                                                                                     | CNPDA15       | -             | _     | —     | _     | CNPDA10       | CNPDA9       |      | CNPDA7       | CNPDA6       | CNPDA5       | CNPDA4       | CNPDA3       | CNPDA2       | CNPDA1       | CNPDA0       |               |

| 6070                        | CNCONA                          | 31:16                                                                               | -             |               | -     |       |       | —             | _            |      | _            | —            |              | _            |              | _            |              | _            | 0000          |

|                             |                                 | 15:0                                                                                | ON            |               | SIDL  | —     |       | —             |              |      |              |              |              | _            |              | _            |              | _            | 0000          |

| 6080                        | CNENA                           | 31:16                                                                               |               |               |       |       |       |               |              |      |              |              |              |              |              | -            |              |              | 0000          |

|                             |                                 | 15:0                                                                                | CNIEA15       |               |       |       |       | CNIEA10       | CNIEA9       |      | CNIEA7       | CNIEA6       | CNIEA5       | CNIEA4       | CNIEA3       | CNIEA2       | CNIEA1       | CNIEA0       | XXXX          |

| 6090                        | CNSTATA                         | 31:16                                                                               |               |               |       | _     | _     |               |              |      |              |              |              |              |              |              |              |              | 0000          |

| 0000                        | CHOININ                         | 15:0                                                                                | CN<br>STATA15 | CN<br>STATA14 | -     | —     | —     | CN<br>STATA10 | CN<br>STATA9 |      | CN<br>STATA7 | CN<br>STATA6 | CN<br>STATA5 | CN<br>STATA4 | CN<br>STATA3 | CN<br>STATA2 | CN<br>STATA1 | CN<br>STATA0 | xxxx          |

# TABLE 12-3:PORTA REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,<br/>PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

|                             |                                 | C         | ONLY  |       |               |               |       |       |      |              |              |        |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|---------------|---------------|-------|-------|------|--------------|--------------|--------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                         |                                 |           |       |       |               |               |       |       |      | Bi           | ts           |        |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13         | 28/12         | 27/11 | 26/10 | 25/9 | 24/8         | 23/7         | 22/6   | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6510                        | TRISF                           | 31:16     | _     | _     | _             |               | _     |       | _    |              |              |        | _            |              | -            |              | _            |              | 0000          |

| 0310                        | TRIST                           | 15:0      | _     | —     | TRISF13       | TRISF12       | —     | _     | —    | TRISF8       | TRISF7       | TRISF6 | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | xxxx          |

| 6520                        | PORTF                           | 31:16     | —     | —     | —             | _             | _     | -     | —    | -            | -            | -      | —            | _            | _            | -            | _            | -            | 0000          |

| 0520                        | TOKI                            | 15:0      | —     | —     | RF13          | RF12          | _     | -     | —    | RF8          | RF7          | RF6    | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | xxxx          |

| 6530                        | LATF                            | 31:16     | —     | —     | —             | _             | _     | -     | —    | -            | -            | -      | —            | _            | _            | -            | _            | -            | 0000          |

| 0000                        | LATI                            | 15:0      | —     | —     | LATF13        | LATF12        | _     | -     | —    | LATF8        | LATF7        | LATF6  | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | _     |       | —             | —             | —     | _     |      | _            | _            |        | —            | _            | _            | _            |              |              | 0000          |

| 0040                        | 000                             | 15:0      | _     |       | ODCF13        | ODCF12        | —     | _     |      | ODCF8        | ODCF7        | ODCF6  | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | xxxx          |

| 6550                        | CNPUF                           | 31:16     | —     | —     | —             | —             | —     | —     |      | —            | —            | _      | —            | —            | —            | —            | —            | _            | 0000          |

| 0000                        |                                 | 15:0      | —     | —     | CNPUF13       | CNPUF12       | —     | —     | —    | CNPUF8       | CNPUF7       | CNPUF6 | CNPUF5       | CNPUF4       | CNPDF3       | CNPUF2       | CNPUF1       | CNPUF0       | xxxx          |

| 6560                        | CNPDF                           | 31:16     | —     | —     | —             | —             | —     | _     | —    | —            | _            | —      | —            | _            | —            | _            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | —     | CNPDF13       | CNPDF12       | —     | -     | —    | CNPDF8       | CNPDF7       | CNPDF6 | CNPDF5       | CNPDF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | xxxx          |

| 6570                        | CNCONF                          | 31:16     | —     | —     | —             | —             | —     | -     | —    | -            | -            | _      | —            | _            | _            | -            | —            | —            | 0000          |

|                             |                                 | 15:0      | ON    | —     | SIDL          | —             | —     | -     | —    | -            | -            | -      | —            | _            | _            | -            | —            | —            | 0000          |

| 6580                        | CNENF                           | 31:16     | —     | —     | —             | —             | —     | -     | —    | -            | -            | -      | —            | _            | -            | -            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | —     | CNIEF13       | CNIEF12       | —     | -     | —    | CNIEF8       | CNIEF7       | -      | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | xxxx          |

|                             |                                 | 31:16     | —     | —     | —             | —             | —     | -     | —    | -            | -            | _      | —            | _            | —            | -            | —            | —            | 0000          |

| 6590                        | CNSTATF                         | 15:0      | _     | —     | CN<br>STATF13 | CN<br>STATF12 | _     | _     | —    | CN<br>STATF8 | CN<br>STATF7 | _      | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | xxxx          |

TABLE 12-11: PORTF REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, AND PIC32MX370F512L DEVICES

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# TABLE 12-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP

| SS                          |                       |               |       |       |       |       |       |       |      | Bi   | its  |      |      |      |      |           |             |      |            |

|-----------------------------|-----------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-----------|-------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2      | 17/1        | 16/0 | All Resets |

| FB38                        | RPA14R <sup>(1)</sup> | 31:16<br>15:0 | _     |       |       |       |       |       | —    |      |      | —    | —    |      | -    | —<br>RPA1 | —<br>4<3:0> | —    | 0000       |

| FB3C                        | RPA15R <sup>(1)</sup> | 31:16<br>15:0 | _     |       | _     |       |       |       |      |      |      | _    |      | _    | _    | -         |             | _    | 0000       |

| FB40                        | RPB0R                 | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      |      |      | —    | RPB0      |             | _    | 0000       |

| FB44                        | RPB1R                 | 31:16<br>15:0 |       |       | _     |       |       |       |      |      |      |      |      |      | —    | RPB1      |             | —    | 0000       |

| FB48                        | RPB2R                 | 31:16         | —     | _     |       | _     |       | _     | _    | _    | _    | _    | _    | _    | —    |           | _           | —    | 0000       |

| FB4C                        | RPB3R                 | 15:0<br>31:16 | _     |       | _     | _     |       | _     | _    | _    | _    | _    |      | _    | _    | RPB2      |             | _    | 0000       |

| FB54                        | RPB5R                 | 15:0<br>31:16 | _     | _     |       |       |       | _     |      |      |      | _    |      | _    | _    | RPB3      |             | _    | 0000       |

| FB58                        | RPB6R                 | 15:0<br>31:16 | _     |       |       | -     |       | _     |      | -    |      | _    |      |      | _    | RPB5      | _           | —    | 0000       |

| FB5C                        | RPB7R                 | 15:0<br>31:16 | _     |       | _     |       |       |       |      |      |      |      |      |      | _    | RPB6      |             | _    | 0000       |

| FB60                        | RPB8R                 | 15:0<br>31:16 |       |       |       |       |       |       |      |      |      |      |      |      |      | RPB7      | /<3:0>      | —    | 0000       |

|                             |                       | 15:0<br>31:16 | _     |       |       |       |       |       |      |      |      |      |      |      | _    | RPB8      |             | _    | 0000       |

| FB64                        | RPB9R                 | 15:0<br>31:16 | _     | _     |       |       |       | _     |      |      |      |      |      | -    |      | RPB9      | <3:0>       | _    | 0000       |

| FB68                        | RPB10R                | 15:0<br>31:16 | _     |       |       |       |       |       |      |      |      |      |      |      |      | RPB1      | 0<3:0>      | ·    | 0000       |

| FB78                        | RPB14R                | 15:0<br>31:16 | _     |       |       |       |       |       |      |      |      |      |      |      |      | RPB1      | 4<3:0>      |      | 0000       |

| FB7C                        | RPB15R                | 15:0          | _     | _     |       | _     |       |       |      |      |      |      |      |      |      | RPB1      | 5<3:0>      |      | 0000       |

| FB84                        | RPC1R <sup>(1)</sup>  | 31:16<br>15:0 | _     |       | _     | _     |       |       |      | _    |      |      |      | _    | _    | RPC1      |             | _    | 0000       |

| FB88                        | RPC2R <sup>(1)</sup>  | 31:16<br>15:0 | _     |       | _     | -     | -     |       |      | -    | -    |      |      |      | —    | RPC2      | <br>2<3:0>  |      | 0000       |

| FB8C                        | RPC3R <sup>(1)</sup>  | 31:16<br>15:0 |       |       |       |       | _     | _     |      |      |      |      |      |      | _    | —<br>RPC3 | —<br>3<3:0> | —    | 0000       |

PIC32MX330/350/370/430/450/470

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend: Note 1:

This register is not available on 64-pin devices.

This register is only available on devices without a USB module. 2:

This register is not available on 64-pin devices with a USB module. 3:

# REGISTER 18-3: SPIxSTAT: SPI STATUS REGISTER (CONTINUED)

- bit 3 SPITBE: SPI Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB is empty

- 0 = Transmit buffer, SPIxTXB is not empty

Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR.

Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

### bit 2 Unimplemented: Read as '0'

bit 1 SPITBF: SPI Transmit Buffer Full Status bit

1 = Transmit not yet started, SPITXB is full

0 = Transmit buffer is not full

#### Standard Buffer Mode:

Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR.

#### Enhanced Buffer Mode:

Set when CWPTR + 1 = SRPTR; cleared otherwise

#### bit 0 SPIRBF: SPI Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

#### Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 31:24        | _                 | —                 | _                 | _                 | _                 | _                 | _                | ADM_EN           |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | ADDR<             | <7:0>             |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-1              |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0            | R-0              |

| 7:0          | URXISE            | L<1:0>            | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |

### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

# Legend:

| Logonal           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-25 Unimplemented: Read as '0'

- bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

- 1 = Automatic Address Detect mode is enabled

- 0 = Automatic Address Detect mode is disabled

- bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

#### bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

- 11 = Reserved, do not use

- 10 = Interrupt is generated and asserted while the transmit buffer is empty

- 01 = Interrupt is generated and asserted when all characters have been transmitted

- 00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

#### bit 13 UTXINV: Transmit Polarity Inversion bit

If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

#### If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

- 1 = IrDA encoded UxTX Idle state is '1'

- 0 = IrDA encoded UxTX Idle state is '0'

#### bit 12 URXEN: Receiver Enable bit

- 1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by the port.

#### bit 11 UTXBRK: Transmit Break bit

- 1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Break transmission is disabled or completed

- bit 10 UTXEN: Transmit Enable bit

- 1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by the port.

#### bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

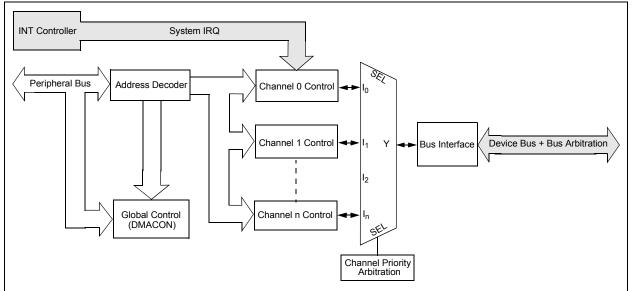

# 21.0 PARALLEL MASTER PORT (PMP)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Parallel Master Port (PMP)" (DS60001128), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable.

The following are key features of the PMP module:

- 8-bit,16-bit interface

- · Up to 16 programmable address lines

- · Up to two Chip Select lines

- Programmable strobe options

- Individual read and write strobes, or

- Read/write strobe with enable strobe

- Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- · Programmable polarity on control signals

- Parallel Slave Port support

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- · Programmable Wait states

- Operate during CPU Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

- Freeze option for in-circuit debugging

**Note:** On 64-pin devices, data pins PMD<15:8> are not available in 16-bit Master modes.

# FIGURE 21-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

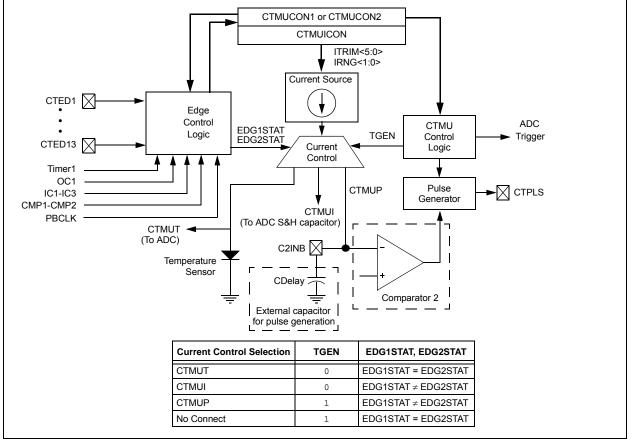

# 26.0 CHARGE TIME MEASUREMENT UNIT (CTMU)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Charge Time Measurement Unit (CTMU) is a flexible analog module that has a configurable current source with a digital configuration circuit built around it. The CTMU can be used for differential time measurement between pulse sources and can be used for generating an asynchronous pulse. By working with other on-chip analog modules, the CTMU can be used for high resolution time measurement, measure capacitance, measure relative changes in capacitance or generate output pulses with a specific time delay. The CTMU is ideal for interfacing with capacitive-based sensors.

FIGURE 26-1: CTMU BLOCK DIAGRAM

The CTMU module includes the following key features:

- Up to 13 channels available for capacitive or time measurement input

- · On-chip precision current source

- 16-edge input trigger sources

- · Selection of edge or level-sensitive inputs

- Polarity control for each edge source

- Control of edge sequence

- Control of response to edges

- · High precision time measurement

- Time delay of external or internal signal asynchronous to system clock

- · Integrated temperature sensing diode

- · Control of current source during auto-sampling

- Four current source ranges

- · Time measurement resolution of one nanosecond

A block diagram of the CTMU is shown in Figure 26-1.

# REGISTER 28-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

- bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output is disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

- bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 **Reserved:** Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | r-1                   | r-1               | r-1               | r-1               | r-1               | r-1               | r-1              | r-1              |

| 31:24        |                       | _                 | _                 | _                 | _                 | —                 | _                | —                |

| 00.40        | r-1                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |

| 23:16        |                       | —                 | _                 | _                 | _                 | FF                | PLLODIV<2:0      | )>               |

| 45.0         | R/P                   | r-1               | r-1               | r-1               | r-1               | R/P               | R/P              | R/P              |

| 15:8         | UPLLEN <sup>(1)</sup> | _                 | _                 | _                 | _                 | UP                | LLIDIV<2:0>      | (1)              |

| 7.0          | r-1                   | R/P-1             | R/P               | R/P-1             | r-1               | R/P               | R/P              | R/P              |

| 7:0          | — FPLLMUL<2:0>        |                   |                   |                   | _                 | F                 | PLLIDIV<2:0      | >                |

#### **DEVCFG2: DEVICE CONFIGURATION WORD 2 REGISTER 28-3:**

| Legend:           | r = Reserved bit | P = Programmable bit      |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-19 Reserved: Write '1'

bit 15

bit 7

bit 18-16 FPLLODIV<2:0>: Default PLL Output Divisor bits

- 111 = PLL output divided by 256 110 = PLL output divided by 64 101 = PLL output divided by 32 100 = PLL output divided by 16 011 = PLL output divided by 8 010 = PLL output divided by 4 001 = PLL output divided by 2 000 = PLL output divided by 1 UPLLEN: USB PLL Enable bit<sup>(1)</sup> 1 = Disable and bypass USB PLL 0 = Enable USB PLL bit 14-11 Reserved: Write '1' bit 10-8 UPLLIDIV<2:0>: USB PLL Input Divider bits<sup>(1)</sup> 111 = 12x divider 110 = 10x divider 101 = 6x divider100 = 5x divider 011 = 4x divider 010 = 3x divider 001 = 2x divider 000 = 1x dividerReserved: Write '1' bit 6-4 FPLLMUL<2:0>: PLL Multiplier bits 111 = 24x multiplier 110 = 21x multiplier 101 = 20x multiplier 100 = 19x multiplier 011 = 18x multiplier 010 = 17x multiplier 001 = 16x multiplier 000 = 15x multiplier

- bit 3 Reserved: Write '1'

Note 1: This bit is available on PIC32MX4XX devices only.

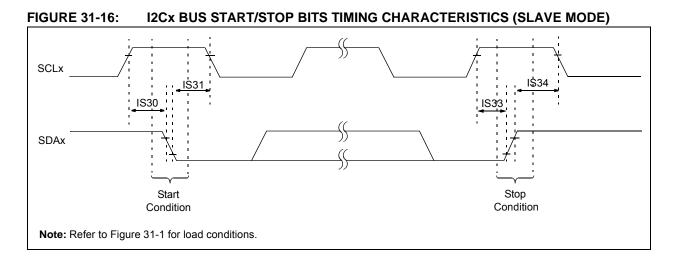

# TABLE 31-33: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE) (CONTINUED)

| AC CHA        | RACTER  | ISTICS           |                        | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |       |                                        |  |  |  |  |

|---------------|---------|------------------|------------------------|------------------------------------------------------|------|-------|----------------------------------------|--|--|--|--|

| Param.<br>No. | Symbol  | Charac           | teristics              | Min. <sup>(1)</sup>                                  | Max. | Units | Conditions                             |  |  |  |  |

| IM34          | THD:STO | Stop Condition   | 100 kHz mode           | Трв * (BRG + 2)                                      |      | ns    | —                                      |  |  |  |  |

|               |         | Hold Time        | 400 kHz mode           | Трв * (BRG + 2)                                      | —    | ns    |                                        |  |  |  |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | Трв * (BRG + 2)                                      | —    | ns    |                                        |  |  |  |  |

| IM40          | TAA:SCL | Output Valid     | 100 kHz mode           | —                                                    | 3500 | ns    | —                                      |  |  |  |  |

|               |         | from Clock       | 400 kHz mode           | —                                                    | 1000 | ns    | —                                      |  |  |  |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | —                                                    | 350  | ns    | —                                      |  |  |  |  |

| IM45          | TBF:SDA | Bus Free Time    | 100 kHz mode           | 4.7                                                  | —    | μS    | The amount of time the                 |  |  |  |  |

|               |         |                  | 400 kHz mode           | 1.3                                                  | —    | μS    | bus must be free                       |  |  |  |  |

|               |         |                  | 1 MHz mode<br>(Note 2) | 0.5                                                  | —    | μS    | before a new<br>transmission can start |  |  |  |  |

| IM50          | Св      | Bus Capacitive L | oading                 | —                                                    | 400  | pF    | —                                      |  |  |  |  |

| IM51          | Tpgd    | Pulse Gobbler D  | elay                   | 52                                                   | 312  | ns    | See Note 3                             |  |  |  |  |

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

# PIC32MX330/350/370/430/450/470

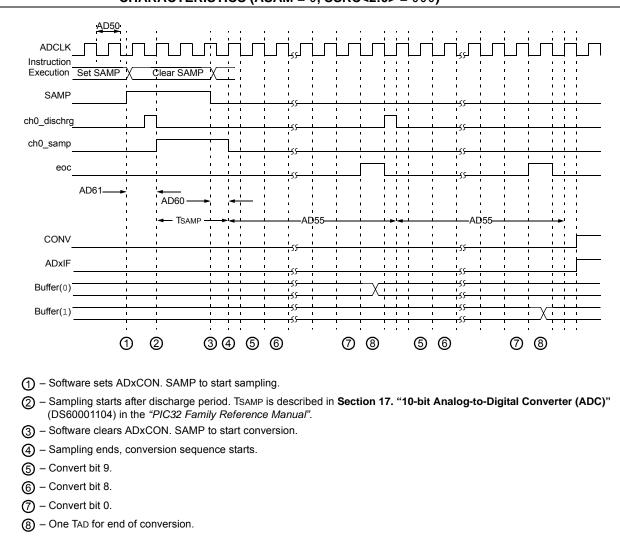

# FIGURE 31-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

# **Revision E (October 2015)**

This revision includes the following updates, as listed in Table A-4.

# TABLE A-4: MAJOR SECTION UPDATES

| Section                                                  | Update Description                                                             |

|----------------------------------------------------------|--------------------------------------------------------------------------------|

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs" | Section 2.10 "Sosc Design Recommendations" was removed.                        |

| 31.0 "Electrical<br>Characteristics"                     | The Power-Down Current (IPD) DC Characteristics were updated (see Table 31-7). |

# **Revision F (September 2016)**

This revision includes the following updates, as listed in Table A-5.

# TABLE A-5: MAJOR SECTION UPDATES

| Section                                                    | Update Description                                                                                                                                                                                             |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up<br>to 512 KB Flash and 128 KB | The PIC32MX450F128HB and PIC32MX470F512LB devices and Note 4 were added to the family features table (see Table 1).                                                                                            |

| SRAM) with Audio/                                          | Note 2 in the 64-pin device pin table was updated (see Table 2).                                                                                                                                               |

| Graphics/Touch (HMI), USB,<br>and Advanced Analog"         | Note 2 in the 64-pin device pin table was updated and Note 4 was removed (see Table 3).                                                                                                                        |

|                                                            | Note 2 and Note 3 in the 100-pin device pin table was updated (see Table 4).                                                                                                                                   |

|                                                            | Note 3 in the 124-pin device pin table was updated (see Table 6).                                                                                                                                              |

|                                                            | Note 2 in the 124-pin device pin table was updated (see Table 7).                                                                                                                                              |

|                                                            | RPF3 was removed from USB devices (see Table 3, Table 5, and Table 7).                                                                                                                                         |

| 1.0 "Device Overview"                                      | The Pinout I/O Descriptions for pins $\overline{\text{U5CTS}}$ , $\overline{\text{U5RTS}}$ , $\overline{\text{U5RX}}$ , and $\overline{\text{U5TX}}$ in 64-pin QFN/TQFP packages were updated (see Table 1-1). |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"   | 2.10 "EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations" was added.                                                                                                                     |

| 8.0 "Oscillator                                            | The Clock Diagram was updated (see Figure 8-1).                                                                                                                                                                |

| Configuration"                                             | The Center Frequency values in the TUN<5:0> bits (OSCTUN<5:0>) were updated (see Register 8-2).                                                                                                                |

| 12.0 "I/O Ports"                                           | Note references in the Input Pin Selection table were updated (see Table 12-1).                                                                                                                                |

|                                                            | Note references in the Output Pin Selection table were updated (see Table 12-2).                                                                                                                               |

|                                                            | PORTF Register Maps were updated (see Table 12-11 and Table 12-3).                                                                                                                                             |

|                                                            | Note 1 was added to the Peripheral Pin Select Input Register Map (see Table 12-17).                                                                                                                            |

| 31.0 "Electrical                                           | The conditions for parameter DI60b (IICH) were updated (see Table 31-8).                                                                                                                                       |

| Characteristics"                                           | Parameter DO50a (Csosc) was removed.                                                                                                                                                                           |