Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                   |                                                                                 |

|---------------------------|---------------------------------------------------------------------------------|

| Product Status            | Active                                                                          |

| Core Processor            | MIPS32® M4K™                                                                    |

| Core Size                 | 32-Bit Single-Core                                                              |

| Speed                     | 80MHz                                                                           |

| Connectivity              | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals               | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| lumber of I/O             | 49                                                                              |

| Program Memory Size       | 128KB (128K x 8)                                                                |

| rogram Memory Type        | FLASH                                                                           |

| EPROM Size                | -                                                                               |

| AM Size                   | 32K x 8                                                                         |

| oltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| ata Converters            | A/D 28x10b                                                                      |

| Oscillator Type           | Internal                                                                        |

| perating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Nounting Type             | Surface Mount                                                                   |

| ackage / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package   | 64-QFN (9x9)                                                                    |

| urchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f128ht-v-rg |

TABLE 1: PIC32MX330/350/370/430/450/470 CONTROLLER FAMILY FEATURES

|                                       |            |              | 0/330/                             |                  |                 | nappab                                | le Pe | ripher               | als                                | •                            |                    |                     |      |     |     |      |                                          |          |      |       |

|---------------------------------------|------------|--------------|------------------------------------|------------------|-----------------|---------------------------------------|-------|----------------------|------------------------------------|------------------------------|--------------------|---------------------|------|-----|-----|------|------------------------------------------|----------|------|-------|

| Device                                | Pins       | Packages     | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers/Capture/Compare <sup>(2)</sup> | UART  | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Analog Comparators | USB On-The-Go (OTG) | СТМU | l²C | PMP | RTCC | DMA Channels<br>(Programmable/Dedicated) | I/O Pins | JTAG | Trace |

| PIC32MX330F064H                       | 64         | QFN,<br>TQFP | 64+12                              | 16               | 37              | 5/5/5                                 | 4     | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 53       | Υ    | N     |

| PIC32MX330F064L                       | 100<br>124 | TQFP<br>VTLA | 64+12                              | 16               | 54              | 5/5/5                                 | 5     | 2/2                  | 5                                  | 28                           | 2                  | N                   | Υ    | 2   | Y   | Y    | 4/0                                      | 85       | Υ    | Υ     |

| PIC32MX350F128H                       | 64         | QFN,<br>TQFP | 128+12                             | 32               | 37              | 5/5/5                                 | 4     | 2/2                  | 5                                  | 28                           | 2                  | N                   | Υ    | 2   | Υ   | Υ    | 4/0                                      | 53       | Υ    | N     |

| PIC32MX350F128L                       | 100<br>124 | TQFP<br>VTLA | 128+12                             | 32               | 54              | 5/5/5                                 | 5     | 2/2                  | 5                                  | 28                           | 2                  | N                   | Υ    | 2   | Υ   | Y    | 4/0                                      | 85       | Υ    | Υ     |

| PIC32MX350F256H                       | 64         | QFN,<br>TQFP | 256+12                             | 64               | 37              | 5/5/5                                 | 4     | 2/2                  | 5                                  | 28                           | 2                  | N                   | Υ    | 2   | Y   | Y    | 4/0                                      | 53       | Υ    | N     |

| PIC32MX350F256L                       | 100<br>124 | TQFP<br>VTLA | 256+12                             | 64               | 54              | 5/5/5                                 | 5     | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Υ    | 4/0                                      | 85       | Y    | Υ     |

| PIC32MX370F512H                       | 64         | QFN,<br>TQFP | 512+12                             | 128              | 37              | 5/5/5                                 | 4     | 2/2                  | 5                                  | 28                           | 2                  | N                   | Υ    | 2   | Y   | Y    | 4/0                                      | 53       | Υ    | N     |

| PIC32MX370F512L                       | 100<br>124 | TQFP<br>VTLA | 512+12                             | 128              | 54              | 5/5/5                                 | 5     | 2/2                  | 5                                  | 28                           | 2                  | N                   | Υ    | 2   | Y   | Υ    | 4/0                                      | 85       | Υ    | Υ     |

| PIC32MX430F064H                       | 64         | QFN,<br>TQFP | 64+12                              | 16               | 34              | 5/5/5                                 | 4     | 2/2                  | 5                                  | 28                           | 2                  | Υ                   | Υ    | 2   | Υ   | Υ    | 4/2                                      | 49       | Υ    | N     |

| PIC32MX430F064L                       | 100<br>124 | TQFP<br>VTLA | 64+12                              | 16               | 51              | 5/5/5                                 | 5     | 2/2                  | 5                                  | 28                           | 2                  | Υ                   | Υ    | 2   | Υ   | Y    | 4/2                                      | 81       | Υ    | Υ     |

| PIC32MX450F128H                       | 64         | QFN,<br>TQFP | 128+12                             | 32               | 34              | 5/5/5                                 | 4     | 2/2                  | 5                                  | 28                           | 2                  | Υ                   | Υ    | 2   | Υ   | Υ    | 4/2                                      | 49       | Υ    | N     |

| PIC32MX450F128HB (see <b>Note 4</b> ) | 64         | QFN,<br>TQFP | 128+12                             | 32               | 34              | 5/5/5                                 | 4     | 2/2                  | 5                                  | 28                           | 2                  | Υ                   | Υ    | 2   | Υ   | Υ    | 4/2                                      | 49       | Υ    | N     |

| PIC32MX450F128L                       | 100<br>124 | TQFP<br>VTLA | 128+12                             | 32               | 51              | 5/5/5                                 | 5     | 2/2                  | 5                                  | 28                           | 2                  | Υ                   | Υ    | 2   | Υ   | Υ    | 4/2                                      | 81       | Υ    | Υ     |

| PIC32MX450F256H                       | 64         | QFN,<br>TQFP | 256+12                             | 64               | 34              | 5/5/5                                 | 4     | 2/2                  | 5                                  | 28                           | 2                  | Υ                   | Υ    | 2   | Y   | Υ    | 4/2                                      | 49       | Υ    | N     |

| PIC32MX450F256L                       | 100<br>124 | TQFP<br>VTLA | 256+12                             | 64               | 51              | 5/5/5                                 | 5     | 2/2                  | 5                                  | 28                           | 2                  | Υ                   | Υ    | 2   | Υ   | Υ    | 4/2                                      | 81       | Υ    | Υ     |

| PIC32MX470F512H                       | 64         | QFN,<br>TQFP | 512+12                             | 128              | 34              | 5/5/5                                 | 4     | 2/2                  | 5                                  | 28                           | 2                  | Υ                   | Υ    | 2   | Y   | Υ    | 4/2                                      | 49       | Y    | N     |

| PIC32MX470F512L                       | 100<br>124 | TQFP<br>VTLA | 512+12                             | 128              | 51              | 5/5/5                                 | 5     | 2/2                  | 5                                  | 28                           | 2                  | Υ                   | Υ    | 2   | Y   | Υ    | 4/2                                      | 81       | Y    | Υ     |

| PIC32MX470F512LB (see Note 4)         | 100<br>124 | TQFP<br>VTLA | 512+12                             |                  | 51              | 5/5/5                                 | 5     | 2/2                  | 5                                  | 28                           | 2                  | Υ                   | Y    | 2   | Y   | Y    | 4/2                                      | 81       | Y    | Υ     |

Note 1: All devices feature 12 KB of Boot Flash memory.

**<sup>2:</sup>** Four out of five timers are remappable.

**<sup>3:</sup>** Four out of five external interrupts are remappable.

<sup>4:</sup> This PIC32 device is targeted to specific audio software packages that are tracked for licensing royalty purposes. All peripherals and electrical characteristics are identical to their corresponding base part numbers

#### TABLE 7: PIN NAMES FOR 124-PIN DEVICES

PIC32MX470F512L

124-PIN VTLA (BOTTOM VIEW)<sup>(1,2,3,4)</sup>

A17

B13

B29

Conductive

Thermal Pad

PIC32MX430F064L

PIC32MX450F128L

PIC32MX450F256L

B1

B56

A51

Α1

Polarity Indicator

A68

| A1  | No Connect                            |

|-----|---------------------------------------|

| A2  | RG15                                  |

| A3  | Vss                                   |

| A4  | AN23/PMD6/RE6                         |

| A5  | RPC1/RC1                              |

| A6  | RPC3/RC3                              |

| A7  | AN16/C1IND/RPG6/SCK2/PMA5/RG6         |

| A8  | AN18/C2IND/RPG8/PMA3/RG8              |

| A9  | AN19/C2INC/RPG9/PMA2/RG9              |

| A10 | VDD                                   |

| A11 | RPE8/RE8                              |

| A12 | AN5/C1INA/RPB5/VBUSON/RB5             |

| A13 | PGED3/AN3/C2INA/RPB3/RB3              |

| A14 | VDD                                   |

| A15 | PGEC1/AN1/RPB1/CTED12/RB1             |

| A16 | No Connect                            |

| A17 | No Connect                            |

| A18 | No Connect                            |

| A19 | No Connect                            |

| A20 | PGEC2/AN6/RPB6/RB6                    |

| A21 | VREF-/CVREF-/PMA7/RA9                 |

| A22 | AVDD                                  |

| A23 | AN8/RPB8/CTED10/RB8                   |

| A24 | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 |

| A25 | Vss                                   |

| A26 | TCK/CTED2/RA1                         |

| A27 | RPF12/RF12                            |

| A28 | AN13/PMA10/RB13                       |

| A29 | AN15/RPB15/OCFB/CTED6/PMA0/RB15       |

| A30 | VDD                                   |

| A31 | RPD15/RD15                            |

| A32 | RPF5/PMA8/RF5                         |

| A33 | No Connect                            |

| A34 | No Connect                            |

| A35 | USBID/RF3                             |

| A36 | RPF2/RF2                              |

| A37 | VBUS                                  |

| !! | lOI               |                                                       |

|----|-------------------|-------------------------------------------------------|

|    | Package<br>Bump # | Full Pin Name                                         |

|    | A38               | D-                                                    |

|    | A39               | SCL2/RA2                                              |

|    | A40               | TDI/CTED9/RA4                                         |

|    | A41               | VDD                                                   |

|    | A42               | OSC2/CLKO/RC15                                        |

|    | A43               | Vss                                                   |

|    | A44               | SDA1/RPA15/RA15                                       |

|    | A45               | RPD9/RD9                                              |

|    | A46               | RPD11/PMCS1/RD11                                      |

|    | A47               | SOSCI/RPC13/RC13                                      |

|    | A48               | VDD                                                   |

|    | A49               | No Connect                                            |

|    | A50               | No Connect                                            |

|    | A51               | No Connect                                            |

|    | A52               | AN24/RPD1/RD1                                         |

|    | A53               | AN26/RPD3/RD3                                         |

|    | A54               | PMD13/RD13                                            |

|    | A55               | RPD5/PMRD/RD5                                         |

|    | A56               | PMD15/RD7                                             |

|    | A57               | No Connect                                            |

|    | A58               | No Connect                                            |

|    | A59               | VDD                                                   |

|    | A60               | RPF1/PMD10/RF1                                        |

|    | A61               | RPG0/PMD8/RG0                                         |

|    | A62               | TRD3/CTED8/RA7                                        |

|    | A63               | Vss                                                   |

|    | A64               | PMD1/RE1                                              |

|    | A65               | TRD1/RG12                                             |

|    | A66               | AN20/PMD2/RE2                                         |

|    | A67               | AN21/PMD4/RE4                                         |

|    | A68               | No Connect                                            |

|    | B1                | VDD                                                   |

|    | B2                | AN22/RPE5/PMD5/RE5                                    |

|    | В3                | AN27/PMD7/RE7                                         |

|    | B4                | RPC2/RC2                                              |

|    | B5                | RPC4/CTED7/RC4                                        |

| l  | B6                | AN17/C1INC/RPG7/PMA4/RG7                              |

| -  | 1 tortho          | railable peripherals and Section 12.2 "Peripheral Din |

- Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

- Shaded package bumps are 5V tolerant.

- 4: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

| PIC32M | X330/35 | 0/3/0/4 | 130/450/ | 470 |  |

|--------|---------|---------|----------|-----|--|

| NOTES: |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

|        |         |         |          |     |  |

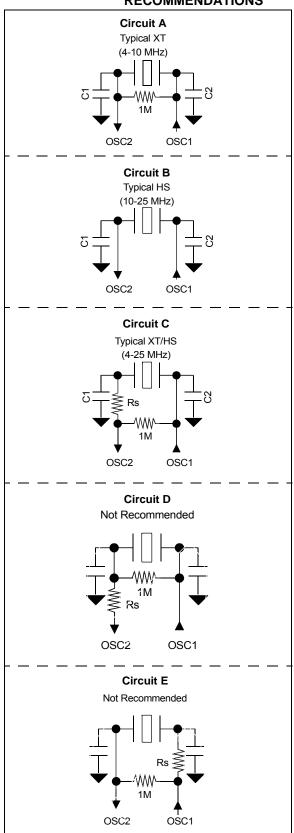

### 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32 OSC2 Pin Capacitance = ~4-5 pF

- COUT = PIC32 OSC1 Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

## EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

```

Crystal manufacturer recommended: C1 = C2 = 15 \ pF

Therefore:

CLOAD = \{([CIN + CI] * [COUT + C2]) / [CIN + CI + C2 + COUT]\} + estimated oscillator PCB stray capacitance

= \{([5 + 15][5 + 15]) / [5 + 15 + 15 + 5]\} + 2.5 \ pF

= \{([20][20]) / [40]\} + 2.5

= 10 + 2.5 = 12.5 \ pF

Rounded to the nearest standard value or 13 pF in this example for Primary Oscillator crystals "C1" and "C2".

```

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator.

The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

#### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC™ and PICmicro® Devices"

- AN849 "Basic PICmicro® Oscillator Design"

# FIGURE 2-4: PRIMARY CRYSTAL OSCILLATOR CIRCUIT RECOMMENDATIONS

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-------------------|------------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                  | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31.24        | _                 | 1                 | _                    | _                 | _                      | _                 | _                | _                |

| 22:46        | U-0               | U-0               | U-0                  | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | _                 | 1                 | _                    | _                 | _                      | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0               | R-0                    | U-0               | U-0              | U-0              |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR(1)         | LVDSTAT <sup>(1)</sup> | _                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0                  | U-0               | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                    | _                 |                        | NVMOF             | P<3:0>           |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 WR: Write Control bit

This bit is writable when WREN = 1 and the unlock sequence is followed.

1 = Initiate a Flash operation. Hardware clears this bit when the operation completes

0 = Flash operation complete or inactive

bit 14 WREN: Write Enable bit

1 = Enable writes to WR bit and enables LVD circuit

0 = Disable writes to WR bit and disables LVD circuit

This is the only bit in this register reset by a device Reset.

bit 13 **WRERR:** Write Error bit<sup>(1)</sup>

This bit is read-only and is automatically set by hardware.

1 = Program or erase sequence did not complete successfully

0 = Program or erase sequence completed normally

bit 12 LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled)<sup>(1)</sup>

This bit is read-only and is automatically set by hardware.

1 = Low-voltage detected (possible data corruption, if WRERR is set)

0 = Voltage level is acceptable for programming

bit 11 LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled)<sup>(1)</sup>

This bit is read-only and is automatically set, and cleared, by hardware.

1 = Low-voltage event active

0 = Low-voltage event NOT active

bit 10-4 Unimplemented: Read as '0'

bit 3-0 NVMOP<3:0>: NVM Operation bits

These bits are writable when WREN = 0.

1111 = Reserved

•

0111 = Reserved

0110 = No operation

0101 = Program Flash (PFM) erase operation: erases PFM, if all pages are not write-protected

0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected

0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected

0010 = No operation

0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected

0000 = No operation

Note 1: This bit is cleared by setting NVMOP = 0000, and initiating a Flash operation (i.e., WR).

#### 12.3.5 OUTPUT MAPPING

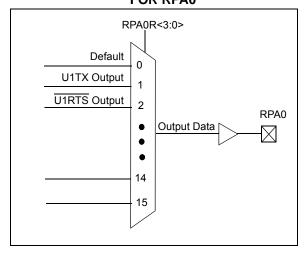

In contrast to inputs, the outputs of the peripheral pin select options are mapped on the basis of the pin. In this case, a control register associated with a particular pin dictates the peripheral output to be mapped. The RPnR registers (Register 12-2) are used to control output mapping. Like the [pin name]R registers, each register contains sets of 4 bit fields. The value of the bit field corresponds to one of the peripherals, and that peripheral's output is mapped to the pin (see Table 12-2 and Figure 12-3).

A null output is associated with the output register reset value of '0'. This is done to ensure that remappable outputs remain disconnected from all output pins by default.

FIGURE 12-3: EXAMPLE OF MULTIPLEXING OF REMAPPABLE OUTPUT FOR RPA0

## 12.3.6 CONTROLLING CONFIGURATION CHANGES

Because peripheral remapping can be changed during run time, some restrictions on peripheral remapping are needed to prevent accidental configuration changes. PIC32 devices include two features to prevent alterations to the peripheral map:

- · Control register lock sequence

- · Configuration bit select lock

#### 12.3.6.1 Control Register Lock

Under normal operation, writes to the RPnR and [pin name]R registers are not allowed. Attempted writes appear to execute normally, but the contents of the registers remain unchanged. To change these registers, they must be unlocked in hardware. The register lock is controlled by the IOLOCK Configuration bit (CFGCON<13>). Setting IOLOCK prevents writes to the control registers; clearing IOLOCK allows writes.

To set or clear the IOLOCK bit, an unlock sequence must be executed. Refer to **Section 6. "Oscillator"** (DS60001112) in the "PIC32 Family Reference Manual" for details.

#### 12.3.6.2 Configuration Bit Select Lock

As an additional level of safety, the device can be configured to prevent more than one write session to the RPnR and [pin name]R registers. The IOL1WAY Configuration bit (DEVCFG3<29>) blocks the IOLOCK bit from being cleared after it has been set once. If IOLOCK remains set, the register unlock procedure does not execute, and the peripheral pin select control registers cannot be written to. The only way to clear the bit and re-enable peripheral remapping is to perform a device Reset.

In the default (unprogrammed) state, IOL1WAY is set, restricting users to one write session.

**TABLE 12-2: OUTPUT PIN SELECTION**

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection      |

|----------------------|----------|-------------|--------------------------------------------|

| RPD2                 | RPD2R    | RPD2R<3:0>  | 0000 = No Connect                          |

| RPG8                 | RPG8R    | RPG8R<3:0>  | 0001 = U3TX                                |

| RPF4                 | RPF4R    | RPF4R<3:0>  | 0010 = U4RTS<br>0011 = Reserved            |

| RPD10                | RPD10R   | RPD10R<3:0> | 0110 = Reserved                            |

| RPF1                 | RPF1R    | RPF1R<3:0>  | 0101 = Reserved                            |

| RPB9                 | RPB9R    | RPB9R<3:0>  | 0110 = SDO2                                |

| RPB10                | RPB10R   | RPB10R<3:0> | 0111 = Reserved<br>1000 = Reserved         |

| RPC14                | RPC14R   | RPC14R<3:0> | 1000 - Reserved                            |

| RPB5                 | RPB5R    | RPB5R<3:0>  | 1010 = Reserved                            |

| RPC1 <sup>(4)</sup>  | RPC1R    | RPC1R<3:0>  | 1011 = OC3                                 |

| RPD14 <sup>(4)</sup> | RPD14R   | RPD14R<3:0> | 1100 = Reserved<br>1101 = C2OUT            |

| RPG1 <sup>(4)</sup>  | RPG1R    | RPG1R<3:0>  | 11101 - G2001<br>1110 = Reserved           |

| RPA14 <sup>(4)</sup> | RPA14R   | RPA14R<3:0> | 1111 = Reserved                            |

| RPD3                 | RPD3R    | RPD3R<3:0>  | 0000 = No Connect                          |

| RPG7                 | RPG7R    | RPG7R<3:0>  | 0001 <b>= U2TX</b>                         |

| RPF5                 | RPF5R    | RPF5R<3:0>  | 0010 = Reserved                            |

| RPD11                | RPD11R   | RPD11R<3:0> | 0011 = U1TX<br>0100 = U5RTS <sup>(4)</sup> |

| RPF0                 | RPF0R    | RPF0R<3:0>  | 0100 = OSRTS( )<br>0101 = Reserved         |

| RPB1                 | RPB1R    | RPB1R<3:0>  | 0110 = SDO2                                |

| RPE5                 | RPE5R    | RPE5R<3:0>  | 0111 = Reserved                            |

| RPC13                | RPC13R   | RPC13R<3:0> | 1000 = SDO1                                |

| RPB3                 | RPB3R    | RPB3R<3:0>  | 1001 = Reserved                            |

| RPF3 <sup>(2)</sup>  | RPF3R    | RPF3R<3:0>  | 1010 = Reserved                            |

| RPC4 <sup>(4)</sup>  | RPC4R    | RPC4R<3:0>  | 1011 = OC4<br>1100 = Reserved              |

| RPD15 <sup>(4)</sup> | RPD15R   | RPD15R<3:0> | 1100 = Reserved                            |

| RPG0 <sup>(4)</sup>  | RPG0R    | RPG0R<3:0>  | 1110 = Reserved                            |

| RPA15 <sup>(4)</sup> | RPA15R   | RPA15R<3:0> | 1111 = Reserved                            |

Note 1: This selection is only available on General Purpose devices.

**<sup>2:</sup>** This selection is only available on 64-pin General Purpose devices.

<sup>3:</sup> This selection is only available on 100-pin General Purpose devices.

<sup>4:</sup> This selection is only available on 100-pin USB and General Purpose devices.

<sup>5:</sup> This selection is not available on 64-pin USB devices.

TABLE 12-5: PORTC REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L, PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY

| w                           |                                 |           |           |           |           |           |       |       |      |      |      |      |      |          |          |          |          |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|----------|----------|----------|----------|------|---------------|

| es:                         |                                 | ø         |           |           |           |           |       |       |      | Bits |      |      |      |          |          |          |          |      |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0 | All<br>Resets |

| 6210                        | TRISC                           | 31:16     | _         |           | _         |           | I     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0210                        | TRISC                           | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | 1     | _     | _    | _    |      |      | _    | TRISC4   | TRISC3   | TRISC2   | TRISC1   | _    | xxxx          |

| 6220                        | PORTC                           | 31:16     | _         | 1         | _         | 1         | I     | _     | _    | _    |      |      | _    | _        | _        | -        |          | _    | 0000          |

| 0220                        | FORTO                           | 15:0      | RC15      | RC14      | RC13      | RC12      | I     | _     | _    | _    |      |      | _    | RC4      | RC3      | RC2      | RC1      | _    | xxxx          |

| 6230                        | LATC                            | 31:16     | _         | 1         | _         | 1         | I     | _     | _    | _    |      |      | _    | _        | _        | -        |          | _    | 0000          |

| 0230                        | LAIC                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | I     | _     | _    | _    |      |      | _    | LATC4    | LATC3    | LATC2    | LATC1    | _    | xxxx          |

| 6240                        | ODCC                            | 31:16     | _         | 1         | _         | 1         | I     | _     | _    | _    |      |      | _    | _        | _        | -        |          | _    | 0000          |

| 0240                        | ODCC                            | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | -     | _     |      | _    | _    | _    | _    | ODCC4    | ODCC3    | ODCC2    | ODCC1    | _    | xxxx          |

| 6250                        | CNPUC                           | 31:16     | _         | 1         | _         | 1         | I     | _     | _    | _    |      |      | _    | _        | _        | -        |          | _    | 0000          |

| 0230                        | CINFOC                          | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | I     | _     | _    | _    |      |      | _    | CNPUC4   | CNPUC3   | CNPUC2   | CNPUC1   | _    | xxxx          |

| 6260                        | CNPDC                           | 31:16     | _         | 1         | _         | 1         | I     | _     | _    | _    |      |      | _    | _        | _        | -        |          | _    | 0000          |

| 0200                        | CINFDC                          | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | I     | _     | _    | _    |      |      | _    | CNPDC4   | CNPDC3   | CNPDC2   | CNPDC1   | _    | xxxx          |

| 6270                        | CNCONC                          | 31:16     | _         | -         | _         |           | -     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0270                        | CNCONC                          | 15:0      | ON        | 1         | SIDL      | 1         | I     | _     | _    | _    |      |      | _    | _        | _        | -        |          | _    | 0000          |

| 6280                        | CNENC                           | 31:16     | _         | 1         |           | 1         | I     | _     | _    | _    |      |      | _    | _        | _        | -        |          | _    | 0000          |

| 0200                        | CINLING                         | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | _     | _     | _    | _    | _    | _    | _    | CNIEC4   | CNIEC3   | CNIEC2   | CNIEC1   | _    | xxxx          |

| 6200                        | CNSTATC                         | 31:16     | _         |           | _         |           | 1     | _     | _    | _    | _    | _    | _    | _        | _        | _        | _        | _    | 0000          |

| 0290                        | CINGIAIC                        | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | _     | _     | _    | _    | _    | _    | _    | CNSTATC4 | CNSTATC3 | CNSTATC2 | CNSTATC1 | _    | xxxx          |

Legend

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

#### 16.1 Control Register

#### REGISTER 16-1: ICXCON: INPUT CAPTURE 'x' CONTROL REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24     | _                 | _                 | -                 | -                 | _                 | -                 | -                | _                |

| 22.46     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16     | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 15:8      | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15.6      | ON <sup>(1)</sup> | _                 | SIDL              | _                 | _                 | _                 | FEDGE            | C32              |

| 7.0       | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0               | R/W-0             | R/W-0            | R/W-0            |

| 7:0       | ICTMR             | ICI<              | 1:0>              | ICOV              | ICBNE             |                   | ICM<2:0>         |                  |

Legend:

bit 8

R = Readable bit W = Writable bit U = Unimplemented bit

-n = Bit Value at POR: ('0', '1', x = unknown) P = Programmable bit r = Reserved bit

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Input Capture Module Enable bit (1)

1 = Module is enabled

0 = Disable and reset module, disable clocks, disable interrupt generation and allow SFR modifications

bit 14 **Unimplemented:** Read as '0' bit 13 **SIDL:** Stop in Idle Control bit

1 = Halt in CPU Idle mode

0 = Continue to operate in CPU Idle mode

bit 12-10 **Unimplemented:** Read as '0'

bit 9 **FEDGE:** First Capture Edge Select bit (only used in mode 6, ICM<2:0> = 110)

1 = Capture rising edge first 0 = Capture falling edge first C32: 32-bit Capture Select bit

1 = 32-bit timer resource capture0 = 16-bit timer resource capture

bit 7 ICTMR: Timer Select bit (Does not affect timer selection when C32 (ICxCON<8>) is '1')

0 = Timer3 is the counter source for capture1 = Timer2 is the counter source for capture

bit 6-5 ICI<1:0>: Interrupt Control bits

11 = Interrupt on every fourth capture event

10 = Interrupt on every third capture event

01 = Interrupt on every second capture event

00 = Interrupt on every capture event

bit 4 ICOV: Input Capture Overflow Status Flag bit (read-only)

1 = Input capture overflow has occurred0 = No input capture overflow has occurred

bit 3 **ICBNE:** Input Capture Buffer Not Empty Status bit (read-only)

1 = Input capture buffer is not empty; at least one more capture value can be read

0 = Input capture buffer is empty

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 3 CS1P: Chip Select 0 Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMCS1)

- $0 = Active-low (\overline{PMCS1})$

- bit 2 **Unimplemented:** Read as '0'

- bit 1 WRSP: Write Strobe Polarity bit

For Slave Modes and Master mode 2 (MODE<1:0> = 00,01,10):

- 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

#### For Master mode 1 (MODE<1:0> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

For Slave modes and Master mode 2 (MODE<1:0> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- 0 = Read Strobe active-low (PMRD)

For Master mode 1 (MODE<1:0> = 11):

- 1 = Read/write strobe active-high (PMRD/PMWR)

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

| PIC32IVIX | (330/350 | 0/3/0/43 | 30/450/4 | 170 |  |

|-----------|----------|----------|----------|-----|--|

| NOTES:    |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

|           |          |          |          |     |  |

REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 31.24        | EDG1MOD           | EDG1POL           |                   | EDG1S               | EL<3:0>           |                   | EDG2STAT               | EDG1STAT         |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | EL<3:0>           |                   | _                      | _                |

| 15:0         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 15:8         | ON                | _                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 7:0          |                   |                   |                   | IRNG                | <1:0>             |                   |                        |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 **EDG1MOD:** Edge 1 Edge Sampling Select bit

1 = Input is edge-sensitive

0 = Input is level-sensitive

bit 30 EDG1POL: Edge 1 Polarity Select bit

1 = Edge 1 programmed for a positive edge response

0 = Edge 1 programmed for a negative edge response

bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

1111 = Reserved

1110 = C2OUT pin is selected

1101 = C1OUT pin is selected

1100 = IC3 Capture Event is selected

1011 = IC2 Capture Event is selected

1010 = IC1 Capture Event is selected

1001 = CTED8 pin is selected

1000 = CTED7 pin is selected

0111 = CTED6 pin is selected

0110 = CTED5 pin is selected

0101 = CTED4 pin is selected

0100 = CTED3 pin is selected

0011 = CTED1 pin is selected

0010 = CTED2 pin is selected

0001 = OC1 Compare Event is selected

0000 = Timer1 Event is selected

bit 25 **EDG2STAT:** Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control edge source

1 = Edge 2 has occurred

0 = Edge 2 has not occurred

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-42) in **Section 31.0** "Electrical Characteristics" for current values.

- **4:** This bit setting is not available for the CTMU temperature diode.

TABLE 31-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARA      | CTERISTICS             | <b>3</b> | (unless of                                   | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |             |  |  |  |  |  |

|---------------|------------------------|----------|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|--|

| Parameter No. | Typical <sup>(3)</sup> | Maximum  | Units                                        | Co                                                                                                                                                                                                                                                       | onditions   |  |  |  |  |  |

| Operating (   | Current (IDD)          | (1,2)    |                                              |                                                                                                                                                                                                                                                          |             |  |  |  |  |  |

| DC20          | 2.5                    | 4        | mA                                           |                                                                                                                                                                                                                                                          | 4 MHz       |  |  |  |  |  |

| DC21          | 6                      | 9        | mA                                           | 10 M                                                                                                                                                                                                                                                     | Hz (Note 4) |  |  |  |  |  |

| DC22          | 11                     | 17       | mA                                           | 20 M                                                                                                                                                                                                                                                     | Hz (Note 4) |  |  |  |  |  |

| DC23          | 21                     | 32       | mA                                           | 40 M                                                                                                                                                                                                                                                     | Hz (Note 4) |  |  |  |  |  |

| DC24          | 30                     | 45       | mA                                           | 60 M                                                                                                                                                                                                                                                     | Hz (Note 4) |  |  |  |  |  |

| DC25          | 40                     | 60       | mA                                           | (                                                                                                                                                                                                                                                        | 80 MHz      |  |  |  |  |  |

| DC25a         | 50                     | 75       | mA 100 MHz, -40°C ≤ Ta ≤ +85°C               |                                                                                                                                                                                                                                                          |             |  |  |  |  |  |

| DC25c         | 72                     | 84       | mA 120 MHz, 0°C ≤ Ta ≤ +70°C                 |                                                                                                                                                                                                                                                          |             |  |  |  |  |  |

| DC26          | 100                    | _        | μA +25°C, 3.3V LPRC (31 kHz) <b>(Note 4)</b> |                                                                                                                                                                                                                                                          |             |  |  |  |  |  |

- **Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, program Flash, and SRAM data memory are operational, program Flash memory Wait states = 7, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating (ON bit = 0), but the associated PMD bit is clear

- · WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- · RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- 4: This parameter is characterized, but not tested in manufacturing.

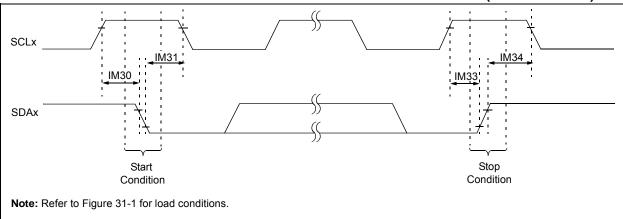

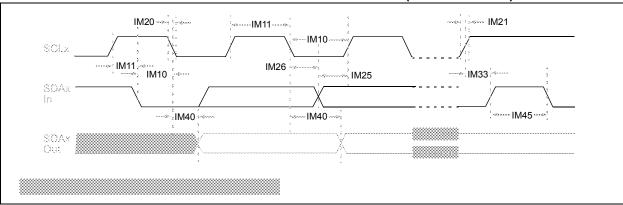

#### FIGURE 31-14: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (MASTER MODE)

### FIGURE 31-15: I2Cx BUS DATA TIMING CHARACTERISTICS (MASTER MODE)

TABLE 31-34: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

| AC CHARACTERISTICS |         |                            |                        |      |      |       |                            |

|--------------------|---------|----------------------------|------------------------|------|------|-------|----------------------------|

| Param.<br>No.      | Symbol  | Charact                    | eristics               | Min. | Max. | Units | Conditions                 |

| IS34               | THD:STO | Stop Condition             | 100 kHz mode           | 4000 | _    | ns    | _                          |

|                    |         | Hold Time                  | 400 kHz mode           | 600  | _    | ns    |                            |

|                    |         |                            | 1 MHz mode<br>(Note 1) | 250  |      | ns    |                            |

| IS40               | TAA:SCL | Output Valid from<br>Clock | 100 kHz mode           | 0    | 3500 | ns    | _                          |

|                    |         |                            | 400 kHz mode           | 0    | 1000 | ns    |                            |

|                    |         |                            | 1 MHz mode<br>(Note 1) | 0    | 350  | ns    |                            |

| IS45               | TBF:SDA | Bus Free Time              | 100 kHz mode           | 4.7  | _    | μS    | The amount of time the bus |

|                    |         |                            | 400 kHz mode           | 1.3  | _    | μS    | must be free before a new  |

|                    |         |                            | 1 MHz mode<br>(Note 1) | 0.5  | _    | μS    | transmission can start     |

| IS50               | Св      | Bus Capacitive Loading     |                        | _    | 400  | pF    | _                          |

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

| PIC32MX330/350/370/430/450/470 |  |  |  |  |  |

|--------------------------------|--|--|--|--|--|

| NOTES:                         |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

|                                |  |  |  |  |  |

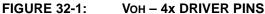

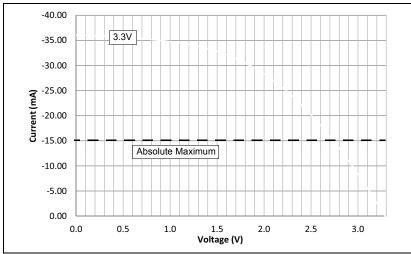

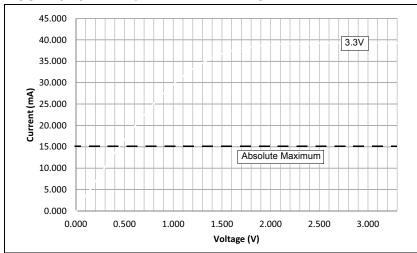

#### 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

**Note:** The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

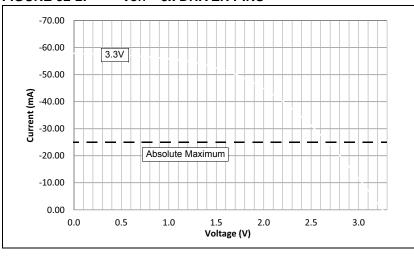

#### FIGURE 32-3: Vol – 4x DRIVER PINS

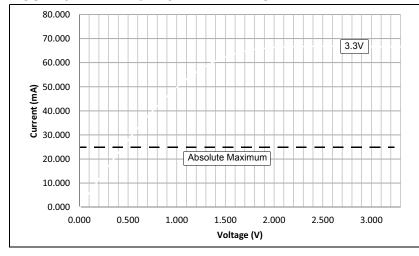

#### FIGURE 32-2: VoH – 8x DRIVER PINS

#### FIGURE 32-4: Vol – 8x DRIVER PINS

### 33.1 Package Marking Information (Continued)

64-Lead QFN (9x9x0.9 mm) with 5.40x5.40 Exposed Pad

#### Example

64-Lead QFN (9x9x0.9 mm) with 4.7x4.7 Exposed Pad

#### Example

124-Lead VTLA (9x9x0.9 mm)

#### Example

Legend: XX...X Customer-specific information

Year code (last digit of calendar year)

YY Year code (last 2 digits of calendar year)

WW Week code (week of January 1 is week '01')

NNN Alphanumeric traceability code

Pb-free JEDEC designator for Matte Tin (Sn)

\* This package is Pb-free. The Pb-free JEDEC designator (e3)

can be found on the outer packaging for this package.

**ote:** In the event the full Microchip part number cannot be marked on one line, it will be carried over to the next line, thus limiting the number of available characters for customer-specific information.

### **Revision C (October 2013)**

This revision includes the following updates, as listed in Table A-2.

TABLE A-2: MAJOR SECTION UPDATES

| Section                                                               | Update Description                                                                                                                                                                |  |  |  |  |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| "32-bit Microcontrollers (up to 512<br>KB Flash and 128 KB SRAM) with | The Operating Conditions and Core sections were updated in support of 100 MHz (-40°C to +85°C) devices.                                                                           |  |  |  |  |

| Audio/Graphics/Touch (HMI), USB, and Advanced Analog"                 | Added Notes 2 and 3 regarding the conductive thermal pad to the 124-pin VTLA pin diagrams.                                                                                        |  |  |  |  |

| 2.0 "Guidelines for Getting Started                                   | Updated the recommended minimum connection (see Figure 2-1).                                                                                                                      |  |  |  |  |

| with 32-bit MCUs"                                                     | Added 2.10 "Sosc Design Recommendation".                                                                                                                                          |  |  |  |  |

| 20.0 "Parallel Master Port (PMP)"                                     | Updated the Parallel Port Control register, PMCON (see Register 20-1).                                                                                                            |  |  |  |  |

|                                                                       | Updated the Parallel Port Mode register, PMMODE (see Register 20-2).                                                                                                              |  |  |  |  |

|                                                                       | Updated the Parallel Port Pin Enable register, PMAEN (see Register 20-4).                                                                                                         |  |  |  |  |

| 30.0 "Electrical Characteristics"                                     | Removed Note 4 from the Absolute Maximum Ratings.                                                                                                                                 |  |  |  |  |

|                                                                       | The maximum frequency for parameter DC5 In Operating MIPS vs. Voltage was changed to 100 MHz (see Table 30-1).                                                                    |  |  |  |  |

|                                                                       | Parameter DC25a was added to DC Characteristics: Operating Current (IDD) (see Table 30-5).                                                                                        |  |  |  |  |

|                                                                       | Parameter DC34c was added to DC Characteristics: Idle Current (IIDLE) (see Table 30-5).                                                                                           |  |  |  |  |

|                                                                       | Added parameters for PIC32MX370/470 devices and removed Note 5 from DC Characteristics: Power-Down Current (IPD) (see Table 30-7).                                                |  |  |  |  |

|                                                                       | Updated the Minimum, Typical, and Maximum values and added a reference to Note 3 for parameter DI30 (ICNPU) in DC Characteristics: I/O Pin Input Specifications (see Table 30-8). |  |  |  |  |

|                                                                       | The SYSCLK values for all required Flash Wait states were updated (see Table 30-13).                                                                                              |  |  |  |  |

|                                                                       | Added parameter DO50A (Csosc) to the Capacitive Loading Requirements on Output Pins (see Table 30-16).                                                                            |  |  |  |  |

|                                                                       | Updated the maximum values for parameter OS10, and the Characteristics definition of parameter OS42 (GM) in the External Clock Timing Characteristics (see Table 30-17).          |  |  |  |  |

| 31.0 "DC and AC Device<br>Characteristics Graphs"                     | Updated the IPD, IIDLE, and IDD graphs, and added new graphs for the PIC32MX370/470 devices (see Figure 31-5 through Figure 31-13).                                               |  |  |  |  |

| NVMDATA (Flash Program Data)57                      |

|-----------------------------------------------------|

| NVMKEY (Programming Unlock)56                       |

| NVMSRCADDR (Source Data Address)57                  |

| OCxCON (Output Compare x Control) 187               |

| OSCCON (Oscillator Control)76                       |

| PFABT (Prefetch Cache Abort Statistics)             |

| PMADDR (Parallel Port Address)219                   |

| PMAEN (Parallel Port Pin Enable)220                 |

|                                                     |

| PMCON (Parallel Port Control)                       |

| PMMODE (Parallel Port Mode)217                      |

| PMSTAT (Parallel Port Status (Slave Modes Only) 221 |

| REFOCON (Reference Oscillator Control)80            |

| REFOTRIM (Reference Oscillator Trim)82              |

| RPnR (Peripheral Pin Select Output)165              |

| RSWRST (Software Reset)62                           |

| RTCCON (RTC Control)225                             |

| RTCDATE (RTC Date Value)230                         |

| RTCTIME (RTC Time Value)229                         |

| SPIxCON (SPI Control)191                            |

| SPIxCON2 (SPI Control 2)194                         |

| SPIxSTAT (SPI Status)195                            |

| T1CON (Type A Timer Control)                        |

|                                                     |

| TxCON (Type B Timer Control)                        |

| U1ADDR (USB Address)                                |

| U1BDTP1 (USB BDT Page 1)133                         |

| U1BDTP2 (USB BDT Page 2)134                         |

| U1BDTP3 (USB BDT Page 3)134                         |

| U1CNFG1 (USB Configuration 1)135                    |

| U1CON (USB Control)129                              |

| U1EIE (USB Error Interrupt Enable)                  |

| U1EIR (USB Error Interrupt Status)125               |

| U1EP0-U1EP15 (USB Endpoint Control)                 |

| U1FRMH (USB Frame Number High)                      |

| U1FRML (USB Frame Number Low)                       |

| U1IE (USB Interrupt Enable)124                      |

| U1IR (USB Interrupt)123                             |

| U10TGCON (USB OTG Control)123                       |

| U10TGIE (USB OTG Interrupt Enable)121               |

| UTOTGIE (USB OTG Interrupt Enable)                  |

| U1OTGIR (USB OTG Interrupt Status)118               |

| U1OTGSTAT (USB OTG Status)120                       |

| U1PWRC (USB Power Control)122                       |

| U1SOF (USB SOF Threshold)133                        |

| U1STAT (USB Status)128                              |

| U1TOK (USB Token)132                                |

| WDTCON (Watchdog Timer Control) 179                 |

| Resets                                              |

| Revision History                                    |

| RTCALRM (RTC ALARM Control)                         |

| · · · · · · · · · · · · · · · · · · ·               |

| S                                                   |

| Serial Peripheral Interface (SPI)                   |

| Software Simulator (MPLAB SIM)                      |

| Outware Simulator (INIT LAD SINI)                   |

| 1                                              |       |

|------------------------------------------------|-------|

| Timer1 Module                                  | . 167 |

| Timer2/3, Timer4/5 Modules                     | . 171 |

| Timing Diagrams                                |       |

| 10-Bit Analog-to-Digital Conversion            |       |

| (ASAM = 0, SSRC<2:0> = 000)                    | . 320 |

| 10-Bit Analog-to-Digital Conversion (ASAM = 1, |       |

| SSRC<2:0> = 111, SAMC<4:0> = 00001)            | . 321 |

| EJTAG                                          |       |

| External Clock                                 |       |

| I/O Characteristics                            |       |

| I2Cx Bus Data (Master Mode)                    |       |

| I2Cx Bus Data (Slave Mode)                     |       |

| I2Cx Bus Start/Stop Bits (Master Mode)         |       |

| I2Cx Bus Start/Stop Bits (Slave Mode)          |       |

| Input Capture (CAPx)                           |       |

| OCx/PWM                                        |       |

|                                                |       |

| Output Compare (OCx)                           |       |

| Parallel Master Port Read                      |       |

| Parallel Master Port Write                     |       |

| Parallel Slave Port                            | . 322 |

| SPIx Master Mode (CKE = 0)                     |       |

| SPIx Master Mode (CKE = 1)                     |       |

| SPIx Slave Mode (CKE = 0)                      |       |

| SPIx Slave Mode (CKE = 1)                      |       |

| Timer1, 2, 3, 4, 5 External Clock              |       |

| UART Reception                                 |       |

| UART Transmission (8-bit or 9-bit Data)        | . 212 |

| Timing Requirements                            |       |

| CLKO and I/O                                   | . 298 |

| Timing Specifications                          |       |

| I2Cx Bus Data Requirements (Master Mode)       | . 311 |

| I2Cx Bus Data Requirements (Slave Mode)        | . 314 |

| Input Capture Requirements                     |       |

| Output Compare Requirements                    |       |

| Simple OCx/PWM Mode Requirements               | . 303 |

| SPIx Master Mode (CKE = 0) Requirements        |       |

| SPIx Master Mode (CKE = 1) Requirements        |       |

| SPIx Slave Mode (CKE = 1) Requirements         |       |

| SPIx Slave Mode Requirements (CKE = 0)         |       |

| ,                                              |       |

| U                                              |       |

| UART                                           | . 205 |

| USB On-The-Go (OTG)                            |       |

|                                                |       |

| V                                              |       |

| VCAP pin                                       | . 272 |

| Voltage Regulator (On-Chip)                    | . 272 |

|                                                |       |

| W                                              |       |

| WWW Address                                    | 359   |

| WWW, On-Line Support                           |       |

|                                                |       |