Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 81                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f128l-i-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4: PIN NAMES FOR 100-PIN DEVICES (CONTINUED)

| 10                                           | 100-PIN TQFP (TOP VIEW) <sup>(1,2,3)</sup>                                                                                                          |                                                    |                                                                                                                                               |  |  |  |  |  |  |

|----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                                              | PIC32MX330F064L<br>PIC32MX350F128L<br>PIC32MX350F256L<br>PIC32MX370F512L                                                                            |                                                    |                                                                                                                                               |  |  |  |  |  |  |

|                                              |                                                                                                                                                     |                                                    | 100 1                                                                                                                                         |  |  |  |  |  |  |

| Pin #                                        | Full Pin Name                                                                                                                                       | Pin #                                              | Full Pin Name                                                                                                                                 |  |  |  |  |  |  |

| 71                                           | RPD11/PMCS1/RD11                                                                                                                                    | 86                                                 | Vdd                                                                                                                                           |  |  |  |  |  |  |

| 72                                           | RPD0/RD0                                                                                                                                            | 87                                                 | RPF0/PMD11/RF0                                                                                                                                |  |  |  |  |  |  |

| 73                                           | SOSCI/RPC13/RC13                                                                                                                                    |                                                    |                                                                                                                                               |  |  |  |  |  |  |

|                                              |                                                                                                                                                     | 88                                                 | RPF1/PMD10/RF1                                                                                                                                |  |  |  |  |  |  |

| 74                                           | SOSCO/RPC14/T1CK/RC14                                                                                                                               | 88                                                 | RPF1/PMD10/RF1<br>RPG1/PMD9/RG1                                                                                                               |  |  |  |  |  |  |

| 74<br>75                                     |                                                                                                                                                     |                                                    |                                                                                                                                               |  |  |  |  |  |  |

|                                              | SOSCO/RPC14/T1CK/RC14                                                                                                                               | 89                                                 | RPG1/PMD9/RG1                                                                                                                                 |  |  |  |  |  |  |

| 75                                           | SOSCO/RPC14/T1CK/RC14<br>Vss                                                                                                                        | 89<br>90                                           | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0                                                                                                                |  |  |  |  |  |  |

| 75<br>76                                     | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1                                                                                                       | 89<br>90<br>91                                     | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6                                                                                                   |  |  |  |  |  |  |

| 75<br>76<br>77                               | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1<br>AN25/RPD2/RD2                                                                                      | 89<br>90<br>91<br>92                               | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6<br>TRD3/CTED8/RA7                                                                                 |  |  |  |  |  |  |

| 75<br>76<br>77<br>78                         | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1<br>AN25/RPD2/RD2<br>AN26/RPD3/RD3                                                                     | 89<br>90<br>91<br>92<br>93                         | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6<br>TRD3/CTED8/RA7<br>PMD0/RE0                                                                     |  |  |  |  |  |  |

| 75<br>76<br>77<br>78<br>79                   | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1<br>AN25/RPD2/RD2<br>AN26/RPD3/RD3<br>RPD12/PMD12/RD12<br>PMD13/RD13<br>RPD4/PMWR/RD4                  | 89<br>90<br>91<br>92<br>93<br>94                   | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6<br>TRD3/CTED8/RA7<br>PMD0/RE0<br>PMD1/RE1<br>TRD2/RG14<br>TRD1/RG12                               |  |  |  |  |  |  |

| 75<br>76<br>77<br>78<br>79<br>80             | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1<br>AN25/RPD2/RD2<br>AN26/RPD3/RD3<br>RPD12/PMD12/RD12<br>PMD13/RD13                                   | 89<br>90<br>91<br>92<br>93<br>94<br>95             | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6<br>TRD3/CTED8/RA7<br>PMD0/RE0<br>PMD1/RE1<br>TRD2/RG14                                            |  |  |  |  |  |  |

| 75<br>76<br>77<br>78<br>79<br>80<br>81       | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1<br>AN25/RPD2/RD2<br>AN26/RPD3/RD3<br>RPD12/PMD12/RD12<br>PMD13/RD13<br>RPD4/PMWR/RD4                  | 89<br>90<br>91<br>92<br>93<br>94<br>95<br>96       | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6<br>TRD3/CTED8/RA7<br>PMD0/RE0<br>PMD1/RE1<br>TRD2/RG14<br>TRD1/RG12<br>TRD0/RG13<br>AN20/PMD2/RE2 |  |  |  |  |  |  |

| 75<br>76<br>77<br>78<br>79<br>80<br>81<br>82 | SOSCO/RPC14/T1CK/RC14<br>Vss<br>AN24/RPD1/RD1<br>AN25/RPD2/RD2<br>AN26/RPD3/RD3<br>RPD12/PMD12/RD12<br>PMD13/RD13<br>RPD4/PMWR/RD4<br>RPD5/PMRD/RD5 | 89<br>90<br>91<br>92<br>93<br>94<br>95<br>96<br>97 | RPG1/PMD9/RG1<br>RPG0/PMD8/RG0<br>TRCLK/RA6<br>TRD3/CTED8/RA7<br>PMD0/RE0<br>PMD1/RE1<br>TRD2/RG14<br>TRD1/RG12<br>TRD0/RG13                  |  |  |  |  |  |  |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx), with the exception of RF6, can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: RPF6 (pin 55) and RPF7 (pin 54) are only remappable for input functions.

# PIC32MX330/350/370/430/450/470

NOTES:

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS50001765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS50001764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" DS50001616

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) DS50001749

## 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

## 2.7 Trace

The trace pins can be connected to a hardware trace-enabled programmer to provide a compressed real-time instruction trace. When used for trace, the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

## 2.8 External Oscillator Pins

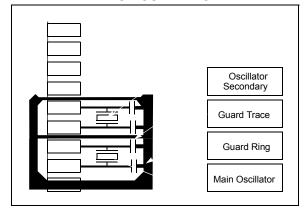

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                              | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------|------------------|--|--|--|

| 04-04        | R/W-0                                         | R/W-0            |  |  |  |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25                                         | IFS24            |  |  |  |

| 00.40        | R/W-0                                         | R/W-0            |  |  |  |

| 23:16        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             |                                               | IFS16            |  |  |  |

| 45.0         | R/W-0                                         | R/W-0            |  |  |  |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | 25/17/9/1<br>R/W-0<br>IFS25<br>R/W-0<br>IFS17 | IFS8             |  |  |  |

| 7.0          | R/W-0                                         | R/W-0            |  |  |  |

| 7:0          | IFS7              | IFS6              | IFS5              | IFS4              | IFS3              | IFS2              | IFS1                                          | IFS0             |  |  |  |

#### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

## Legend:

| 0                 |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-0 IFS31-IFS0: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

## REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC9             | IEC8             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC7              | IEC6              | IEC5              | IEC4              | IEC3              | IEC2              | IEC1             | IEC0             |

| Legend:           |                                                     |                      |                    |

|-------------------|-----------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      |                    |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 IEC31-IEC0: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        |                   |                   |                   | ROTRI             | √<8:1>            |                   |                  |                  |

| 00.40        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | ROTRIM<0>         | _                 | —                 | _                 | —                 | —                 | -                | —                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | —                 | _                 | —                 | —                 | U-0              | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

#### REGISTER 8-4: REFOTRIM: REFERENCE OSCILLATOR TRIM REGISTER

| Legend:           | y = Value set from Configuration bits on POR |                                    |                    |  |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-23 ROTRIM<8:0>: Reference Oscillator Trim bits

Note: While the ON bit (REFOCON<15>) is '1', writes to this register do not take effect until the DIVSWEN bit is also set to '1'.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 51.24        | LTAGBOOT          | —                 | —                 | —                 | —                 | -                 | _                | —                |  |  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23.10        | LTAG<19:12>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   |                   |                   | LTAG<             | 11:4>             |                   | R/W-x            |                  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-0             | R/W-0             | R/W-1            | U-0              |  |  |

| 7.0          |                   | LTAG<             | <3:0>             |                   | LVALID            | LLOCK             | LTYPE            | —                |  |  |

#### **REGISTER 9-3: CHETAG: CACHE TAG REGISTER**

## Legend:

| R = Readable bitW = Writable bitU = Unimplemented bit, re |                  | ad as '0'            |                    |  |

|-----------------------------------------------------------|------------------|----------------------|--------------------|--|

| -n = Value at POR                                         | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |  |

#### bit 31 LTAGBOOT: Line TAG Address Boot bit

- 1 = The line is in the 0x1D000000 (physical) area of memory

- 0 = The line is in the 0x1FC00000 (physical) area of memory

#### bit 30-24 Unimplemented: Write '0'; ignore read

#### bit 23-4 LTAG<19:0>: Line TAG Address bits

LTAG<19:0> bits are compared against physical address to determine a hit. Because its address range and position of PFM in kernel space and user space, the LTAG PFM address is identical for virtual addresses, (system) physical addresses, and PFM physical addresses.

#### bit 3 LVALID: Line Valid bit

- 1 = The line is valid and is compared to the physical address for hit detection

- 0 = The line is not valid and is not compared to the physical address for hit detection

#### bit 2 LLOCK: Line Lock bit

- 1 = The line is locked and will not be replaced

- 0 = The line is not locked and can be replaced

#### bit 1 LTYPE: Line Type bit

- 1 = The line caches instruction words

- 0 = The line caches data words

- bit 0 Unimplemented: Write '0'; ignore read

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                                    | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------------|------------------|--|--|

| 21.24        | U-0                                                 | U-0              |  |  |

| 31:24        | —                 |                   | _                 | —                 |                   |                   |                                                     | -                |  |  |

| 22:16        | U-0                                                 | U-0              |  |  |

| 23:16        | —                 |                   | _                 | —                 | -                 |                   |                                                     | —                |  |  |

| 15:8         | U-0                                                 | U-0              |  |  |

| 15.0         | —                 | _                 | _                 | —                 | _                 | -                 | 25/17/9/1<br>U-0<br>U-0<br>U-0<br>U-0<br>U-0<br>R-0 | -                |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0                                                 | R-0              |  |  |

| 7:0          |                   |                   |                   |                   |                   |                   | FRMH<2:0>                                           |                  |  |  |

## REGISTER 11-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

| REGISTER II-13. UTTOR. USB TOREN REGISTER |                         |                   |                   |                   |                   |                   |                  |                  |

|-------------------------------------------|-------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range                              | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24                                     | U-0                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24                                     | —                       |                   | —                 | —                 | -                 | _                 | -                | —                |

| 23:16                                     | U-0                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10                                     | _                       |                   | _                 | —                 | -                 | _                 |                  | —                |

| 15:8                                      | U-0                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0                                      | _                       |                   |                   | —                 |                   | _                 |                  | —                |

| 7.0                                       | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0                                       | PID<3:0> <sup>(1)</sup> |                   |                   | EP<3:0>           |                   |                   |                  |                  |

## REGISTER 11-15: U1TOK: USB TOKEN REGISTER

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

0001 = OUT (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 1101 = SETUP (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

**Note 1:** All other values are reserved and must not be used.

## 12.1 Parallel I/O (PIO) Ports

All port pins have ten registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

## 12.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the presence of outputs higher than VDD (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Device Pin Tables"** section for the available pins and their functionality.

# 12.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

## 12.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be an NOP.

## 12.1.4 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports allows the PIC32MX330/350/370/430/450/470 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

Each I/O pin also has a weak pull-up and every I/O pin has a weak pull-down connected to it. The pullups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on change notifi-<br>cation pins should always be disabled<br>when the port pin is configured as a digital |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | output. They should also be disabled on                                                                                            |

|       | 5V tolerant pins when the pin voltage can                                                                                          |

|       | exceed VDD.                                                                                                                        |

An additional control register (CNCONx) is shown in Register 12-3.

# 12.2 CLR, SET, and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                   | —                 | _                 | _                 | _                 | —                 | _                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | —                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          |                     |                   | S                 | WDTWINEN          | WDTCLR            |                   |                  |                  |

## REGISTER 15-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                                    |                    |  |  |

|-------------------|-----------------------------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 WDTCLR: Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31.24        |                   | —                 | _                 |                      | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   |                   | _                    | —                 | —                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | —                    | —                 | —                 | —                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | -                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

## REGISTER 17-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 OC32: 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisions to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in HW only)

- 0 = No PWM Fault condition has occurred

- bit 3 OCTSEL: Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin is enabled

- 110 = PWM mode on OCx; Fault pin is disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

| REGISTE | R 19-1: I2CxCON: I <sup>2</sup> C CONTROL REGISTER (CONTINUED)                                                                                                                                                                                                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | <ul> <li>GCEN: General Call Enable bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)</li> <li>0 = General call address disabled</li> </ul>                                                                                              |

| bit 6   | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with SCLREL bit.<br>1 = Enable software or receive clock stretching<br>0 = Disable software or receive clock stretching                                                                                                                     |

| bit 5   | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge<br>0 = Send ACK during Acknowledge                                                                                        |

| bit 4   | <ul> <li>ACKEN: Acknowledge Sequence Enable bit</li> <li>(when operating as I<sup>2</sup>C master, applicable during master receive)</li> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.<br/>Hardware clear at end of master Acknowledge sequence.</li> <li>0 = Acknowledge sequence not in progress</li> </ul> |

| bit 3   | <ul> <li>RCEN: Receive Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte.</li> <li>0 = Receive sequence not in progress</li> </ul>                                                                                               |

| bit 2   | <ul> <li>PEN: Stop Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.</li> <li>0 = Stop condition not in progress</li> </ul>                                                                                                       |

| bit 1   | <ul> <li>RSEN: Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence.</li> <li>0 = Repeated Start condition not in progress</li> </ul>                                                              |

| bit 0   | <ul> <li>Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.</li> <li>0 = Start condition not in progress</li> </ul>                                                                                                        |

**Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

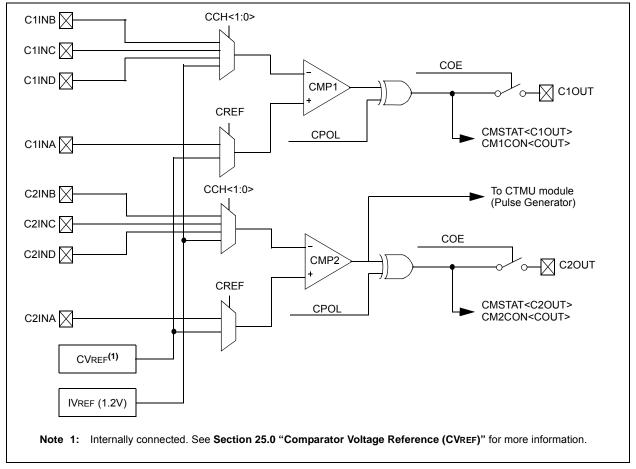

# 24.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer Section 19. to "Comparator" (DS60001110), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Analog Comparator module contains two comparators that can be configured in a variety of ways.

The following are key features of this module:

- · Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be Inverted

- Selectable interrupt generation

A block diagram of the comparator module is provided in Figure 24-1.

#### FIGURE 24-1: COMPARATOR BLOCK DIAGRAM

## 31.1 DC Characteristics

## TABLE 31-1: OPERATING MIPS VS. VOLTAGE

| Characteristic | Characteristic VDD Range Temp. Range<br>(in Volts) (in °C) |                 | Max. Frequency                 |

|----------------|------------------------------------------------------------|-----------------|--------------------------------|

| Characteristic |                                                            |                 | PIC32MX330/350/370/430/450/470 |

| DC5            | 2.3-3.6V <sup>(1)</sup>                                    | -40°C to +85°C  | 100 MHz                        |

| DC5b           | 2.3-3.6V <sup>(1)</sup>                                    | -40°C to +105°C | 80 MHz                         |

| DC5c           | 2.3-3.6V <sup>(1)</sup>                                    | 0°C to +70°C    | 120 MHz                        |

**Note 1:** Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 31-10 for VBORMIN values.

## TABLE 31-2: THERMAL OPERATING CONDITIONS

| Rating                                                                               | Symbol | Min. | Typical     | Max. | Unit |

|--------------------------------------------------------------------------------------|--------|------|-------------|------|------|

| Commercial Temperature Devices                                                       |        |      |             |      |      |

| Operating Junction Temperature Range                                                 | TJ     | 0    |             | +115 | °C   |

| Operating Ambient Temperature Range                                                  | TA     | 0    | _           | +70  | °C   |

| Industrial Temperature Devices                                                       |        |      |             |      |      |

| Operating Junction Temperature Range                                                 | TJ     | -40  |             | +125 | °C   |

| Operating Ambient Temperature Range                                                  | TA     | -40  | _           | +85  | °C   |

| V-temp Temperature Devices                                                           |        |      |             |      |      |

| Operating Junction Temperature Range                                                 | TJ     | -40  | _           | +140 | °C   |

| Operating Ambient Temperature Range                                                  | TA     | -40  |             | +105 | °C   |

| Power Dissipation:<br>Internal Chip Power Dissipation:<br>PINT = VDD x (IDD – S IOH) | PD     |      | Pint + Pi/o |      | w    |

| I/O Pin Power Dissipation:<br>I/O = S (({VDD – VOH} x IOH) + S (VOL x IOL))          |        |      |             |      |      |

| Maximum Allowed Power Dissipation                                                    | PDMAX  | (    | TJ — TA)/θJ | A    | W    |

#### TABLE 31-3: THERMAL PACKAGING CHARACTERISTICS

| Characteristics                                       | Symbol | Typical | Max. | Unit | Notes |

|-------------------------------------------------------|--------|---------|------|------|-------|

| Package Thermal Resistance, 64-pin QFN (9x9x0.9 mm)   | θJA    | 28      | _    | °C/W | 1     |

| Package Thermal Resistance, 64-pin TQFP (10x10x1 mm)  | θJA    | 47      | _    | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (12x12x1 mm) | θJA    | 43      | —    | °C/W | 1     |

| Package Thermal Resistance, 100-pin TQFP (14x14x1 mm) | θJA    | 43      | _    | °C/W | 1     |

| Package Thermal Resistance, 124-pin VTLA              | θJA    | 21      |      | °C/W | 1     |

**Note 1:** Junction to ambient thermal resistance, Theta-JA ( $\theta$ JA) numbers are achieved by package simulations.

| DC CHARACTERISTICS |       |                                   | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                     |                      |    |                                                                               |  |

|--------------------|-------|-----------------------------------|------------------------------------------------------|---------------------|----------------------|----|-------------------------------------------------------------------------------|--|

| Param.<br>No.      | Symb. | Characteristics                   | Min.                                                 | Тур. <sup>(1)</sup> | Max. Uni             |    | Conditions                                                                    |  |

|                    |       | Input Leakage Current<br>(Note 3) |                                                      |                     |                      |    |                                                                               |  |

| DI50               | lı∟   | I/O Ports                         | —                                                    | _                   | <u>+</u> 1           | μA | $Vss \le VPIN \le VDD,$ Pin at high-impedance                                 |  |

| DI51               |       | Analog Input Pins                 | —                                                    | —                   | <u>+</u> 1           | μA | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance                              |  |

| DI55               |       | MCLR <sup>(2)</sup>               | _                                                    |                     | <u>+</u> 1           | μA | $Vss \leq V \text{PIN} \leq V \text{DD}$                                      |  |

| DI56               |       | OSC1                              | —                                                    | —                   | <u>+</u> 1           | μA | $VSS \le VPIN \le VDD,$<br>XT and HS modes                                    |  |

|                    |       |                                   |                                                      |                     |                      |    | Pins with Analog functions.<br>Exceptions: [N/A] = 0 mA<br>max                |  |

| DI60a              | licl  | Input Low Injection<br>Current    | 0                                                    | _                   | <sub>-5</sub> (7,10) | mA | Digital 5V tolerant desig-<br>nated pins. Exceptions:<br>[N/A] = 0 mA max     |  |

|                    |       |                                   |                                                      |                     |                      |    | Digital non-5V tolerant desig-<br>nated pins. Exceptions:<br>[N/A] = 0 mA max |  |

### TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

- 7: VIL source < (VSS 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- **10:** Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (Vss 0.3)).

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

## TABLE 31-21: INTERNAL LPRC ACCURACY

| АС СНА                          | RACTERISTICS    | (unless | $\begin{tabular}{ l l l l l l l l l l l l l l l l l l l$ |      |       |            |  |  |

|---------------------------------|-----------------|---------|----------------------------------------------------------|------|-------|------------|--|--|

| Param.<br>No.                   | Characteristics | Min.    | Typical                                                  | Max. | Units | Conditions |  |  |

| LPRC @ 31.25 kHz <sup>(1)</sup> |                 |         |                                                          |      |       |            |  |  |

| F21                             | LPRC            | -15     | —                                                        | +15  | %     | —          |  |  |

Note 1: Change of LPRC frequency as VDD changes.

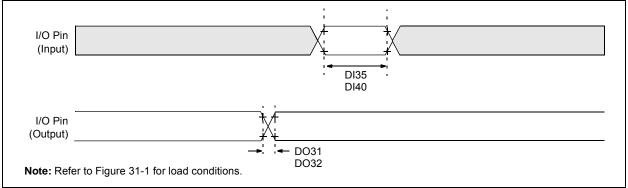

## FIGURE 31-3: I/O TIMING CHARACTERISTICS

## TABLE 31-22: I/O TIMING REQUIREMENTS

| AC CHAI       | RACTERIS | STICS                          | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |                        |         |            |            |  |

|---------------|----------|--------------------------------|------------------------------------------------------|------|------------------------|---------|------------|------------|--|

| Param.<br>No. | Symbol   | Characteristics <sup>(2)</sup> |                                                      | Min. | Typical <sup>(1)</sup> | Max.    | Units      | Conditions |  |

| DO31          | TIOR     | Port Output Rise Time          |                                                      | —    | 5                      | 15      | ns         | Vdd < 2.5V |  |

|               |          |                                |                                                      | _    | 5                      | 10      | ns         | Vdd > 2.5V |  |

| DO32          | TIOF     | Port Output Fall Time          |                                                      | _    | 5                      | 15      | ns         | VDD < 2.5V |  |

|               |          |                                | —                                                    | 5    | 10                     | ns      | VDD > 2.5V |            |  |

| DI35          | TINP     | INTx Pin High or Low Time      |                                                      | 10   | —                      | _       | ns         | —          |  |

| DI40          | Trbp     | CNx High or Low Tir            | 2                                                    | _    | _                      | TSYSCLK | _          |            |  |

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: This parameter is characterized, but not tested in manufacturing.

| AC CHA        | RACTER                 | ISTICS                        |                               | JIREMENTS (MASTER MODE)Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |      |                                            |                                         |  |  |

|---------------|------------------------|-------------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------------------------------------|-----------------------------------------|--|--|

| Param.<br>No. | Symbol Characteristics |                               |                               |                                                                                                                                                                                                                                   |      | ≤ TA ≤ +105°C for V-temp  nits  Conditions |                                         |  |  |

| IM10          | TLO:SCL                | Clock Low Time                | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                   |      | μS                                         |                                         |  |  |

|               | 1201002                |                               | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                   |      | μs                                         | _                                       |  |  |

|               |                        |                               | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                   |      | μs                                         | -                                       |  |  |

| IM11          | THI:SCL                | Clock High Time               | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                   | _    | μS                                         | <u> </u>                                |  |  |

|               |                        |                               | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                   | _    | μS                                         | _                                       |  |  |

|               |                        |                               | 1 MHz mode<br>(Note 2)        | Трв * (BRG + 2)                                                                                                                                                                                                                   |      | μs                                         | _                                       |  |  |

| IM20          | TF:SCL                 | SDAx and SCLx<br>Fall Time    | 100 kHz mode                  |                                                                                                                                                                                                                                   | 300  | ns                                         | CB is specified to be from 10 to 400 pF |  |  |

|               |                        |                               | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                       | 300  | ns                                         |                                         |  |  |

|               |                        |                               | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                                                 | 100  | ns                                         |                                         |  |  |

| IM21          | TR:SCL                 | SDAx and SCLx<br>Rise Time    | 100 kHz mode                  | —                                                                                                                                                                                                                                 | 1000 | ns                                         | CB is specified to be                   |  |  |

|               |                        |                               | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                       | 300  | ns                                         | from 10 to 400 pF                       |  |  |

|               |                        |                               | 1 MHz mode<br><b>(Note 2)</b> | —                                                                                                                                                                                                                                 | 300  | ns                                         |                                         |  |  |

| IM25          | Tsu:dat                | Data Input<br>Setup Time      | 100 kHz mode                  | 250                                                                                                                                                                                                                               | _    | ns                                         |                                         |  |  |

|               |                        |                               | 400 kHz mode                  | 100                                                                                                                                                                                                                               | —    | ns                                         |                                         |  |  |

|               |                        |                               | 1 MHz mode<br><b>(Note 2)</b> | 100                                                                                                                                                                                                                               | —    | ns                                         |                                         |  |  |

| IM26          | THD:DAT                | Data Input<br>Hold Time       | 100 kHz mode                  | 0                                                                                                                                                                                                                                 | —    | μS                                         | —                                       |  |  |

|               |                        |                               | 400 kHz mode                  | 0                                                                                                                                                                                                                                 | 0.9  | μS                                         | ]                                       |  |  |

|               |                        |                               | 1 MHz mode<br><b>(Note 2)</b> | 0                                                                                                                                                                                                                                 | 0.3  | μs                                         |                                         |  |  |

| IM30          | Tsu:sta                | Start Condition<br>Setup Time | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                   | —    | μS                                         | Only relevant for                       |  |  |

|               |                        |                               | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                   | —    | μs                                         | Repeated Start                          |  |  |

|               |                        |                               | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                   |      | μs                                         | condition                               |  |  |

| IM31          | Thd:sta                | Start Condition<br>Hold Time  | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                   | —    | μS                                         | After this period, the                  |  |  |

|               |                        |                               | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                   |      | μS                                         | first clock pulse is                    |  |  |

|               |                        |                               | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                   | —    | μs                                         | generated                               |  |  |

| IM33          | Tsu:sto                | Stop Condition<br>Setup Time  | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                   | —    | μS                                         | —                                       |  |  |

|               |                        |                               | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                   |      | μS                                         |                                         |  |  |

|               |                        |                               | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                   | _    | μs                                         |                                         |  |  |

## TABLE 31-33: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

**Note 1:** BRG is the value of the  $l^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

# PIC32MX330/350/370/430/450/470

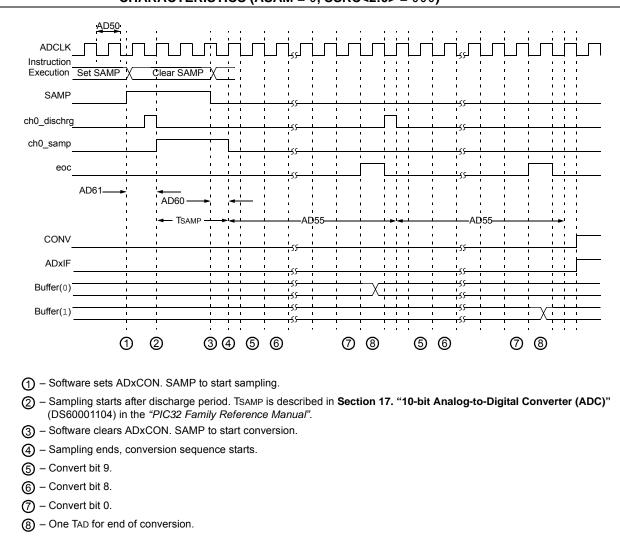

## FIGURE 31-18: ANALOG-TO-DIGITAL CONVERSION (10-BIT MODE) TIMING CHARACTERISTICS (ASAM = 0, SSRC<2:0> = 000)

# APPENDIX A: REVISION HISTORY

## Revision A (July 2012)

This is the initial released version of the document.

## Revision B (April 2013)

| Note: | The status of this data sheet was updated<br>to Preliminary; however, any electrical<br>specifications listed for PIC32MX370/470 |  |  |  |  |  |

|-------|----------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|       | devices is to be considered Advance                                                                                              |  |  |  |  |  |

|       | Information and is marked accordingly.                                                                                           |  |  |  |  |  |

This revision includes the following updates, as shown in Table A-1.

## TABLE A-1: MAJOR SECTION UPDATES

| Section                                                                                    | Update Description                                                                                             |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 512                                                        | SRAM was changed from 32 KB to 64 KB.                                                                          |

| KB Flash and 128 KB SRAM) with<br>Audio/Graphics/Touch (HMI), USB,<br>and Advanced Analog" | Data Memory (KB) was changed from 32 to 64 for the following devices (see Table 1):                            |

|                                                                                            | • PIC32MX350F256H                                                                                              |

|                                                                                            | • PIC32MX350F256L                                                                                              |

|                                                                                            | • PIC32MX450F256H                                                                                              |

|                                                                                            | • PIC32MX450F256L                                                                                              |

|                                                                                            | The following devices were added:                                                                              |