#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 128KB (128K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 32K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                               |

| Supplier Device Package    | 124-VTLA (9x9)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f128l-i-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Numb        | er                                 |             |                |                                                                                                  |

|----------|------------------------|-----------------|------------------------------------|-------------|----------------|--------------------------------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA                    | Pin<br>Type | Buffer<br>Type | Description                                                                                      |

| CVREF-   | 15                     | 28              | A21                                | I           | Analog         | Comparator Voltage Reference (Low)                                                               |

| CVREF+   | 16                     | 29              | B17                                | Ι           | Analog         | Comparator Voltage Reference (High)                                                              |

| CVREFOUT | 23                     | 34              | A24                                | Ι           | Analog         | Comparator Voltage Reference (Output)                                                            |

| C1INA    | 11                     | 20              | A12                                | I           | Analog         |                                                                                                  |

| C1INB    | 12                     | 21              | B11                                | I           | Analog         | Comparator 1 Inputa                                                                              |

| C1INC    | 5                      | 11              | B6                                 | I           | Analog         | Comparator 1 Inputs                                                                              |

| C1IND    | 4                      | 10              | A7                                 | I           | Analog         |                                                                                                  |

| C2INA    | 13                     | 22              | A13                                | Ι           | Analog         |                                                                                                  |

| C2INB    | 14                     | 23              | B13                                | Ι           | Analog         |                                                                                                  |

| C2INC    | 8                      | 14              | A9                                 | Ι           | Analog         | Comparator 2 Inputs                                                                              |

| C2IND    | 6                      | 12              | A8                                 | I           | Analog         | 1                                                                                                |

| C1OUT    | PPS                    | PPS             | PPS                                | 0           |                | Comparator 1 Output                                                                              |

| C2OUT    | PPS                    | PPS             | PPS                                | 0           |                | Comparator 2 Output                                                                              |

| PMALL    | 30                     | 44              | A29                                | 0           | TTL/ST         | Parallel Master Port Address Latch Enable Low Byte                                               |

| PMALH    | 29                     | 43              | B24                                | 0           | TTL/ST         | Parallel Master Port Address Latch Enable High Byte                                              |

| PMA0     | 30                     | 44              | A29                                | 0           | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes)        |

| PMA1     | 29                     | 43              | B24                                | 0           | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes)        |

| PMA2     | 8                      | 14              | A9                                 | 0           | TTL/ST         |                                                                                                  |

| PMA3     | 6                      | 12              | A8                                 | 0           | TTL/ST         |                                                                                                  |

| PMA4     | 5                      | 11              | B6                                 | 0           | TTL/ST         |                                                                                                  |

| PMA5     | 4                      | 10              | A7                                 | 0           | TTL/ST         |                                                                                                  |

| PMA6     | 16                     | 29              | B17                                | 0           | TTL/ST         |                                                                                                  |

| PMA7     | 22                     | 28              | A21                                | 0           | TTL/ST         |                                                                                                  |

| PMA8     | 32                     | 50              | A32                                | 0           | TTL/ST         |                                                                                                  |

| PMA9     | 31                     | 49              | B27                                | 0           | TTL/ST         |                                                                                                  |

| PMA10    | 28                     | 42              | A28                                | 0           | TTL/ST         | Devellet Meeter Dert date (Develtingered Meeter                                                  |

| PMA11    | 27                     | 41              | B23                                | 0           | TTL/ST         | Parallel Master Port data (Demultiplexed Master mode) or Address/Data (Multiplexed Master modes) |

| PMA12    | 24                     | 35              | B20                                | 0           | TTL/ST         |                                                                                                  |

| PMA13    | 23                     | 34              | A24                                | 0           | TTL/ST         | ]                                                                                                |

| PMA14    | 45                     | 71              | A46                                | 0           | TTL/ST         | ]                                                                                                |

| PMA15    | 44                     | 70              | B38                                | 0           | TTL/ST         | ]                                                                                                |

| PMCS1    | 45                     | 71              | A46                                | 0           | TTL/ST         | ]                                                                                                |

| PMCS2    | 44                     | 70              | B38                                | 0           | TTL/ST         | ]                                                                                                |

| PMD0     | 60                     | 93              | B52                                | I/O         | TTL/ST         | 1                                                                                                |

| PMD1     | 61                     | 94              | A64                                | I/O         | TTL/ST         | 1                                                                                                |

| PMD2     | 62                     | 98              | A66                                | I/O         | TTL/ST         | 1                                                                                                |

|          | ST = Schmi             |                 | tible input or ou<br>out with CMOS |             |                | alog = Analog input P = Power<br>= Output I = Input                                              |

#### TARI E 1-1. PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices.

|          |                        | Pin Numb                 | er                                                  |             |                |                                                                                 |  |  |

|----------|------------------------|--------------------------|-----------------------------------------------------|-------------|----------------|---------------------------------------------------------------------------------|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP          | 124-pin<br>VTLA                                     | Pin<br>Type | Buffer<br>Type | Description                                                                     |  |  |

| CTED4    | 22                     | 33                       | B19                                                 | 1           | ST             | CTMU External Edge Input 4                                                      |  |  |

| CTED5    | 29                     | 43                       | B24                                                 | I           | ST             | CTMU External Edge Input 5                                                      |  |  |

| CTED6    | 30                     | 44                       | A29                                                 | I           | ST             | CTMU External Edge Input 6                                                      |  |  |

| CTED7    | —                      | 9                        | B5                                                  | I           | ST             | CTMU External Edge Input 7                                                      |  |  |

| CTED8    | —                      | 92                       | A62                                                 | I           | ST             | CTMU External Edge Input 8                                                      |  |  |

| CTED9    | —                      | 60                       | A40                                                 | I           | ST             | CTMU External Edge Input 9                                                      |  |  |

| CTED10   | 21                     | 32                       | A23                                                 | I           | ST             | CTMU External Edge Input 10                                                     |  |  |

| CTED11   | 23                     | 34                       | A24                                                 | I           | ST             | CTMU External Edge Input 11                                                     |  |  |

| CTED12   | 15                     | 24                       | A15                                                 | I           | ST             | CTMU External Edge Input 12                                                     |  |  |

| CTED13   | 14                     | 23                       | B13                                                 | I           | ST             | CTMU External Edge Input 13                                                     |  |  |

| MCLR     | 7                      | 13                       | B7                                                  | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device.      |  |  |

| AVdd     | 19                     | 30                       | A22                                                 | Р           | Р              | Positive supply for analog modules. This pin must be<br>connected at all times. |  |  |

| AVss     | 20                     | 31                       | B18                                                 | Р           | Р              | Ground reference for analog modules                                             |  |  |

| Vdd      | 10, 26, 38,<br>57      | 2, 16, 37,<br>46, 62, 86 | B1, A10, A14,<br>B21, A30,<br>A41, A48,<br>A59, B53 | Ρ           | _              | Positive supply for peripheral logic and I/O pins                               |  |  |

| Vcap     | 56                     | 85                       | B48                                                 | Р           | —              | Capacitor for Internal Voltage Regulator                                        |  |  |

| Vss      | 9, 25, 41              | 15, 36, 45,<br>65, 75    | A3, B8, B12,<br>A25, B25,<br>A43, B41,<br>A63       | Ρ           | _              | Ground reference for logic and I/O pins                                         |  |  |

| VREF+    | 16                     | 29                       | B17                                                 | I           | Analog         | Analog Voltage Reference (High) Input                                           |  |  |

| Vref-    | 15                     | 28                       | A21                                                 | Ι           | Analog         | Analog Voltage Reference (Low) Input                                            |  |  |

#### TARI E 1-1. PINOLIT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

Analog = Analog input O = Output

I = Input

Note 1: This pin is only available on devices without a USB module.

This pin is only available on devices with a USB module. 2:

3: This pin is not available on 64-pin devices.

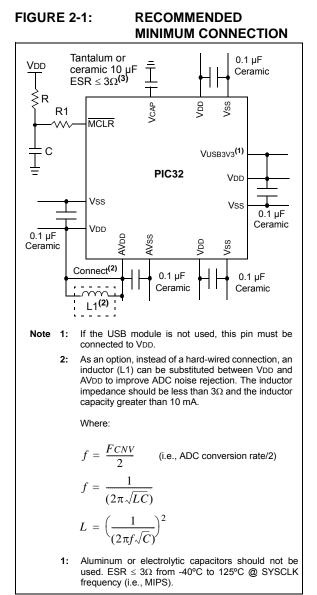

## 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F. This capacitor should be located as close to the device as possible.

# 2.3 Capacitor on Internal Voltage Regulator (VCAP)

### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (3 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 31.0 "Electrical Characteristics"** for additional information on CEFC specifications.

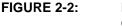

## 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides two specific device functions:

- Device Reset

- · Device programming and debugging

Pulling The  $\overline{\text{MCLR}}$  pin low generates a device Reset. Figure 2-2 illustrates a typical  $\overline{\text{MCLR}}$  circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

3:

## EXAMPLE OF MCLR PIN CONNECTIONS

No pull-ups or bypass capacitors are allowed on

active debug/program PGECx/PGEDx pins.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 31:24        | BMXDRMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 23:16        | BMXDRMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 15:8         | BMXDRMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 7:0          |                   |                   |                   | BMXDR             | MSZ<7:0>          |                   |                  |                  |  |  |  |  |

#### BMXDRMSZ: DATA RAM SIZE REGISTER **REGISTER 4-5:**

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXDRMSZ<31:0>: Data RAM Memory (DRM) Size bits

Static value that indicates the size of the Data RAM in bytes: 0x00004000 = Device has 16 KB RAM 0x00008000 = Device has 32 KB RAM 0x00010000 = Device has 64 KB RAM 0x00020000 = Device has 128 KB RAM

#### **REGISTER 4-6: BMXPUPBA: PROGRAM FLASH (PFM) USER PROGRAM BASE ADDRESS** REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | —                 | _                 | —                 | —                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | _                 | _                 | _                 | _                 | BMXPUPBA<19:16>   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0               | R-0              | R-0              |  |  |

| 15:8         |                   |                   |                   | BMXPU             | PBA<15:8>         |                   |                  |                  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   |                   |                   | BMXPU             | PBA<7:0>          |                   |                  |                  |  |  |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-20 Unimplemented: Read as '0'

bit 19-11 BMXPUPBA<19:11>: Program Flash (PFM) User Program Base Address bits

## bit 10-0 BMXPUPBA<10:0>: Read-Only bits Value is always '0', which forces 2 KB increments

Note 1: At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXPFMSZ.

NOTES:

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 18-16 PLLMULT<2:0>: Phase-Locked Loop (PLL) Multiplier bits

- 111 = Clock is multiplied by 24

- 110 = Clock is multiplied by 21

- 101 = Clock is multiplied by 20

- 100 = Clock is multiplied by 19

- 011 = Clock is multiplied by 18

- 010 = Clock is multiplied by 17

- 001 = Clock is multiplied by 16

- 000 =Clock is multiplied by 15

- bit 15 Unimplemented: Read as '0'

- bit 14-12 COSC<2:0>: Current Oscillator Selection bits

- 111 = Internal Fast RC (FRC) Oscillator divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC (FRC) Oscillator divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (Posc) (XT, HS or EC)

- 001 = Internal Fast RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast RC (FRC) Oscillator

- bit 11 Unimplemented: Read as '0'

- bit 10-8 NOSC<2:0>: New Oscillator Selection bits

- 111 = Internal Fast RC Oscillator (FRC) divided by OSCCON<FRCDIV> bits

- 110 = Internal Fast RC Oscillator (FRC) divided by 16

- 101 = Internal Low-Power RC (LPRC) Oscillator

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator with PLL module (XTPLL, HSPLL or ECPLL)

- 010 = Primary Oscillator (XT, HS or EC)

- 001 = Internal Fast Internal RC Oscillator with PLL module via Postscaler (FRCPLL)

- 000 = Internal Fast Internal RC Oscillator (FRC)

On Reset, these bits are set to the value of the FNOSC Configuration bits (DEVCFG1<2:0>).

- bit 7 CLKLOCK: Clock Selection Lock Enable bit

- If clock switching and monitoring is disabled (FCKSM<1:0> = 1x):

- 1 = Clock and PLL selections are locked

- 0 = Clock and PLL selections are not locked and may be modified

If clock switching and monitoring is enabled (FCKSM<1:0> = 0x): Clock and PLL selections are never locked and may be modified.

- bit 6 ULOCK: USB PLL Lock Status bit<sup>(1)</sup>

- 1 = Indicates that the USB PLL module is in lock or USB PLL module start-up timer is satisfied

- 0 = Indicates that the USB PLL module is out of lock or USB PLL module start-up timer is in progress or USB PLL is disabled

- bit 5 SLOCK: PLL Lock Status bit

- 1 = PLL module is in lock or PLL module start-up timer is satisfied

- 0 = PLL module is out of lock, PLL start-up timer is running or PLL is disabled

- bit 4 **SLPEN:** Sleep Mode Enable bit

- 1 = Device will enter Sleep mode when a WAIT instruction is executed

- 0 = Device will enter Idle mode when a WAIT instruction is executed

- bit 3 CF: Clock Fail Detect bit

- 1 = FSCM has detected a clock failure

- 0 = No clock failure has been detected

- **Note 1:** This bit is available on PIC32MX4XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 51.24        | LTAGBOOT          | —                 | —                 | —                 | —                 | -                 | _                | —                |  |  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23.10        | LTAG<19:12>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 15:0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | LTAG<11:4>        |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-0             | R/W-0             | R/W-1            | U-0              |  |  |

| 7.0          |                   | LTAG<             | <3:0>             |                   | LVALID            | LLOCK             | LTYPE            | —                |  |  |

### **REGISTER 9-3: CHETAG: CACHE TAG REGISTER**

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

### bit 31 LTAGBOOT: Line TAG Address Boot bit

- 1 = The line is in the 0x1D000000 (physical) area of memory

- 0 = The line is in the 0x1FC00000 (physical) area of memory

#### bit 30-24 Unimplemented: Write '0'; ignore read

#### bit 23-4 LTAG<19:0>: Line TAG Address bits

LTAG<19:0> bits are compared against physical address to determine a hit. Because its address range and position of PFM in kernel space and user space, the LTAG PFM address is identical for virtual addresses, (system) physical addresses, and PFM physical addresses.

#### bit 3 LVALID: Line Valid bit

- 1 = The line is valid and is compared to the physical address for hit detection

- 0 = The line is not valid and is not compared to the physical address for hit detection

### bit 2 LLOCK: Line Lock bit

- 1 = The line is locked and will not be replaced

- 0 = The line is not locked and can be replaced

#### bit 1 LTYPE: Line Type bit

- 1 = The line caches instruction words

- 0 = The line caches data words

- bit 0 Unimplemented: Write '0'; ignore read

'0' = Bit is cleared

x = Bit is unknown

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 21.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 31:24        | CHEHIT<31:24>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 23:16        |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 15:8         | CHEHIT<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |  |

| 7:0          |                   |                   |                   | CHEHIT            | <7:0>             |                   |                  |                  |  |  |  |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| R = Rea      | eadable bit       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

### REGISTER 9-10: CHEHIT: CACHE HIT STATISTICS REGISTER

### bit 31-0 CHEHIT<31:0>: Cache Hit Count bits

-n = Value at POR

Incremented each time the processor issues an instruction fetch or load that hits the prefetch cache from a cacheable region. Non-cacheable accesses do not modify this value.

'1' = Bit is set

|              |                   |                   |                   |                   |                   | •                 |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                   |                   |                   | CHEMIS            | <31:24>           |                   |                  |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                   |                   |                   | CHEMIS            | <23:16>           |                   |                  |                  |  |  |

|              | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | CHEMIS<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          | CHEMIS<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| R = Rea      | dable bit         |                   | W = Writable      | bit               | U = Unimple       | emented bit, re   | ead as '0'       |                  |  |  |

| -n = Valu    | e at POR          |                   | '1' = Bit is se   | t                 | '0' = Bit is cl   | eared             | x = Bit is unl   | known            |  |  |

#### bit 31-0 CHEMIS<31:0>: Cache Miss Count bits

Incremented each time the processor issues an instruction fetch from a cacheable region that misses the prefetch cache. Non-cacheable accesses do not modify this value.

## 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32 USB module includes the following features:

- USB full-speed support for host and device

- Low-speed host support

- USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, and other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

### TABLE 12-8: PORTD REGISTER MAP FOR PIC32MX330F064H, PIC32MX350F128H, PIC32MX350F256H, PIC32MX370F512H, PIC32MX430F064H, PIC32MX450F128H, PIC32MX450F256H, PIC32MX470F512H DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |               |               |              | В            | its          |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                          | 31:16     | _     | —     | —     | —     | _             | -             | —            | _            | —            | _            | —            | _            | _            | —            | —            |              | 0000          |

| 0000                        | ANOLLD                          | 15:0      | —     | —     | _     | —     |               | _             |              | _            | —            | _            |              |              | ANSELD3      | ANSELD2      | ANSELD1      |              | 000E          |

| 6310                        | TRISD                           | 31:16     | _     | —     | _     | —     | _             |               | _            | —            | _            | —            | _            | _            | _            | —            | —            |              | 0000          |

| 00.0                        |                                 | 15:0      | —     | —     | —     | —     | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | xxxx          |

| 5320                        | PORTD                           | 31:16     | —     | —     | —     | —     | —             |               | —            | —            | —            | —            | —            | —            | —            | —            | —            |              | 0000          |

| 0020                        |                                 | 15:0      | —     | —     | —     | —     | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | xxxx          |

| 6330                        | LATD                            | 31:16     | —     | —     | —     | —     | —             |               | —            | —            | —            | —            | —            | —            | —            | —            | —            |              | 0000          |

|                             |                                 | 15:0      | —     | —     | —     | —     | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | xxxx          |

| 6340                        | ODCD                            | 31:16     | —     | —     | —     | —     | _             | —             | _            | —            | —            | —            | —            | —            | —            | —            | _            |              | 0000          |

|                             |                                 | 15:0      | —     | —     | —     | —     | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | xxxx          |

| 6350                        | CNPUD                           | 31:16     | —     | —     | —     | —     | _             | —             | _            | —            | —            | —            | —            | —            | —            | —            | _            |              | 0000          |

|                             |                                 | 15:0      | —     | —     | —     | —     | CNPUD11       | CNPUD10       | CNPUD9       | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | xxxx          |

| 6360                        | CNPDD                           | 31:16     | —     | —     | —     | —     | _             | —             | _            | —            | —            | —            | —            | —            | —            | —            | _            |              | 0000          |

|                             |                                 | 15:0      | —     | —     | —     | —     | CNPDD11       | CNPDD10       | CNPDD9       | CNPDD8       | CNPDD7       | CNPDD6       | CNPDD5       | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | xxxx          |

| 6370                        | CNCOND                          | 31:16     | —     | —     | —     | —     | _             | —             | —            | _            | —            | _            | _            | _            | _            | —            | —            |              | 0000          |

|                             |                                 | 15:0      | ON    | —     | SIDL  | —     | _             | —             | —            | _            | —            | _            | _            | _            | _            | —            | —            |              | 0000          |

| 6380                        | CNEND                           | 31:16     | —     | —     | —     | —     | _             | -             | —            | -            | —            | -            | —            | —            | -            | —            | —            | -            | 0000          |

|                             | 0.12.10                         | 15:0      | —     | —     | —     | —     | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | xxxx          |

|                             |                                 | 31:16     | _     | _     | _     | _     | —             | _             | —            | —            | —            | —            | —            | —            | —            | —            | —            | _            | 0000          |

| 6390                        | CNSTATD                         | 15:0      | _     | —     | —     | —     | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | xxxx          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

# TABLE 12-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| 2012-2016  |  |

|------------|--|

| Microchip  |  |

| Technology |  |

| Inc        |  |

0

| SS                          |                       |               |       |               |       |       |       |       |      | Bi   | ts   |      |      |      |      |          |           |      |            |

|-----------------------------|-----------------------|---------------|-------|---------------|-------|-------|-------|-------|------|------|------|------|------|------|------|----------|-----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14         | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2     | 17/1      | 16/0 | All Resets |

| FC14                        | RPE5R                 | 31:16         |       | —             | —     | —     | —     | _     | —    |      | _    | _    | —    |      | _    | _        | —         | _    | 0000       |

|                             |                       | 15:0          | —     | —             | —     | —     | —     | _     | —    | —    | —    | _    | —    | _    |      | RPE5     | <3:0>     |      | 0000       |

| FC20                        | RPE8R <sup>(1)</sup>  | 31:16         | _     | —             | _     |       |       | _     | —    |      | _    |      |      | _    | _    | -        | -         | —    | 0000       |

|                             |                       | 15:0<br>31:16 |       |               |       |       |       |       |      |      |      |      |      |      |      | RPE8     | <3:0>     | _    | 0000       |

| FC24                        | RPE9R <sup>(1)</sup>  | 15:0          | _     | _             | _     |       | _     |       |      |      |      | _    | _    | _    | _    | <br>RPE9 | <3:0>     | _    | 0000       |

|                             |                       | 31:16         |       | _             | _     |       | _     | _     | _    |      |      | _    | _    | _    | _    |          | _         | _    | 0000       |

| FC40                        | RPF0R                 | 15:0          | _     | _             | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF0     | <3:0>     |      | 0000       |

|                             |                       | 31:16         | _     | _             | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _        | _         | _    | 0000       |

| FC44                        | RPF1R                 | 15:0          | _     | _             | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF1     | <3:0>     |      | 0000       |

| FC48                        | RPF2R <sup>(3)</sup>  | 31:16         | —     | —             | —     | —     | _     | _     | —    | _    |      | _    | —    | —    |      | —        | _         | _    | 0000       |

| FC40                        | RPF2R**               | 15:0          | _     | _             | _     | -     | -     | -     | _    | —    | _    |      | -    | _    |      | RPF2     | <3:0>     |      | 0000       |

| FC4C                        | RPF3R <sup>(2)</sup>  | 31:16         | —     | —             | —     |       |       | _     | —    | _    | —    |      |      | —    | —    | —        | —         | —    | 0000       |

| 1 040                       |                       | 15:0          | —     | —             | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | RPF3     | <3:0>     |      | 0000       |

| FC50                        | RPF4R                 | 31:16         | —     | —             | —     | —     | —     | _     | —    | _    | —    | _    | —    | —    | —    | —        | —         | —    | 0000       |

| 1000                        |                       | 15:0          | -     | —             | —     | —     | —     | _     | —    | _    | —    |      | —    | _    |      | RPF4     | <3:0>     |      | 0000       |

| FC54                        | RPF5R                 | 31:16         | —     | _             | _     | —     |       | _     | _    | —    | —    |      | —    | _    | —    |          |           | —    | 0000       |

|                             |                       | 15:0          | -     | _             | -     | —     | —     | _     | _    | _    | -    | -    | —    | _    |      | RPF5     | <3:0>     |      | 0000       |

| FC58                        | RPF6R <sup>(2)</sup>  | 31:16         | _     | _             | _     | _     |       | _     | _    |      |      | _    | _    | _    |      |          | -         |      | 0000       |

|                             |                       | 15:0<br>31:16 | _     |               |       |       |       |       |      | _    |      |      |      | _    |      | RPF6     |           |      | 0000       |

| FC60                        | RPF8R <sup>(1)</sup>  | 15:0          |       |               |       |       |       |       |      |      |      |      |      |      |      | <br>RPF8 |           | —    | 0000       |

|                             |                       | 31:16         |       |               |       |       |       |       |      |      |      |      |      |      |      |          | < <u></u> |      | 0000       |

| FC70                        | RPF12R <sup>(1)</sup> | 15:0          | _     | _             | _     | _     | _     |       | _    | _    |      |      | _    | _    |      | RPF12    | 2<3:0>    |      | 0000       |

|                             | (4)                   | 31:16         | _     |               |       |       |       | _     |      | _    | _    | _    |      | _    |      | _        | _         | _    | 0000       |

| FC74                        | RPF13R <sup>(1)</sup> | 15:0          | _     | _             | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF1     | 3<3:0>    |      | 0000       |

|                             | 55665(1)              | 31:16         | _     | _             |       |       | _     | _     | _    | _    | _    | _    | _    | _    |      | _        |           | _    | 0000       |

| FC80                        | RPG0R <sup>(1)</sup>  | 15:0          | _     | —             | _     | —     | —     | _     | —    | _    | _    | _    | —    | _    |      | RPG0     | <3:0>     |      | 0000       |

| FC84                        | RPG1R <sup>(1)</sup>  | 31:16         |       | —             |       | _     | _     |       | —    |      |      |      | _    | -    |      |          |           | _    | 0000       |

| FU04                        | RPGIR''               | 15:0          |       | _             | —     | _     | _     | _     | _    |      |      | -    | _    | _    |      | RPG1     | <3:0>     |      | 0000       |

| FC98                        | RPG6R                 | 31:16         | —     | —             | _     | —     | —     | _     | —    | —    | _    | -    | —    | —    | _    | —        |           |      | 0000       |

| 1090                        |                       | 15:0          |       | —             | _     | _     | _     | _     | —    |      | _    | _    | —    | —    |      | RPG6     | <3:0>     |      | 0000       |

| FC9C                        | RPG7R                 | 31:16         | _     | —             | —     | _     | —     | _     | —    | _    | —    |      | —    | _    | _    |          | —         | —    | 0000       |

|                             |                       | 15:0          | —     | <br>set; = ur | —     | —     | —     | —     | —    | _    | _    | _    | _    | —    |      | RPG7     | <3:0>     |      | 0000       |

**Note 1:** This register is not available on 64-pin devices.

2: This register is only available on devices without a USB module.

3: This register is not available on 64-pin devices with a USB module.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                   | —                 | _                 | _                 | _                 | —                 | _                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | —                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          |                     |                   | S                 | WDTPS<4:0         | >                 |                   | WDTWINEN         | WDTCLR           |

## REGISTER 15-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                                       |                    |  |  |  |  |

|-------------------|-----------------------------------------------|---------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit                              | it U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared                  | x = Bit is unknown |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 WDTCLR: Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## REGISTER 21-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 5-2 WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup>

- 1111 = Wait of 16 Трв • •

- 0001 = Wait of 2 Трв 0000 = Wait of 1 Трв (default)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Wait of 4 TPB 10 = Wait of 3 TPB 01 = Wait of 2 TPB

- 00 = Wait of 1 Трв (default)

For Read operations: 11 = Wait of 3 TPB 10 = Wait of 2 TPB 01 = Wait of 1 TPB 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPB cycle for a write operation; WAITB = 1 TPB cycle, WAITE = 0 TPB cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- **3:** These pins are active when MODE16 = 1 (16-bit mode).

|              |                   | ICDAIL. N         |                   |                   |                   |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                   | YEAR1             | 0<3:0>            |                   | YEAR0             | 1<3:0>            |                  |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                   | MONTH             | 10<3:0>           |                   | MONTH01<3:0>      |                   |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   | DAY10             | <3:0>             |                   |                   | DAY01             | <3:0>            |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          |                   | _                 | _                 | —                 |                   | WDAYO             | )1<3:0>          |                  |  |  |

|              |                   |                   |                   |                   | •                 |                   |                  |                  |  |  |

| Legend:      |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ead as '0'       |                  |  |  |

| -n = Value   | e at POR          |                   | '1' = Bit is se   | et                | '0' = Bit is cl   | eared             | x = Bit is un    | known            |  |  |

## REGISTER 22-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digits

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1s place digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1s place digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

| Bit<br>Range    | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|-----------------|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04           | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24 CH0NB — — |                      |                   |                   |                   |                   | CH0SB<4:0>        |                  |                  |  |  |  |

| 00.40           | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16           | CH0NA <sup>(3)</sup> | _                 | —                 |                   |                   |                   |                  |                  |  |  |  |

| 45.0            | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8            | —                    | -                 | —                 | _                 | _                 |                   | _                | _                |  |  |  |

| 7:0             | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 7:0             | _                    | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

### REGISTER 23-4: AD1CHS: ADC INPUT SELECT REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

| bit 31    | CH0NB: Negative Input Select bit for Sample B                                      |

|-----------|------------------------------------------------------------------------------------|

|           | 1 = Channel 0 negative input is AN1                                                |

|           | 0 = Channel 0 negative input is VREFL                                              |

| bit 30-29 | Unimplemented: Read as '0'                                                         |

| bit 28-24 | CH0SB<4:0>: Positive Input Select bits for Sample B                                |

|           | 11110 = Channel 0 positive input is Open <sup>(1)</sup>                            |

|           | 11101 = Channel 0 positive input is CTMU temperature sensor (CTMUT) <sup>(2)</sup> |

|           | 11100 = Channel 0 positive input is IVREF <sup>(3)</sup>                           |

|           | 11011 = Channel 0 positive input is AN27                                           |

|           | •                                                                                  |

|           | •                                                                                  |

|           | •                                                                                  |

|           | 00001 = Channel 0 positive input is AN1                                            |

|           | 00000 = Channel 0 positive input is AN0                                            |

| bit 23    | CH0NA: Negative Input Select bit for Sample A Multiplexer Setting <sup>(3)</sup>   |

|           | 1 = Channel 0 negative input is AN1                                                |

|           | 0 = Channel 0 negative input is VREFL                                              |

| bit 22-21 | Unimplemented: Read as '0'                                                         |

| bit 20-16 | CH0SA<4:0>: Positive Input Select bits for Sample A Multiplexer Setting            |

|           | 11110 = Channel 0 positive input is Open <sup>(1)</sup>                            |

|           | 11101 = Channel 0 positive input is CTMU temperature sensor (CTMUT) <sup>(2)</sup> |

|           | 11100 = Channel 0 positive input is IVREF <sup>(3)</sup>                           |

|           | 11011 = Channel 0 positive input is AN27                                           |

|           | •                                                                                  |

|           | •                                                                                  |

|           | •                                                                                  |

|           | 00001 = Channel 0 positive input is AN1                                            |

|           | 00000 = Channel 0 positive input is AN0                                            |

| bit 15-0  | Unimplemented: Read as '0'                                                         |

| Note 1:   | This selection is only used with CTMU capacitive and time measurement.             |

| 2:        | See Section 26.0 "Charge Time Measurement Unit (CTMU)" for more information.       |

3: See Section 25.0 "Comparator Voltage Reference (CVREF)" for more information.

## 27.0 POWER-SAVING FEATURES

| Note: | This data sheet summarizes the features<br>of the PIC32MX330/350/370/430/450/470<br>family of devices. It is not intended to be a<br>comprehensive reference source. To<br>complement the information in this data<br>sheet, refer to <b>Section 10.</b> " <b>Power-</b><br><b>Saving Features</b> " (DS60001130), which<br>is available from the <i>Documentation</i> ><br><i>Reference Manual</i> section of the<br>Microphin PIC22 work arite |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       |                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|       | (www.microchip.com/pic32).                                                                                                                                                                                                                                                                                                                                                                                                                       |

This section describes power-saving features for the PIC32MX330/350/370/430/450/470 family of devices. These PIC32 devices offer a total of nine methods and modes, organized into two categories, that allow the user to balance power consumption with device performance. In all of the methods and modes described in this section, power-saving is controlled by software.

## 27.1 Power Saving with CPU Running

When the CPU is running, power consumption can be controlled by reducing the CPU clock frequency, lowering the PBCLK and by individually disabling modules. These methods are grouped into the following categories:

- FRC Run mode: the CPU is clocked from the FRC clock source with or without postscalers.

- LPRC Run mode: the CPU is clocked from the LPRC clock source.

- Sosc Run mode: the CPU is clocked from the Sosc clock source.

In addition, the Peripheral Bus Scaling mode is available where peripherals are clocked at the programmable fraction of the CPU clock (SYSCLK).

## 27.2 CPU Halted Methods

The device supports two power-saving modes, Sleep and Idle, both of which Halt the clock to the CPU. These modes operate with all clock sources, as listed below:

- Posc Idle mode: the system clock is derived from the Posc. The system clock source continues to operate. Peripherals continue to operate, but can optionally be individually disabled.

- FRC Idle mode: the system clock is derived from the FRC with or without postscalers. Peripherals continue to operate, but can optionally be individually disabled.

- Sosc Idle mode: the system clock is derived from the Sosc. Peripherals continue to operate, but can optionally be individually disabled.

- LPRC Idle mode: the system clock is derived from the LPRC. Peripherals continue to operate, but can optionally be individually disabled. This is the lowest power mode for the device with a clock

running.

• Sleep mode: the CPU, the system clock source and any peripherals that operate from the system clock source are Halted. Some peripherals can operate in Sleep using specific clock sources. This is the lowest power mode for the device.

## 27.3 Power-Saving Operation

Peripherals and the CPU can be Halted or disabled to further reduce power consumption.

## 27.3.1 SLEEP MODE

Sleep mode has the lowest power consumption of the device power-saving operating modes. The CPU and most peripherals are Halted. Select peripherals can continue to operate in Sleep mode and can be used to wake the device from Sleep. See the individual peripheral module sections for descriptions of behavior in Sleep.

Sleep mode includes the following characteristics:

- The CPU is Halted.

- The system clock source is typically shutdown. See Section 27.3.3 "Peripheral Bus Scaling Method" for specific information.

- There can be a wake-up delay based on the oscillator selection.

- The Fail-Safe Clock Monitor (FSCM) does not operate during Sleep mode.

- The BOR circuit remains operative during Sleep mode.

- The WDT, if enabled, is not automatically cleared prior to entering Sleep mode.

- Some peripherals can continue to operate at limited functionality in Sleep mode. These peripherals include I/O pins that detect a change in the input signal, WDT, ADC, UART and peripherals that use an external clock input or the internal LPRC oscillator (e.g., RTCC, Timer1 and Input Capture).

- I/O pins continue to sink or source current in the same manner as they do when the device is not in Sleep.

- The USB module can override the disabling of the Posc or FRC. Refer to the USB section for specific details.

- Modules can be individually disabled by software prior to entering Sleep in order to further reduce consumption.

## 30.6 MPLAB X SIM Software Simulator

The MPLAB X SIM Software Simulator allows code development in a PC-hosted environment by simulating the PIC MCUs and dsPIC DSCs on an instruction level. On any given instruction, the data areas can be examined or modified and stimuli can be applied from a comprehensive stimulus controller. Registers can be logged to files for further run-time analysis. The trace buffer and logic analyzer display extend the power of the simulator to record and track program execution, actions on I/O, most peripherals and internal registers.

The MPLAB X SIM Software Simulator fully supports symbolic debugging using the MPLAB XC Compilers, and the MPASM and MPLAB Assemblers. The software simulator offers the flexibility to develop and debug code outside of the hardware laboratory environment, making it an excellent, economical software development tool.

## 30.7 MPLAB REAL ICE In-Circuit Emulator System

The MPLAB REAL ICE In-Circuit Emulator System is Microchip's next generation high-speed emulator for Microchip Flash DSC and MCU devices. It debugs and programs all 8, 16 and 32-bit MCU, and DSC devices with the easy-to-use, powerful graphical user interface of the MPLAB X IDE.

The emulator is connected to the design engineer's PC using a high-speed USB 2.0 interface and is connected to the target with either a connector compatible with in-circuit debugger systems (RJ-11) or with the new high-speed, noise tolerant, Low-Voltage Differential Signal (LVDS) interconnection (CAT5).

The emulator is field upgradable through future firmware downloads in MPLAB X IDE. MPLAB REAL ICE offers significant advantages over competitive emulators including full-speed emulation, run-time variable watches, trace analysis, complex breakpoints, logic probes, a ruggedized probe interface and long (up to three meters) interconnection cables.

## 30.8 MPLAB ICD 3 In-Circuit Debugger System

The MPLAB ICD 3 In-Circuit Debugger System is Microchip's most cost-effective, high-speed hardware debugger/programmer for Microchip Flash DSC and MCU devices. It debugs and programs PIC Flash microcontrollers and dsPIC DSCs with the powerful, yet easy-to-use graphical user interface of the MPLAB IDE.

The MPLAB ICD 3 In-Circuit Debugger probe is connected to the design engineer's PC using a highspeed USB 2.0 interface and is connected to the target with a connector compatible with the MPLAB ICD 2 or MPLAB REAL ICE systems (RJ-11). MPLAB ICD 3 supports all MPLAB ICD 2 headers.

## 30.9 PICkit 3 In-Circuit Debugger/ Programmer