Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f128lt-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 5: PIN NAMES FOR 100-PIN DEVICES (CONTINUED)

| 100-PIN TQFP | (TOP VIEW) <sup>(1,2)</sup> |

|--------------|-----------------------------|

|--------------|-----------------------------|

PIC32MX430F064L PIC32MX450F128L PIC32MX450F256L PIC32MX470F512L

100

|       |                       |       | 1                   |

|-------|-----------------------|-------|---------------------|

| Pin # | Full Pin Name         | Pin # | Full Pin Name       |

| 71    | RPD11/PMCS1/RD11      | 86    | VDD                 |

| 72    | RPD0/INT0/RD0         | 87    | RPF0/PMD11/RF0      |

| 73    | SOSCI/RPC13/RC13      | 88    | RPF1/PMD10/RF1      |

| 74    | SOSCO/RPC14/T1CK/RC14 | 89    | RPG1/PMD9/RG1       |

| 75    | Vss                   | 90    | RPG0/PMD8/RG0       |

| 76    | AN24/RPD1/RD1         | 91    | TRCLK/RA6           |

| 77    | AN25/RPD2/RD2         | 92    | TRD3/CTED8/RA7      |

| 78    | AN26/RPD3/RD3         | 93    | PMD0/RE0            |

| 79    | RPD12/PMD12/RD12      | 94    | PMD1/RE1            |

| 80    | PMD13/RD13            | 95    | TRD2/RG14           |

| 81    | RPD4/PMWR/RD4         | 96    | TRD1/RG12           |

| 82    | RPD5/PMRD/RD5         | 97    | TRD0/RG13           |

| 83    | PMD14/RD6             | 98    | AN20/CTPLS/PMD2/RE2 |

| 84    | PMD15/RD7             | 99    | RPE3/PMD3/RE3       |

| 85    | VCAP                  | 100   | AN21/PMD4/RE4       |

Note

1:

The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 12.0 "I/O Ports" for more information.

| REGIST  | ER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER (CONTINUED)                                                                                                                    |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 9-8 | IS1<1:0>: Interrupt Subpriority bits<br>11 = Interrupt subpriority is 3<br>10 = Interrupt subpriority is 2<br>01 = Interrupt subpriority is 1<br>00 = Interrupt subpriority is 0 |

| bit 7-5 | Unimplemented: Read as '0'                                                                                                                                                       |

| bit 4-2 | IP0<2:0>: Interrupt Priority bits                                                                                                                                                |

|         | <pre>111 = Interrupt priority is 7</pre>                                                                                                                                         |

|         | 001 = Interrupt priority is 1<br>000 = Interrupt is disabled                                                                                                                     |

| bit 1-0 | ISO<1:0>: Interrupt Subpriority bits                                                                                                                                             |

|         | <pre>11 = Interrupt subpriority is 3 10 = Interrupt subpriority is 2 01 = Interrupt subpriority is 1 00 = Interrupt subpriority is 0</pre>                                       |

| Note:   | This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.                                                            |

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------------|-------------------------|-------------------|----------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 31.24        | _                 | _                       | _                       |                   | —                    | _                 | _                     | —                       |

| 23:16        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 23.10        | _                 | _                       | _                       |                   | —                    | _                 | _                     | —                       |

| 15:8         | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 15.0         | _                 | _                       | _                       |                   | —                    | _                 | _                     | —                       |

|              | R/WC-0, HS        | R/WC-0, HS              | R/WC-0, HS              | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS        | R-0                   | R/WC-0, HS              |

| 7:0          | STALLIF           | ATTACHIF <sup>(1)</sup> | RESUMEIF <sup>(2)</sup> | IDLEIF            | TRNIF <sup>(3)</sup> | SOFIF             | UERRIF <sup>(4)</sup> | URSTIF <sup>(5)</sup>   |

|              | OTTLE             |                         | REGOMEN                 | IDEEN             |                      | 0011              | OLIVI                 | DETACHIF <sup>(6)</sup> |

|              |                   |                         |                         |                   |                      |                   |                       | 1                       |

# REGISTER 11-6: U1IR: USB INTERRUPT REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit         |                    |  |

|-------------------|-------------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

|       | -  |                                                                                                                                              |

|-------|----|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7 |    | <b>STALLIF:</b> STALL Handshake Interrupt bit 1 = In Host mode, a STALL handshake was received during the handshake phase of the transaction |

|       |    |                                                                                                                                              |

|       |    | In Device mode, a STALL handshake was transmitted during the handshake phase of the transaction                                              |

|       |    | 0 = STALL handshake has not been sent                                                                                                        |

| bit 6 |    | ATTACHIF: Peripheral Attach Interrupt bit <sup>(1)</sup>                                                                                     |

|       |    | 1 = Peripheral attachment was detected by the USB module                                                                                     |

|       |    | 0 = Peripheral attachment was not detected                                                                                                   |

| bit 5 |    | <b>RESUMEIF:</b> Resume Interrupt bit <sup>(2)</sup>                                                                                         |

|       |    | 1 = K-State is observed on the D+ or D- pin for 2.5 µs                                                                                       |

|       |    | 0 = K-State is not observed                                                                                                                  |

| bit 4 |    | <b>IDLEIF:</b> Idle Detect Interrupt bit                                                                                                     |

|       |    | <ul><li>1 = Idle condition detected (constant Idle state of 3 ms or more)</li><li>0 = No Idle condition detected</li></ul>                   |

| bit 3 |    | TRNIF: Token Processing Complete Interrupt bit <sup>(3)</sup>                                                                                |

| DILS  |    | 1 = Processing of current token is complete; a read of the U1STAT register will provide endpoint information                                 |

|       |    | 0 = Processing of current token not complete                                                                                                 |

| bit 2 |    | SOFIF: SOF Token Interrupt bit                                                                                                               |

|       |    | 1 = SOF token received by the peripheral or the SOF threshold reached by the host                                                            |

|       |    | 0 = SOF token was not received nor threshold reached                                                                                         |

| bit 1 |    | UERRIF: USB Error Condition Interrupt bit <sup>(4)</sup>                                                                                     |

|       |    | 1 = Unmasked error condition has occurred                                                                                                    |

|       |    | 0 = Unmasked error condition has not occurred                                                                                                |

| bit 0 |    | URSTIF: USB Reset Interrupt bit (Device mode) <sup>(5)</sup>                                                                                 |

|       |    | 1 = Valid USB Reset has occurred                                                                                                             |

|       |    | 0 = No USB Reset has occurred                                                                                                                |

| bit 0 |    | <b>DETACHIF:</b> USB Detach Interrupt bit (Host mode) <sup>(6)</sup>                                                                         |

|       |    | 1 = Peripheral detachment was detected by the USB module                                                                                     |

|       |    | 0 = Peripheral detachment was not detected                                                                                                   |

| Note  | 1: | This bit is valid only if the HOSTEN bit is set (see Register 11-11), there is no activity on the USB for                                    |

|       |    | $2.5 \mu\text{s}$ , and the current bus state is not SE0.                                                                                    |

|       | 2: | When not in Suspend mode, this interrupt should be disabled.                                                                                 |

|       | 3: | Clearing this bit will cause the STAT FIFO to advance.                                                                                       |

|       | 4: | Only error conditions enabled through the U1EIE register will set this bit.                                                                  |

|       | 5: | Device mode.                                                                                                                                 |

|       | 6: | Host mode.                                                                                                                                   |

| Bit<br>Range | Bit<br>31/23/15/7                                            | Bit<br>30/22/14/6     | Bit<br>29/21/13/5     | Bit<br>28/20/12/4     | Bit<br>27/19/11/3 | Bit<br>26/18/10/2    | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |  |

|--------------|--------------------------------------------------------------|-----------------------|-----------------------|-----------------------|-------------------|----------------------|----------------------|------------------|--|

| 24.24        | U-0                                                          | U-0                   | U-0                   | U-0                   | U-0               | U-0                  | U-0                  | U-0              |  |

| 31:24        | -                                                            | -                     | —                     | —                     | —                 | —                    | —                    | —                |  |

| 23:16        | U-0                                                          | U-0                   | U-0                   | U-0                   | U-0               | U-0                  | U-0                  | U-0              |  |

| 23.10        | -                                                            | -                     | —                     | —                     | —                 | _                    | _                    | —                |  |

| 15:8         | U-0                                                          | U-0                   | U-0                   | U-0                   | U-0               | U-0                  | U-0                  | U-0              |  |

| 15.0         | _                                                            | _                     | —                     | —                     | —                 | —                    | —                    | —                |  |

|              | R-x                                                          | R-x                   | R/W-0                 | R/W-0                 | R/W-0             | R/W-0                | R/W-0                | R/W-0            |  |

| 7:0          | JSTATE SE0 PKTDIS <sup>(4)</sup><br>TOKBUSY <sup>(1,5)</sup> | PKTDIS <sup>(4)</sup> |                       |                       |                   | DDDDDT               | USBEN <sup>(4)</sup> |                  |  |

|              |                                                              | USBRST                | HOSTEN <sup>(2)</sup> | RESUME <sup>(3)</sup> | PPBRST            | SOFEN <sup>(5)</sup> |                      |                  |  |

#### REGISTER 11-11: U1CON: USB CONTROL REGISTER

#### Legend:

| Logona                            |                  |                                    |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **JSTATE:** Live Differential Receiver JSTATE flag bit 1 = JSTATE detected on the USB

- 0 = No JSTATE detected

- bit 6 SE0: Live Single-Ended Zero flag bit

1 = Single Ended Zero detected on the USB

0 = No Single Ended Zero detected

- bit 5 **PKTDIS:** Packet Transfer Disable bit<sup>(4)</sup>

- 1 = Token and packet processing disabled (set upon SETUP token received)

- 0 = Token and packet processing enabled

- TOKBUSY: Token Busy Indicator bit<sup>(1,5)</sup>

- 1 = Token being executed by the USB module

- 0 = No token being executed

#### bit 4 USBRST: Module Reset bit<sup>(5)</sup>

- 1 = USB reset is generated

- 0 = USB reset is terminated

#### bit 3 HOSTEN: Host Mode Enable bit<sup>(2)</sup>

- 1 = USB host capability is enabled

- 0 = USB host capability is disabled

#### bit 2 RESUME: RESUME Signaling Enable bit<sup>(3)</sup>

- 1 = RESUME signaling is activated

- 0 = RESUME signaling is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- **3:** Software must set the RESUME bit for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 |                   | _                 | —                 |                   |                   |                  | -                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 |                   | _                 | —                 | -                 |                   |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | —                 | _                 | _                 | —                 | -                 | -                 | -                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |

| 7:0          |                   |                   |                   |                   |                   |                   | FRMH<2:0>        |                  |

#### REGISTER 11-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

|              |                   |                   |                   | LOISTEN           |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 |                   | —                 | —                 | -                 | _                 | -                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 |                   | _                 | —                 | -                 | _                 |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         | _                 |                   |                   | —                 |                   | _                 |                  | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | PID<3             | 3:0>(1)           |                   |                   | EP<               | 3:0>             |                  |

#### REGISTER 11-15: U1TOK: USB TOKEN REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

0001 = OUT (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 1101 = SETUP (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

**Note 1:** All other values are reserved and must not be used.

| Peripheral Pin | [pin name]R SFR      | [pin name]R bits | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection        |  |  |  |

|----------------|----------------------|------------------|-----------------------------------------------------------|--|--|--|

| INT1           | INT1R                | INT1R<3:0>       | 0000 = RPD1<br>0001 = RPG9                                |  |  |  |

| ТЗСК           | T3CKR                | T3CKR<3:0>       | 0010 = RPB14<br>0011 = RPD0                               |  |  |  |

| IC1            | IC1R                 | IC1R<3:0>        | 0100 = RPD8<br>0101 = RPB6                                |  |  |  |

| U3CTS          | U3CTSR               | U3CTSR<3:0>      | 0110 = RPD5<br>0111 = RPB2                                |  |  |  |

| U4RX           | U4RXR                | U4RXR<3:0>       | 1000 = RPF3 <sup>(4)</sup><br>1001 = RPF13 <sup>(3)</sup> |  |  |  |

| U5RX           | U5RXR <sup>(3)</sup> | U5RXR<3:0>       | 1010 = Reserved<br>1011 = RPF2 <sup>(1)</sup>             |  |  |  |

| SS2            | SS2R                 | SS2R<3:0>        | 1100 = RPC2 <sup>(3)</sup><br>1101 = RPE8 <sup>(3)</sup>  |  |  |  |

| OCFA           | OCFAR                | OCFAR<3:0>       | 1110 = Reserved<br>1111 = Reserved                        |  |  |  |

# TABLE 12-1:INPUT PIN SELECTION (CONTINUED)

Note 1: This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

3: This selection is not available on 64-pin USB and General Purpose devices.

4: This selection is only available on General Purpose devices.

# TABLE 12-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

|                           |                  |           |       |       |       |       |       |       |      |      | -    |      |      |      |      |      |       |      |            |

|---------------------------|------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|------|-------|------|------------|

| ŝ                         |                  |           |       | Bits  |       |       |       |       |      |      |      |      |      |      |      |      |       |      |            |

| Virtual Addre<br>(BF80_#) | Register<br>Name | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0 | All Resets |

| 50.10                     |                  | 31:16     | _     | -     |       | _     | _     | _     | _    | _    | _    | -    | _    | _    | -    | _    | _     | _    | 0000       |

| FCA0                      | RPG8R            | 15:0      | _     | _     | _     | _     | —     |       | _    | _    | _    | _    | _    | _    |      | RPG8 | <3:0> |      | 0000       |

| 5044                      | DDOOD            | 31:16     | _     | _     | _     | _     | _     | _     | —    | _    | _    | _    | _    | _    | _    | —    | —     | —    | 0000       |

| FCA4                      | RPG9R            | 15:0      |       | —     | —     | -     | —     | _     | —    | _    | _    |      |      |      |      | RPG9 | <3:0> |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is only available on devices without a USB module.

3: This register is not available on 64-pin devices with a USB module.

# 15.1 Watchdog Timer Control Registers

| DS60001185F-page |  |

|------------------|--|

| е<br>—           |  |

| 78               |  |

# TABLE 15-1: WATCHDOG TIMER CONTROL REGISTER MAP

| ess                        |                                 | æ         |       |       |       |       |       |       |      |      | Bits |      |      |          |      |      |          |        | s          |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|------|------|----------|--------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3 | 18/2 | 17/1     | 16/0   | All Resets |

| 0000                       | WDTCON                          | 31:16     | _     | _     | _     | _     | -     | -     | —    | —    | _    | —    | —    | _        | _    | _    | —        | —      | 0000       |

| 0000                       | WDICON                          | 15:0      | ON    |       |       |       | _     | _     | _    | _    |      |      | SI   | VDTPS<4: | )>   |      | WDTWINEN | WDTCLR | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | —                 | CSSL30            | CSSL29            | CSSL28            | CSSL27            | CSSL26            | CSSL25           | CSSL24           |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CSSL23            | CSSL21            | CSSL21            | CSSL20            | CSSL19            | CSSL18            | CSSL17           | CSSL16           |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |

#### REGISTER 23-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

# Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15-0 CSSL<30:0>: ADC Input Pin Scan Selection bits<sup>(1,2)</sup>

- 1 = Select ANx for input scan

- 0 = Skip ANx for input scan

- **Note 1:** CSSL = ANx, where x = 0-27; CSSL30 selects Vss for scan; CSSL29 selects CTMU input for scan; CSSL28 selects IVREF for scan.

- 2: On devices with less than 28 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| 04.04        | r-0               | r-1               | r-1               | R/P               | r-1               | r-1                   | r-1              | R/P              |

| 31:24        | _                 | —                 | —                 | CP                | —                 | —                     | —                | BWP              |

| 00.40        | r-1               | r-1               | r-1               | r-1               | R/P               | R/P                   | R/P              | R/P              |

| 23:16        | —                 | —                 | —                 | —                 |                   | PWP                   | <7:4>            |                  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | r-1                   | r-1              | r-1              |

| 15:8         |                   | PWP<              | <3:0>             |                   | —                 | —                     | _                | —                |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P               | R/P                   | R/P              | R/P              |

| 7:0          | _                 | _                 | —                 | ICESE             | L<1:0>            | JTAGEN <sup>(1)</sup> | DEBU             | G<1:0>           |

#### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:           | r = Reserved bit | P = Programmable bit |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 **Reserved:** Write '0'

bit 30-29 Reserved: Write '1'

bit 28 **CP:** Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device.

1 = Protection is disabled

0 = Protection is enabled

#### bit 27-25 Reserved: Write '1'

bit 24 BWP: Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable

0 = Boot Flash is not writable

bit 23-20 Reserved: Write '1'

bit 19-12 **PWP<7:0>:** Program Flash Write-Protect bits

Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages.

| 11111111 = Disabled    |

|------------------------|

| 11111110 = 0xBD00_0FFF |

| 11111101 = 0xBD00_1FFF |

| 11111100 = 0xBD00_2FFF |

| 11111011 = 0xBD00_3FFF |

| 11111010 = 0xBD00_4FFF |

| 11111001 = 0xBD00_5FFF |

| 11111000 = 0xBD00_6FFF |

| 11110111 = 0xBD00_7FFF |

| 11110110 = 0xBD00 8FFF |

| 11110101 = 0xBD00_9FFF |

| 11110100 = 0xBD00_AFFF |

| 11110011 = 0xBD00 BFFF |

| 11110010 = 0xBD00 CFFF |

| 11110001 = 0xBD00 DFFF |

| 11110000 = 0xBD00 EFFF |

| 11101111 = 0xBD00 FFFF |

| . –                    |

|                        |

|                        |

| 01111111 = 0xBD07 FFFF |

| _                      |

|                        |

Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

# 30.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

# 30.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature

- Built-in support for Bugzilla issue tracker

| DC CHA        | RACTE | RISTICS                           | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                     |                      |       |                                                                               |  |  |  |

|---------------|-------|-----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|----------------------|-------|-------------------------------------------------------------------------------|--|--|--|

| Param.<br>No. | Symb. | Characteristics                   | Min.                                                                                                                                                                                                                                                                                                                                                   | Тур. <sup>(1)</sup> | Max.                 | Units | Conditions                                                                    |  |  |  |

|               |       | Input Leakage Current<br>(Note 3) |                                                                                                                                                                                                                                                                                                                                                        |                     |                      |       |                                                                               |  |  |  |

| DI50          | lı∟   | I/O Ports                         | —                                                                                                                                                                                                                                                                                                                                                      | _                   | <u>+</u> 1           | μA    | $Vss \le VPIN \le VDD,$ Pin at high-impedance                                 |  |  |  |

| DI51          |       | Analog Input Pins                 | —                                                                                                                                                                                                                                                                                                                                                      | —                   | <u>+</u> 1           | μA    | $Vss \le VPIN \le VDD,$ Pin at high-impedance                                 |  |  |  |

| DI55          |       | MCLR <sup>(2)</sup>               | _                                                                                                                                                                                                                                                                                                                                                      |                     | <u>+</u> 1           | μA    | $Vss \leq V \text{PIN} \leq V \text{DD}$                                      |  |  |  |

| DI56          |       | OSC1                              | —                                                                                                                                                                                                                                                                                                                                                      | —                   | <u>+</u> 1           | μA    | $VSS \le VPIN \le VDD,$<br>XT and HS modes                                    |  |  |  |

|               |       |                                   |                                                                                                                                                                                                                                                                                                                                                        |                     |                      |       | Pins with Analog functions.<br>Exceptions: [N/A] = 0 mA<br>max                |  |  |  |

| DI60a         | licl  | Input Low Injection<br>Current    | 0                                                                                                                                                                                                                                                                                                                                                      | _                   | <sub>-5</sub> (7,10) | mA    | Digital 5V tolerant desig-<br>nated pins. Exceptions:<br>[N/A] = 0 mA max     |  |  |  |

|               |       |                                   |                                                                                                                                                                                                                                                                                                                                                        |                     |                      |       | Digital non-5V tolerant desig-<br>nated pins. Exceptions:<br>[N/A] = 0 mA max |  |  |  |

#### TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

- 7: VIL source < (VSS 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- **10:** Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (Vss 0.3)).

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

| DC CHARACTERISTICS |       |                                                                       | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                     |                        |       |                                                                                                                                                                                                                                                                                              |

|--------------------|-------|-----------------------------------------------------------------------|------------------------------------------------------|---------------------|------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No.      | Symb. | Characteristics                                                       | Min.                                                 | Тур. <sup>(1)</sup> | Max.                   | Units | Conditions                                                                                                                                                                                                                                                                                   |

| DI60b              | Іісн  | Input High Injection<br>Current                                       | 0                                                    |                     | +5 <sup>(8,9,10)</sup> | mA    | Pins with Analog functions.<br>Exceptions: [SOSCI,<br>SOSCO, OSC1, D+, D-] = 0<br>mA max.<br>Digital 5V tolerant desig-<br>nated pins (VIH < $5.5V$ ) <sup>(9)</sup> .<br>Exceptions: [All] = 0 mA<br>max.<br>Digital non-5V tolerant desig-<br>nated pins. Exceptions:<br>[N/A] = 0 mA max. |

| DI60c              | ∑IICT | Total Input Injection<br>Current (sum of all I/O<br>and control pins) | -20 <sup>(11)</sup>                                  | _                   | +20 <sup>(11)</sup>    | mA    | Absolute instantaneous sum<br>of all $\pm$ input injection cur-<br>rents from all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT                                                                                                                                                         |

#### TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

- 7: VIL source < (Vss 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- **10:** Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS 0.3)).

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

# PIC32MX330/350/370/430/450/470

#### **FIGURE 31-10:** SPIx MODULE MASTER MODE (CKE = 0) TIMING CHARACTERISTICS SCKx (CKP = 0) SP11 SP10 SP21 SP20 SCKx (CKP = 1) SP35 SP20 SP21 Bit 14 SDOx MSb -1 LSb **SP31** SP30 SDIx LSb In MSb In Bit 14 SP40 'SP41' Note: Refer to Figure 31-1 for load conditions.

| AC CHARACTERISTICS |                       |                                            |        | $\label{eq:standard operating Conditions: 2.3V to 3.6V} \end{tabular} \begin{tabular}{lllllllllllllllllllllllllllllllllll$ |      |       |                    |  |  |

|--------------------|-----------------------|--------------------------------------------|--------|----------------------------------------------------------------------------------------------------------------------------|------|-------|--------------------|--|--|

| Param.<br>No.      | Symbol                | Characteristics <sup>(1)</sup>             | Min.   | Typical <sup>(2)</sup>                                                                                                     | Max. | Units | Conditions         |  |  |

| SP10               | TscL                  | SCKx Output Low Time<br>(Note 3)           | Тѕск/2 | —                                                                                                                          | —    | ns    | —                  |  |  |

| SP11               | TscH                  | SCKx Output High Time<br>(Note 3)          | Тѕск/2 | —                                                                                                                          | —    | ns    | _                  |  |  |

| SP20               | TSCF                  | SCKx Output Fall Time (Note 4)             | —      | —                                                                                                                          | _    | ns    | See parameter DO32 |  |  |

| SP21               | TscR                  | SCKx Output Rise Time (Note 4)             | —      | _                                                                                                                          | _    | ns    | See parameter DO31 |  |  |

| SP30               | TDOF                  | SDOx Data Output Fall Time (Note 4)        |        | _                                                                                                                          | _    | ns    | See parameter DO32 |  |  |

| SP31               | TDOR                  | SDOx Data Output Rise Time (Note 4)        | _      | _                                                                                                                          |      | ns    | See parameter DO31 |  |  |

| SP35               | TSCH2DOV,             | SDOx Data Output Valid after               | _      | _                                                                                                                          | 15   | ns    | VDD > 2.7V         |  |  |

|                    | TscL2DoV              | SCKx Edge                                  |        | —                                                                                                                          | 20   | ns    | VDD < 2.7V         |  |  |

| SP40               | TDIV2scH,<br>TDIV2scL | Setup Time of SDIx Data Input to SCKx Edge | 10     | —                                                                                                                          | —    | ns    | _                  |  |  |

| SP41               | TscH2diL,<br>TscL2diL | Hold Time of SDIx Data Input to SCKx Edge  | 10     | —                                                                                                                          |      | ns    | —                  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not violate this specification.

**4:** Assumes 50 pF load on all SPIx pins.

#### TABLE 31-31: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS (CONTINUED)

| AC CHARACTERISTICS |                      |                                |              | Standard Operating Conditions: 2.3V to 3.6V<br>(unless otherwise stated)Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |       |            |  |  |

|--------------------|----------------------|--------------------------------|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|------------|--|--|

| Param.<br>No.      | Symbol               | Characteristics <sup>(1)</sup> | Min.         | Тур. <sup>(2)</sup>                                                                                                                                                                                                                                              | Max. | Units | Conditions |  |  |

| SP52               | TscH2ssH<br>TscL2ssH | SSx after SCKx Edge            | Тscк +<br>20 | —                                                                                                                                                                                                                                                                | _    | ns    | _          |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 40 ns.

4: Assumes 50 pF load on all SPIx pins.

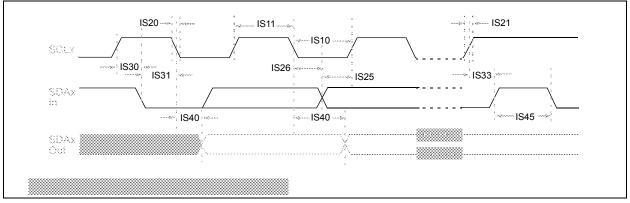

# TABLE 31-33: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE) (CONTINUED)

| AC CHARACTERISTICS |         |                                                                             |                        | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |      |                                        |                        |  |  |

|--------------------|---------|-----------------------------------------------------------------------------|------------------------|------------------------------------------------------|------|----------------------------------------|------------------------|--|--|

| Param.<br>No.      | Symbol  | Characteristics                                                             |                        | Min. <sup>(1)</sup>                                  | Max. | Units                                  | Conditions             |  |  |

| IM34               | THD:STO | Stop Condition                                                              | 100 kHz mode           | Трв * (BRG + 2)                                      |      | ns                                     | —                      |  |  |

|                    |         | Hold Time                                                                   | 400 kHz mode           | Трв * (BRG + 2)                                      | —    | ns                                     |                        |  |  |

|                    |         |                                                                             | 1 MHz mode<br>(Note 2) | Трв * (BRG + 2)                                      | —    | ns                                     |                        |  |  |

| IM40               | TAA:SCL | . Output Valid<br>from Clock                                                | 100 kHz mode           | —                                                    | 3500 | ns                                     | —                      |  |  |

|                    |         |                                                                             | 400 kHz mode           | —                                                    | 1000 | ns                                     | —                      |  |  |

|                    |         |                                                                             | 1 MHz mode<br>(Note 2) | —                                                    | 350  | ns                                     | —                      |  |  |

| IM45               | Tbf:sda | BF:SDA Bus Free Time 100 kHz mode<br>400 kHz mode<br>1 MHz mode<br>(Note 2) | 100 kHz mode           | 4.7                                                  | —    | μS                                     | The amount of time the |  |  |

|                    |         |                                                                             | 400 kHz mode           | 1.3                                                  | —    | μS                                     | bus must be free       |  |  |

|                    |         |                                                                             | 0.5                    | —                                                    | μS   | before a new<br>transmission can start |                        |  |  |

| IM50               | Св      | Bus Capacitive Loading                                                      |                        | —                                                    | 400  | pF                                     | —                      |  |  |

| IM51               | Tpgd    | Pulse Gobbler D                                                             | elay                   | 52                                                   | 312  | ns                                     | See Note 3             |  |  |

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

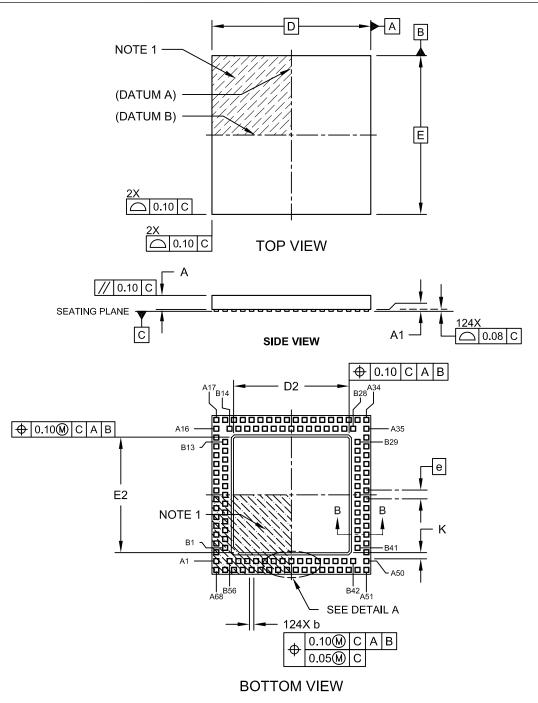

# 124-Terminal Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-193A Sheet 1 of 2

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support