Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| -                          |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Details                    |                                                                                 |

| Product Status             | Obsolete                                                                        |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 128KB (128K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 32K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                |

| Supplier Device Package    | 124-VTLA (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f128lt-i-tl |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 4: PIN NAMES FOR 100-PIN DEVICES

**100-PIN TQFP (TOP VIEW)**(1,2,3)

PIC32MX330F064L PIC32MX350F128L PIC32MX350F256L PIC32MX370F512L

100

1

| Pin# | Full Pin Name                        |

|------|--------------------------------------|

| 1    | RG15                                 |

| 2    | VDD                                  |

| 3    | AN22/RPE5/PMD5/RE5                   |

| 4    | AN23/PMD6/RE6                        |

| -    | AN27/PMD7/RE7                        |

| 5    |                                      |

| 6    | RPC1/RC1<br>RPC2/RC2                 |

| 7    |                                      |

| 8    | RPC3/RC3                             |

| 9    | RPC4/CTED7/RC4                       |

| 10   | AN16/C1IND/RPG6/SCK2/PMA5/RG6        |

| 11   | AN17/C1INC/RPG7/PMA4/RG7             |

| 12   | AN18/C2IND/RPG8/PMA3/RG8             |

| 13   | MCLR                                 |

| 14   | AN19/C2INC/RPG9/PMA2/RG9             |

| 15   | Vss                                  |

| 16   | VDD                                  |

| 17   | TMS/CTED1/RA0                        |

| 18   | RPE8/RE8                             |

| 19   | RPE9/RE9                             |

| 20   | AN5/C1INA/RPB5/RB5                   |

| 21   | AN4/C1INB/RB4                        |

| 22   | PGED3/AN3/C2INA/RPB3/RB3             |

| 23   | PGEC3/AN2/C2INB/RPB2/CTED13/RB2      |

| 24   | PGEC1/AN1/RPB1/CTED12/RB1            |

| 25   | PGED1/AN0/RPB0/RB0                   |

| 26   | PGEC2/AN6/RPB6/RB6                   |

| 27   | PGED2/AN7/RPB7/CTED3/RB7             |

| 28   | VREF-/CVREF-/PMA7/RA9                |

| 29   | VREF+/CVREF+/PMA6/RA10               |

| 30   | AVDD                                 |

| 31   | AVss                                 |

| 32   | AN8/RPB8/CTED10/RB8                  |

| 33   | AN9/RPB9/CTED4/RB9                   |

| 34   | CVREFOUT/AN10/RPB10/CTED11PMA13/RB10 |

| 35   | AN11/PMA12/RB11                      |

| Pin# | Full Pin Name                   |

|------|---------------------------------|

| 36   | Vss                             |

| 37   | VDD                             |

| 38   | TCK/CTED2/RA1                   |

| 39   | RPF13/RF13                      |

| 40   | RPF12/RF12                      |

| 41   | AN12/PMA11/RB12                 |

| 42   | AN13/PMA10/RB13                 |

| 43   | AN14/RPB14/CTED5/PMA1/RB14      |

| 44   | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 45   | Vss                             |

| 46   | VDD                             |

| 47   | RPD14/RD14                      |

| 48   | RPD15/RD15                      |

| 49   | RPF4/PMA9/RF4                   |

| 50   | RPF5/PMA8/RF5                   |

| 51   | RPF3/RF3                        |

| 52   | RPF2/RF2                        |

| 53   | RPF8/RF8                        |

| 54   | RPF7/RF7                        |

| 55   | RPF6/SCK1/INT0/RF6              |

| 56   | SDA1/RG3                        |

| 57   | SCL1/RG2                        |

| 58   | SCL2/RA2                        |

| 59   | SDA2/RA3                        |

| 60   | TDI/CTED9/RA4                   |

| 61   | TDO/RA5                         |

| 62   | VDD                             |

| 63   | OSC1/CLKI/RC12                  |

| 64   | OSC2/CLKO/RC15                  |

| 65   | Vss                             |

| 66   | RPA14/RA14                      |

| 67   | RPA15/RA15                      |

| 68   | RPD8/RTCC/RD8                   |

| 69   | RPD9/RD9                        |

| 70   | RPD10/PMCS2/RD10                |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RAx-RGx), with the exception of RF6, can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

- 3: RPF6 (pin 55) and RPF7 (pin 54) are only remappable for input functions.

### TABLE 5: PIN NAMES FOR 100-PIN DEVICES

100-PIN TQFP (TOP VIEW)(1,2)

PIC32MX430F064L PIC32MX450F128L PIC32MX450F256L PIC32MX470F512L

100

1

| Pin# | Full Pin Name                         |

|------|---------------------------------------|

| 1    | RG15                                  |

| 2    | Vpp                                   |

|      | AN22/RPE5/PMD5/RE5                    |

| 3    |                                       |

| 4    | AN23/PMD6/RE6                         |

| 5    | AN27/PMD7/RE7                         |

| 6    | RPC1/RC1                              |

| 7    | RPC2/RC2                              |

| 8    | RPC3/RC3                              |

| 9    | RPC4/CTED7/RC4                        |

| 10   | AN16/C1IND/RPG6/SCK2/PMA5/RG6         |

| 11   | AN17/C1INC/RPG7/PMA4/RG7              |

| 12   | AN18/C2IND/RPG8/PMA3/RG8              |

| 13   | MCLR                                  |

| 14   | AN19/C2INC/RPG9/PMA2/RG9              |

| 15   | Vss                                   |

| 16   | VDD                                   |

| 17   | TMS/CTED1/RA0                         |

| 18   | RPE8/RE8                              |

| 19   | RPE9/RE9                              |

| 20   | AN5/C1INA/RPB5/VBuson/RB5             |

| 21   | AN4/C1INB/RB4                         |

| 22   | PGED3/AN3/C2INA/RPB3/RB3              |

| 23   | PGEC3/AN2/C2INB/RPB2/CTED13/RB2       |

| 24   | PGEC1/AN1/RPB1/CTED12/RB1             |

| 25   | PGED1/AN0/RPB0/RB0                    |

| 26   | PGEC2/AN6/RPB6/RB6                    |

| 27   | PGED2/AN7/RPB7/CTED3/RB7              |

| 28   | VREF-/CVREF-/PMA7/RA9                 |

| 29   | VREF+/CVREF+/PMA6/RA10                |

| 30   | AVDD                                  |

| 31   | AVss                                  |

| 32   | AN8/RPB8/CTED10/RB8                   |

| 33   | AN9/RPB9/CTED4/RB9                    |

| 34   | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10 |

| 35   | AN11/PMA12/RB11                       |

| Pin # | Full Pin Name                   |

|-------|---------------------------------|

| 36    | Vss                             |

| 37    | VDD                             |

| 38    | TCK/CTED2/RA1                   |

| 39    | RPF13/RF13                      |

| 40    | RPF12/RF12                      |

| 41    | AN12/PMA11/RB12                 |

| 42    | AN13/PMA10/RB13                 |

| 43    | AN14/RPB14/CTED5/PMA1/RB14      |

| 44    | AN15/RPB15/OCFB/CTED6/PMA0/RB15 |

| 45    | Vss                             |

| 46    | VDD                             |

| 47    | RPD14/RD14                      |

| 48    | RPD15/RD15                      |

| 49    | RPF4/PMA9/RF4                   |

| 50    | RPF5/PMA8/RF5                   |

| 51    | USBID/RF3                       |

| 52    | RPF2/RF2                        |

| 53    | RPF8/RF8                        |

| 54    | VBUS                            |

| 55    | Vusb3v3                         |

| 56    | D-                              |

| 57    | D+                              |

| 58    | SCL2/RA2                        |

| 59    | SDA2/RA3                        |

| 60    | TDI/CTED9/RA4                   |

| 61    | TDO/RA5                         |

| 62    | VDD                             |

| 63    | OSC1/CLKI/RC12                  |

| 64    | OSC2/CLKO/RC15                  |

| 65    | Vss                             |

| 66    | SCL1/RPA14/RA14                 |

| 67    | SDA1/RPA15/RA15                 |

| 68    | RPD8/RTCC/RD8                   |

| 69    | RPD9/RD9                        |

| 70    | RPD10/SCK1/PMCS2/RD10           |

Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 12.0 "I/O Ports" for more information.

TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

|          |                        | er                       |                                                     |             |                |                                                                              |

|----------|------------------------|--------------------------|-----------------------------------------------------|-------------|----------------|------------------------------------------------------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP          | 124-pin<br>VTLA                                     | Pin<br>Type | Buffer<br>Type | Description                                                                  |

| CTED4    | 22                     | 33                       | B19                                                 | I           | ST             | CTMU External Edge Input 4                                                   |

| CTED5    | 29                     | 43                       | B24                                                 | I           | ST             | CTMU External Edge Input 5                                                   |

| CTED6    | 30                     | 44                       | A29                                                 | I           | ST             | CTMU External Edge Input 6                                                   |

| CTED7    | _                      | 9                        | B5                                                  | I           | ST             | CTMU External Edge Input 7                                                   |

| CTED8    | _                      | 92                       | A62                                                 | I           | ST             | CTMU External Edge Input 8                                                   |

| CTED9    | _                      | 60                       | A40                                                 | I           | ST             | CTMU External Edge Input 9                                                   |

| CTED10   | 21                     | 32                       | A23                                                 | I           | ST             | CTMU External Edge Input 10                                                  |

| CTED11   | 23                     | 34                       | A24                                                 | I           | ST             | CTMU External Edge Input 11                                                  |

| CTED12   | 15                     | 24                       | A15                                                 | I           | ST             | CTMU External Edge Input 12                                                  |

| CTED13   | 14                     | 23                       | B13                                                 | I           | ST             | CTMU External Edge Input 13                                                  |

| MCLR     | 7                      | 13                       | В7                                                  | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device.   |

| AVDD     | 19                     | 30                       | A22                                                 | Р           | Р              | Positive supply for analog modules. This pin must be connected at all times. |

| AVss     | 20                     | 31                       | B18                                                 | Р           | Р              | Ground reference for analog modules                                          |

| VDD      | 10, 26, 38,<br>57      | 2, 16, 37,<br>46, 62, 86 | B1, A10, A14,<br>B21, A30,<br>A41, A48,<br>A59, B53 | Р           | _              | Positive supply for peripheral logic and I/O pins                            |

| VCAP     | 56                     | 85                       | B48                                                 | Р           |                | Capacitor for Internal Voltage Regulator                                     |

| Vss      | 9, 25, 41              | 15, 36, 45,<br>65, 75    | A3, B8, B12,<br>A25, B25,<br>A43, B41,<br>A63       | Р           | _              | Ground reference for logic and I/O pins                                      |

| VREF+    | 16                     | 29                       | B17                                                 | I           | Analog         | Analog Voltage Reference (High) Input                                        |

| VREF-    | 15                     | 28                       | A21                                                 | ı           | Analog         | Analog Voltage Reference (Low) Input                                         |

**Legend:** CMOS = CMOS compatible input or output

ST = Schmitt Trigger input with CMOS levels

TTL = TTL input buffer

Analog = Analog input

O = Output

P = Power I = Input

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices.

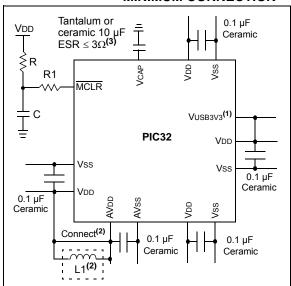

# FIGURE 2-1: RECOMMENDED MINIMUM CONNECTION

Note 1: If the USB module is not used, this pin must be connected to VDD.

2: As an option, instead of a hard-wired connection, an inductor (L1) can be substituted between VDD and AVDD to improve ADC noise rejection. The inductor impedance should be less than 3Ω and the inductor capacity greater than 10 mA.

Where:

$$f=\frac{FCNV}{2} \qquad \text{(i.e., ADC conversion rate/2)}$$

$$f=\frac{1}{(2\pi\sqrt{LC})}$$

$$L=\left(\frac{1}{(2\pi f\sqrt{C})}\right)^2$$

Aluminum or electrolytic capacitors should not be used. ESR ≤ 3Ω from -40°C to 125°C @ SYSCLK frequency (i.e., MIPS).

### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu$ F to 47  $\mu$ F. This capacitor should be located as close to the device as possible.

# 2.3 Capacitor on Internal Voltage Regulator (VCAP)

#### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (3 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 31.0** "Electrical **Characteristics**" for additional information on CEFC specifications.

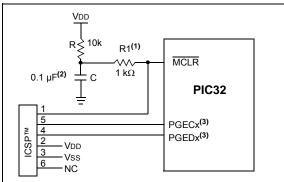

## 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides two specific device functions:

- · Device Reset

- · Device programming and debugging

Pulling The MCLR pin low generates a device Reset. Figure 2-2 illustrates a typical MCLR circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the MCLR pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the  $\overline{\text{MCLR}}$  pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

# FIGURE 2-2: EXAMPLE OF MCLR PIN CONNECTIONS

- Note 1:  $\frac{470\Omega \leq R1 \leq 1 k\Omega \text{ will limit any current flowing into}}{\text{MCLR}} \text{ from the external capacitor C, in the event of}} \\ \frac{\text{MCLR}}{\text{MCLR}} \text{ pin breakdown, due to Electrostatic Discharge}} \\ \frac{\text{(ESD) or Electrical Overstress (EOS). Ensure that the}}{\text{MCLR}} \text{ pin VIH and VIL specifications are met without interfering with the Debug/Programmer tools.}}$

- The capacitor can be sized to prevent unintentional Resets from brief glitches or to extend the device Reset period during POR.

- No pull-ups or bypass capacitors are allowed on active debug/program PGECx/PGEDx pins.

REGISTER 6-1: RCON: RESET CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 31:24        | U-0               | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0                | U-0                |

| 31.24        | _                 | _                 | HVDR              | _                 | _                 | _                 | _                  | _                  |

| 23:16        | U-0                | U-0                |

| 23.10        | _                 | _                 | _                 | _                 | -                 | -                 | _                  | _                  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 13.6         | _                 | _                 | _                 | _                 | -                 | -                 | CMR                | VREGS              |

| 7.0          | R/W-0, HS         | R/W-0, HS         | U-0               | R/W-0, HS         | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR               | _                 | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

Legend:HS = Set by hardwareR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-30 Unimplemented: Read as '0'

bit 29 HVDR: High Voltage Detect Reset Flag bit

1 = High Voltage Detect (HVD) Reset has occurred

0 = HVD Reset has not occurred

bit 28-10 Unimplemented: Read as '0'

bit 9 **CMR:** Configuration Mismatch Reset Flag bit

1 = Configuration mismatch Reset has occurred

0 = Configuration mismatch Reset has not occurred

bit 8 **VREGS:** Voltage Regulator Standby Enable bit

1 = Regulator is enabled and is on during Sleep mode

0 = Regulator is set to Stand-by Tracking mode

bit 7 **EXTR:** External Reset (MCLR) Pin Flag bit

1 = Master Clear (pin) Reset has occurred

0 = Master Clear (pin) Reset has not occurred

bit 6 **SWR:** Software Reset Flag bit

1 = Software Reset was executed

0 = Software Reset as not executed

bit 5 Unimplemented: Read as '0'

bit 4 WDTO: Watchdog Timer Time-out Flag bit

1 = WDT Time-out has occurred

0 = WDT Time-out has not occurred

bit 3 SLEEP: Wake From Sleep Flag bit

1 = Device was in Sleep mode

0 = Device was not in Sleep mode

bit 2 **IDLE:** Wake From Idle Flag bit

1 = Device was in Idle mode

0 = Device was not in Idle mode

bit 1 **BOR:** Brown-out Reset Flag bit<sup>(1)</sup>

1 = Brown-out Reset has occurred

0 = Brown-out Reset has not occurred

bit 0 **POR:** Power-on Reset Flag bit<sup>(1)</sup>

1 = Power-on Reset has occurred

0 = Power-on Reset has not occurred

Note 1: User software must clear this bit to view next detection.

#### REGISTER 10-10: DCHxSSA: DMA CHANNEL 'x' SOURCE START ADDRESS REGISTER

| Bit Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|-----------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24     |                   | CHSSA<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22.46     | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16     | CHSSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8      |                   | CHSSA<15:8>       |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

|           |                   |                   |                   | CHSSA             | <7:0>             |                   | ·                |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 CHSSA<31:0> Channel Source Start Address bits

Channel source start address.

**Note:** This must be the physical address of the source.

### REGISTER 10-11: DCHxDSA: DMA CHANNEL 'x' DESTINATION START ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   | CHDSA<31:24>      |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 22.46        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | CHDSA<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | CHDSA<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

|              | _                 |                   |                   | CHDSA             | <7:0>             |                   |                  |                  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-0 CHDSA<31:0>: Channel Destination Start Address bits

Channel destination start address.

**Note:** This must be the physical address of the destination.

#### REGISTER 11-5: U1PWRC: USB POWER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31.24        | _                 | -                 | -                 | _                 |                        | 1                 | _                |                  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23.10        | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 15.6         | _                 | -                 | -                 | _                 | _                      | -                 | _                |                  |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |

| 7:0          | UACTPND           | _                 | _                 | USLPGRD           | USBBUSY <sup>(1)</sup> | _                 | USUSPEND         | USBPWR           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7 **UACTPND:** USB Activity Pending bit

1 = USB bus activity has been detected; but an interrupt is pending, it has not been generated yet

0 = An interrupt is not pending

bit 6-5 **Unimplemented:** Read as '0'

bit 4 USLPGRD: USB Sleep Entry Guard bit

1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

0 = USB module does not block Sleep entry

bit 3 **USBBUSY:** USB Module Busy bit<sup>(1)</sup>

1 = USB module is active or disabled, but not ready to be enabled

0 = USB module is not active and is ready to be enabled

**Note:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all

USB module registers produce undefined results.

bit 2 Unimplemented: Read as '0'

bit 1 USUSPEND: USB Suspend Mode bit

1 = USB module is placed in Suspend mode

(The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

0 = USB module operates normally

bit 0 USBPWR: USB Operation Enable bit

1 = USB module is turned on

0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

#### REGISTER 11-18: U1BDTP2: USB BDT PAGE 2 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | _                 | -                 | _                 | -                 | -                 | _                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | _                 | -                 | 1                 | -                 | 1                 | 1                 | -                | _                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   | BDTPTR            | H<23:16>          |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRH<23:16>: BDT Base Address bits

This 8-bit value provides address bits 23 through 16 of the BDT base address, which defines the starting

location of the BDT in system memory.

REGISTER 11-19: U1BDTP3: USB BDT PAGE 3 REGISTER

The 32-bit BDT base address is 512-byte aligned.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | 1                 | 1                 | 1                 | -                 | 1                 | 1                 | -                | -                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | -                 |                   | _                 | 1                 | -                 | _                | -                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _                 | _                 | _                 | -                 | -                 | _                | _                |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

|              |                   |                   |                   | BDTPTR            | U<31:24>          |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRU<31:24>: BDT Base Address bits

> This 8-bit value provides address bits 31 through 24 of the BDT base address, defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

TABLE 12-7: PORTD REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L, PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY

| ess                         |                                 |           |               |               |               |               |               |               |              | Bits         | 3            |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                          | 31:16     | _             | _             | _             | _             | _             | _             | _            | -            | -            | _            | -            | _            | _            | _            | _            | -            | 0000          |

| 0300                        | ANSLLD                          | 15:0      |               | _             | _             | _             | _             | _             | _            | -            | -            | _            | 1            | _            | ANSELD3      | ANSELD2      | ANSELD1      | -            | 000E          |

| 6310                        | TRISD                           | 31:16     | 1             | _             | _             | _             | _             | -             | _            | I            | I            | _            | 1            | _            | _            | _            | _            | -            | 0000          |

| 0310                        | TIXIOD                          | 15:0      | TRISD15       | TRISD14       | TRISD13       | TRISD12       | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | xxxx          |

| 5320                        | PORTD                           | 31:16     | _             | _             | _             | _             | _             | _             | _            |              |              | _            | _            |              | _            | _            | _            |              | 0000          |

| 3320                        | TOKID                           | 15:0      | RD15          | RD14          | RD13          | RD12          | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | xxxx          |

| 6330                        | LATD                            | 31:16     | _             | _             | _             | _             | _             | _             | _            |              |              | _            | _            |              | _            | _            | _            |              | 0000          |

| 0000                        | L/(1D                           | 15:0      | LATD15        | LATD14        | LATD13        | LATD12        | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | xxxx          |

| 6340                        | ODCD                            | 31:16     | _             | _             | _             | _             | _             | _             | _            | _            | _            | _            | _            |              | _            | _            | _            | _            | 0000          |

| 0040                        | ODOD                            | 15:0      | ODCD15        | ODCD14        | ODCD13        | ODCD12        | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | xxxx          |

| 6350                        | CNPUD                           | 31:16     | _             | _             | _             | _             | _             | _             | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        | 0111 02                         |           | CNPUD15       | CNPUD14       | CNPUD13       | CNPUD12       | CNPUD11       | CNPUD10       | CNPUD9       | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | xxxx          |

| 6360                        | CNPDD                           | 31:16     | -             | _             | _             | _             | _             | _             | _            | 1            | ı            | _            | I            | _            | _            | _            | _            | -            | 0000          |

| -                           | 0.1. 22                         |           | CNPDD15       | CNPDD14       | CNPDD13       | CNPDD12       | CNPDD11       | CNPDD10       | CNPDD9       | CNPDD8       | CNPDD7       | CNPDD6       | CNPDD5       | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | xxxx          |

| 6370                        | CNCOND                          | 31:16     | -             | _             | _             | _             | _             | _             | _            | -            | -            | _            | 1            | _            | _            | _            | _            | -            | 0000          |

| 00.0                        | 0.100112                        | 15:0      | ON            | _             | SIDL          | _             | _             | _             | _            | -            | -            | _            | 1            | _            | _            | _            | _            | -            | 0000          |

| 6380                        | CNEND                           | 31:16     | -             | _             | _             | _             | _             | _             | _            | 1            | I            | _            | I            | _            | _            | _            | _            | -            | 0000          |

| -                           | 0112112                         | 15:0      | CNIED15       | CNIED14       | CNIED13       | CNIED12       | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | xxxx          |

|                             |                                 | 31:16     | _             | _             | _             | _             | _             | _             | _            |              | -            | _            |              | _            | _            | _            | _            | _            | 0000          |

| 6390                        | CNSTATD                         | 15:0      | CNS<br>TATD15 | CN<br>STATD14 | CN<br>STATD13 | CN<br>STATD12 | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | xxxx          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

TABLE 12-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| Virtual Address<br>(BF80_#) | Register<br>Name     | Bit Range |       |       |       |       |       | Bits  |      |      |      |      |      |      |      |       |        |      |            |  |  |

|-----------------------------|----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|--|--|

|                             |                      | •         | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |  |  |

| FC14 RPI                    | PE5R                 | 31:16     | _     |       | _     |       |       | _     | _    |      |      | _    |      |      |      | _     |        |      | 0000       |  |  |

| T C 14 KF                   | LJK                  | 15:0      | _     |       | _     | _     | -     | _     | _    | _    | _    | _    | _    | _    |      | RPE5  | <3:0>  |      | 0000       |  |  |

| FC20 RPE                    | PE8R <sup>(1)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |  |  |

| 1 020 KFI                   | - LOIX.              | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPE8  | <3:0>  |      | 0000       |  |  |

| FC24 RPE                    | PE9R <sup>(1)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |  |  |

| 1024 1011                   |                      | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPE9  | <3:0>  |      | 0000       |  |  |

| FC40 RPF                    | PF0R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |  |  |

| 1040 1011                   | 1 010                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF0  | <3:0>  |      | 0000       |  |  |

| FC44 RPF                    | PF1R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |  |  |

| 1044   1011                 |                      | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF1  | <3:0>  |      | 0000       |  |  |

| FC48 RPF                    | PF2R <sup>(3)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |  |  |

| 1040 1011                   |                      | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF2  | <3:0>  |      | 0000       |  |  |

| FC4C RPI                    | PF3R <sup>(2)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |  |  |

| 1 040 141                   | TOIC                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF3  | <3:0>  |      | 0000       |  |  |

| FC50 RPF                    | PF4R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |  |  |

| 1 030 1111                  | 1 711                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF4  | <3:0>  |      | 0000       |  |  |

| FC54 RPF                    | PF5R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    |      |      | _    |      | _    | _    | _     | _      | _    | 0000       |  |  |

| 1 004 141                   | 1 010                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF5  | <3:0>  |      | 0000       |  |  |

| FC58 RPF                    | PF6R <sup>(2)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    |      |      | _    |      | _    | _    | _     | _      | _    | 0000       |  |  |

| T C36 KFI                   | TI UK                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF6  | <3:0>  |      | 0000       |  |  |

| FC60 RPF                    | PF8R <sup>(1)</sup>  | 31:16     | _     | _     | _     | _     | -     | _     | _    | _    | _    | _    | _    | _    | -    | _     | _      | _    | 0000       |  |  |

| T COO INFI                  | -1 OK                | 15:0      | _     | _     | _     | _     | _     | _     | _    |      |      | _    |      | _    |      | RPF8  | <3:0>  |      | 0000       |  |  |

| FC70 RPF                    | PF12R <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | _    |      |      | _    |      | _    | _    | _     | _      | _    | 0000       |  |  |

| 1070 1011                   | 1 121(**             | 15:0      | _     | _     | _     | _     | -     | _     | _    | _    | _    | _    | _    | _    |      | RPF12 | 2<3:0> |      | 0000       |  |  |

| FC74 RPF                    | PF13R <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | _    |      |      | _    |      | _    | _    | _     | _      | _    | 0000       |  |  |

| 1074 1011                   | 1 1010               | 15:0      | _     | _     | _     | _     | _     | _     | _    |      |      | _    |      | _    |      | RPF13 | 3<3:0> |      | 0000       |  |  |

| FC80 RP0                    | PG0R <sup>(1)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |  |  |

| T COU INFO                  | GUIN                 | 15:0      | _     | _     | _     | _     | _     | _     | _    |      |      | _    |      | _    |      | RPG0  | <3:0>  |      | 0000       |  |  |

| FC84 RP0                    | PG1R <sup>(1)</sup>  | 31:16     | _     | -     | _     | _     | -     | _     | _    | _    | _    | _    | _    | _    | -    | _     | _      | _    | 0000       |  |  |

| 1 004 KF                    |                      | 15:0      | _     |       | _     | _     | -     | _     | _    | _    |      | _    | _    | -    |      | RPG1  | <3:0>  |      | 0000       |  |  |

| ECOO DD                     | DC6D                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      |      | 0000       |  |  |

| FC98 RP0                    | PG6R                 | 15:0      | _     | _     | _     | _     | _     | _     |      | _    |      |      |      | _    |      | RPG6  | <3:0>  |      | 0000       |  |  |

| ECOC DD                     | DC7D                 | 31:16     | _     |       | _     | _     |       | _     | _    | _    | _    | _    | _    | _    |      | _     | _      |      | 0000       |  |  |

| FC9C RP0                    | PG7R                 | 15:0      | _     | -     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPG7  | <3:0>  |      | 0000       |  |  |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

<sup>2:</sup> This register is only available on devices without a USB module.

<sup>3:</sup> This register is not available on 64-pin devices with a USB module.

## 13.2 Control Registers

## TABLE 13-1: TIMER1 REGISTER MAP

|                           | 0                               |           |       | INECIO |       |       |       |       |      |      |        |      |       |        |      |       |      |      |           |

|---------------------------|---------------------------------|-----------|-------|--------|-------|-------|-------|-------|------|------|--------|------|-------|--------|------|-------|------|------|-----------|

| ess                       |                                 | 0         |       | Bits   |       |       |       |       |      |      |        |      |       |        |      |       |      |      | S.        |

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14  | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5  | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Reset |

| 0600                      | T1CON                           | 31:16     | _     | _      | _     | _     | _     | _     | _    | _    | _      | _    | _     | _      | _    | _     | _    | _    | 0000      |

| 0600                      | TICON                           | 15:0      | ON    | _      | SIDL  | TWDIS | TWIP  | _     | _    | _    | TGATE  | _    | TCKPS | S<1:0> | _    | TSYNC | TCS  | _    | 0000      |

| 0610                      | TMR1                            | 31:16     |       |        | _     | _     | _     | _     | _    | _    | _      |      | _     | -      | _    | _     | _    | -    | 0000      |

| 0010                      | TIVITY                          | 15:0      |       |        |       |       |       |       |      | TMR1 | <15:0> |      |       |        |      |       |      |      | 0000      |

| 0620                      | PR1                             | 31:16     | _     | 1      | -     | _     | -     | -     | _    | -    | _      | -    | _     | I      | _    | _     | -    | -    | 0000      |

| 0020                      | 1 181                           | 15:0      |       |        |       |       |       |       |      | PR1< | 15:0>  |      |       |        |      |       |      |      | FFFF      |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

PIC32MX330/350/370/430/450/470

REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | _                 | _                | _                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             | _                 | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 **ON:** Timer On bit<sup>(1)</sup>

1 = Timer is enabled

0 = Timer is disabled

bit 14 Unimplemented: Read as '0'

bit 13 SIDL: Stop in Idle Mode bit

1 = Discontinue operation when device enters Idle mode

0 = Continue operation even in Idle mode

bit 12 **TWDIS:** Asynchronous Timer Write Disable bit

1 = Writes to TMR1 are ignored until pending write operation completes

0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)

bit 11 **TWIP:** Asynchronous Timer Write in Progress bit

In Asynchronous Timer mode:

1 = Asynchronous write to TMR1 register in progress

0 = Asynchronous write to TMR1 register complete

In Synchronous Timer mode:

This bit is read as '0'.

bit 10-8 Unimplemented: Read as '0'

bit 7 TGATE: Timer Gated Time Accumulation Enable bit

$\frac{\text{When TCS} = 1:}{\text{This bit is ignored.}}$

When TCS = 0:

1 = Gated time accumulation is enabled

0 = Gated time accumulation is disabled

bit 6 Unimplemented: Read as '0'

bit 5-4 TCKPS<1:0>: Timer Input Clock Prescale Select bits

11 = 1:256 prescale value

10 = 1:64 prescale value

01 = 1:8 prescale value

00 = 1:1 prescale value

bit 3 Unimplemented: Read as '0'

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## **REGISTER 18-1: SPIXCON: SPI CONTROL REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 04:04        | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 31:24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN             | FRMSYPW           | F                 | FRMCNT<2:0>      |                       |

| 00.40        | R/W-0                  | U-0                | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |

| 23:16        | MCLKSEL <sup>(2)</sup> | _                  | _                 | _                 | _                 | _                 | SPIFE            | ENHBUF <sup>(2)</sup> |

| 15:0         | R/W-0                  | U-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 15:8         | ON <sup>(1)</sup>      | _                  | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |

| 7:0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |

| 7:0          | SSEN                   | CKP <sup>(4)</sup> | MSTEN             | DISSDI            | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31 FRMEN: Framed SPI Support bit

1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

0 = Framed SPI support is disabled

bit 30 FRMSYNC: Frame Sync Pulse Direction Control on SSx pin bit (Framed SPI mode only)

1 = Frame sync pulse input (Slave mode)

0 = Frame sync pulse output (Master mode)

bit 29 **FRMPOL:** Frame Sync Polarity bit (Framed SPI mode only)

1 = Frame pulse is active-high

0 = Frame pulse is active-low

bit 28 MSSEN: Master Mode Slave Select Enable bit

1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

0 = Slave select SPI support is disabled.

bit 27 FRMSYPW: Frame Sync Pulse Width bit

1 = Frame sync pulse is one character wide

0 = Frame sync pulse is one clock wide

bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in FRAMED\_SYNC mode.

111 = Reserved; do not use

110 = Reserved; do not use

101 = Generate a frame sync pulse on every 32 data characters

100 = Generate a frame sync pulse on every 16 data characters

011 = Generate a frame sync pulse on every 8 data characters

010 = Generate a frame sync pulse on every 4 data characters

001 = Generate a frame sync pulse on every 2 data characters

000 = Generate a frame sync pulse on every data character **MCLKSEL**: Master Clock Enable bit<sup>(2)</sup>

1 = REFCLK is used by the Baud Rate Generator

0 = PBCLK is used by the Baud Rate Generator

bit 22-18 Unimplemented: Read as '0'

bit 23

**Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

2: This bit can only be written when the ON bit = 0.

3: This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

**4:** When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

### REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)

- bit 8 **TRMT:** Transmit Shift Register is Empty bit (read-only)

- 1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)

- 0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer

- bit 7-6 URXISEL<1:0>: Receive Interrupt Mode Selection bit

- 11 = Reserved; do not use

- 10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters)

- 01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters)

- 00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character)

- bit 5 **ADDEN:** Address Character Detect bit (bit 8 of received data = 1)

- 1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect

- 0 = Address Detect mode is disabled

- bit 4 RIDLE: Receiver Idle bit (read-only)

- 1 = Receiver is Idle

- 0 = Data is being received

- bit 3 **PERR:** Parity Error Status bit (read-only)

- 1 = Parity error has been detected for the current character

- 0 = Parity error has not been detected

- bit 2 **FERR:** Framing Error Status bit (read-only)

- 1 = Framing error has been detected for the current character

- 0 = Framing error has not been detected

- bit 1 **OERR:** Receive Buffer Overrun Error Status bit.

This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state.

- 1 = Receive buffer has overflowed

- 0 = Receive buffer has not overflowed

- bit 0 **URXDA:** Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

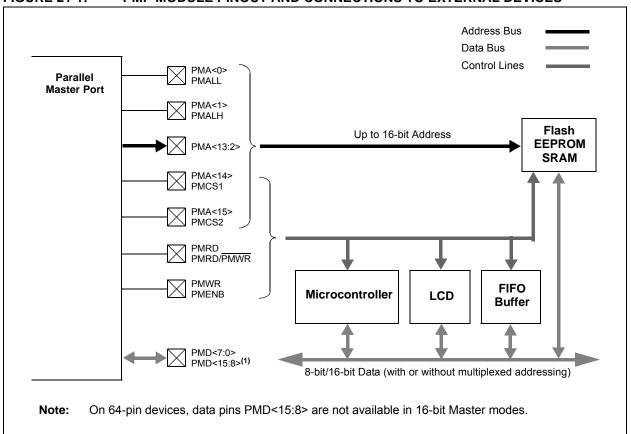

# 21.0 PARALLEL MASTER PORT (PMP)

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 13. "Parallel Master Port (PMP)"** (DS60001128), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable.

The following are key features of the PMP module:

- · 8-bit.16-bit interface

- · Up to 16 programmable address lines

- · Up to two Chip Select lines

- Programmable strobe options

- Individual read and write strobes, or

- Read/write strobe with enable strobe

- · Address auto-increment/auto-decrement

- · Programmable address/data multiplexing

- · Programmable polarity on control signals

- · Parallel Slave Port support

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- · Programmable Wait states

- · Operate during CPU Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

- · Freeze option for in-circuit debugging

**Note:** On 64-pin devices, data pins PMD<15:8> are not available in 16-bit Master modes.

FIGURE 21-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

TABLE 31-5: DC CHARACTERISTICS: OPERATING CURRENT (IDD)

| DC CHARA      | CTERISTICS             | <b>3</b> | (unless of | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |             |  |  |  |  |  |

|---------------|------------------------|----------|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|--|--|--|--|--|

| Parameter No. | Typical <sup>(3)</sup> | Maximum  | Units      | Jnits Conditions                                                                                                                                                                                                                                         |             |  |  |  |  |  |

| Operating (   | Current (IDD)          | (1,2)    |            |                                                                                                                                                                                                                                                          |             |  |  |  |  |  |

| DC20          | 2.5                    | 4        | mA         | 4 MHz                                                                                                                                                                                                                                                    |             |  |  |  |  |  |

| DC21          | 6                      | 9        | mA         | 10 MHz (Note 4)                                                                                                                                                                                                                                          |             |  |  |  |  |  |

| DC22          | 11                     | 17       | mA         | 20 M                                                                                                                                                                                                                                                     | Hz (Note 4) |  |  |  |  |  |

| DC23          | 21                     | 32       | mA         | 40 M                                                                                                                                                                                                                                                     | Hz (Note 4) |  |  |  |  |  |

| DC24          | 30                     | 45       | mA         | 60 M                                                                                                                                                                                                                                                     | Hz (Note 4) |  |  |  |  |  |

| DC25          | 40                     | 60       | mA         | 3                                                                                                                                                                                                                                                        | 30 MHz      |  |  |  |  |  |

| DC25a         | 50                     | 75       | mA         | 100 MHz, -40°C ≤ TA ≤ +85°C                                                                                                                                                                                                                              |             |  |  |  |  |  |

| DC25c         | 72                     | 84       | mA         | 120 MHz, 0°C ≤ Ta ≤ +70°C                                                                                                                                                                                                                                |             |  |  |  |  |  |

| DC26          | 100                    | _        | μA         | +25°C, 3.3V LPRC (31 kHz) <b>(Note</b>                                                                                                                                                                                                                   |             |  |  |  |  |  |

- **Note 1:** A device's IDD supply current is mainly a function of the operating voltage and frequency. Other factors, such as PBCLK (Peripheral Bus Clock) frequency, number of peripheral modules enabled, internal code execution pattern, execution from Program Flash memory vs. SRAM, I/O pin loading and switching rate, oscillator type, as well as temperature, can have an impact on the current consumption.

- 2: The test conditions for IDD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- · OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU, program Flash, and SRAM data memory are operational, program Flash memory Wait states = 7, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating (ON bit = 0), but the associated PMD bit is clear

- · WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- CPU executing while(1) statement from Flash

- · RTCC and JTAG are disabled

- **3:** Data in "Typical" column is at 3.3V, 25°C at specified operating frequency unless otherwise stated. Parameters are for design guidance only and are not tested.

- 4: This parameter is characterized, but not tested in manufacturing.

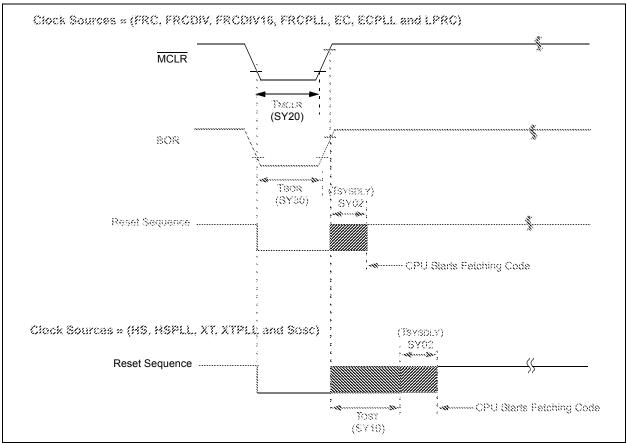

FIGURE 31-5: EXTERNAL RESET TIMING CHARACTERISTICS

**TABLE 31-23: RESETS TIMING**

| AC CHA        | \RACTERI | ISTICS                                                                                                                         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated) Operating temperature $0^{\circ}C \leq TA \leq +70^{\circ}C \text{ for Commercia} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \text{ for V-temp}$ |                              |      |       |            |  |  |  |

|---------------|----------|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------|------|-------|------------|--|--|--|

| Param.<br>No. | Symbol   | Characteristics <sup>(1)</sup>                                                                                                 | Min.                                                                                                                                                                                                                                                                                    | Typical <sup>(2)</sup>       | Max. | Units | Conditions |  |  |  |

| SY00          | TPU      | Power-up Period<br>Internal Voltage Regulator Enabled                                                                          | _                                                                                                                                                                                                                                                                                       | 400                          | 600  | μS    | _          |  |  |  |

| SY02          | TSYSDLY  | System Delay Period: Time Required to Reload Device Configuration Fuses plus SYSCLK Delay before First instruction is Fetched. | _                                                                                                                                                                                                                                                                                       | 1 μs +<br>8 SYSCLK<br>cycles | _    | _     | _          |  |  |  |

| SY20          | TMCLR    | MCLR Pulse Width (low)                                                                                                         | 2                                                                                                                                                                                                                                                                                       | _                            | _    | μS    | _          |  |  |  |

| SY30          | TBOR     | BOR Pulse Width (low)                                                                                                          | _                                                                                                                                                                                                                                                                                       | 1                            | _    | μS    | _          |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

<sup>2:</sup> Data in "Typ" column is at 3.3V, 25°C unless otherwise stated. Characterized by design but not tested.

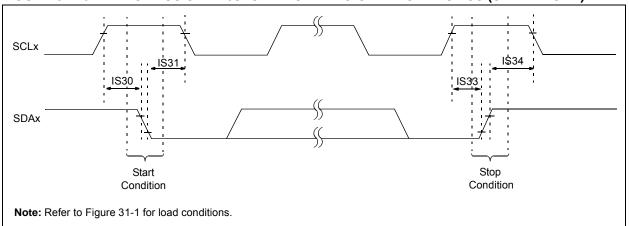

## FIGURE 31-16: I2Cx BUS START/STOP BITS TIMING CHARACTERISTICS (SLAVE MODE)

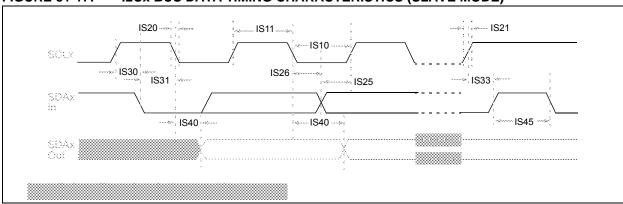

## FIGURE 31-17: I2Cx BUS DATA TIMING CHARACTERISTICS (SLAVE MODE)

**FIGURE 32-6:** TYPICAL IPD CURRENT @ VDD = 3.3V

TYPICAL IPD CURRENT @ VDD = 3.3V **FIGURE 32-7:**

**FIGURE 32-8:** TYPICAL IIDLE CURRENT @ VDD = 3.3V

## **INDEX**

| A                                                                 |     | CPU Module2                                                 | 7, 35 |

|-------------------------------------------------------------------|-----|-------------------------------------------------------------|-------|

| AC Characteristics                                                | 205 | CTMU                                                        |       |

| 10-Bit Conversion Rate Parameters                                 |     | Registers                                                   | . 253 |

| ADC Specifications                                                |     | Customer Change Notification Service                        | . 359 |

| Analog-to-Digital Conversion Requirements                         |     | Customer Notification Service                               | . 359 |

| EJTAG Timing Requirements                                         |     | Customer Support                                            | . 359 |