Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 120MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 49                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 28x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-VFQFN Exposed Pad                                                             |

| Supplier Device Package    | 64-QFN (9x9)                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256h-120-mr |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### 3.2 Architecture Overview

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- Enhanced JTAG (EJTAG) Controller

### 3.2.1 EXECUTION UNIT

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction

address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

### 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

| Divide UNIT LATENCIES AND REPEAT RATES |                                                |         |             |  |  |  |  |  |  |

|----------------------------------------|------------------------------------------------|---------|-------------|--|--|--|--|--|--|

| Op code                                | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |  |  |  |  |  |  |

| MULT/MULTU, MADD/MADDU,                | 16 bits                                        | 1       | 1           |  |  |  |  |  |  |

| MSUB/MSUBU                             | 32 bits                                        | 2       | 2           |  |  |  |  |  |  |

| MUL                                    | 16 bits                                        | 2       | 1           |  |  |  |  |  |  |

|                                        | 32 bits                                        | 3       | 2           |  |  |  |  |  |  |

| DIV/DIVU                               | 8 bits                                         | 12      | 11          |  |  |  |  |  |  |

|                                        | 16 bits                                        | 19      | 18          |  |  |  |  |  |  |

|                                        | 24 bits                                        | 26      | 25          |  |  |  |  |  |  |

|                                        | 32 bits                                        | 33      | 32          |  |  |  |  |  |  |

### TABLE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGER MULTIPLY/ DIVIDE UNIT LATENCIES AND REPEAT RATES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | —                    | —                     | —                      | —                 | —                | _                |

| 22.16        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | -                    | —                     | —                      | —                 |                  | _                |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> | —                 | —                | _                |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 |                      | —                     | NVMOP<3:0>             |                   |                  |                  |

### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

### Legend:

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

| bit 15   | WR: Write Control bit                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------|

|          | This bit is writable when WREN = 1 and the unlock sequence is followed.                                             |

|          | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                               |

|          | 0 = Flash operation complete or inactive                                                                            |

| bit 14   | WREN: Write Enable bit                                                                                              |

|          | 1 = Enable writes to WR bit and enables LVD circuit                                                                 |

|          | 0 = Disable writes to WR bit and disables LVD circuit                                                               |

|          | This is the only bit in this register reset by a device Reset.                                                      |

| bit 13   | WRERR: Write Error bit <sup>(1)</sup>                                                                               |

|          | This bit is read-only and is automatically set by hardware.                                                         |

|          | 1 = Program or erase sequence did not complete successfully                                                         |

|          | 0 = Program or erase sequence completed normally                                                                    |

| bit 12   | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                   |

|          | This bit is read-only and is automatically set by hardware.                                                         |

|          | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                |

|          | 0 = Voltage level is acceptable for programming                                                                     |

| bit 11   | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                 |

|          | This bit is read-only and is automatically set, and cleared, by hardware.                                           |

|          | 1 = Low-voltage event active                                                                                        |

|          | 0 = Low-voltage event NOT active                                                                                    |

| bit 10-4 | Unimplemented: Read as '0'                                                                                          |

| bit 3-0  | NVMOP<3:0>: NVM Operation bits                                                                                      |

|          | These bits are writable when WREN = 0.                                                                              |

|          | 1111 = Reserved                                                                                                     |

|          | •                                                                                                                   |

|          |                                                                                                                     |

|          | 0111 = Reserved                                                                                                     |

|          | 0110 = No operation                                                                                                 |

|          | 0101 = Program Flash (PFM) erase operation: erases PFM, if all pages are not write-protected                        |

|          | 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected                          |

|          | 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected<br>0010 = No operation |

|          | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected                      |

|          | 0000 = No operation                                                                                                 |

|          |                                                                                                                     |

|          |                                                                                                                     |

**Note 1:** This bit is cleared by setting NVMOP = 0000, and initiating a Flash operation (i.e., WR).

## 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features      |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|

|       | of the PIC32MX330/350/370/430/450/           |  |  |  |  |  |  |

|       | 470 family of devices. It is not intended to |  |  |  |  |  |  |

|       | be a comprehensive reference source. To      |  |  |  |  |  |  |

|       | complement the information in this data      |  |  |  |  |  |  |

|       | sheet, refer to Section 6. "Oscillator       |  |  |  |  |  |  |

|       | Configuration" (DS60001112), which is        |  |  |  |  |  |  |

|       | available from the Documentation >           |  |  |  |  |  |  |

|       | Reference Manual section of the              |  |  |  |  |  |  |

|       | Microchip PIC32 web site                     |  |  |  |  |  |  |

|       | (www.microchip.com/pic32).                   |  |  |  |  |  |  |

The PIC32MX330/350/370/430/450/470 oscillator system has the following modules and features:

- A Total of four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

### **Oscillator Control Registers** 8.1

| TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP |                                 |           |       |       |         |            |         |       |           |        |         |                      |          |       |        |                       |           |          |                     |

|--------------------------------------------|---------------------------------|-----------|-------|-------|---------|------------|---------|-------|-----------|--------|---------|----------------------|----------|-------|--------|-----------------------|-----------|----------|---------------------|

| ess                                        |                                 |           | Bits  |       |         |            |         |       |           |        |         |                      |          |       |        | 6                     |           |          |                     |

| Virtual Address<br>(BF80_#)                | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13   | 28/12      | 27/11   | 26/10 | 25/9      | 24/8   | 23/7    | 22/6                 | 21/5     | 20/4  | 19/3   | 18/2                  | 17/1      | 16/0     | All Reset           |

| F000                                       | OSCCON                          | 31:16     | _     | _     | PI      | LLODIV<2:0 | >       |       | FRCDIV<2: | 0>     | —       | SOSCRDY              | PBDIVRDY | PBDI\ | /<1:0> | Pl                    | LMULT<2:0 | <b>`</b> | x1xx <sup>(2)</sup> |

| F000                                       | USCCON                          | 15:0      | _     |       | COSC<2: | 0>         | _       |       | NOSC<2:0  | )>     | CLKLOCK | ULOCK <sup>(4)</sup> | SLOCK    | SLPEN | CF     | UFRCEN <sup>(4)</sup> | SOSCEN    | OSWEN    | xxxx <sup>(2)</sup> |

| F010                                       | OSCTUN                          | 31:16     | —     | _     | _       | _          | _       | —     | —         |        | _       | —                    | _        | _     |        | —                     | _         | _        | 0000                |

| 1010                                       | 030101                          | 15:0      | —     | _     |         | —          | —       | —     | —         |        | -       | _                    |          |       | TUN    | <b>\&lt;5:0&gt;</b>   |           |          | 0000                |

| 5000                                       | REFOCON                         | 31:16     | _     |       |         |            |         |       |           |        | RODIV<  | 4:0>                 |          |       |        |                       |           |          | 0000                |

| F020                                       | REFUCUN                         | 15:0      | ON    | —     | SIDL    | OE         | RSLP    | —     | DIVSWEN   | ACTIVE | —       | —                    | —        | —     |        | ROSE                  | L<3:0>    |          | 0000                |

| 5000                                       | DEFOTDIM                        | 31:16     |       |       |         | I          | ROTRIM< | 8:0>  |           |        |         | _                    |          | _     | _      | _                     | _         | —        | 0000                |

| F030                                       | REFOTRIM                        | 15:0      | _     | _     |         | _          | _       | _     | _         |        | —       | _                    |          | _     |        | _                     |           | _        | 0000                |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

Reset values are dependent on the DEVCFGx Configuration bits and the type of reset. 2:

This bit is only available on devices with a USB module. 3:

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                     | —                 | _                 | _                 |                   | _                 | -                | —                     |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                   | —                 | _                 | _                 | _                 | —                 | _                | —                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | —                 | _                 | _                 | _                 | _                 | _                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | CHPF             | RI<1:0>               |

### REGISTER 10-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14-9 Unimplemented: Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

### bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 = Channel is disabled

### bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

0 = Channel is disabled on block transfer complete

### bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

- bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

### REGISTER 10-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)

bit 4 **CHDHIF:** Channel Destination Half Full Interrupt Flag bit

- 1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)

- 0 = No interrupt is pending

- bit 3 CHBCIF: Channel Block Transfer Complete Interrupt Flag bit

- 1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs

- 0 = No interrupt is pending

- bit 2 CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit

- 1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)

- 0 = No interrupt is pending

- bit 1 CHTAIF: Channel Transfer Abort Interrupt Flag bit

- 1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted

- 0 = No interrupt is pending

- bit 0 CHERIF: Channel Address Error Interrupt Flag bit

- 1 = A channel address error has been detected

- Either the source or the destination address is invalid.

- 0 = No interrupt is pending

## PIC32MX330/350/370/430/450/470

### REGISTER 10-12: DCHxSSIZ: DMA CHANNEL 'x' SOURCE SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                   | -                 | —                 | —                 | —                 | —                 | —                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   | —                 | —                 | —                 | _                 | —                 | _                | _                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHSSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | CHSSIZ            | <7:0>             |                   |                  |                  |  |  |

# Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHSSIZ<15:0>: Channel Source Size bits

1111111111111111 = 65,535 byte source size

### **REGISTER 10-13: DCHxDSIZ: DMA CHANNEL 'x' DESTINATION SIZE REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | _                 | —                 | _                 | _                 | —                 | _                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHDSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7.0          |                   |                   |                   | CHDSIZ            | <7:0>             |                   |                  |                  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

### TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       |       | ,     |      |      | Bit  | s    |      |          |        |        |         |        | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | —     | —     |       | —     | _     | _     | —    | —    |      |      | —    | —        | —      | —      | —       | _      | 0000       |

| 5390                        | UIEF9                           | 15:0      | —     | _     |       |       | _     | _     | —    | —    | —    |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53A0                        | U1EP10                          | 31:16     | —     | _     |       | _     |       |       | _    |      |      |      | _    | —        | _      | _      | _       | -      | 0000       |

| 53A0                        | UIEFIU                          | 15:0      | _     | _     |       | _     | -     | -     | _    | _    | _    |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 5560                        | UIEFII                          | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     | _     | _     | —     | _     | —     | —     | -    | -    | —    | —    | _    | —        | _      | _      | —       | _      | 0000       |

| 5300                        | UIEFIZ                          | 15:0      | _     | _     | —     | _     | —     | —     | -    | -    | —    | —    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     | _     |       | —     | _     | —     | —     |      | _    | _    | _    |      | —        | —      | _      | —       | _      | 0000       |

| 55D0                        | UIEF 13                         | 15:0      | _     | _     | —     | _     | —     | —     | -    | -    | —    | —    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     |       | _     | _     | _     | _     | _    | -    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     |       | _     | _     | _     | _     |      | _    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     |       | _     | _     | _     | _     |      | _    |      |      | _    | _        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     |       | _     | _     | _     | _     |      | _    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

### REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN BD banks

- 0 = Even/Odd buffer pointers not being Reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set the RESUME bit for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 |                   | _                 | —                 |                   |                   |                  | -                |  |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | —                 |                   | _                 | —                 | -                 |                   |                  | —                |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15.0         | —                 | _                 | _                 | —                 | -                 | -                 | -                | —                |  |  |  |

| 7:0          | U-0               | U-0               | U-0               | U-0               | U-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   |                   |                   |                   | FRMH<2:0>        |                  |  |  |  |

### REGISTER 11-14: U1FRMH: USB FRAME NUMBER HIGH REGISTER

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-3 Unimplemented: Read as '0'

bit 2-0 **FRMH<2:0>:** The Upper 3 bits of the Frame Numbers bits The register bits are updated with the current frame number whenever a SOF TOKEN is received.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        | —                 |                   | —                 | —                 | -                 | _                 | -                | —                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | _                 |                   | _                 | —                 | -                 | _                 |                  | —                |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 15.0         | _                 |                   |                   | —                 |                   | _                 |                  | —                |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   | PID<3             | 3:0>(1)           |                   | EP<3:0>           |                   |                  |                  |  |  |  |  |

### REGISTER 11-15: U1TOK: USB TOKEN REGISTER

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-4 **PID<3:0>:** Token Type Indicator bits<sup>(1)</sup>

0001 = OUT (TX) token type transaction

- 1001 = IN (RX) token type transaction

- 1101 = SETUP (TX) token type transaction

Note: All other values are reserved and must not be used.

bit 3-0 **EP<3:0>:** Token Command Endpoint Address bits The four bit value must specify a valid endpoint.

**Note 1:** All other values are reserved and must not be used.

|                             | PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY |           |           |           |           |           |       |       |      |      |      |      |      |          |          |          |          |      |               |

|-----------------------------|-------------------------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|----------|----------|----------|----------|------|---------------|

| ess                         |                                                                                     |           |           |           |           |           |       |       |      | Bits |      |      |      |          |          |          |          |      |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup>                                                     | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0 | All<br>Resets |

| 6210                        | TRISC                                                                               | 31:16     | _         | —         | _         | —         | _     | —     | _    | _    | _    | —    | —    | —        | _        | _        | —        | —    | 0000          |

| 0210                        | 11100                                                                               | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | —     | —     | —    | —    | —    | —    | —    | TRISC4   | TRISC3   | TRISC2   | TRISC1   | —    | xxxx          |

| 6220                        | PORTC                                                                               | 31:16     |           | _         | _         |           | _     | —     |      |      |      |      |      | —        | _        | _        | —        | _    | 0000          |

| 0220                        | 1 OKTO                                                                              | 15:0      | RC15      | RC14      | RC13      | RC12      | _     | —     | _    | —    | —    | —    | —    | RC4      | RC3      | RC2      | RC1      | —    | xxxx          |

| 6230                        | LATC                                                                                | 31:16     | _         | _         | _         | _         | -     | —     | _    | _    | _    | _    | —    | —        | _        | _        | —        | —    | 0000          |

| 0230                        | LAIO                                                                                | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | _     | —     | _    | _    | _    | _    | _    | LATC4    | LATC3    | LATC2    | LATC1    | —    | xxxx          |

| 6240                        | ODCC                                                                                | 31:16     | _         | —         | _         | —         |       | _     |      |      |      | _    | _    | _        | -        | -        | _        | —    | 0000          |

| 0240                        | ODCC                                                                                | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    |       | —     |      |      | _    | —    | —    | ODCC4    | ODCC3    | ODCC2    | ODCC1    | —    | xxxx          |

| 6250                        | CNPUC                                                                               | 31:16     |           | -         | -         | _         |       | —     |      |      | _    | —    | —    | -        | -        | -        | _        | —    | 0000          |

| 0250                        | CINFUC                                                                              | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | _     | —     | —    | —    | —    | -    | -    | CNPUC4   | CNPUC3   | CNPUC2   | CNPUC1   | —    | xxxx          |

| 6260                        | CNPDC                                                                               | 31:16     | -         | _         | _         | —         | —     | —     | —    | —    | —    | -    | -    | -        | —        | —        | _        | —    | 0000          |

| 0200                        | CINFDC                                                                              | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | —     | —     | —    | —    | —    | -    | -    | CNPDC4   | CNPDC3   | CNPDC2   | CNPDC1   | —    | xxxx          |

| 6270                        | CNCONC                                                                              | 31:16     | -         | _         | _         | —         | —     | —     | —    | —    | —    | -    | -    | -        | —        | —        | _        | —    | 0000          |

| 0270                        | CINCOINC                                                                            | 15:0      | ON        | _         | SIDL      | —         | —     | —     | —    | —    | —    | -    | -    | -        | —        | —        | _        | —    | 0000          |

| 6280                        | CNENC                                                                               | 31:16     | _         | _         |           | _         | _     | —     | —    | _    |      |      |      | _        | _        | _        | _        | —    | 0000          |

| 0200                        | GNEING                                                                              | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | _     | —     | —    | _    |      |      |      | CNIEC4   | CNIEC3   | CNIEC2   | CNIEC1   | —    | xxxx          |

| 6200                        | CNSTATC                                                                             | 31:16     | _         |           |           | _         | _     | —     | —    | _    |      |      |      | _        | _        | _        | _        | —    | 0000          |

| 0290                        | CINSTALC                                                                            | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 |       | _     |      | -    | _    |      | _    | CNSTATC4 | CNSTATC3 | CNSTATC2 | CNSTATC1 | —    | xxxx          |

## TABLE 12-5: PORTC REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

#### 17.1 **Control Registers**

### TABLE 17-1: OUTPUT COMPARE 1 THROUGH OUTPUT COMPARE 5 REGISTER MAP

| ess                         |                                 |               |       |             |       |       |       |       |      | Bi     | ts       |      |      |       |        |      |            |      |              |

|-----------------------------|---------------------------------|---------------|-------|-------------|-------|-------|-------|-------|------|--------|----------|------|------|-------|--------|------|------------|------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15 | 30/14       | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8   | 23/7     | 22/6 | 21/5 | 20/4  | 19/3   | 18/2 | 17/1       | 16/0 | All Resets   |

|                             | OC1CON                          | 31:16         | _     | —           | —     |       | _     | —     | —    | _      | _        | _    | —    | —     | _      |      | —          |      | 0000         |

| 3000                        |                                 | 15:0          | ON    | —           | SIDL  | _     | _     | —     | —    | _      | -        |      | OC32 | OCFLT | OCTSEL |      | OCM<2:0>   |      | 0000         |

| 3010                        | OC1R                            | 31:16         |       |             |       |       |       |       |      | OC1R   | <31.0>   |      |      |       |        |      |            |      | xxxx         |

| 0010                        | oom                             | 15:0          |       |             |       |       |       |       |      | 00111  | -011.0-  |      |      |       |        |      |            |      | xxxx         |

| 3020                        | OC1RS                           | 31:16         |       |             |       |       |       |       |      | OC1RS  | 6<31:0>  |      |      |       |        |      |            |      | XXXX         |

|                             |                                 | 15:0          |       |             |       |       |       |       |      |        |          |      |      |       |        |      | -          |      | XXXX         |

| 3200                        | OC2CON                          | 31:16         |       |             | -     | _     | _     |       |      | _      |          |      | —    | —<br> |        |      | -          | _    | 0000         |

|                             |                                 | 15:0<br>31:16 | ON    | _           | SIDL  |       |       |       |      |        | —        | —    | OC32 | OCFLT | OCTSEL |      | OCM<2:0>   |      | 0000         |

| 3210                        | OC2R                            | 15:0          |       |             |       |       |       |       |      | OC2R   | <31:0>   |      |      |       |        |      |            |      | xxxx         |

|                             |                                 | 31.16         |       |             |       |       |       |       |      |        |          |      |      |       |        |      |            |      | XXXX         |

| 3220                        | OC2RS                           | 15:0          |       | 0C2RS<31:0> |       |       |       |       |      |        |          |      |      | xxxx  |        |      |            |      |              |

|                             |                                 | 31.16         | _     |             | _     |       | _     | _     | _    |        | _        | _    | _    | _     |        | _    | _          |      | 0000         |

| 3400                        | OC3CON                          | 15:0          | ON    | _           | SIDL  | _     | _     | _     | _    | _      | _        | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0>   |      | 0000         |

| 0440                        | 0000                            | 31:16         |       |             |       |       |       |       |      | 0000   | -04-05   |      |      | •     |        |      |            |      | xxxx         |

| 3410                        | OC3R                            | 15:0          |       |             |       |       |       |       |      | OC3R   | <31.0>   |      |      |       |        |      |            |      | xxxx         |

| 3420                        | OC3RS                           | 31:16         |       |             |       |       |       |       |      | OC3RS  | <31·0>   |      |      |       |        |      |            |      | xxxx         |

| 0420                        | 000110                          | 15:0          |       |             |       |       |       |       |      | 000110 | -01.04   |      |      |       |        |      |            |      | xxxx         |

| 3600                        | OC4CON                          | 31:16         |       | _           | —     | _     | —     | _     | —    | _      | _        | _    | —    | —     | —      | _    | —          | —    | 0000         |

|                             |                                 | 15:0          | ON    | —           | SIDL  | —     | —     | —     | —    | —      | —        | _    | OC32 | OCFLT | OCTSEL |      | OCM<2:0>   |      | 0000         |

| 3610                        | OC4R                            | 31:16         | -     |             |       |       |       |       |      | OC4R   | <31:0>   |      |      |       |        |      |            |      | XXXX         |

|                             |                                 | 15:0          |       |             |       |       |       |       |      |        |          |      |      |       |        |      |            |      | XXXX         |

| 3620                        | OC4RS                           | 31:16<br>15:0 |       |             |       |       |       |       |      | OC4RS  | \$<31:0> |      |      |       |        |      |            |      | xxxx         |

|                             |                                 | 31:16         |       |             | _     |       | _     | _     | _    |        | _        | _    | _    |       |        | _    | _          |      | xxxx<br>0000 |

| 3800                        | OC5CON                          | 15:0          | ON    |             | SIDL  |       |       |       |      |        | _        |      | OC32 | OCFLT | OCTSEL |      | OCM<2:0>   |      | 0000         |

|                             |                                 | 31:16         |       |             | OIDE  |       |       |       |      |        |          |      | 0002 | OOLEI | OUTOLL |      | 00111-2.04 |      | xxxx         |

| 3810                        | OC5R                            | 15:0          |       |             |       |       |       |       |      | OC5R   | <31:0>   |      |      |       |        |      |            |      | xxxx         |

|                             | 0.0555                          | 31.16         |       |             |       |       |       |       |      | 0.05-  |          |      |      |       |        |      |            |      | xxxx         |

| 3820                        | OC5RS                           | 15:0          | 1     |             |       |       |       |       |      | OC5RS  | s<31:0>  |      |      |       |        |      |            |      | xxxx         |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information. Note 1:

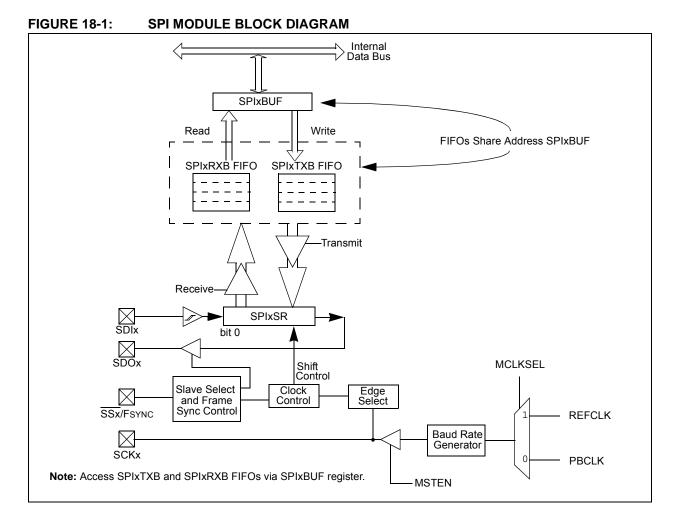

## 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. Some of the key features of the SPI module are:

- · Master and Slave modes support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- Operation during CPU Sleep and Idle mode

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-----------------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                     | —                     | _                 | _                 | _                 | —                 | _                | —                |  |  |  |  |  |

| 00.40        | U-0                   | U-0                   | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | —                     | —                     | _                 | _                 | —                 | —                 | —                | —                |  |  |  |  |  |

|              | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 15:8         | CS2 <sup>(1)</sup>    | CS1 <sup>(3)</sup>    |                   | ADDR<13:8>        |                   |                   |                  |                  |  |  |  |  |  |

|              | ADDR15 <sup>(2)</sup> | ADDR14 <sup>(4)</sup> |                   |                   | ADDR              | <13.02            |                  |                  |  |  |  |  |  |

| 7:0          | R/W-0                 | R/W-0                 | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

|              | ADDR<7:0>             |                       |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

### REGISTER 21-3: PMADDR: PARALLEL PORT ADDRESS REGISTER

### Legend:

| - <b>J</b>        |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 CS2: Chip Select 2 bit<sup>(1)</sup>

- 1 = Chip Select 2 is active

- 0 = Chip Select 2 is inactive

- bit 15 ADDR<15>: Destination Address bit 15<sup>(2)</sup>

- bit 14 CS1: Chip Select 1 bit<sup>(3)</sup>

- 1 = Chip Select 1 is active

- 0 = Chip Select 1 is inactive

- bit 14 ADDR<14>: Destination Address bit 14<sup>(4)</sup>

- bit 13-0 ADDR<13:0>: Address bits

- Note 1: When the CSF<1:0> bits (PMCON<7:6>) = 10 or 01.

- **2:** When the CSF<1:0> bits (PMCON<7:6>) = 00.

- 3: When the CSF<1:0> bits (PMCON<7:6>) = 10.

- **4:** When the CSF<1:0> bits (PMCON<7:6>) = 00 or 01.

### REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(3)</sup> 11111111 = Alarm will trigger 256 times

0000000 = Alarm will trigger one time

The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

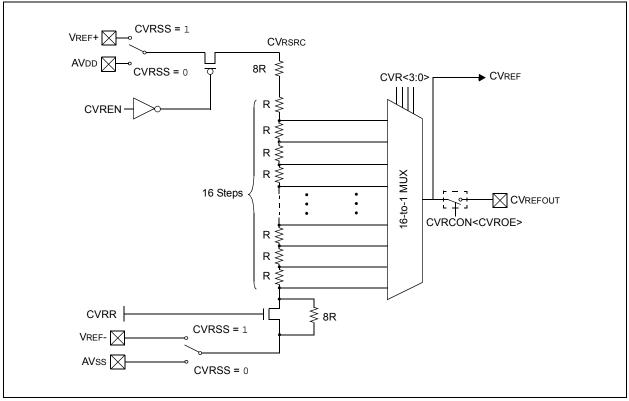

### 25.0 COMPARATOR VOLTAGE REFERENCE (CVREF)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The CVREF module is a 16-tap, resistor ladder network that provides a selectable reference voltage. Although its primary purpose is to provide a reference for the analog comparators, it also may be used independently of them. A block diagram of the module is illustrated in Figure 25-1. The resistor ladder is segmented to provide two ranges of voltage reference values and has a power-down function to conserve power when the reference is not being used. The module's supply reference can be provided from either device VDD/Vss or an external voltage reference. The CVREF output is available for the comparators and typically available for pin output.

The CVREF module has the following features:

- High and low range selection

- · Sixteen output levels available for each range

- Internally connected to comparators to conserve device pins

- · Output can be connected to a pin

### FIGURE 25-1: COMPARATOR VOLTAGE REFERENCE BLOCK DIAGRAM

NOTES:

| AC CHA        | RACTERI | STICS                             | $ \begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercia} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array} $ |      |      |       |                                                                                   |  |  |  |

|---------------|---------|-----------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------------------|--|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>    | Min.                                                                                                                                                                                                                                                                                                                                                | Тур. | Max. | Units | Conditions                                                                        |  |  |  |

| USB313        | VUSB3V3 | USB Voltage                       | 3.0                                                                                                                                                                                                                                                                                                                                                 | _    | 3.6  | V     | Voltage on VUSB3V3<br>must be in this range<br>for proper USB<br>operation        |  |  |  |

| USB315        | VILUSB  | Input Low Voltage for USB Buffer  | —                                                                                                                                                                                                                                                                                                                                                   |      | 0.8  | V     | —                                                                                 |  |  |  |

| USB316        | VIHUSB  | Input High Voltage for USB Buffer | 2.0                                                                                                                                                                                                                                                                                                                                                 |      | _    | V     | —                                                                                 |  |  |  |

| USB318        | VDIFS   | Differential Input Sensitivity    | _                                                                                                                                                                                                                                                                                                                                                   | _    | 0.2  | V     | The difference<br>between D+ and D-<br>must exceed this value<br>while VCM is met |  |  |  |

| USB319        | VCM     | Differential Common Mode Range    | 0.8                                                                                                                                                                                                                                                                                                                                                 |      | 2.5  | V     | —                                                                                 |  |  |  |

| USB320        | Zout    | Driver Output Impedance           | 28.0                                                                                                                                                                                                                                                                                                                                                |      | 44.0 | Ω     | —                                                                                 |  |  |  |

| USB321        | Vol     | Voltage Output Low                | 0.0                                                                                                                                                                                                                                                                                                                                                 | _    | 0.3  | V     | 1.425 kΩ load<br>connected to VUSB3V3                                             |  |  |  |

| USB322        | Vон     | Voltage Output High               | 2.8                                                                                                                                                                                                                                                                                                                                                 | —    | 3.6  | V     | 14.25 k $\Omega$ load connected to ground                                         |  |  |  |

### TABLE 31-41: OTG ELECTRICAL SPECIFICATIONS

Note 1: These parameters are characterized, but not tested in manufacturing.

PIC32MX330/350/370/430/450/470

100

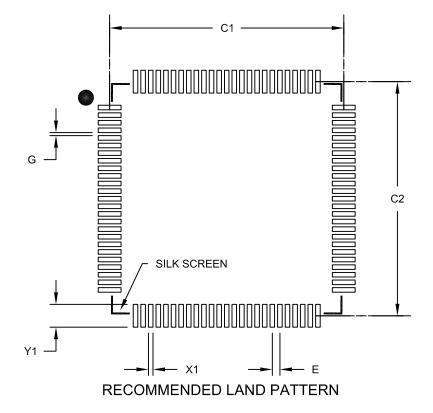

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |      |          |      |  |

|---------------------------|-------------|------|----------|------|--|

| Dimensior                 | l Limits    | MIN  | NOM      | MAX  |  |

| Contact Pitch             | E           |      | 0.50 BSC | -    |  |

| Contact Pad Spacing       | C1          |      | 15.40    |      |  |

| Contact Pad Spacing       | C2          |      | 15.40    |      |  |

| Contact Pad Width (X100)  | X1          |      |          | 0.30 |  |

| Contact Pad Length (X100) | Y1          |      |          | 1.50 |  |

| Distance Between Pads     | G           | 0.20 |          |      |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B