Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-VQFN (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256h-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# TABLE 7: PIN NAMES FOR 124-PIN DEVICES (CONTINUED)

| 124               | -PIN VTLA (BOTTOM VIEW) <sup>(1,2,3,4)</sup>                             | 17       |                   |                | A34           |                       |

|-------------------|--------------------------------------------------------------------------|----------|-------------------|----------------|---------------|-----------------------|

|                   | A                                                                        | 17       |                   | B13 B29        |               | nductive<br>ermal Pad |

|                   | PIC32MX430F064L<br>PIC32MX450F128L<br>PIC32MX450F256L<br>PIC32MX470F512L |          |                   | B1<br>B56      | B41           | A51                   |

|                   |                                                                          | y Indica | A1<br>tor         | A68            |               |                       |

| Package<br>Bump # | Full Pin Name                                                            |          | Package<br>Bump # |                | Full Pin Name |                       |

| B7                | MCLR                                                                     |          | B32               | SDA2/RA3       |               |                       |

| B8                | Vss                                                                      |          | B33               | TDO/RA5        |               |                       |

| B9                | TMS/CTED1/RA0                                                            |          | B34               | OSC1/CLKI/RC12 | 2             |                       |

| B10               | RPE9/RE9                                                                 |          | B35               | No Connect     |               |                       |

| B11               | AN4/C1INB/RB4                                                            |          | B36               | SCL1/RPA14/RA  | 14            |                       |

| B12               | Vss                                                                      |          | B37               | RPD8/RTCC/RD8  | 8             |                       |

| B13               | PGEC3/AN2/C2INB/RPB2/CTED13/RB2                                          |          | B38               | RPD10/SCK1/PM  | CS2/RD10      |                       |

| B14               | PGED1/AN0/RPB0/RB0                                                       |          | B39               | RPD0/INT0/RD0  |               |                       |

| B15               | No Connect                                                               |          | B40               | SOSCO/RPC14/T  | 1CK/RC14      |                       |

| B16               | PGED2/AN7/RPB7/CTED3/RB7                                                 |          | B41               | Vss            |               |                       |

| B17               | VREF+/CVREF+/PMA6/RA10                                                   |          | B42               | AN25/RPD2/RD2  |               |                       |

| B18               | AVss                                                                     |          | B43               | RPD12/PMD12/R  | D12           |                       |

| B19               | AN9/RPB9/CTED4/RB9                                                       |          | B44               | RPD4/PMWR/RD   | 4             |                       |

| B20               | AN11/PMA12/RB11                                                          |          | B45               | PMD14/RD6      |               |                       |

| B21               | Vdd                                                                      |          | B46               | No Connect     |               |                       |

| B22               | RPF13/RF13                                                               |          | B47               | No Connect     |               |                       |

| B23               | AN12/PMA11/RB12                                                          |          | B48               | VCAP           |               |                       |

| B24               | AN14/RPB14/CTED5/PMA1/RB14                                               |          | B49               | RPF0/PMD11/RF  | 0             |                       |

| B25               | Vss                                                                      |          | B50               | RPG1/PMD9/RG   | 1             |                       |

| B26               | RPD14/RD14                                                               |          | B51               | TRCLK/RA6      |               |                       |

| B27               | RPF4/PMA9/RF4                                                            |          | B52               | PMD0/RE0       |               |                       |

| B28               | No Connect                                                               |          | B53               | VDD            |               |                       |

| B29               | RPF8/RF8                                                                 |          | B54               | TRD2/RG14      |               |                       |

| B30               | VUSB3V3                                                                  |          | B55               | TRD0/RG13      |               |                       |

| B31               | D+                                                                       |          | B56               | RPE3/CTPLS/PM  | D3/RE3        |                       |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: Shaded package bumps are 5V tolerant.

4: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

# PIC32MX330/350/370/430/450/470

|          |                        | Pin Numb          | er                 |             |                |                                   |

|----------|------------------------|-------------------|--------------------|-------------|----------------|-----------------------------------|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP   | 124-pin<br>VTLA    | Pin<br>Type | Buffer<br>Type | Description                       |

| RE0      | 60                     | 93                | B52                | I/O         | ST             |                                   |

| RE1      | 61                     | 94                | A64                | I/O         | ST             |                                   |

| RE2      | 62                     | 98                | A66                | I/O         | ST             |                                   |

| RE3      | 63                     | 99                | B56                | I/O         | ST             |                                   |

| RE4      | 64                     | 100               | A67                | I/O         | ST             | DODIE is a hidiractional I/O part |

| RE5      | 1                      | 3                 | B2                 | I/O         | ST             | PORTE is a bidirectional I/O port |

| RE6      | 2                      | 4                 | A4                 | I/O         | ST             |                                   |

| RE7      | 3                      | 5                 | B3                 | I/O         | ST             |                                   |

| RE8      | —                      | 18                | A11                | I/O         | ST             | ]                                 |

| RE9      | —                      | 19                | B10                | I/O         | ST             | ]                                 |

| RF0      | 58                     | 87                | B49                | I/O         | ST             |                                   |

| RF1      | 59                     | 88                | A60                | I/O         | ST             | 1                                 |

| RF2      | 34(1)                  | 52                | A36                | I/O         | ST             | 1                                 |

| RF3      | 33                     | 51                | A35                | I/O         | ST             |                                   |

| RF4      | 31                     | 49                | B27                | I/O         | ST             |                                   |

| RF5      | 32                     | 50                | A32                | I/O         | ST             | PORTF is a bidirectional I/O port |

| RF6      | 35(1)                  | 55(1)             | B30 <sup>(1)</sup> | I/O         | ST             |                                   |

| RF7      | —                      | 54(1)             | A37 <sup>(1)</sup> | I/O         | ST             |                                   |

| RF8      | —                      | 53                | B29                | I/O         | ST             |                                   |

| RF12     | —                      | 40                | A27                | I/O         | ST             |                                   |

| RF13     | —                      | 39                | B22                | I/O         | ST             |                                   |

| RG0      |                        | 90                | A61                | I/O         | ST             |                                   |

| RG1      |                        | 89                | B50                | I/O         | ST             |                                   |

| RG2      | 37(1)                  | 57(1)             | B31                | I/O         | ST             |                                   |

| RG3      | 36 <sup>(1)</sup>      | 56 <sup>(1)</sup> | A38                | I/O         | ST             |                                   |

| RG6      | 4                      | 10                | A7                 | I/O         | ST             |                                   |

| RG7      | 5                      | 11                | B6                 | I/O         | ST             | POPTC is a hidiractional 1/0 part |

| RG8      | 6                      | 12                | A8                 | I/O         | ST             | PORTG is a bidirectional I/O port |

| RG9      | 8                      | 14                | A9                 | I/O         | ST             |                                   |

| RG12     | —                      | 96                | A65                | I/O         | ST             | ]                                 |

| RG13     | —                      | 97                | B55                | I/O         | ST             | ]                                 |

| RG14     | —                      | 95                | B54                | I/O         | ST             | ]                                 |

| RG15     | _                      | 1                 | A2                 | I/O         | ST             |                                   |

| T1CK     | 48                     | 74                | B40                | I           | ST             | Timer1 External Clock Input       |

| T2CK     | PPS                    | PPS               | PPS                | I           | ST             | Timer2 External Clock Input       |

| ТЗСК     | PPS                    | PPS               | PPS                | I           | ST             | Timer3 External Clock Input       |

| T4CK     | PPS                    | PPS               | PPS                | I           | ST             | Timer4 External Clock Input       |

| T5CK     | PPS                    | PPS               | PPS                | 1           | ST             | Timer5 External Clock Input       |

#### TABLE 1-1-PINOLIT I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

**Note 1:** This pin is only available on devices without a USB module. 2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 |                  | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | _                 | —                 | _                 | _                 | —                 | —                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8         | BMXDKPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | BMXDK             | PBA<7:0>          |                   |                  |                  |  |  |  |

### REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

### Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 **BMXDKPBA<15:10>:** DRM Kernel Program Base Address bits When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 BMXDKPBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | NVMDATA<31:24>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | NVMDATA<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | NVMDATA<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   |                   |                   | NVMD              | ATA<7:0>          |                   |                  |                  |  |  |  |  |

### REGISTER 5-4: NVMDATA: FLASH PROGRAM DATA REGISTER

### Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 NVMDATA<31:0>: Flash Programming Data bits

Note: The bits in this register are only reset by a Power-on Reset (POR).

### REGISTER 5-5: NVMSRCADDR: SOURCE DATA ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        |                   | NVMSRCADDR<31:24> |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.10        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | NVMSRCADDR<23:16> |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | NVMSRCADDR<15:8>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          |                   | NVMSRCADDR<7:0>   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                           |                             |  |  |  |

|-------------------|------------------|---------------------------|-----------------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | nplemented bit, read as '0' |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown          |  |  |  |

### bit 31-0 NVMSRCADDR<31:0>: Source Data Address bits

The system physical address of the data to be programmed into the Flash when the NVMOP<3:0> bits (NVMCON<3:0>) are set to perform row programming.

| Interrupt Source <sup>(1)</sup>    | IRQ # | Vector |               | Interru      | upt Bit Location |              | Persistent |

|------------------------------------|-------|--------|---------------|--------------|------------------|--------------|------------|

| Interrupt Source."                 | IKQ # | #      | Flag          | Enable       | Priority         | Sub-priority | Interrupt  |

| CNB – PORTB Input Change Interrupt | 45    | 33     | IFS1<13>      | IEC1<13>     | IPC8<12:10>      | IPC8<9:8>    | Yes        |

| CNC – PORTC Input Change Interrupt | 46    | 33     | IFS1<14>      | IEC1<14>     | IPC8<12:10>      | IPC8<9:8>    | Yes        |

| CND – PORTD Input Change Interrupt | 47    | 33     | IFS1<15>      | IEC1<15>     | IPC8<12:10>      | IPC8<9:8>    | Yes        |

| CNE – PORTE Input Change Interrupt | 48    | 33     | IFS1<16>      | IEC1<16>     | IPC8<12:10>      | IPC8<9:8>    | Yes        |

| CNF – PORTF Input Change Interrupt | 49    | 33     | IFS1<17>      | IEC1<17>     | IPC8<12:10>      | IPC8<9:8>    | Yes        |

| CNG – PORTG Input Change Interrupt | 50    | 33     | IFS1<18>      | IEC1<18>     | IPC8<12:10>      | IPC8<9:8>    | Yes        |

| PMP – Parallel Master Port         | 51    | 34     | IFS1<19>      | IEC1<19>     | IPC8<20:18>      | IPC8<17:16>  | Yes        |

| PMPE – Parallel Master Port Error  | 52    | 34     | IFS1<20>      | IEC1<20>     | IPC8<20:18>      | IPC8<17:16>  | Yes        |

| SPI2E – SPI2 Fault                 | 53    | 35     | IFS1<21>      | IEC1<21>     | IPC8<28:26>      | IPC8<25:24>  | Yes        |

| SPI2RX – SPI2 Receive Done         | 54    | 35     | IFS1<22>      | IEC1<22>     | IPC8<28:26>      | IPC8<25:24>  | Yes        |

| SPI2TX – SPI2 Transfer Done        | 55    | 35     | IFS1<23>      | IEC1<23>     | IPC8<28:26>      | IPC8<25:24>  | Yes        |

| U2E – UART2 Error                  | 56    | 36     | IFS1<24>      | IEC1<24>     | IPC9<4:2>        | IPC9<1:0>    | Yes        |

| U2RX – UART2 Receiver              | 57    | 36     | IFS1<25>      | IEC1<25>     | IPC9<4:2>        | IPC9<1:0>    | Yes        |

| U2TX – UART2 Transmitter           | 58    | 36     | IFS1<26>      | IEC1<26>     | IPC9<4:2>        | IPC9<1:0>    | Yes        |

| I2C2B – I2C2 Bus Collision Event   | 59    | 37     | IFS1<27>      | IEC1<27>     | IPC9<12:10>      | IPC9<9:8>    | Yes        |

| I2C2S – I2C2 Slave Event           | 60    | 37     | IFS1<28>      | IEC1<28>     | IPC9<12:10>      | IPC9<9:8>    | Yes        |

| I2C2M – I2C2 Master Event          | 61    | 37     | IFS1<29>      | IEC1<29>     | IPC9<12:10>      | IPC9<9:8>    | Yes        |

| U3E – UART3 Error                  | 62    | 38     | IFS1<30>      | IEC1<30>     | IPC9<20:18>      | IPC9<17:16>  | Yes        |

| U3RX – UART3 Receiver              | 63    | 38     | IFS1<31>      | IEC1<31>     | IPC9<20:18>      | IPC9<17:16>  | Yes        |

| U3TX – UART3 Transmitter           | 64    | 38     | IFS2<0>       | IEC2<0>      | IPC9<20:18>      | IPC9<17:16>  | Yes        |

| U4E – UART4 Error                  | 65    | 39     | IFS2<1>       | IEC2<1>      | IPC9<28:26>      | IPC9<25:24>  | Yes        |

| U4RX – UART4 Receiver              | 66    | 39     | IFS2<2>       | IEC2<2>      | IPC9<28:26>      | IPC9<25:24>  | Yes        |

| U4TX – UART4 Transmitter           | 67    | 39     | IFS2<3>       | IEC2<3>      | IPC9<28:26>      | IPC9<25:24>  | Yes        |

| U5E – UART5 Error                  | 68    | 40     | IFS2<4>       | IEC2<4>      | IPC10<4:2>       | IPC10<1:0>   | Yes        |

| U5RX – UART5 Receiver              | 69    | 40     | IFS2<5>       | IEC2<5>      | IPC10<4:2>       | IPC10<1:0>   | Yes        |

| U5TX – UART5 Transmitter           | 70    | 40     | IFS2<6>       | IEC2<6>      | IPC10<4:2>       | IPC10<1:0>   | Yes        |

| CTMU – CTMU Event                  | 71    | 41     | IFS2<7>       | IEC2<7>      | IPC10<12:10>     | IPC10<9:8>   | Yes        |

| DMA0 – DMA Channel 0               | 72    | 42     | IFS2<8>       | IEC2<8>      | IPC10<20:18>     | IPC10<17:16> | No         |

| DMA1 – DMA Channel 1               | 73    | 43     | IFS2<9>       | IEC2<9>      | IPC10<28:26>     | IPC10<25:24> | No         |

| DMA2 – DMA Channel 2               | 74    | 44     | IFS2<10>      | IEC2<10>     | IPC11<4:2>       | IPC11<1:0>   | No         |

| DMA3 – DMA Channel 3               | 75    | 45     | IFS2<11>      | IEC2<11>     | IPC11<12:10>     | IPC11<9:8>   | No         |

|                                    |       | Lowe   | st Natural Or | der Priority |                  |              |            |

### TABLE 7-1: INTERRUPT IRQ, VECTOR AND BIT LOCATION (CONTINUED)

Note 1: Not all interrupt sources are available on all devices. See TABLE 1: "PIC32MX330/350/370/430/450/470 Controller Family Features" for the list of available peripherals.

# TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 3 REGISTER MAP

| ess                         |                                 | 0                                                                                                                                                                                    |             |       |       |       |        |       |      | Bi         | its     |        |        |        |         |        |        |        |            |

|-----------------------------|---------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------|-------|-------|--------|-------|------|------------|---------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range                                                                                                                                                                            | 31/15       | 30/14 | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8       | 23/7    | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH0CON                         | 31:16                                                                                                                                                                                | —           | _     |       | _     |        | _     | _    | _          | _       | _      | _      | _      | _       | _      | _      |        | 0000       |

| 3060                        | DCHUCON                         | JN         15:0         CHBUSY         —         —         —         —         —         CHCHNS         CHEN         CHAED         CHAEN         —         CHEDET         CHPRI<1:0> |             |       |       |       |        |       |      |            |         | 0000   |        |        |         |        |        |        |            |

| 3070                        | DCH0ECON                        | 31:16                                                                                                                                                                                |             |       |       |       |        |       |      |            |         |        |        | 00FF   |         |        |        |        |            |

| 0070                        | DOINCEOUN                       | 15:0                                                                                                                                                                                 |             |       |       | CHSIR | Q<7:0> |       |      |            | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      | —      | FFF8       |

| 3080                        | DCH0INT                         | 31:16                                                                                                                                                                                | —           | —     | —     | —     | -      | —     | —    | —          | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0000                        | Borioitti                       | 15:0                                                                                                                                                                                 | —           | —     | —     | —     | —      | —     | —    | —          | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3090                        | DCH0SSA                         | 31:16<br>15:0                                                                                                                                                                        | CHSSA<31:0> |       |       |       |        |       |      |            |         |        |        |        |         |        |        |        |            |

|                             |                                 | 31:16                                                                                                                                                                                | 6           |       |       |       |        |       |      |            |         |        |        |        |         |        |        |        |            |

| 30A0                        | DCH0DSA                         | 15:0                                                                                                                                                                                 |             |       |       |       |        |       |      | CHDSA      | A<31:0> |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16                                                                                                                                                                                | _           | _     | _     |       | _      | _     | _    | _          | _       | _      | _      | _      | _       | _      |        | _      | 0000       |

| 30B0                        | DCH0SSIZ                        | 15:0                                                                                                                                                                                 |             |       |       |       |        |       |      | CHSSIZ     | Z<15:0> |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16                                                                                                                                                                                | _           | _     | _     | _     | _      | _     | _    | _          | _       | _      | _      | _      | _       | _      | _      | _      | 0000       |

| 30C0                        | DCH0DSIZ                        | 15:0 CHDSIZ<15:0> 000                                                                                                                                                                |             |       |       |       |        |       |      |            |         | 0000   |        |        |         |        |        |        |            |

| 0000                        |                                 | 31:16                                                                                                                                                                                | —           | _     | —     | —     | —      | —     | —    | _          | —       |        | _      | —      | _       | _      | —      | _      | 0000       |

| 30D0                        | DCH0SPTR                        | 15:0                                                                                                                                                                                 |             |       |       |       |        |       |      | CHSPT      | R<15:0> |        |        |        |         | •      |        |        | 0000       |

| 2050                        |                                 | 31:16                                                                                                                                                                                | _           | _     | _     | —     | _      | _     | _    | _          | _       | _      | _      | _      | _       | _      | _      | _      | 0000       |

| 30E0                        | DCH0DPTR                        | 15:0                                                                                                                                                                                 |             |       |       |       |        |       |      | CHDPT      | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 2050                        | DCH0CSIZ                        | 31:16                                                                                                                                                                                | —           |       | _     | _     | _      | _     | _    | _          | _       | _      | _      | _      | _       | _      | _      | _      | 0000       |

| 30FU                        | DCHUCSIZ                        | 15:0                                                                                                                                                                                 |             |       |       |       |        |       |      | CHCSIZ     | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 3100                        | DCH0CPTR                        | 31:16                                                                                                                                                                                | —           | _     |       | _     |        | _     | _    | —          | _       | _      | _      | _      | _       | _      | _      |        | 0000       |

| 3100                        | DCHUCFTK                        | 15:0                                                                                                                                                                                 |             |       |       |       |        |       |      | CHCPT      | R<15:0> |        | -      |        |         |        |        |        | 0000       |

| 3110                        | DCH0DAT                         | 31:16                                                                                                                                                                                | —           | —     |       | —     | _      | —     | —    | —          |         | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 5110                        | DONUDAI                         | 15:0                                                                                                                                                                                 | —           | —     | _     | —     | _      |       | —    | —          |         |        |        | CHPDA  | AT<7:0> |        |        |        | 0000       |

| 3120                        | DCH1CON                         | 31:16                                                                                                                                                                                | —           | —     | _     | —     | —      |       | —    |            | —       | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 0120                        | Bonnoon                         | 15:0                                                                                                                                                                                 | CHBUSY      | —     | —     | —     | _      | —     | —    | CHCHNS     | CHEN    | CHAED  | CHCHN  | CHAEN  |         | CHEDET | CHPR   | l<1:0> | 0000       |

| 3130                        | DCH1ECON                        | 31:16                                                                                                                                                                                | —           | —     | —     | —     | —      | —     | —    | —          |         | 1      | -      |        | Q<7:0>  | -      |        |        | OOFF       |

| 0.00                        |                                 | 15:0                                                                                                                                                                                 |             |       |       | CHSIR | Q<7:0> |       |      |            | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      |        | —      | FFF8       |

| 3140                        | DCH1INT                         | 31:16                                                                                                                                                                                | -           | _     | _     | —     | _      | —     | _    | —          | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 55                          |                                 | 15:0 — — — — — — — — — — — CHSDIF CHSHIF CHDDIF CHDHF CHBCIF CHCCIF CHTAIF CHERIF 0000                                                                                               |             |       |       |       |        |       |      |            | 0000    |        |        |        |         |        |        |        |            |

| 3150                        | DCH1SSA                         | A 31:16 0000                                                                                                                                                                         |             |       |       |       |        |       |      |            |         |        |        |        |         |        |        |        |            |

|                             |                                 | 15:0                                                                                                                                                                                 | 0000        |       |       |       |        |       |      |            |         |        |        |        |         |        |        |        |            |

| 3160                        | DCH1DSA                         | 31:16 0000                                                                                                                                                                           |             |       |       |       |        |       |      |            |         |        |        |        |         |        |        |        |            |

|                             |                                 | 15:0                                                                                                                                                                                 |             |       |       |       |        |       |      | exadecimal |         |        |        |        |         |        |        |        | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

| INE OIDTE    | SISTER 10-6. DEFRECON. DMA CHANNEL & EVENT CONTROL REGISTER |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

|--------------|-------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                           | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 31:24        | U-0                                                         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        |                                                             | —                 | _                 | —                 | —                 |                   | —                | —                |  |  |  |  |

| 22:16        | R/W-1                                                       | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup>                                  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 15.0         | R/W-1                                                       | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |  |  |  |

| 15:8         | CHSIRQ<7:0> <sup>(1)</sup>                                  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | S-0                                                         | S-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |  |  |  |

| 7.0          | CFORCE                                                      | CABORT            | PATEN             | SIRQEN            | AIRQEN            |                   |                  |                  |  |  |  |  |

#### REGISTER 10-8 DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

# bit 31-24 Unimplemented: Read as '0'

| bit 31-24 | Unimplemented: Read as '0'                                                                                 |

|-----------|------------------------------------------------------------------------------------------------------------|

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                |

|           | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                           |

|           | •                                                                                                          |

|           | •                                                                                                          |

|           | •                                                                                                          |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag                             |

|           | 00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag                             |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                      |

|           | •                                                                                                          |

|           | •                                                                                                          |

|           |                                                                                                            |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer<br>00000000 = Interrupt 0 will initiate a DMA transfer |

| h:4 7     |                                                                                                            |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                            |

|           | 1 = A DMA transfer is forced to begin when this bit is written to a '1'                                    |

|           | 0 = This bit always reads '0'                                                                              |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                             |

|           | 1 = A DMA transfer is aborted when this bit is written to a '1'                                            |

|           | 0 = This bit always reads '0'                                                                              |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                              |

|           | 1 = Abort transfer and clear CHEN on pattern match                                                         |

|           | 0 = Pattern match is disabled                                                                              |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                       |

|           | 1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs                                     |

- Start channel cell transfer if an interrupt matching CHSIRQ occurs 0 = Interrupt number CHSIRQ is ignored and does not start a transfer

- bit 3 AIRQEN: Channel Abort IRQ Enable bit

- 1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

- 0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

- bit 2-0 Unimplemented: Read as '0'

- Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                              | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------|------------------|

| 21.24        | U-0                                           | U-0              |

| 31:24        |                   | —                 | —                 | —                 |                   | —                 | —                                             | —                |

| 23:16        | U-0                                           | U-0              |

| 23.10        |                   |                   | _                 | _                 | _                 | _                 | _                                             | —                |

| 15:8         | U-0                                           | U-0              |

| 10.0         | _                 | _                 | _                 | _                 |                   | _                 | _                                             | —                |

|              | R/W-0                                         | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup><br>EOFEE <sup>(2)</sup> | PIDEE            |

### REGISTER 11-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

| bit 7 | <b>BTSEE:</b> Bit Stuff Error Interrupt Enable bit |

|-------|----------------------------------------------------|

|       |                                                    |

- 1 = BTSEF interrupt is enabled

- 0 = BTSEF interrupt is disabled

- bit 6 BMXEE: Bus Matrix Error Interrupt Enable bit

- 1 = BMXEF interrupt is enabled

- 0 = BMXEF interrupt is disabled

- bit 5 **DMAEE:** DMA Error Interrupt Enable bit

- 1 = DMAEF interrupt is enabled

- 0 = DMAEF interrupt is disabled

- bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

- 1 = BTOEF interrupt is enabled

- 0 = BTOEF interrupt is disabled

- bit 3 **DFN8EE:** Data Field Size Error Interrupt Enable bit

- 1 = DFN8EF interrupt is enabled

- 0 = DFN8EF interrupt is disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

### Note 1: Device mode.

2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

# TABLE 12-2: OUTPUT PIN SELECTION (CONTINUED)

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection        |

|----------------------|----------|-------------|----------------------------------------------|

| RPD9                 | RPD9R    | RPD9R<3:0>  | 0000 = No Connect                            |

| RPG6                 | RPG6R    | RPG6R<3:0>  | 0001 = U3RTS                                 |

| RPB8                 | RPB8R    | RPB8R<3:0>  | 0010 = U4TX                                  |

| RPB15                | RPB15R   | RPB15R<3:0> | 0011 = REFCLKO<br>0100 = U5TX <sup>(4)</sup> |

| RPD4                 | RPD4R    | RPD4R<3:0>  | 0100 = 001 x 0                               |

| RPB0                 | RPB0R    | RPB0R<3:0>  | 0110 = Reserved                              |

| RPE3                 | RPE3R    | RPE3R<3:0>  | 0111 = <u>SS1</u>                            |

| RPB7                 | RPB7R    | RPB7R<3:0>  | 1000 <b>= SDO1</b>                           |

| RPB2                 | RPB2R    | RPB2R<3:0>  | 1001 = Reserved                              |

| RPF12 <sup>(4)</sup> | RPF12R   | RPF12R<3:0> | 1010 = Reserved                              |

| RPD12 <sup>(4)</sup> | RPD12R   | RPD12R<3:0> |                                              |

| RPF8 <sup>(4)</sup>  | RPF8R    | RPF8R<3:0>  | 1100 - Reserved                              |

| RPC3 <sup>(4)</sup>  | RPC3R    | RPC3R<3:0>  | 1110 = Reserved                              |

| RPE9 <sup>(4)</sup>  | RPE9R    | RPE9R<3:0>  | 1111 = Reserved                              |

| RPD1                 | RPD1R    | RPD1R<3:0>  | 0000 = No Connect                            |

| RPG9                 | RPG9R    | RPG9R<3:0>  | 0001 = U2RTS                                 |

| RPB14                | RPB14R   | RPB14R<3:0> | 0010 = Reserved<br>0011 = U1RTS              |

| RPD0                 | RPD0R    | RPD0R<3:0>  | $0100 = U5TX^{(4)}$                          |

| RPD8                 | RPD8R    | RPD8R<3:0>  | 0101 = Reserved                              |

| RPB6                 | RPB6R    | RPB6R<3:0>  | 0110 = <u>SS2</u>                            |

| RPD5                 | RPD5R    | RPD5R<3:0>  | 0111 = Reserved<br>1000 = SDO1               |

| RPF3 <sup>(3)</sup>  | RPF3R    | RPF3R<3:0>  | 1000 = SDOT                                  |

| RPF6 <sup>(1)</sup>  | RPF6R    | RPF6R<3:0>  | 1010 = Reserved                              |

| RPF13 <sup>(4)</sup> | RPF13R   | RPF13R<3:0> | 1011 = OC2                                   |

| RPC2 <sup>(4)</sup>  | RPC2R    | RPC2R<3:0>  | 1100 = OC1<br>1101 = Reserved                |

| RPE8 <sup>(4)</sup>  | RPE8R    | RPE8R<3:0>  | 1110 = Reserved                              |

| RPF2 <sup>(5)</sup>  | RPF2R    | RPF2R<3:0>  | 1111 = Reserved                              |

**Note 1:** This selection is only available on General Purpose devices.

**2:** This selection is only available on 64-pin General Purpose devices.

3: This selection is only available on 100-pin General Purpose devices.

4: This selection is only available on 100-pin USB and General Purpose devices.

5: This selection is not available on 64-pin USB devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | -                 | _                 | _                 | _                 | _                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | -                 | _                 | _                 | -                 | _                 | _                 | _                | —                |

| 15.0         | R/W-0             | U-0               | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON                | _                 | SIDL              | _                 | _                 |                   | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 7:0          | _                 |                   | _                 | _                 | _                 | _                 | _                |                  |

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

|-------------------|------------------|----------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Change Notice (CN) Control ON bit

- 1 = CN is enabled

- 0 = CN is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Control bit

- 1 = CPU Idle Mode halts CN operation

- 0 = CPU Idle does not affect CN operation

- bit 12-0 Unimplemented: Read as '0'

# PIC32MX330/350/370/430/450/470

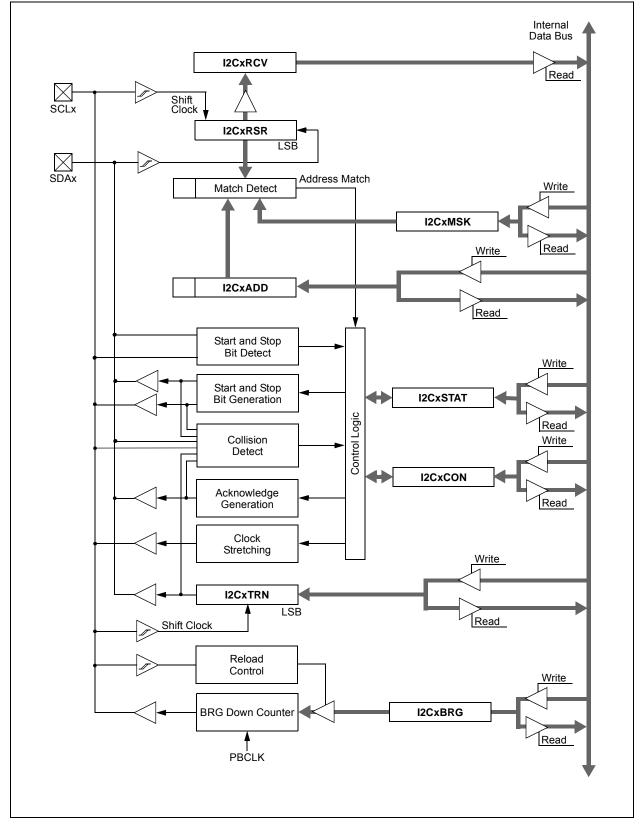

# FIGURE 19-1: I<sup>2</sup>C BLOCK DIAGRAM

# REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | -                 | -                 | —                 | _                 | -                | _                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        |                   | —                 | _                 | _                 | _                 |                   | _                | -                |  |  |

| 45.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |  |  |

| 15:8         | ACKSTAT           | TRSTAT            | -                 | _                 | _                 | BCL               | GCSTAT           | ADD10            |  |  |

| 7:0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |  |  |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |  |  |

| Legend:           | HS = Set in hardware | HSC = Hardware set/cleared |                   |  |

|-------------------|----------------------|----------------------------|-------------------|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re  | ead as '0'        |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared       | C = Clearable bit |  |

### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit

(when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Acknowledge was not received from slave

- 0 = Acknowledge was received from slave

Hardware set or clear at end of slave Acknowledge.

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

1 = A bus collision has been detected during a master operation

0 = No collision

Hardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module.

- bit 9 **GCSTAT:** General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware set when address matches general call address. Hardware clear at Stop detection.

bit 8 ADD10: 10-bit Address Status bit

1 = 10-bit address was matched

0 = 10-bit address was not matched

Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

- bit 7 IWCOL: Write Collision Detect bit

- 1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy

- 0 = No collision

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

bit 6 I2COV: Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 31:24        | U-0               | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

|              | _                 | _                    | _                 | _                 | _                 | _                 | _                | _                    |

| 00.40        | U-0               | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | _                 | _                    | _                 | _                 | _                 | _                 | —                | —                    |

| 45.0         | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                |

| 15:8         | PTEN<1            | 5:14> <sup>(1)</sup> | (1) PTEN<13:8>    |                   |                   |                   |                  |                      |

| 7:0          | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                |

|              |                   |                      | PTEN              | <7:2>             |                   |                   | PTEN<            | <1:0> <sup>(2)</sup> |

### REGISTER 21-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

# Legend:

| Legenu.           |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-16 Unimplemented: Write '0'; ignore read

- bit 15-14 **PTEN<15:14>:** PMCSx Address Port Enable bits

- 1 = PMA15 and PMA14 function as either PMA<15:14> or PMCS2 and PMCS1<sup>(1)</sup>

- 0 = PMA15 and PMA14 function as port I/O

- bit 13-2 **PTEN<13:2>:** PMP Address Port Enable bits 1 = PMA<13:2> function as PMP address lines

- 0 = PMA<13:2> function as port I/O

- bit 1-0 **PTEN<1:0>:** PMALH/PMALL Address Port Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- Note 1: The use of these pins as PMA15/PMA14 or CS2/CS1 is selected by the CSF<1:0> bits (PMCON<7:6>).

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by the ADRMUX<1:0> bits in the PMCON register.

# 27.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid. To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). See Table 27-1 for more information.

Note: Disabling a peripheral module while it's ON bit is set, may result in undefined behavior. The ON bit for the associated peripheral module must be cleared prior to disable a module via the PMDx bits.

| TABLE 27-1: | PERIPHERAL MODULE DISABLE BITS AND LOCATIONS |

|-------------|----------------------------------------------|

|             |                                              |

| Peripheral <sup>(1)</sup>    | PMDx bit Name <sup>(1)</sup> | Register Name and Bit Location |

|------------------------------|------------------------------|--------------------------------|

| ADC1                         | AD1MD                        | PMD1<0>                        |

| СТМИ                         | CTMUMD                       | PMD1<8>                        |

| Comparator Voltage Reference | CVRMD                        | PMD1<12>                       |

| Comparator 1                 | CMP1MD                       | PMD2<0>                        |

| Comparator 2                 | CMP2MD                       | PMD2<1>                        |

| Input Capture 1              | IC1MD                        | PMD3<0>                        |

| Input Capture 2              | IC2MD                        | PMD3<1>                        |

| Input Capture 3              | IC3MD                        | PMD3<2>                        |

| Input Capture 4              | IC4MD                        | PMD3<3>                        |

| Input Capture 5              | IC5MD                        | PMD3<4>                        |

| Output Compare 1             | OC1MD                        | PMD3<16>                       |

| Output Compare 2             | OC2MD                        | PMD3<17>                       |

| Output Compare 3             | OC3MD                        | PMD3<18>                       |

| Output Compare 4             | OC4MD                        | PMD3<19>                       |

| Output Compare 5             | OC5MD                        | PMD3<20>                       |

| Timer1                       | T1MD                         | PMD4<0>                        |

| Timer2                       | T2MD                         | PMD4<1>                        |

| Timer3                       | T3MD                         | PMD4<2>                        |

| Timer4                       | T4MD                         | PMD4<3>                        |

| Timer5                       | T5MD                         | PMD4<4>                        |

| UART1                        | U1MD                         | PMD5<0>                        |

| UART2                        | U2MD                         | PMD5<1>                        |

| UART3                        | U3MD                         | PMD5<2>                        |

| UART4                        | U4MD                         | PMD5<3>                        |

| UART5                        | U5MD                         | PMD5<4>                        |

| SPI1                         | SPI1MD                       | PMD5<8>                        |

| SPI2                         | SPI2MD                       | PMD5<9>                        |

| I2C1                         | I2C1MD                       | PMD5<16>                       |

| 2C2                          | I2C2MD                       | PMD5<17>                       |

| USB <sup>(2)</sup>           | USBMD                        | PMD5<24>                       |

| RTCC                         | RTCCMD                       | PMD6<0>                        |

| Reference Clock Output       | REFOMD                       | PMD6<1>                        |

| PMP                          | PMPMD                        | PMD6<16>                       |

Note 1: Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MX330/350/ 370/430/450/470 Controller Family Features" for the lists of available peripherals.

2: Module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

# 30.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 30.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

# 31.0 ELECTRICAL CHARACTERISTICS

This section provides an overview of the PIC32MX330/350/370/430/450/470 electrical characteristics. Additional information will be provided in future revisions of this document as it becomes available.

Absolute maximum ratings for the PIC32MX330/350/370/430/450/470 devices are listed below. Exposure to these maximum rating conditions for extended periods may affect device reliability. Functional operation of the device at these or any other conditions, above the parameters indicated in the operation listings of this specification, is not implied.

# **Absolute Maximum Ratings**

### (See Note 1)

| Ambient temperature under bias                                                  | 40°C to +105°C           |

|---------------------------------------------------------------------------------|--------------------------|

| Storage temperature                                                             |                          |

| Voltage on VDD with respect to Vss                                              |                          |

| Voltage on any pin that is not 5V tolerant, with respect to Vss (Note 3)        | 0.3V to (VDD + 0.3V)     |

| Voltage on any 5V tolerant pin with respect to Vss when $VDD \ge 2.3V$ (Note 3) | -0.3V to +6.0V           |

| Voltage on any 5V tolerant pin with respect to Vss when VDD < 2.3V (Note 3)     | 0.3V to +3.6V            |

| Voltage on D+ or D- pin with respect to VUSB3V3                                 | 0.3V to (VUSB3V3 + 0.3V) |

| Voltage on VBUS with respect to VSS                                             | -0.3V to +5.5V           |

| Maximum current out of Vss pin(s)                                               | 200 mA                   |

| Maximum current into VDD pin(s) (Note 2)                                        | 200 mA                   |

| Maximum output current sourced/sunk by any 4x I/O pin                           | 15 mA                    |

| Maximum output current sourced/sunk by any 8x I/O pin                           | 25 mA                    |

| Maximum current sunk by all ports                                               | 150 mA                   |

| Maximum current sourced by all ports (Note 2)                                   | 150 mA                   |

**Note 1:** Stresses above those listed under "**Absolute Maximum Ratings**" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions, above those indicated in the operation listings of this specification, is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

- 2: Maximum allowable current is a function of device maximum power dissipation (see Table 31-2).

- 3: See the "Device Pin Tables" section for the 5V tolerant pins.

### TABLE 31-18: EXTERNAL CLOCK TIMING REQUIREMENTS