Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Becano                     |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

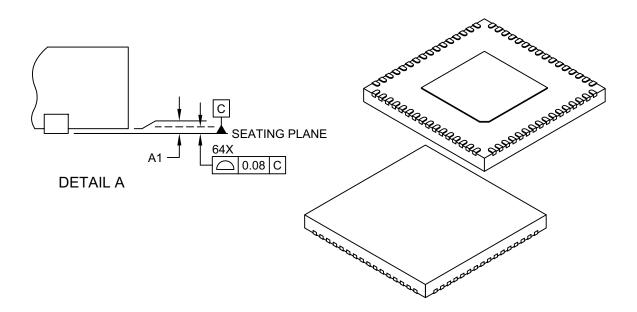

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256h-i-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Device Pin Tables**

| 64-      | -PIN QFN <sup>(1,2,3,4)</sup> AND TQFP <sup>(1,2,3,4)</sup> (TOP VII | EW)              |                       |

|----------|----------------------------------------------------------------------|------------------|-----------------------|

| Pl<br>Pl | C32MX330F064H<br>C32MX350F128H<br>C32MX350F256H<br>C32MX370F512H     |                  |                       |

|          | 64                                                                   | 1                | 64                    |

|          | QF                                                                   | N <sup>(4)</sup> | TQFP                  |

| Pin #    | Full Pin Name                                                        | Pin #            | Full Pin Name         |

| 1        | AN22/RPE5/PMD5/RE5                                                   | 33               | RPF3/RF3              |

| 2        | AN23/PMD6/RE6                                                        | 34               | RPF2/RF2              |

| 3        | AN27/PMD7/RE7                                                        | 35               | RPF6/SCK1/INT0/RF6    |

| 4        | AN16/C1IND/RPG6/SCK2/PMA5/RG6                                        | 36               | SDA1/RG3              |

| 5        | AN17/C1INC/RPG7/PMA4/RG7                                             | 37               | SCL1/RG2              |

| 6        | AN18/C2IND/RPG8/PMA3/RG8                                             | 38               | VDD                   |

| 7        | MCLR                                                                 | 39               | OSC1/CLKI/RC12        |

| 8        | AN19/C2INC/RPG9/PMA2/RG9                                             | 40               | OSC2/CLKO/RC15        |

| 9        | Vss                                                                  | 41               | Vss                   |

| 10       | Vdd                                                                  | 42               | RPD8/RTCC/RD8         |

| 11       | AN5/C1INA/RPB5/RB5                                                   | 43               | RPD9/RD9              |

| 12       | AN4/C1INB/RB4                                                        | 44               | RPD10/PMCS2/RD10      |

| 13       | PGED3/AN3/C2INA/RPB3/RB3                                             | 45               | RPD11/PMCS1/RD11      |

| 14       | PGEC3/AN2/C2INB/RPB2/CTED13/RB2                                      | 46               | RPD0/RD0              |

| 15       | PGEC1/VREF-/CVREF-/AN1/RPB1/CTED12/RB1                               | 47               | SOSCI/RPC13/RC13      |

| 16       | PGED1/VREF+/CVREF+/AN0/RPB0/PMA6/RB0                                 | 48               | SOSCO/RPC14/T1CK/RC14 |

| 17       | PGEC2/AN6/RPB6/RB6                                                   | 49               | AN24/RPD1/RD1         |

| 18       | PGED2/AN7/RPB7/CTED3//RB7                                            | 50               | AN25/RPD2/RD2         |

| 19       | AVDD                                                                 | 51               | AN26/RPD3/RD3         |

| 20       | AVss                                                                 | 52               | RPD4/PMWR/RD4         |

| 21       | AN8/RPB8/CTED10//RB8                                                 | 53               | RPD5/PMRD/RD5         |

| 22       | AN9/RPB9/CTED4/PMA7/RB9                                              | 54               | RD6                   |

| 23       | TMS/Cvrefout/AN10/RPB10/CTED11//PMA13/RB10                           | 55               | RD7                   |

| 24       | TDO/AN11/PMA12/RB11                                                  | 56               | VCAP                  |

| 25       | Vss                                                                  | 57               | VDD                   |

| 26       | Vdd                                                                  | 58               | RPF0/RF0              |

| 27       | TCK/AN12/PMA11/RB12                                                  | 59               | RPF1/RF1              |

| 28       | TDI/AN13/PMA10/RB13                                                  | 60               | PMD0/RE0              |

| 29       | AN14/RPB14/CTED5/PMA1/RB14                                           | 61               | PMD1/RE1              |

| 30       | AN15/RPB15/OCFB/CTED6/PMA0/RB15                                      | 62               | AN20/PMD2/RE2         |

| 31       | RPF4/SDA2/PMA9/RF4                                                   | 63               | RPE3/CTPLS/PMD3/RE3   |

| 32       | RPF5/SCL2/PMA8/RF5                                                   | 64               | AN21/PMD4/RE4         |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

Every I/O port pin (RBx-RGx), with the exception of RF6, can be used as a change notification pin (CNBx-CNGx). See Section 12.0 "I/O 2: Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

RPF6 (pin 35) is only available for output functions. 4:

|                                                                                                           |                        | Pin Numb                 | er                                                  |             |                |                                                                                 |

|-----------------------------------------------------------------------------------------------------------|------------------------|--------------------------|-----------------------------------------------------|-------------|----------------|---------------------------------------------------------------------------------|

| CTED5<br>CTED6<br>CTED7<br>CTED8<br>CTED9<br>CTED10<br>CTED11<br>CTED12<br>CTED13<br>MCLR<br>AVDD<br>AVSS | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP          | 124-pin<br>VTLA                                     | Pin<br>Type | Buffer<br>Type | Description                                                                     |

| CTED4                                                                                                     | 22                     | 33                       | B19                                                 | 1           | ST             | CTMU External Edge Input 4                                                      |

| CTED5                                                                                                     | 29                     | 43                       | B24                                                 | I           | ST             | CTMU External Edge Input 5                                                      |

| CTED6                                                                                                     | 30                     | 44                       | A29                                                 | I           | ST             | CTMU External Edge Input 6                                                      |

| CTED7                                                                                                     | —                      | 9                        | B5                                                  | I           | ST             | CTMU External Edge Input 7                                                      |

| CTED8                                                                                                     | —                      | 92                       | A62                                                 | I           | ST             | CTMU External Edge Input 8                                                      |

| CTED9                                                                                                     | —                      | 60                       | A40                                                 | Ι           | ST             | CTMU External Edge Input 9                                                      |

| CTED10                                                                                                    | 21                     | 32                       | A23                                                 | Ι           | ST             | CTMU External Edge Input 10                                                     |

| CTED11                                                                                                    | 23                     | 34                       | A24                                                 | Ι           | ST             | CTMU External Edge Input 11                                                     |

| CTED12                                                                                                    | 15                     | 24                       | A15                                                 | I           | ST             | CTMU External Edge Input 12                                                     |

| CTED13                                                                                                    | 14                     | 23                       | B13                                                 | I           | ST             | CTMU External Edge Input 13                                                     |

| MCLR                                                                                                      | 7                      | 13                       | B7                                                  | I/P         | ST             | Master Clear (Reset) input. This pin is an active-low Reset to the device.      |

| AVdd                                                                                                      | 19                     | 30                       | A22                                                 | Р           | Р              | Positive supply for analog modules. This pin must be<br>connected at all times. |

| AVss                                                                                                      | 20                     | 31                       | B18                                                 | Р           | Р              | Ground reference for analog modules                                             |

| Vdd                                                                                                       | 10, 26, 38,<br>57      | 2, 16, 37,<br>46, 62, 86 | B1, A10, A14,<br>B21, A30,<br>A41, A48,<br>A59, B53 | Ρ           | _              | Positive supply for peripheral logic and I/O pins                               |

| Vcap                                                                                                      | 56                     | 85                       | B48                                                 | Р           | —              | Capacitor for Internal Voltage Regulator                                        |

| Vss                                                                                                       | 9, 25, 41              | 15, 36, 45,<br>65, 75    | A3, B8, B12,<br>A25, B25,<br>A43, B41,<br>A63       | Ρ           | _              | Ground reference for logic and I/O pins                                         |

| VREF+                                                                                                     | 16                     | 29                       | B17                                                 | I           | Analog         | Analog Voltage Reference (High) Input                                           |

| Vref-                                                                                                     | 15                     | 28                       | A21                                                 | Ι           | Analog         | Analog Voltage Reference (Low) Input                                            |

#### TARI E 1-1. PINOLIT I/O DESCRIPTIONS (CONTINUED)

Legend: CMOS = CMOS compatible input or output ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

Analog = Analog input O = Output

I = Input

Note 1: This pin is only available on devices without a USB module.

This pin is only available on devices with a USB module. 2:

3: This pin is not available on 64-pin devices.

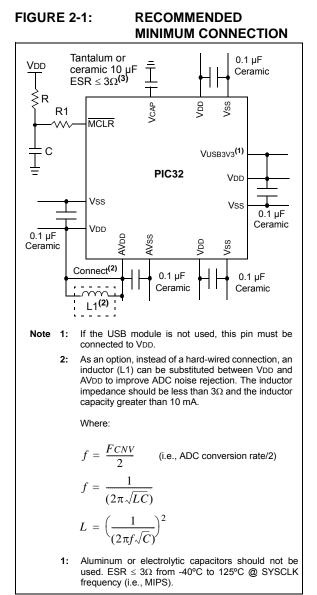

### 2.2.1 BULK CAPACITORS

The use of a bulk capacitor is recommended to improve power supply stability. Typical values range from 4.7  $\mu F$  to 47  $\mu F$ . This capacitor should be located as close to the device as possible.

## 2.3 Capacitor on Internal Voltage Regulator (VCAP)

#### 2.3.1 INTERNAL REGULATOR MODE

A low-ESR (3 ohm) capacitor is required on the VCAP pin, which is used to stabilize the internal voltage regulator output. The VCAP pin must not be connected to VDD, and must have a CEFC capacitor, with at least a 6V rating, connected to ground. The type can be ceramic or tantalum. Refer to **Section 31.0 "Electrical Characteristics"** for additional information on CEFC specifications.

## 2.4 Master Clear (MCLR) Pin

The  $\overline{\text{MCLR}}$  pin provides two specific device functions:

- Device Reset

- · Device programming and debugging

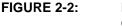

Pulling The  $\overline{\text{MCLR}}$  pin low generates a device Reset. Figure 2-2 illustrates a typical  $\overline{\text{MCLR}}$  circuit. During device programming and debugging, the resistance and capacitance that can be added to the pin must be considered. Device programmers and debuggers drive the  $\overline{\text{MCLR}}$  pin. Consequently, specific voltage levels (VIH and VIL) and fast signal transitions must not be adversely affected. Therefore, specific values of R and C will need to be adjusted based on the application and PCB requirements.

For example, as illustrated in Figure 2-2, it is recommended that the capacitor C, be isolated from the MCLR pin during programming and debugging operations.

Place the components illustrated in Figure 2-2 within one-quarter inch (6 mm) from the MCLR pin.

3:

### EXAMPLE OF MCLR PIN CONNECTIONS

No pull-ups or bypass capacitors are allowed on

active debug/program PGECx/PGEDx pins.

## 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32 USB module includes the following features:

- USB full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, and other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

| Bit<br>Range                              | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24                                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24 -<br>23:16 -                        |                   | _                 |                   |                   |                   | —                 |                  | —                |

| 22:16                                     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10                                     | -                 | _                 |                   |                   | -                 | —                 |                  | —                |

| 15.0                                      | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0                                      | -                 | _                 |                   |                   | -                 | —                 |                  | —                |

| 7:0                                       | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0              | R/W-0            |

| Range         3           31:24         - | IDIE              | T1MSECIE          | LSTATEIE          | ACTVIE            | SESVDIE           | SESENDIE          |                  | VBUSVDIE         |

### REGISTER 11-2: U10TGIE: USB OTG INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 **IDIE:** ID Interrupt Enable bit

- 1 = ID interrupt is enabled

- 0 = ID interrupt is disabled

- bit 6 T1MSECIE: 1 Millisecond Timer Interrupt Enable bit

- 1 = 1 millisecond timer interrupt is enabled

- 0 = 1 millisecond timer interrupt is disabled

- bit 5 LSTATEIE: Line State Interrupt Enable bit

- 1 = Line state interrupt is enabled

- 0 = Line state interrupt is disabled

- bit 4 ACTVIE: Bus Activity Interrupt Enable bit

- 1 = ACTIVITY interrupt is enabled

- 0 = ACTIVITY interrupt is disabled

- bit 3 SESVDIE: Session Valid Interrupt Enable bit

- 1 = Session valid interrupt is enabled

- 0 = Session valid interrupt is disabled

- bit 2 SESENDIE: B-Session End Interrupt Enable bit

- 1 = B-session end interrupt is enabled

- 0 = B-session end interrupt is disabled

- bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVDIE: A-VBUS Valid Interrupt Enable bit

- 1 = A-VBUS valid interrupt is enabled

- 0 = A-VBUS valid interrupt is disabled

| Bit<br>Range                                                                                                         | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|----------------------------------------------------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24                                                                                                                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24<br>23:16                                                                                                       |                   |                   |                   |                   |                   | —                 | _                | _                |

| 23:16                                                                                                                | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|                                                                                                                      |                   |                   |                   |                   |                   | —                 | _                | _                |

| 15.0                                                                                                                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0                                                                                                                 | -                 | -                 | —                 | —                 | -                 | —                 | —                | _                |

| 7:0                                                                                                                  | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| Range         3           31:24         -           23:16         -           15:8         -           7:0         - | DPPULUP           | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG          | VBUSDIS          |

#### REGISTER 11-4: U10TGCON: USB OTG CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | DPPULUP: D+ Pull-Up Enable bit |

|-------|--------------------------------|

|       |                                |

- 1 = D+ data line pull-up resistor is enabled

- 0 = D+ data line pull-up resistor is disabled

#### bit 6 **DMPULUP:** D- Pull-Up Enable bit

- 1 = D- data line pull-up resistor is enabled

- 0 = D- data line pull-up resistor is disabled

### bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

- 1 = D+ data line pull-down resistor is enabled

- 0 = D+ data line pull-down resistor is disabled

#### bit 4 DMPULDWN: D- Pull-Down Enable bit

- 1 = D- data line pull-down resistor is enabled

- 0 = D- data line pull-down resistor is disabled

- bit 3 **VBUSON:** VBUS Power-on bit

- 1 = VBUS line is powered

- 0 = VBUS line is not powered

- bit 2 OTGEN: OTG Functionality Enable bit

- 1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

- 0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

#### bit 1 VBUSCHG: VBUS Charge Enable bit

- 1 = VBUS line is charged through a pull-up resistor

- 0 = VBUS line is not charged through a resistor

#### bit 0 VBUSDIS: VBUS Discharge Enable bit

- 1 = VBUS line is discharged through a pull-down resistor

- 0 = VBUS line is not discharged through a resistor

## 12.1 Parallel I/O (PIO) Ports

All port pins have ten registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

### 12.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the presence of outputs higher than VDD (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Device Pin Tables"** section for the available pins and their functionality.

# 12.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

## 12.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be an NOP.

## 12.1.4 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports allows the PIC32MX330/350/370/430/450/470 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

Each I/O pin also has a weak pull-up and every I/O pin has a weak pull-down connected to it. The pullups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on change notifi-<br>cation pins should always be disabled<br>when the port pin is configured as a digital |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | output. They should also be disabled on                                                                                            |

|       | 5V tolerant pins when the pin voltage can                                                                                          |

|       | exceed VDD.                                                                                                                        |

An additional control register (CNCONx) is shown in Register 12-3.

## 12.2 CLR, SET, and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

# TABLE 12-6: PORTC REGISTER MAP FOR PIC32MX330F064H, PIC32MX350F128H, PIC32MX350F256H, PIC32MX370F512H, PIC32MX430F064H, PIC32MX450F128H, PIC32MX450F256H, AND PIC32MX470F512H DEVICES ONLY

| ess                         |                                 |           |           |           |           |           |       |       |      | Bits |      |      |      |      |      |      |      |      |               |

|-----------------------------|---------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|------|------|------|------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All<br>Resets |

| 6210                        | TRISC                           | 31:16     | _         | _         |           | —         |       | —     | —    | —    | —    | -    | —    | —    |      |      | —    | —    | 0000          |

| 0210                        | TRIBC                           | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | _     | —     | _    | —    | _    | _    | _    | _    | _    | —    | —    | _    | xxxx          |

| 6220                        | PORTC                           | 31:16     | _         | _         |           | _         | _     | —     | _    | —    | _    | _    | —    | —    | —    | —    |      | —    | 0000          |

| 0220                        | TOINIC                          | 15:0      | RC15      | RC14      | RC13      | RC12      | _     | —     | _    | —    | —    | _    | —    | —    | —    | —    |      | —    | xxxx          |

| 6230                        | LATC                            | 31:16     | _         |           |           | _         | _     | —     | —    | —    | —    |      |      |      | —    | —    |      | —    | 0000          |

| 0200                        | 2/10                            | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | —     | —     | —    | —    | —    | _    |      |      | —    | —    | —    | —    | xxxx          |

| 6240                        | ODCC                            | 31:16     | _         | —         |           | —         | _     | —     | —    | —    | —    | —    | —    | —    | —    | —    | —    | —    | 0000          |

| 02.0                        |                                 | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    | -     | —     | —    | —    | —    | —    | —    | —    | —    | —    | —    | —    | xxxx          |

| 6250                        | CNPUC                           | 31:16     | —         | —         | —         | —         | -     | —     | —    | —    | —    | —    | —    | —    | —    | —    | —    | —    | 0000          |

| 0200                        |                                 | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | -     | —     | —    | —    | —    | —    | —    | —    | —    | —    | —    | —    | xxxx          |

| 6260                        | CNPDC                           | 31:16     | —         | —         | —         | —         | -     | —     | —    | —    | —    | —    | —    | —    | —    | —    | —    | —    | 0000          |

| 0200                        |                                 | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | —     | —     | _    | —    | —    | —    | _    | _    | _    | —    | -    | —    | xxxx          |

| 6270                        | CNCONC                          | 31:16     | —         | —         | —         | —         | -     | —     | —    | —    | —    | —    | —    | —    | —    | —    | —    | —    | 0000          |

| 02.0                        |                                 | 15:0      | ON        | —         | SIDL      | —         | -     | —     | —    | —    | —    | —    | —    | —    | —    | —    | —    | —    | 0000          |

| 6280                        | CNENC                           | 31:16     | _         | —         |           | —         | _     | —     | _    | —    | _    | _    | _    | _    | _    | —    |      | _    | 0000          |

|                             |                                 | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | —     | —     | _    | —    | —    | —    | _    | _    | _    | —    | -    | —    | xxxx          |

| 6290                        | CNSTATC                         | 31:16     | _         | —         |           | —         | _     | —     | —    | —    | —    | —    | —    | —    | —    | —    | —    | —    | 0000          |

| 0200                        | 0.10 // 10                      | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 | —     | —     | —    | —    | —    | —    |      |      |      | —    | —    |      | xxxx          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

## TABLE 12-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| 2012-2016  |  |

|------------|--|

| Microchip  |  |

| Technology |  |

| Inc        |  |

0

| SS                          |                       |               |       |               |       |       |       |       |      | Bi   | ts   |      |      |      |      |          |           |      |            |

|-----------------------------|-----------------------|---------------|-------|---------------|-------|-------|-------|-------|------|------|------|------|------|------|------|----------|-----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14         | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2     | 17/1      | 16/0 | All Resets |

| FC14                        | RPE5R                 | 31:16         |       | —             | —     | —     | —     | _     | —    |      | _    | _    | —    |      | _    | _        | —         | _    | 0000       |

|                             |                       | 15:0          | —     | —             | —     | —     | —     | _     | —    | —    | —    | _    | —    | _    |      | RPE5     | <3:0>     |      | 0000       |

| FC20                        | RPE8R <sup>(1)</sup>  | 31:16         | _     | —             | _     |       |       | _     | —    |      | _    |      |      | _    | _    | -        | -         | —    | 0000       |

|                             |                       | 15:0<br>31:16 |       |               |       |       |       |       |      |      |      |      |      |      |      | RPE8     | <3:0>     | _    | 0000       |

| FC24                        | RPE9R <sup>(1)</sup>  | 15:0          | _     | _             | _     |       | _     |       |      |      |      | _    | _    | _    | _    |          | 9<3:0>    | _    | 0000       |

|                             |                       | 31:16         |       | _             | _     |       | _     | _     | _    |      |      | _    | _    | _    | _    |          | _         | _    | 0000       |

| FC40                        | RPF0R                 | 15:0          | _     | _             | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF0     | <3:0>     |      | 0000       |

|                             |                       | 31:16         | _     | _             | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _        | _         | _    | 0000       |

| FC44                        | RPF1R                 | 15:0          | _     | _             | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF1     | <3:0>     |      | 0000       |

| FC48                        | RPF2R <sup>(3)</sup>  | 31:16         | —     | —             | —     | —     | _     | _     | —    | _    |      | _    | —    | —    |      | —        | _         | _    | 0000       |

| FC40                        | RPF2R**               | 15:0          | _     | _             | _     | -     | -     | -     | _    | —    | _    |      | -    | _    |      | RPF2     | <3:0>     |      | 0000       |

| FC4C                        | RPF3R <sup>(2)</sup>  | 31:16         | —     | —             | —     |       |       | _     | —    | _    | —    |      | —    | 0000 |      |          |           |      |            |

| 1 040                       |                       | 15:0          | —     | —             | —     | —     | —     | —     | —    | —    | —    | —    | —    | —    |      | RPF3     | <3:0>     |      | 0000       |

| FC50                        | RPF4R                 | 31:16         | —     | —             | —     | —     | —     | _     | —    | -    | —    | _    | —    | —    | —    | —        | —         | —    | 0000       |

| 1000                        |                       | 15:0          | -     | —             | —     | —     | —     | _     | —    | _    | —    |      | —    | _    |      | RPF4     | <3:0>     |      | 0000       |

| FC54                        | RPF5R                 | 31:16         | —     | _             | _     | —     |       | _     | _    | —    | —    |      | —    | _    | —    |          |           | —    | 0000       |

|                             |                       | 15:0          | -     | _             | -     | —     | —     | _     | _    | _    | -    | -    | —    | _    |      | RPF5     | <3:0>     |      | 0000       |

| FC58                        | RPF6R <sup>(2)</sup>  | 31:16         | _     | _             | _     | _     |       | _     | _    |      |      | _    | _    | _    |      |          | -         |      | 0000       |

|                             |                       | 15:0<br>31:16 | _     |               |       |       |       |       |      | _    |      |      |      | _    |      | RPF6     |           |      | 0000       |

| FC60                        | RPF8R <sup>(1)</sup>  | 15:0          |       |               |       |       |       |       |      |      |      |      |      |      |      | <br>RPF8 |           | —    | 0000       |

|                             |                       | 31:16         |       |               |       |       |       |       |      |      |      |      |      |      |      |          | < <u></u> |      | 0000       |

| FC70                        | RPF12R <sup>(1)</sup> | 15:0          | _     | _             | _     | _     | _     |       | _    | _    |      |      | _    | _    |      | RPF12    | 2<3:0>    |      | 0000       |

|                             | (4)                   | 31:16         | _     |               |       |       |       | _     |      | _    | _    | _    |      | _    |      | _        | _         | _    | 0000       |

| FC74                        | RPF13R <sup>(1)</sup> | 15:0          | _     | _             | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF1     | 3<3:0>    |      | 0000       |

|                             | 55665(1)              | 31:16         | _     | _             |       |       | _     | _     | _    | _    | _    | _    | _    | _    |      | _        |           | _    | 0000       |

| FC80                        | RPG0R <sup>(1)</sup>  | 15:0          | _     | —             | _     | —     | —     | _     | —    | _    | _    | _    | —    | _    |      | RPG0     | <3:0>     |      | 0000       |

| FC84                        | RPG1R <sup>(1)</sup>  | 31:16         |       | —             |       | _     | _     |       | —    |      |      |      | _    | -    |      |          |           | _    | 0000       |

| FU04                        | RPGIR''               | 15:0          |       | _             | —     | _     | _     | _     | _    |      |      | -    | _    | _    |      | RPG1     | <3:0>     |      | 0000       |

| FC98                        | RPG6R                 | 31:16         | —     | —             | _     | —     | —     | _     | —    | —    | _    | -    | —    | —    | _    | —        |           |      | 0000       |

| 1090                        |                       | 15:0          |       | —             | _     | _     | _     | _     | —    |      | _    | _    | —    | —    |      | RPG6     | <3:0>     |      | 0000       |

| FC9C                        | RPG7R                 | 31:16         | _     | —             | —     | _     | —     | _     | —    | _    | —    |      | —    | _    | _    | _        | —         | —    | 0000       |

|                             |                       | 15:0          | —     | <br>set; = ur | —     | —     | —     | —     | —    | _    | _    | _    | _    | —    |      | RPG7     | <3:0>     |      | 0000       |

**Note 1:** This register is not available on 64-pin devices.

2: This register is only available on devices without a USB module.

3: This register is not available on 64-pin devices with a USB module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31.24        | _                 | —                 | -                 | -                    | _                 | _                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | _                    | _                 | _                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | —                 | SIDL              | _                    | _                 | _                 | —                | —                |

| 7:0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | —                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

#### REGISTER 17-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, i | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 OC32: 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisions to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in HW only)

- 0 = No PWM Fault condition has occurred

- bit 3 OCTSEL: Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin is enabled

- 110 = PWM mode on OCx; Fault pin is disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

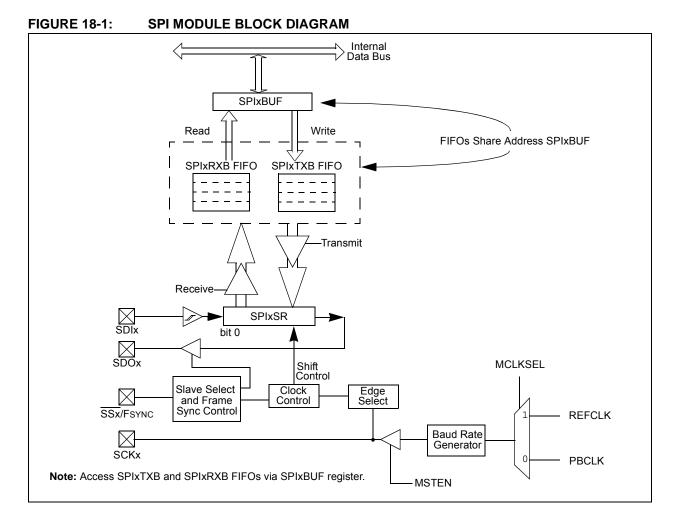

## 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. Some of the key features of the SPI module are:

- · Master and Slave modes support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- Operation during CPU Sleep and Idle mode

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

NOTES:

'0' = Bit is cleared

x = Bit is unknown

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/1 |       | Bit B<br>4/6 29/21/13/5 28/20 |       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2          | Bit<br>25/17/9/1                                                                                                                                                                                                 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------------------|-------|-------------------------------|-------|-------------------|----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|--|--|--|

| 04.04        | R/W-x                         | R/W-x | R/W-x                         | R/W-x | R/W-x             | R/W-x                      | R/W-x                                                                                                                                                                                                            | R/W-x            |  |  |  |

| 31:24        |                               | HR10• | <3:0>                         |       |                   | HR01                       | 25/17/9/1         24/1           R/W-x         R/           1<3:0>         R/W-x           R/W-x         R/           01<3:0>         R/W-x           U         01           U         01           U         01 |                  |  |  |  |

| 00.40        | R/W-x                         | R/W-x | R/W-x                         | R/W-x | R/W-x             | R/W-x                      | R/W-x                                                                                                                                                                                                            | R/W-x            |  |  |  |

| 23:16        |                               | MIN10 | <3:0>                         |       | MIN01<3:0>        |                            |                                                                                                                                                                                                                  |                  |  |  |  |

| 45.0         | R/W-x                         | R/W-x | R/W-x                         | R/W-x | R/W-x             | R/W-x                      | R/W-x                                                                                                                                                                                                            | R/W-x            |  |  |  |

| 15:8         |                               | SEC10 | <3:0>                         |       |                   | SEC01                      | R/W-x R/W-<br>01<3:0>                                                                                                                                                                                            |                  |  |  |  |

| 7.0          | U-0                           | U-0   | U-0                           | U-0   | U-0               | HR01<3<br>R/W-x<br>MIN01<3 | U-0                                                                                                                                                                                                              | U-0              |  |  |  |

| 7:0          | —                             | —     | _                             | _     | _                 | —                          | —                                                                                                                                                                                                                | _                |  |  |  |

|              |                               |       |                               |       |                   |                            |                                                                                                                                                                                                                  |                  |  |  |  |

| Legend:      |                               |       |                               |       |                   |                            |                                                                                                                                                                                                                  |                  |  |  |  |

| R = Read     | able bit                      |       | W = Writable                  | e bit | U = Unimple       | emented bit, re            | ead as '0'                                                                                                                                                                                                       |                  |  |  |  |

### REGISTER 22-3: RTCTIME: RTC TIME VALUE REGISTER

bit 31-28 HR10<3:0>: Binary-Coded Decimal Value of Hours bits, 10s place digits; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary-Coded Decimal Value of Hours bits, 1s place digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary-Coded Decimal Value of Minutes bits, 10s place digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary-Coded Decimal Value of Minutes bits, 1s place digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary-Coded Decimal Value of Seconds bits, 10s place digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary-Coded Decimal Value of Seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

'1' = Bit is set

-n = Value at POR

## TABLE 23-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 0                                  |                                    | Bits                               |       |       |       |       |         |            |          |          |      |      | ŝ    |      |      |      |            |

|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------|------------------------------------|------------------------------------|-------|-------|-------|-------|---------|------------|----------|----------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register R | Bit Range                          | 31/15                              | 30/14                              | 29/13 | 28/12 | 27/11 | 26/10 | 25/9    | 24/8       | 23/7     | 22/6     | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 9110                        | ADC1BUFA                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ADC Result Word A (ADC1BUFA<31:0>) |                                    |                                    |       |       |       |       |         |            |          | 0000     |      |      |      |      |      |      |            |

| 9120                        | ADC1BUFB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31:16<br>15:0                      | ADC Result Word B (ADC1BUFB<31:0>) |                                    |       |       |       |       |         |            |          |          | 0000 |      |      |      |      |      |            |

| 9130                        | ADC1BUFC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31:16<br>15:0                      | ADC Result Word C (ADC1BUFC<31:0>) |                                    |       |       |       |       |         |            |          |          | 0000 |      |      |      |      |      |            |

| 9140                        | ADC1BUFD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31:16<br>15:0                      | ADC Result Word D (ADC1BUFD<31:0>) |                                    |       |       |       |       |         |            |          |          | 0000 |      |      |      |      |      |            |

| 9150                        | ADC1BUFE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31:16<br>15:0                      |                                    | ADC Result Word E (ADC1BUFE<31:0>) |       |       |       |       |         |            |          |          | 0000 |      |      |      |      |      |            |

| 9160                        | ADC1BUFF                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 31:16<br>15:0                      |                                    |                                    |       |       |       |       | ADC Res | ult Word F | (ADC1BUF | F<31:0>) |      |      |      |      |      |      | 0000       |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for details.

## 30.0 DEVELOPMENT SUPPORT

The PIC<sup>®</sup> microcontrollers (MCU) and dsPIC<sup>®</sup> digital signal controllers (DSC) are supported with a full range of software and hardware development tools:

- Integrated Development Environment

- MPLAB<sup>®</sup> X IDE Software

- Compilers/Assemblers/Linkers

- MPLAB XC Compiler

- MPASM<sup>™</sup> Assembler

- MPLINK<sup>™</sup> Object Linker/ MPLIB<sup>™</sup> Object Librarian

- MPLAB Assembler/Linker/Librarian for Various Device Families

- Simulators

- MPLAB X SIM Software Simulator

- Emulators

- MPLAB REAL ICE™ In-Circuit Emulator

- In-Circuit Debuggers/Programmers

- MPLAB ICD 3

- PICkit™ 3

- Device Programmers

- MPLAB PM3 Device Programmer

- Low-Cost Demonstration/Development Boards, Evaluation Kits and Starter Kits

- Third-party development tools

## 30.1 MPLAB X Integrated Development Environment Software

The MPLAB X IDE is a single, unified graphical user interface for Microchip and third-party software, and hardware development tool that runs on Windows<sup>®</sup>, Linux and Mac OS<sup>®</sup> X. Based on the NetBeans IDE, MPLAB X IDE is an entirely new IDE with a host of free software components and plug-ins for high-performance application development and debugging. Moving between tools and upgrading from software simulators to hardware debugging and programming tools is simple with the seamless user interface.

With complete project management, visual call graphs, a configurable watch window and a feature-rich editor that includes code completion and context menus, MPLAB X IDE is flexible and friendly enough for new users. With the ability to support multiple tools on multiple projects with simultaneous debugging, MPLAB X IDE is also suitable for the needs of experienced users.

Feature-Rich Editor:

- · Color syntax highlighting

- Smart code completion makes suggestions and provides hints as you type

- Automatic code formatting based on user-defined rules

- · Live parsing

User-Friendly, Customizable Interface:

- Fully customizable interface: toolbars, toolbar buttons, windows, window placement, etc.

- Call graph window

- Project-Based Workspaces:

- Multiple projects

- Multiple tools

- · Multiple configurations

- · Simultaneous debugging sessions

File History and Bug Tracking:

- · Local file history feature