Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | ·                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

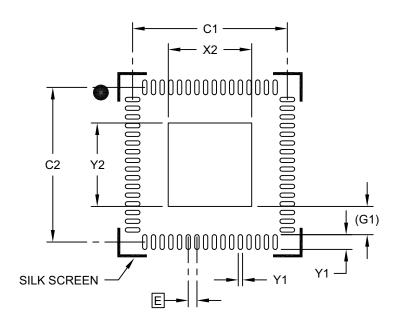

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256h-v-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1  |                        | Pin Numb        | er                               |             |                |                                                     |  |  |  |  |  |  |

|----------|------------------------|-----------------|----------------------------------|-------------|----------------|-----------------------------------------------------|--|--|--|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA                  | Pin<br>Type | Buffer<br>Type | Description                                         |  |  |  |  |  |  |

| RB0      | 16                     | 25              | B14                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RB1      | 15                     | 24              | A15                              | I/O         | ST             | 7                                                   |  |  |  |  |  |  |

| RB2      | 14                     | 23              | B13                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RB3      | 13                     | 22              | A13                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RB4      | 12                     | 21              | B11                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RB5      | 11                     | 20              | A12                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RB6      | 17                     | 26              | A20                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RB7      | 18                     | 27              | B16                              | I/O         | ST             | PORTB is a bidirectional I/O port                   |  |  |  |  |  |  |

| RB8      | 21                     | 32              | A23                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RB9      | 22                     | 33              | B19                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RB10     | 23                     | 34              | A24                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RB11     | 24                     | 35              | B20                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RB12     | 27                     | 41              | B23                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RB13     | 28                     | 42              | A28                              | I/O         | ST             | 7                                                   |  |  |  |  |  |  |

| RB14     | 29                     | 43              | B24                              | I/O         | ST             | 7                                                   |  |  |  |  |  |  |

| RB15     | 30                     | 44              | A29                              | I/O         | ST             | 7                                                   |  |  |  |  |  |  |

| RC1      | —                      | 6               | A5                               | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RC2      | —                      | 7               | B4                               | I/O         | ST             | 7                                                   |  |  |  |  |  |  |

| RC3      | —                      | 8               | A6                               | I/O         | ST             | 7                                                   |  |  |  |  |  |  |

| RC4      | —                      | 9               | B5                               | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RC12     | 39                     | 63              | B34                              | I/O         | ST             | PORTC is a bidirectional I/O port                   |  |  |  |  |  |  |

| RC13     | 47                     | 73              | A47                              | I/O         | ST             | 7                                                   |  |  |  |  |  |  |

| RC14     | 48                     | 74              | B40                              | I/O         | ST             | 7                                                   |  |  |  |  |  |  |

| RC15     | 40                     | 64              | A42                              | I/O         | ST             | 7                                                   |  |  |  |  |  |  |

| RD0      | 46                     | 72              | B39                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RD1      | 49                     | 76              | A52                              | I/O         | ST             | 7                                                   |  |  |  |  |  |  |

| RD2      | 50                     | 77              | B42                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RD3      | 51                     | 78              | A53                              | I/O         | ST             | 7                                                   |  |  |  |  |  |  |

| RD4      | 52                     | 81              | B44                              | I/O         | ST             | 7                                                   |  |  |  |  |  |  |

| RD5      | 53                     | 82              | A55                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RD6      | 54                     | 83              | B45                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RD7      | 55                     | 84              | A56                              | I/O         | ST             | POPTD is a hidiractional UC sort                    |  |  |  |  |  |  |

| RD8      | 42                     | 68              | B37                              | I/O         | ST             | PORTD is a bidirectional I/O port                   |  |  |  |  |  |  |

| RD9      | 43                     | 69              | A45                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RD10     | 44                     | 70              | B38                              | I/O         | ST             | 1                                                   |  |  |  |  |  |  |

| RD11     | 45                     | 71              | A46                              | I/O         | ST             | 1                                                   |  |  |  |  |  |  |

| RD12     | —                      | 79              | B43                              | I/O         | ST             | 1                                                   |  |  |  |  |  |  |

| RD13     | —                      | 80              | A54                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RD14     | —                      | 47              | B26                              | I/O         | ST             |                                                     |  |  |  |  |  |  |

| RD15     | —                      | 48              | A31                              | I/O         | I/O ST         |                                                     |  |  |  |  |  |  |

| -        |                        | itt Trigger inp | ible input or o<br>out with CMOS |             |                | alog = Analog input P = Power<br>= Output I = Input |  |  |  |  |  |  |

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS (CONTINUED)

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|--|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                    |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |  |  |

| 23:16        | _                 | —                 | —                 | _                 | _                 | —                 | —                | —                    |  |  |  |  |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |  |  |  |  |

| 15:8         | —                 | _                 | _                 | _                 | _                 | —                 |                  | —                    |  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |  |  |  |  |  |

| 7:0          |                   |                   |                   | _                 |                   | _                 | _                | SWRST <sup>(1)</sup> |  |  |  |  |  |

## REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:         HC = Cleared by hardware |                  |                                             |                    |  |  |  |  |  |  |

|------------------------------------------|------------------|---------------------------------------------|--------------------|--|--|--|--|--|--|

| R = Readable bit                         | W = Writable bit | able bit U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |  |

| -n = Value at POR                        | '1' = Bit is set | '0' = Bit is cleared                        | x = Bit is unknown |  |  |  |  |  |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup>

- 1 = Enable software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

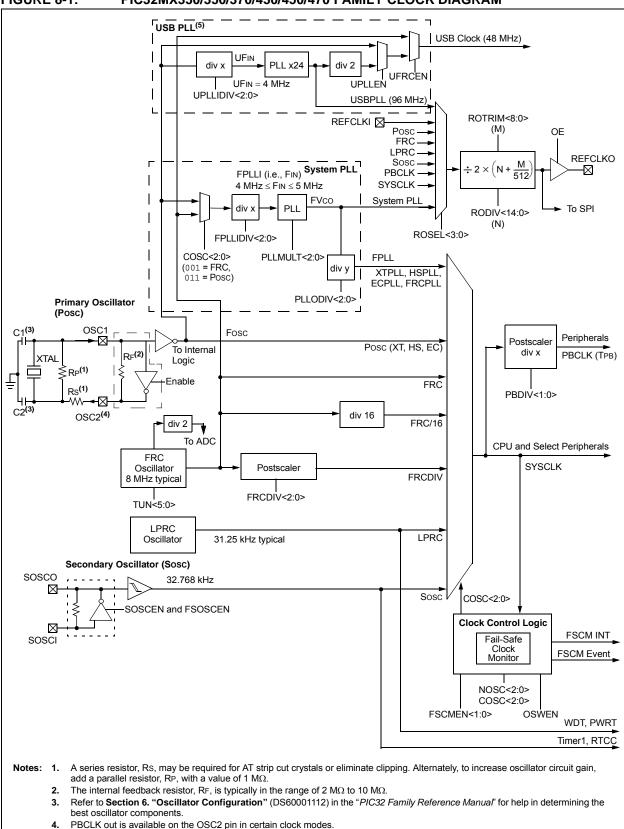

## 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features      |  |  |  |  |  |  |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|

|       | of the PIC32MX330/350/370/430/450/           |  |  |  |  |  |  |  |  |  |  |  |

|       | 470 family of devices. It is not intended to |  |  |  |  |  |  |  |  |  |  |  |

|       | be a comprehensive reference source. To      |  |  |  |  |  |  |  |  |  |  |  |

|       | complement the information in this data      |  |  |  |  |  |  |  |  |  |  |  |

|       | sheet, refer to Section 6. "Oscillator       |  |  |  |  |  |  |  |  |  |  |  |

|       | Configuration" (DS60001112), which is        |  |  |  |  |  |  |  |  |  |  |  |

|       | available from the Documentation >           |  |  |  |  |  |  |  |  |  |  |  |

|       | Reference Manual section of the              |  |  |  |  |  |  |  |  |  |  |  |

|       | Microchip PIC32 web site                     |  |  |  |  |  |  |  |  |  |  |  |

|       | (www.microchip.com/pic32).                   |  |  |  |  |  |  |  |  |  |  |  |

The PIC32MX330/350/370/430/450/470 oscillator system has the following modules and features:

- A Total of four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

#### FIGURE 8-1: PIC32MX330/350/370/430/450/470 FAMILY CLOCK DIAGRAM

5. USB PLL is available on PIC32MX4XX devices only.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | -                 | —                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | —                 | -                 | -                 | —                 | _                 | _                | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         |                   | —                 | _                 | _                 | —                 |                   | _                | —                |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   |                   | CHPDAT            | 7:0>              |                   |                  |                  |

## REGISTER 10-18: DCHxDAT: DMA CHANNEL 'x' PATTERN DATA REGISTER

## Legend:

| ========          |                  |                                    |                    |  |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

#### bit 7-0 **CHPDAT<7:0>:** Channel Data Register bits

Pattern Terminate mode: Data to be matched must be stored in this register to allow terminate on match.

All other modes: Unused.

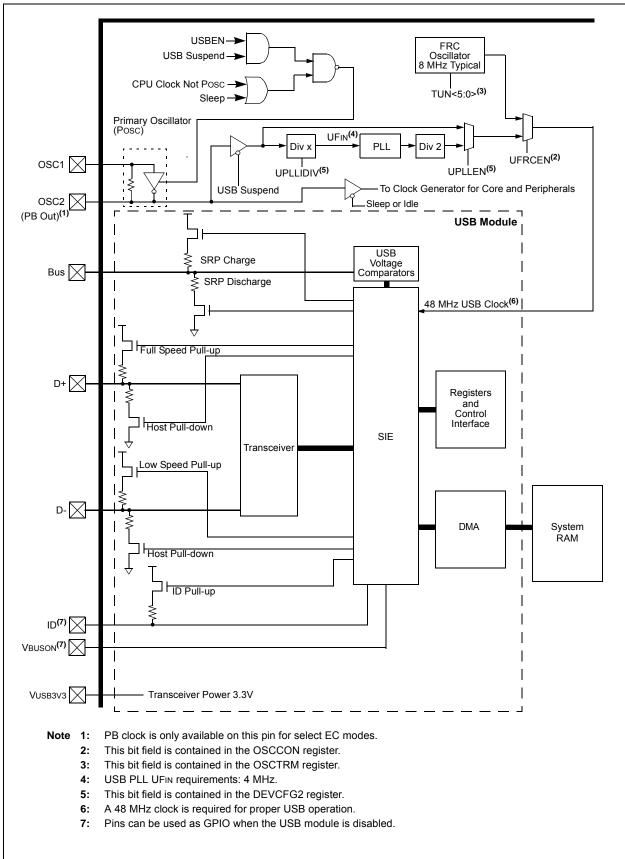

FIGURE 11-1: PIC32MX430/450/470 USB INTERFACE DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

|              | —                 | —                 |                   | —                 | _                      | —                 | —                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23.10        | —                 | —                 |                   | —                 | _                      | —                 | —                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 15.0         | —                 | —                 |                   | —                 | _                      | —                 | —                | _                |

| 7:0          | R-0               | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | R/W-0            | R/W-0            |

| 7.0          | UACTPND           | _                 |                   | USLPGRD           | USBBUSY <sup>(1)</sup> |                   | USUSPEND         | USBPWR           |

#### REGISTER 11-5: U1PWRC: USB POWER CONTROL REGISTER

#### Legend:

| zogonai           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 UACTPND: USB Activity Pending bit

- 1 = USB bus activity has been detected; but an interrupt is pending, it has not been generated yet

0 = An interrupt is not pending

- bit 6-5 Unimplemented: Read as '0'

- bit 4 USLPGRD: USB Sleep Entry Guard bit

- 1 = Sleep entry is blocked if USB bus activity is detected or if a notification is pending

- 0 = USB module does not block Sleep entry

- bit 3 USBBUSY: USB Module Busy bit<sup>(1)</sup>

- 1 = USB module is active or disabled, but not ready to be enabled

- 0 = USB module is not active and is ready to be enabled

- **Note:** When USBPWR = 0 and USBBUSY = 1, status from all other registers is invalid and writes to all USB module registers produce undefined results.

- bit 2 Unimplemented: Read as '0'

- bit 1 USUSPEND: USB Suspend Mode bit

- 1 = USB module is placed in Suspend mode

- (The 48 MHz USB clock will be gated off. The transceiver is placed in a low-power state.)

- 0 = USB module operates normally

- bit 0 USBPWR: USB Operation Enable bit

- 1 = USB module is turned on

- 0 = USB module is disabled

(Outputs held inactive, device pins not used by USB, analog features are shut down to reduce power consumption.)

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Periphera<br>Selection |

|----------------------|----------|-------------|--------------------------------------|

| RPD2                 | RPD2R    | RPD2R<3:0>  | 0000 = No Connect                    |

| RPG8                 | RPG8R    | RPG8R<3:0>  | 0001 = U3TX                          |

| RPF4                 | RPF4R    | RPF4R<3:0>  | 0010 = U4RTS<br>0011 = Reserved      |

| RPD10                | RPD10R   | RPD10R<3:0> | 0100 = Reserved                      |

| RPF1                 | RPF1R    | RPF1R<3:0>  | 0101 = Reserved                      |

| RPB9                 | RPB9R    | RPB9R<3:0>  | 0110 = SDO2                          |

| RPB10                | RPB10R   | RPB10R<3:0> | 0111 = Reserved<br>1000 = Reserved   |

| RPC14                | RPC14R   | RPC14R<3:0> | 1000 = Reserved                      |

| RPB5                 | RPB5R    | RPB5R<3:0>  | 1010 = Reserved                      |

| RPC1 <sup>(4)</sup>  | RPC1R    | RPC1R<3:0>  | 1011 <b>= OC3</b>                    |

| RPD14 <sup>(4)</sup> | RPD14R   | RPD14R<3:0> | 1100 = Reserved<br>1101 = C2OUT      |

| RPG1 <sup>(4)</sup>  | RPG1R    | RPG1R<3:0>  | 1110 = Reserved                      |

| RPA14 <sup>(4)</sup> | RPA14R   | RPA14R<3:0> | 1111 = Reserved                      |

| RPD3                 | RPD3R    | RPD3R<3:0>  | 0000 = No Connect                    |

| RPG7                 | RPG7R    | RPG7R<3:0>  | 0001 = U2TX                          |

| RPF5                 | RPF5R    | RPF5R<3:0>  | 0010 = Reserved                      |

| RPD11                | RPD11R   | RPD11R<3:0> |                                      |

| RPF0                 | RPF0R    | RPF0R<3:0>  | 0100 = 05RTS(*)                      |

| RPB1                 | RPB1R    | RPB1R<3:0>  | 0110 = SDO2                          |

| RPE5                 | RPE5R    | RPE5R<3:0>  | 0111 = Reserved                      |

| RPC13                | RPC13R   | RPC13R<3:0> | 1000 <b>= SDO1</b>                   |

| RPB3                 | RPB3R    | RPB3R<3:0>  | 1001 = Reserved                      |

| RPF3 <sup>(2)</sup>  | RPF3R    | RPF3R<3:0>  | 1010 = Reserved                      |

| RPC4 <sup>(4)</sup>  | RPC4R    | RPC4R<3:0>  | 1011 = OC4<br>1100 = Reserved        |

| RPD15 <sup>(4)</sup> | RPD15R   | RPD15R<3:0> | 1100 - Reserved                      |

| RPG0 <sup>(4)</sup>  | RPG0R    | RPG0R<3:0>  | 1110 = Reserved                      |

| RPA15 <sup>(4)</sup> | RPA15R   | RPA15R<3:0> | 1111 = Reserved                      |

## TABLE 12-2: OUTPUT PIN SELECTION

Note 1: This selection is only available on General Purpose devices.

**2:** This selection is only available on 64-pin General Purpose devices.

3: This selection is only available on 100-pin General Purpose devices.

4: This selection is only available on 100-pin USB and General Purpose devices.

5: This selection is not available on 64-pin USB devices.

#### TABLE 12-8: PORTD REGISTER MAP FOR PIC32MX330F064H, PIC32MX350F128H, PIC32MX350F256H, PIC32MX370F512H, PIC32MX430F064H, PIC32MX450F128H, PIC32MX450F256H, PIC32MX470F512H DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |               |               |              | В            | its          |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                          | 31:16     | _     | —     | —     | —     | _             | -             | —            | _            | —            | _            | —            | _            | _            | —            | —            |              | 0000          |

| 0000                        | ANOLLD                          | 15:0      | —     | —     | _     | —     |               | _             |              | _            | —            | _            |              |              | ANSELD3      | ANSELD2      | ANSELD1      |              | 000E          |

| 6310                        | TRISD                           | 31:16     | _     | —     | _     | —     | _             |               | _            | —            | _            | —            | _            | _            | _            | —            | —            |              | 0000          |

| 00.0                        |                                 | 15:0      | —     | —     | —     | —     | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | xxxx          |

| 5320                        | PORTD                           | 31:16     | —     | —     | —     | —     | —             |               | —            | —            | —            | —            | —            | —            | —            | —            | —            |              | 0000          |

| 0020                        |                                 | 15:0      | —     | —     | —     | —     | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | xxxx          |

| 6330                        | LATD                            | 31:16     | —     | —     | —     | —     | —             |               | —            | —            | —            | —            | —            | —            | —            | —            | —            |              | 0000          |

|                             |                                 | 15:0      | —     | —     | —     | —     | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | xxxx          |

| 6340                        | ODCD                            | 31:16     | —     | —     | —     | —     | _             | —             | _            | —            | —            | —            | —            | —            | —            | —            | _            |              | 0000          |

|                             |                                 | 15:0      | —     | —     | —     | —     | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | xxxx          |

| 6350                        | CNPUD                           | 31:16     | —     | —     | —     | —     | _             | —             | _            | —            | —            | —            | —            | —            | —            | —            | _            |              | 0000          |

|                             |                                 | 15:0      | —     | —     | —     | —     | CNPUD11       | CNPUD10       | CNPUD9       | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | xxxx          |

| 6360                        | CNPDD                           | 31:16     | —     | —     | —     | —     | _             | —             | _            | —            | —            | —            | —            | —            | —            | —            | _            |              | 0000          |

|                             |                                 | 15:0      | —     | —     | —     | —     | CNPDD11       | CNPDD10       | CNPDD9       | CNPDD8       | CNPDD7       | CNPDD6       | CNPDD5       | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | xxxx          |

| 6370                        | CNCOND                          | 31:16     | —     | —     | —     | —     | _             | —             | —            | _            | —            | _            | _            | _            | _            | —            | —            |              | 0000          |

|                             |                                 | 15:0      | ON    | —     | SIDL  | —     | _             | —             | —            | _            | —            | _            | _            | _            | _            | —            | —            |              | 0000          |

| 6380                        | CNEND                           | 31:16     | —     | —     | —     | —     | _             | -             | —            | -            | —            | -            | —            | —            | -            | —            | —            | -            | 0000          |

|                             | 0.12.10                         | 15:0      | —     | —     | —     | —     | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | xxxx          |

|                             |                                 | 31:16     | _     | _     | _     | _     | —             | _             | —            | —            | —            | —            | —            | —            | —            | —            | —            | _            | 0000          |

| 6390                        | CNSTATD                         | 15:0      | _     | —     | —     | —     | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | xxxx          |

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

## 13.2 Control Registers

### TABLE 13-1: TIMER1 REGISTER MAP

| ess                       |       | 0         |       | Bits  |       |       |       |       |      |      |        |      |      |        |      |       |      | s    |            |

|---------------------------|-------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------|------|------|--------|------|-------|------|------|------------|

| Virtual Addre<br>(BF80_#) |       | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5 | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 0600                      | T1CON | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | —    | —      | —    | —     | _    | _    | 0000       |

| 0600                      | TICON | 15:0      | ON    | _     | SIDL  | TWDIS | TWIP  | _     | _    | _    | TGATE  | _    | TCKP | S<1:0> | —    | TSYNC | TCS  | _    | 0000       |

| 0610                      | TMR1  | 31:16     |       | _     | —     | —     | —     | _     | —    | _    | —      | —    | _    | —      | —    | —     | —    | —    | 0000       |

| 0010                      |       | 15:0      |       |       |       |       |       |       |      | TMR1 | <15:0> |      |      |        |      |       |      |      | 0000       |

| 0620                      | PR1   | 31:16     | _     | _     | _     | _     | _     | -     | -    | -    | —      | _    | —    | —      | —    | _     | _    | -    | 0000       |

| 0020                      | FIXI  | 15:0      |       |       |       |       |       |       |      | PR1< | 15:0>  |      |      |        |      |       |      |      | FFFF       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

## 15.1 Watchdog Timer Control Registers

| DS60001185F-page |  |

|------------------|--|

| (D)              |  |

| 78               |  |

## TABLE 15-1: WATCHDOG TIMER CONTROL REGISTER MAP

| ess                        |                                 | æ         |       | Bits  |       |       |       |       |      |      |      | s    |      |          |      |      |          |        |           |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|------|------|----------|--------|-----------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3 | 18/2 | 17/1     | 16/0   | All Reset |

| 0000                       | WDTCON                          | 31:16     | _     | _     | _     | _     | -     | -     | —    | —    | _    | —    | —    | _        | _    | _    | —        | —      | 0000      |

| 0000                       | WDICON                          | 15:0      | ON    |       |       |       | _     | _     | _    | _    |      |      | SI   | VDTPS<4: | )>   |      | WDTWINEN | WDTCLR | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

### 16.1 Control Register

#### REGISTER 16-1: ICxCON: INPUT CAPTURE 'x' CONTROL REGISTER

| Bit Range                                                 | Bit<br>31/23/15/7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Bit<br>30/22/14/6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Bit<br>29/21/13/5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Bit<br>28/20/12/4                                                                                                     | Bit<br>27/19/11/3          | Bit<br>26/18/10/2         | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------|---------------------------|------------------|------------------|--|--|

| 31:24                                                     | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                   | U-0                        | U-0                       | U-0              | U-0              |  |  |

| 01.24                                                     | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | —                                                                                                                     | —                          | —                         | —                | —                |  |  |

| 23:16                                                     | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | U-0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | U-0                                                                                                                   | U-0                        | U-0                       | U-0              | U-0              |  |  |

|                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | —                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | —                                                                                                                     | —                          |                           | —                |                  |  |  |