Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 49                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-TQFP                                                                         |

| Supplier Device Package    | 64-TQFP (10x10)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256ht-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

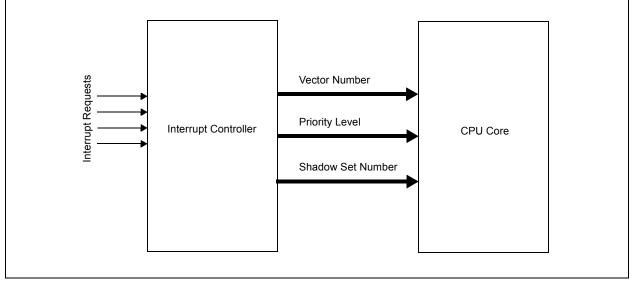

# 7.0 INTERRUPT CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 8. "Interrupt Controller" (DS60001108), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX330/350/370/430/450/470 devices generate interrupt requests in response to interrupt events from peripheral modules. The interrupt control module exists externally to the CPU logic and prioritizes the interrupt events before presenting them to the CPU.

The PIC32MX330/350/370/430/450/470 interrupt module includes the following features:

- Up to 76 interrupt sources

- · Up to 46 interrupt vectors

- · Single and multi-vector mode operations

- Five external interrupts with edge polarity control

- Interrupt proximity timer

- Seven user-selectable priority levels for each vector

- Four user-selectable subpriority levels within each priority

- Dedicated shadow set configurable for any priority level (see the FSRSSEL<2:0> bits (DEVCFG3<18:16>) in 28.0 "Special Features" for more information)

- Software can generate any interrupt

- User-configurable interrupt vector table location

- User-configurable interrupt vector spacing

# FIGURE 7-1: INTERRUPT CONTROLLER MODULE BLOCK DIAGRAM

| TABLE 7-2: IN | ITERRUPT REGISTER | MAP (CONTINUED) |

|---------------|-------------------|-----------------|

|---------------|-------------------|-----------------|

| ess                         |                  | <sup>0</sup> |       |       |       |       |               |       |                         | Bits             |      |       |       |             |           |        |        |        |               |

|-----------------------------|------------------|--------------|-------|-------|-------|-------|---------------|-------|-------------------------|------------------|------|-------|-------|-------------|-----------|--------|--------|--------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name | Bit Range    | 31/15 | 30/14 | 29/13 | 28/12 | 27/11         | 26/10 | 25/9                    | 24/8             | 23/7 | 22/6  | 21/5  | 20/4        | 19/3      | 18/2   | 17/1   | 16/0   | All<br>Resets |

| 10F0                        | IPC6             | 31:16        | _     | _     | —     | (     | CMP1IP<2:0    | >     | CMP1IS                  | S<1:0>           | _    | _     | —     | F           | CEIP<2:0> |        | FCEIS  | S<1:0> | 0000          |

| 101.0                       | IF CO            | 15:0         | —     | _     | —     |       | RTCCIP<2:0>   |       | RTCCIS                  | S<1:0>           | _    | _     | —     | FSCMIP<2:0> |           | >      | FSCMI  | S<1:0> | 0000          |

| 1100                        | 1100 IPC7 31:    |              |       | _     | _     |       | U1IP<2:0>     |       | U1IS<                   | <1:0>            | _    | _     | _     | SPI1IP<2:0> |           | SPI1IS | 6<1:0> | 0000   |               |

| 1100                        | IPC7             | 15:0         |       | _     | _     | ι     | USBIP<2:0>(2) |       | USBIS<                  | :1:0> <b>(2)</b> | _    | _     | _     | CMP2IP<2:0> |           | CMP2   | S<1:0> | 0000   |               |

| 1110                        | IPC8             | 31:16        | _     | —     | —     |       | SPI2IP<2:0>   |       | SPI2IS                  | <1:0>            | _    | _     | —     | PMPIP<2:0>  |           | PMPIS  | 6<1:0> | 0000   |               |

| 1110                        | IPCo             | 15:0         | _     | —     | —     |       | CNIP<2:0>     |       | CNIS                    | <1:0>            | _    | _     | —     | I2C1IP<2:0> |           | 12C115 | 6<1:0> | 0000   |               |

| 1100                        | IPC9             | 31:16        | _     | _     | _     |       | U4IP<2:0>     |       | U4IS<1:0> — — U3IP<2:0> |                  |      | U3IS- | <1:0> | 0000        |           |        |        |        |               |

| 1120                        | IPC9             | 15:0         |       | _     | _     |       | I2C2IP<2:0>   |       | I2C2IS                  | <1:0>            | _    | _     | _     | l           | J2IP<2:0> |        | U2IS-  | <1:0>  | 0000          |

| 1120                        | IPC10            | 31:16        | _     | —     | —     | I     | DMA1IP<2:0    | >     | DMA1IS                  | S<1:0>           | _    | _     | —     | DI          | MA0IP<2:0 | >      | DMA0   | S<1:0> | 0000          |

| 1130                        | IPCIU            | 15:0         | _     | _     | _     | (     | CTMUIP<2:0    | >     | CTMU                    | S<1:0>           | _    | _     | —     | l           | J5IP<2:0> |        | U5IS-  | <1:0>  | 0000          |

| 11.10                       | IPC11            | 31:16        | _     | —     | —     | —     | —             | —     | —                       | —                | _    | _     | —     | —           | —         | —      | _      | _      | 0000          |

| 1140 I                      | IPUTT            | 15:0         | _     | -     |       |       | DMA3IP<2:0    | >     | DMA3IS                  | S<1:0>           | _    | _     | _     | DI          | MA2IP<2:0 | >      | DMA2I  | S<1:0> | 0000          |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This bit is only available on 100-pin devices.

2: This bit is only implemented on devices with a USB module.

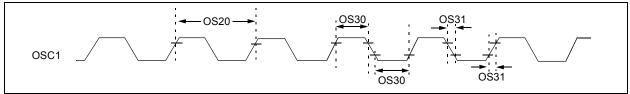

# 8.0 OSCILLATOR CONFIGURATION

| Note: | This data sheet summarizes the features      |  |  |  |  |  |

|-------|----------------------------------------------|--|--|--|--|--|

|       | of the PIC32MX330/350/370/430/450/           |  |  |  |  |  |

|       | 470 family of devices. It is not intended to |  |  |  |  |  |

|       | be a comprehensive reference source. To      |  |  |  |  |  |

|       | complement the information in this data      |  |  |  |  |  |

|       | sheet, refer to Section 6. "Oscillator       |  |  |  |  |  |

|       | Configuration" (DS60001112), which is        |  |  |  |  |  |

|       | available from the Documentation >           |  |  |  |  |  |

|       | Reference Manual section of the              |  |  |  |  |  |

|       | Microchip PIC32 web site                     |  |  |  |  |  |

|       | (www.microchip.com/pic32).                   |  |  |  |  |  |

The PIC32MX330/350/370/430/450/470 oscillator system has the following modules and features:

- A Total of four external and internal oscillator options as clock sources

- On-Chip PLL with user-selectable input divider, multiplier and output divider to boost operating frequency on select internal and external oscillator sources

- On-Chip user-selectable divisor postscaler on select oscillator sources

- Software-controllable switching between various clock sources

- A Fail-Safe Clock Monitor (FSCM) that detects clock failure and permits safe application recovery or shutdown

- Dedicated On-Chip PLL for USB peripheral

A block diagram of the oscillator system is provided in Figure 8-1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | DCRCDATA<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | DCRCDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | DCRCDA            | TA<7:0>           |                   |                  |                  |  |  |

### REGISTER 10-5: DCRCDATA: DMA CRC DATA REGISTER

# Legend:

| Legena:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

### REGISTER 10-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   | DCRCXOR<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | DCRCXOR<7:0>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

# PIC32MX330/350/370/430/450/470

### REGISTER 10-16: DCHxCSIZ: DMA CHANNEL 'x' CELL-SIZE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | -                | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | _                 | —                 | _                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | CHCSIZ<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   | CHCSIZ<7:0>       |                   |                   |                   |                   |                  |                  |  |  |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

bit 15-0 CHCSIZ<15:0>: Channel Cell-Size bits

1111111111111111 = 65,535 bytes transferred on an event

### REGISTER 10-17: DCHxCPTR: DMA CHANNEL 'x' CELL POINTER REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | -                 | —                 | —                 | -                 | —                 |                   |                  | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                 | _                | —                |  |  |

| 45.0         | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | CHCPTR<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   | CHCPTR<7:0>       |                   |                   |                   |                   |                  |                  |  |  |

| Legend:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

bit 31-16 Unimplemented: Read as '0'

### Note: When in Pattern Detect mode, this register is reset on a pattern detect.

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              |                   | _                 | -                 | _                 |                   |                   |                  | -                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | -                 | _                 |                   |                   |                  | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | _                 | -                 | _                 |                   |                   |                  | —                |

| 7:0          | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | LSPD              | RETRYDIS          |                   | EPCONDIS          | EPRXEN            | EPTXEN            | EPSTALL          | EPHSHK           |

### REGISTER 11-21: U1EP0-U1EP15: USB ENDPOINT CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

- bit 7 LSPD: Low-Speed Direct Connection Enable bit (Host mode and U1EP0 only)

- 1 = Direct connection to a low-speed device is enabled

- 0 = Direct connection to a low-speed device is disabled; hub required with PRE\_PID

- bit 6 **RETRYDIS:** Retry Disable bit (Host mode and U1EP0 only)

- 1 = Retry NAKed transactions is disabled

- 0 = Retry NAKed transactions is enabled; retry done in hardware

### bit 5 Unimplemented: Read as '0'

bit 4 **EPCONDIS:** Bidirectional Endpoint Control bit

If EPTXEN = 1 and EPRXEN = 1:

1 = Disable Endpoint n from Control transfers; only TX and RX transfers allowed

0 = Enable Endpoint n for Control (SETUP) transfers; TX and RX transfers also allowed Otherwise, this bit is ignored.

- bit 3 **EPRXEN:** Endpoint Receive Enable bit

- 1 = Endpoint n receive is enabled

- 0 = Endpoint n receive is disabled

- bit 2 EPTXEN: Endpoint Transmit Enable bit

- 1 = Endpoint n transmit is enabled

- 0 = Endpoint n transmit is disabled

- bit 1 EPSTALL: Endpoint Stall Status bit

- 1 = Endpoint n was stalled

- 0 = Endpoint n was not stalled

- bit 0 EPHSHK: Endpoint Handshake Enable bit

- 1 = Endpoint Handshake is enabled

- 0 = Endpoint Handshake is disabled (typically used for isochronous endpoints)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | _                 |                   | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 |                   |                   | _                 | _                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | _                 | _                | —                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             |                   | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER

# Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

### bit 31-16 Unimplemented: Read as '0'

| DIL 31-10 | ommplemented: Read as 0                                                                                                                                                        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | ON: Timer On bit <sup>(1)</sup>                                                                                                                                                |

|           | 1 = Timer is enabled                                                                                                                                                           |

|           | 0 = Timer is disabled                                                                                                                                                          |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                                                                                    |

|           | <ul><li>1 = Discontinue operation when device enters Idle mode</li><li>0 = Continue operation even in Idle mode</li></ul>                                                      |

| bit 12    | TWDIS: Asynchronous Timer Write Disable bit                                                                                                                                    |

|           | <ul><li>1 = Writes to TMR1 are ignored until pending write operation completes</li><li>0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)</li></ul> |

| bit 11    | TWIP: Asynchronous Timer Write in Progress bit                                                                                                                                 |

|           | In Asynchronous Timer mode:                                                                                                                                                    |

|           | 1 = Asynchronous write to TMR1 register in progress                                                                                                                            |

|           | 0 = Asynchronous write to TMR1 register complete                                                                                                                               |

|           | In Synchronous Timer mode:<br>This bit is read as '0'.                                                                                                                         |

| bit 10-8  | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 7     | TGATE: Timer Gated Time Accumulation Enable bit                                                                                                                                |

|           | When TCS = 1:                                                                                                                                                                  |

|           | This bit is ignored.                                                                                                                                                           |

|           | When TCS = 0:<br>1 = Gated time accumulation is enabled                                                                                                                        |

|           | 0 = Gated time accumulation is disabled                                                                                                                                        |

| bit 6     | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 5-4   | TCKPS<1:0>: Timer Input Clock Prescale Select bits                                                                                                                             |

|           | 11 = 1:256 prescale value                                                                                                                                                      |

|           | 10 = 1:64 prescale value                                                                                                                                                       |

|           | 01 = 1:8 prescale value<br>00 = 1:1 prescale value                                                                                                                             |

| bit 3     |                                                                                                                                                                                |

| DILO      | Unimplemented: Read as '0'                                                                                                                                                     |

|           |                                                                                                                                                                                |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# 18.1 Control Registers

# TABLE 18-1: SPI2 AND SPI2 REGISTER MAP

| ess                         |                                 | 6         |               |         |        |              |              |              |           | Bit    | s       |        |        |          |             |          |        |         |            |

|-----------------------------|---------------------------------|-----------|---------------|---------|--------|--------------|--------------|--------------|-----------|--------|---------|--------|--------|----------|-------------|----------|--------|---------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14   | 29/13  | 28/12        | 27/11        | 26/10        | 25/9      | 24/8   | 23/7    | 22/6   | 21/5   | 20/4     | 19/3        | 18/2     | 17/1   | 16/0    | All Resets |

| 5800                        | SPI1CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:0 | )>     | MCLKSEL | —      |        |          |             | _        | SPIFE  | ENHBUF  | 0000       |

| 3800                        | SFILCON                         | 15:0      | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | EL<1:0>  | SRXISE | EL<1:0> | 0000       |

| 5910                        | SPI1STAT                        | 31:16     | _             | _       | _      |              | RXE          | BUFELM<4:    | 0>        |        |         | _      |        |          | TXI         | BUFELM<4 | :0>    |         | 0000       |

| 5610                        | SFIISTAI                        | 15:0      | _             | _       | _      | FRMERR       | SPIBUSY      | _            | _         | SPITUR | SRMT    | SPIROV | SPIRBE |          | SPITBE      | _        | SPITBF | SPIRBF  | 19EB       |

| 5820                        | SPI1BUF                         | 31:16     | DATA<31:0>    |         |        |              |              |              |           |        |         | 0000   |        |          |             |          |        |         |            |

| 5620                        |                                 | 15:0      |               |         |        |              |              |              |           | DAIA   | 51.02   |        |        |          |             |          |        |         | 0000       |

| 5830                        | SPI1BRG                         | 31:16     | _             | —       | —      |              | —            | —            | —         |        | —       | —      | —      | —        | —           | —        | —      | —       | 0000       |

| 5650                        |                                 | 15:0      | —             | —       | —      | _            | —            | —            | _         |        |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16     | —             | —       | —      | _            | —            | —            | _         | _      | _       | —      | —      | _        | —           | —        | —      | -       | 0000       |

| 5840                        | SPI1CON2                        | 15:0      | SPI<br>SGNEXT | -       | —      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | —      | —      | —        | AUD<br>MONO | —        | AUDMC  | )D<1:0> | 0000       |

| 5400                        | SPI2CON                         | 31:16     | FRMEN         | FRMSYNC | FRMPOL | MSSEN        | FRMSYPW      | FF           | RMCNT<2:0 | )>     | MCLKSEL | _      | _      | —        | _           | _        | SPIFE  | ENHBUF  | 0000       |

| 5A00                        | SPIZCON                         | 15:0      | ON            | _       | SIDL   | DISSDO       | MODE32       | MODE16       | SMP       | CKE    | SSEN    | CKP    | MSTEN  | DISSDI   | STXISE      | EL<1:0>  | SRXISE | EL<1:0> | 0000       |

| 5440                        | SPI2STAT                        | 31:16     | —             | —       | _      |              | RXE          | BUFELM<4:    | 0>        |        |         | _      |        |          | TXI         | BUFELM<4 | :0>    |         | 0000       |

| SATU                        | 3F1231AI                        | 15:0      | _             |         | —      | FRMERR       | SPIBUSY      | _            | _         | SPITUR | SRMT    | SPIROV | SPIRBE | _        | SPITBE      | _        | SPITBF | SPIRBF  | 19EB       |

| 5A20                        | SPI2BUF                         | 31:16     |               |         |        |              |              |              |           | DATA<  | 31.05   |        |        |          |             |          |        |         | 0000       |

| 5A20                        | 3FI2D0I                         | 15:0      |               |         |        |              |              |              |           | DAIAS  | 51.02   |        |        |          |             |          |        |         | 0000       |

| 5A30                        | SPI2BRG                         | 31:16     | —             | —       | —      | _            | —            | —            | _         | _      | _       | —      | -      | _        | —           | —        | —      | -       | 0000       |

| 5A30                        |                                 | 15:0      | _             | —       | -      |              | _            | _            | _         |        |         |        |        | BRG<8:0> |             |          |        |         | 0000       |

|                             |                                 | 31:16     | _             | —       | —      | _            | —            | —            | _         | _      | _       | —      | —      | —        | _           | —        | —      | —       | 0000       |

| 5A40                        | SPI2CON2                        | 15:0      | SPI<br>SGNEXT | _       | _      | FRM<br>ERREN | SPI<br>ROVEN | SPI<br>TUREN | IGNROV    | IGNTUR | AUDEN   | _      | _      |          | AUD<br>MONO | _        | AUDMC  | )D<1:0> | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table except SPIxBUF have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# 20.2 Timing Diagrams

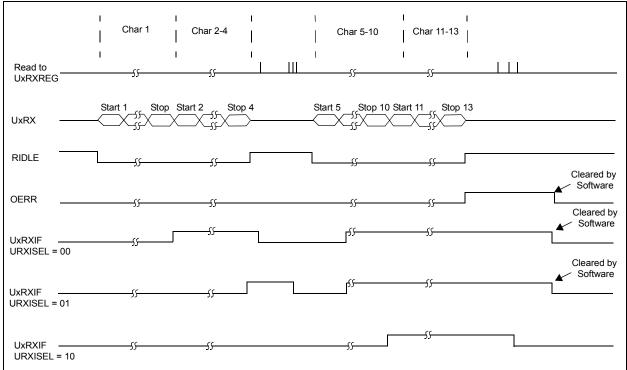

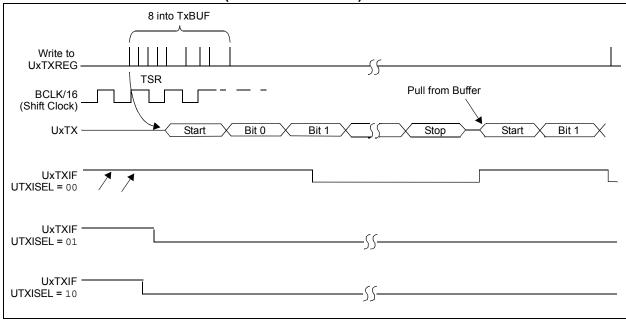

Figure 20-2 and Figure 20-3 illustrate typical receive and transmit timing for the UART module.

# FIGURE 20-2: UART RECEPTION

### FIGURE 20-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

# PIC32MX330/350/370/430/450/470

### REGISTER 23-3: AD1CON3: ADC CONTROL REGISTER 3

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5        | Bit<br>28/20/12/4        | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|--------------------------|--------------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0                      | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | _                        | —                        | —                 | —                 | —                | —                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0                      | U-0                      | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | _                 | —                 | _                        | _                        | _                 | —                 | _                | _                |  |  |  |  |

| 45.0         | R/W-0             | U-0               | U-0                      | R/W-0                    | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | ADRC              | —                 | _                        | SAMC<4:0> <sup>(1)</sup> |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0                    | R/W-0                    | R/W-0             | R/W-0             | R/W              | R/W-0            |  |  |  |  |

| 7:0          |                   |                   | ADCS<7:0> <sup>(2)</sup> |                          |                   |                   |                  |                  |  |  |  |  |

# Legend:

| =ogona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ADRC:** ADC Conversion Clock Source bit

- 1 = Clock derived from FRC

- 0 = Clock derived from Peripheral Bus Clock (PBCLK)

- bit 14-13 Unimplemented: Read as '0'

- - 00000001 =TPB • 2 • (ADCS<7:0> + 1) = 4 • TPB = TAD 00000000 =TPB • 2 • (ADCS<7:0> + 1) = 2 • TPB = TAD

- **Note 1:** This bit is only used if the SSRC<2:0> bits (AD1CON1<7:5>) = 111.

- 2: This bit is not used if the ADRC bit (AD1CON3<15>) = 1.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4   | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------------|------------------|

| 31:24        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

|              | EDG1MOD           | EDG1POL           |                   | EDG1S               | EDG2STAT          | EDG1STAT          |                        |                  |

| 23:16        | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | U-0                    | U-0              |

| 23.10        | EDG2MOD           | EDG2POL           |                   | EDG2S               | _                 | _                 |                        |                  |

| 15:0         | R/W-0             | U-0               | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 15:8         | ON                | —                 | CTMUSIDL          | TGEN <sup>(1)</sup> | EDGEN             | EDGSEQEN          | IDISSEN <sup>(2)</sup> | CTTRIG           |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0                  | R/W-0            |

| 7:0          |                   |                   | IRNG              | <1:0>               |                   |                   |                        |                  |

### REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER

### Legend:

| 3                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31 EDG1MOD: Edge 1 Edge Sampling Select bit

1 = Input is edge-sensitive

0 = Input is level-sensitive

bit 30 EDG1POL: Edge 1 Polarity Select bit

1 = Edge 1 programmed for a positive edge response

0 = Edge 1 programmed for a negative edge response

### bit 29-26 EDG1SEL<3:0>: Edge 1 Source Select bits

### 1111 = Reserved

1110 = C2OUT pin is selected

- 1101 = C1OUT pin is selected

- 1100 = IC3 Capture Event is selected

- 1011 = IC2 Capture Event is selected

- 1010 = IC1 Capture Event is selected

- 1001 = CTED8 pin is selected

- 1000 = CTED7 pin is selected

- 0111 = CTED6 pin is selected

- 0110 = CTED5 pin is selected

- 0101 = CTED4 pin is selected

- 0100 = CTED3 pin is selected

- 0011 = CTED1 pin is selected

- 0010 = CTED2 pin is selected

- 0001 = OC1 Compare Event is selected

# 0000 = Timer1 Event is selected

# bit 25 EDG2STAT: Edge 2 Status bit

Indicates the status of Edge 2 and can be written to control edge source

- 1 = Edge 2 has occurred

- 0 = Edge 2 has not occurred

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-42) in Section 31.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

# REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

| REGIST    | ER 26-1: CIMUCON: CIMU CONTROL REGISTER (CONTINUE                                                                      |

|-----------|------------------------------------------------------------------------------------------------------------------------|

| bit 24    | EDG1STAT: Edge 1 Status bit                                                                                            |

|           | Indicates the status of Edge 1 and can be written to control edge source                                               |

|           | 1 = Edge 1 has occurred                                                                                                |

|           | 0 = Edge 1 has not occurred                                                                                            |

| bit 23    | EDG2MOD: Edge 2 Edge Sampling Select bit                                                                               |

|           | 1 = Input is edge-sensitive                                                                                            |

|           | 0 = Input is level-sensitive                                                                                           |

| bit 22    | EDG2POL: Edge 2 Polarity Select bit                                                                                    |

|           | 1 = Edge 2 programmed for a positive edge response                                                                     |

|           | 0 = Edge 2 programmed for a negative edge response                                                                     |

| bit 21-18 | EDG2SEL<3:0>: Edge 2 Source Select bits                                                                                |

|           | 1111 = Reserved                                                                                                        |

|           | 1110 = C2OUT pin is selected<br>1101 = C1OUT pin is selected                                                           |

|           | 1100 = PBCLK clock is selected                                                                                         |

|           | 1011 = IC3 Capture Event is selected                                                                                   |

|           | 1010 = IC2 Capture Event is selected                                                                                   |

|           | 1001 = IC1 Capture Event is selected                                                                                   |

|           | 1000 = CTED13 pin is selected                                                                                          |

|           | 0111 = CTED12 pin is selected<br>0110 = CTED11 pin is selected                                                         |

|           | 0101 = CTED10 pin is selected                                                                                          |

|           | 0100 = CTED9 pin is selected                                                                                           |

|           | 0011 = CTED1 pin is selected                                                                                           |

|           | 0010 = CTED2 pin is selected                                                                                           |

|           | 0001 = OC1 Compare Event is selected                                                                                   |

|           | 0000 = Timer1 Event is selected                                                                                        |

|           | Unimplemented: Read as '0'                                                                                             |

| bit 15    | ON: ON Enable bit                                                                                                      |

|           | 1 = Module is enabled                                                                                                  |

|           | 0 = Module is disabled                                                                                                 |

| bit 14    | Unimplemented: Read as '0'                                                                                             |

| bit 13    | CTMUSIDL: Stop in Idle Mode bit                                                                                        |

|           | 1 = Discontinue module operation when device enters Idle mode                                                          |

| bit 12    | <ul> <li>0 = Continue module operation in Idle mode</li> <li>TGEN: Time Generation Enable bit<sup>(1)</sup></li> </ul> |

| DIL 12    |                                                                                                                        |

|           | <ul><li>1 = Enables edge delay generation</li><li>0 = Disables edge delay generation</li></ul>                         |

| bit 11    | EDGEN: Edge Enable bit                                                                                                 |

|           | 1 = Edges are not blocked                                                                                              |

|           | 1 = Edges are hot blocked0 = Edges are blocked                                                                         |

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-42) in Section 31.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

| Bit<br>31/23/15/7           | Bit<br>30/22/14/6         | Bit<br>29/21/13/5                                                                                                     | Bit<br>28/20/12/4                                                                                                                                                                | Bit<br>27/19/11/3                                                                                                                                                                                                                                                                                                                                                               | Bit<br>26/18/10/2                                                                                                                                                                                            | Bit<br>25/17/9/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit<br>24/16/8/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|-----------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R                           | R                         | R                                                                                                                     | R                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                            | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

|                             | VER<                      | :3:0> <sup>(1)</sup>                                                                                                  |                                                                                                                                                                                  | DEVID<27:24> <sup>(1)</sup>                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| R                           | R                         | R                                                                                                                     | R                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                            | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| DEVID<23:16> <sup>(1)</sup> |                           |                                                                                                                       |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| R                           | R                         | R                                                                                                                     | R                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                            | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| DEVID<15:8> <sup>(1)</sup>  |                           |                                                                                                                       |                                                                                                                                                                                  |                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| R                           | R                         | R                                                                                                                     | R                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                            | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |