Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

# Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                           |

|----------------------------|----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 120MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 81                                                                               |

| Program Memory Size        | 256КВ (256К х 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 28x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                    |

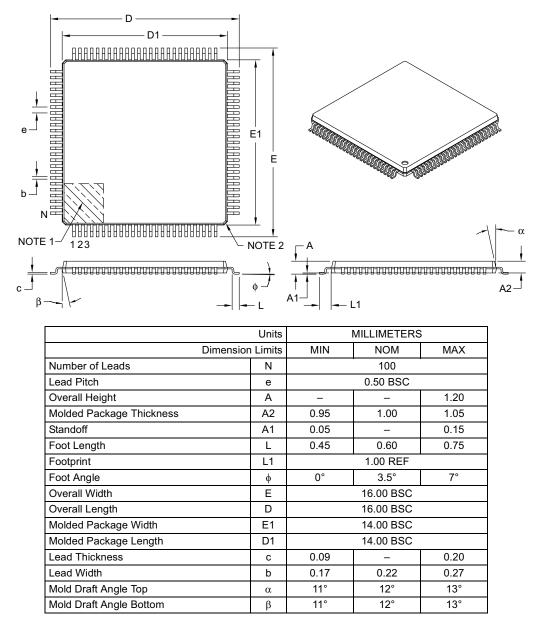

| Package / Case             | 100-TQFP                                                                         |

| Supplier Device Package    | 100-TQFP (14x14)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256l-120-pf |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | —                    | —                     | —                      | —                 | —                | _                |

| 22.16        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | -                    | —                     | —                      | —                 |                  | _                |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> | —                 | —                | _                |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | —                 | —                 |                      | —                     | NVMOP<3:0>             |                   |                  |                  |

# REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

# bit 31-16 Unimplemented: Read as '0'

| bit 15   | WR: Write Control bit                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------|

|          | This bit is writable when WREN = 1 and the unlock sequence is followed.                                             |

|          | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                               |

|          | 0 = Flash operation complete or inactive                                                                            |

| bit 14   | WREN: Write Enable bit                                                                                              |

|          | 1 = Enable writes to WR bit and enables LVD circuit                                                                 |

|          | 0 = Disable writes to WR bit and disables LVD circuit                                                               |

|          | This is the only bit in this register reset by a device Reset.                                                      |

| bit 13   | WRERR: Write Error bit <sup>(1)</sup>                                                                               |

|          | This bit is read-only and is automatically set by hardware.                                                         |

|          | 1 = Program or erase sequence did not complete successfully                                                         |

|          | 0 = Program or erase sequence completed normally                                                                    |

| bit 12   | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                   |

|          | This bit is read-only and is automatically set by hardware.                                                         |

|          | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                |

|          | 0 = Voltage level is acceptable for programming                                                                     |

| bit 11   | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                 |

|          | This bit is read-only and is automatically set, and cleared, by hardware.                                           |

|          | 1 = Low-voltage event active                                                                                        |

|          | 0 = Low-voltage event NOT active                                                                                    |

| bit 10-4 | Unimplemented: Read as '0'                                                                                          |

| bit 3-0  | NVMOP<3:0>: NVM Operation bits                                                                                      |

|          | These bits are writable when WREN = 0.                                                                              |

|          | 1111 = Reserved                                                                                                     |

|          | •                                                                                                                   |

|          |                                                                                                                     |

|          | 0111 = Reserved                                                                                                     |

|          | 0110 = No operation                                                                                                 |

|          | 0101 = Program Flash (PFM) erase operation: erases PFM, if all pages are not write-protected                        |

|          | 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected                          |

|          | 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected<br>0010 = No operation |

|          | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected                      |

|          | 0000 = No operation                                                                                                 |

|          |                                                                                                                     |

|          |                                                                                                                     |

**Note 1:** This bit is cleared by setting NVMOP = 0000, and initiating a Flash operation (i.e., WR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 31:24        | DCRCDATA<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | DCRCDATA<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | DCRCDATA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | DCRCDA            | TA<7:0>           |                   |                  |                  |  |  |

# REGISTER 10-5: DCRCDATA: DMA CRC DATA REGISTER

# Legend:

| Legena:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

# bit 31-0 DCRCDATA<31:0>: CRC Data Register bits

Writing to this register will seed the CRC generator. Reading from this register will return the current value of the CRC. Bits greater than PLEN will return '0' on any read.

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): Only the lower 16 bits contain IP header checksum information. The upper 16 bits are always '0'. Data written to this register is converted and read back in 1's complement form (i.e., current IP header checksum value).

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Bits greater than PLEN will return '0' on any read.

# REGISTER 10-6: DCRCXOR: DMA CRCXOR ENABLE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        |                   | DCRCXOR<31:24>    |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | DCRCXOR<23:16>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | DCRCXOR<15:8>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          |                   | DCRCXOR<7:0>      |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

### bit 31-0 DCRCXOR<31:0>: CRC XOR Register bits

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): This register is unused.

When CRCTYP (DCRCCON<15>) = 0 (CRC module is in LFSR mode):

- 1 = Enable the XOR input to the Shift register

- 0 = Disable the XOR input to the Shift register; data is shifted in directly from the previous stage in the register

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                     | —                 | _                 | _                 |                   | _                 | -                | —                     |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                   | —                 | _                 | -                 | _                 | —                 | _                | —                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | —                 | _                 | _                 | _                 | _                 | _                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | CHPF             | RI<1:0>               |

# REGISTER 10-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | e bit W = Writable bit |                      | read as '0'        |

|-------------------|------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set       | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14-9 Unimplemented: Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

# bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 = Channel is disabled

# bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

0 = Channel is disabled on block transfer complete

# bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

- bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                              | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------|------------------|

| 21.24        | U-0                                           | U-0              |

| 31:24        |                   | —                 | —                 | —                 |                   | —                 | —                                             | —                |

| 23:16        | U-0                                           | U-0              |

| 23.10        |                   |                   | _                 | _                 | _                 | _                 | _                                             | —                |

| 15:8         | U-0                                           | U-0              |

| 10.0         | _                 | _                 | _                 | _                 |                   | _                 | _                                             | —                |

|              | R/W-0                                         | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup><br>EOFEE <sup>(2)</sup> | PIDEE            |

# REGISTER 11-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | <b>BTSEE:</b> Bit Stuff Error Interrupt Enable bit |

|-------|----------------------------------------------------|

|       |                                                    |

- 1 = BTSEF interrupt is enabled

- 0 = BTSEF interrupt is disabled

- bit 6 BMXEE: Bus Matrix Error Interrupt Enable bit

- 1 = BMXEF interrupt is enabled

- 0 = BMXEF interrupt is disabled

- bit 5 **DMAEE:** DMA Error Interrupt Enable bit

- 1 = DMAEF interrupt is enabled

- 0 = DMAEF interrupt is disabled

- bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

- 1 = BTOEF interrupt is enabled

- 0 = BTOEF interrupt is disabled

- bit 3 **DFN8EE:** Data Field Size Error Interrupt Enable bit

- 1 = DFN8EF interrupt is enabled

- 0 = DFN8EF interrupt is disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

# Note 1: Device mode.

2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

# TABLE 12-1: INPUT PIN SELECTION

| Peripheral Pin | [pin name]R SFR       | [pin name]R bits | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection                                      |

|----------------|-----------------------|------------------|-----------------------------------------------------------------------------------------|

| INT3           | INT3R                 | INT3R<3:0>       | 0000 = RPD2<br>0001 = RPG8                                                              |

| T2CK           | T2CKR                 | T2CKR<3:0>       | 0010 = RPF4<br>0011 = RPD10                                                             |

| IC3            | IC3R                  | IC3R<3:0>        | 0100 = RPF1<br>0101 = RPB9                                                              |

| U1RX           | U1RXR                 | U1RXR<3:0>       |                                                                                         |

| U2RX           | U2RXR                 | U2RXR<3:0>       | 1000 - RFB3<br>1001 = Reserved<br>1010 = RPC1 <sup>(3)</sup>                            |

| U5CTS          | U5CTSR <sup>(3)</sup> | U5CTSR<3:0>      | $\frac{1011}{1011} = \text{RPD14(3)}$<br>1100 = RPG1(3)                                 |

| REFCLKI        | REFCLKIR              | REFCLKIR<3:0>    | 1101 = RPA14 <sup>(3)</sup><br>1110 = Reserved<br>1111 = RPF2 <sup>(1)</sup>            |

| INT4           | INT4R                 | INT4R<3:0>       | 0000 = RPD3<br>0001 = RPG7                                                              |

| T5CK           | T5CKR                 | T5CKR<3:0>       | 0010 = RPF5<br>0011 = RPD11                                                             |

| IC4            | IC4R                  | IC4R<3:0>        | 0100 = RPF0<br>0101 = RPB1                                                              |

| U3RX           | U3RXR                 | U3RXR<3:0>       |                                                                                         |

| U4CTS          | U4CTSR                | U4CTSR<3:0>      | 1000 = Ri B3<br>1001 = Reserved<br>1010 = RPC4 <sup>(3)</sup>                           |

| SDI1           | SDI1R                 | SDI1R<3:0>       | 1011 = RPD15 <sup>(3)</sup><br>1100 = RPG0 <sup>(3)</sup>                               |

| SDI2           | SDI2R                 | SDI2R<3:0>       | 1101 = RPA15 <sup>(3)</sup><br>1110 = RPF2 <sup>(1)</sup><br>1111 = RPF7 <sup>(2)</sup> |

| INT2           | INT2R                 | INT2R<3:0>       | 0000 = RPD9<br>0001 = RPG6                                                              |

| T4CK           | T4CKR                 | T4CKR<3:0>       | 0010 = RPB8<br>0011 = RPB15                                                             |

| IC2            | IC2R                  | IC2R<3:0>        | 0100 = RPD4<br>0101 = RPB0                                                              |

| IC5            | IC5R                  | IC5R<3:0>        |                                                                                         |

| U1CTS          | U1CTSR                | U1CTSR<3:0>      | 1000 = Reserved<br>1001 = RPF12 <sup>(3)</sup><br>1010 = RPD12 <sup>(3)</sup>           |

| U2CTS          | U2CTSR                | U2CTSR<3:0>      | 1011 = RPF8 <sup>(3)</sup><br>1100 = RPC3 <sup>(3)</sup>                                |

| SS1            | SS1R                  | SS1R<3:0>        | 1101 = RPE9 <sup>(3)</sup><br>1110 = Reserved                                           |

|                |                       |                  | 1111 <b>= RPB2</b>                                                                      |

**Note 1:** This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

3: This selection is not available on 64-pin USB and General Purpose devices.

4: This selection is only available on General Purpose devices.

|                             | PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, PIC32MX470F512L DEVICES ONLY |               |       |       |       |       |       |       |              |              |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------------------------------------------------------|---------------|-------|-------|-------|-------|-------|-------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| sse                         |                                                                                 |               | Bits  |       |       |       |       |       |              |              |              |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup>                                                 | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6400                        | ANSELE                                                                          | 31:16         | _     | _     | _     | —     | _     | _     | —            | —            | —            | —            | —            | —            | -            | —            | -            | _            | 0000          |

|                             |                                                                                 | 15:0          | _     | —     | —     | —     | —     | —     | —            | —            | ANSELE7      | ANSELE6      | ANSELE5      | ANSELE4      | _            | ANSELE2      | _            | —            | 00F4          |

| 6410                        | TRISE                                                                           | 31:16         | —     | —     | —     | —     | —     | —     | —            |              | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                                                                 | 15:0          | —     | —     | —     | —     | _     | _     | TRISE9       | TRISE8       | TRISE7       | TRISE6       | TRISE5       | TRISE4       | TRISE3       | TRISE2       | TRISE1       | TRISE0       | XXXX          |

| 6420                        | 20 PORTE                                                                        | 31:16         | —     | —     | —     | —     | _     | _     | _            | _            | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

|                             |                                                                                 | 15:0          | —     | —     | _     | _     | _     | _     | RE9          | RE8          | RE7          | RE6          | RE5          | RE4          | RE3          | RE2          | RE1          | RE0          | XXXX          |

| 6440                        | ) LATE                                                                          | 31:16         | —     | —     | _     | _     | _     | _     | —            | -            |              | —            | —            | —            | —            | -            | —            | —            | 0000          |

|                             |                                                                                 | 15:0          | —     |       |       |       | _     |       | LATE9        | LATE8        | LATE7        | LATE6        | LATE5        | LATE4        | LATE3        | LATE2        | LATE1        | LATE0        | XXXX          |

| 6440                        | ODCE                                                                            | 31:16         |       |       |       | —     | _     |       | -            | -            | -            | -            | -            | -            | -            | -            | -            | -            | 0000          |

|                             |                                                                                 | 15:0          |       |       |       | —     | _     |       | ODCE9        | ODCE8        | ODCE7        | ODCE6        | ODCE5        | ODCE4        | ODCE3        | ODCE2        | ODCE1        | ODCE0        | XXXX          |

| 6450                        | CNPUE                                                                           | 31:16         |       |       | —     | _     | _     |       |              |              |              |              |              |              |              |              |              |              | 0000          |

|                             |                                                                                 | 15:0          |       | _     | —     | _     | _     |       | CNPUE9       | CNPUE8       | CNPUE7       | CNPUE6       | CNPUE5       | CNPUE4       | CNPDE3       | CNPUE2       | CNPUE1       | CNPUE0       |               |

| 6460                        | CNPDE                                                                           | 31:16<br>15:0 |       |       |       | —     | _     | —     | —<br>CNPDE9  |              | —<br>CNPDE7  | —<br>CNPDE6  | —<br>CNPDE5  | —<br>CNPDE4  | —<br>CNPDE3  | —<br>CNPDE2  |              |              | 0000          |

|                             |                                                                                 | 31:16         |       | —     | —     | —     | _     | _     |              |              | -            |              |              | -            |              | -            |              |              |               |

| 6470                        | CNCONE                                                                          | 15:0          | ON    | _     |       |       | _     | _     | _            |              |              |              |              |              | _            | _            |              |              | 0000          |

|                             |                                                                                 | 31:16         |       |       | -     |       |       |       | —            |              |              |              |              |              |              |              |              |              | 0000          |

| 6480                        | CNENE                                                                           | 15:0          |       |       |       |       | _     |       |              | CNIEE8       | CNIEE7       | CNIEE6       | CNIEE5       | CNIEE4       | CNIEE3       | CNIEE2       | CNIEE1       | CNIEE0       | xxxx          |

|                             |                                                                                 | 31:16         | _     |       | _     |       |       |       |              |              |              |              |              |              |              |              |              |              | 0000          |

| 6490                        | CNSTATE                                                                         | 15:0          | _     | _     | _     | _     | -     | _     | CN<br>STATE9 | CN<br>STATE8 | CN<br>STATE7 | CN<br>STATE6 | CN<br>STATE5 | CN<br>STATE4 | CN<br>STATE3 | CN<br>STATE2 | CN<br>STATE1 | CN<br>STATE0 | xxxx          |

# TABLE 12-9: PORTE REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                   | _                 | _                 | _                 | _                 | _                 | —                | _                |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                   | —                 | _                 | _                 | _                 | —                 | _                | _                |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1,2)</sup> | —                 | _                 | _                 | —                 | _                 | —                | —                |

| 7.0          | U-0                 | R-y               | R-y               | R-y               | R-y               | R-y               | R/W-0            | R/W-0            |

| 7:0          |                     |                   | S                 | WDTWINEN          | WDTCLR            |                   |                  |                  |

# REGISTER 15-1: WDTCON: WATCHDOG TIMER CONTROL REGISTER

| Legend:           | y = Values set from Configuration bits on POR |                          |                    |  |  |  |

|-------------------|-----------------------------------------------|--------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                              | U = Unimplemented bit, I | read as '0'        |  |  |  |

| -n = Value at POR | '1' = Bit is set                              | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |

# bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Watchdog Timer Enable bit<sup>(1,2)</sup>

- 1 = Enables the WDT if it is not enabled by the device configuration

- 0 = Disable the WDT if it was enabled in software

- bit 14-7 Unimplemented: Read as '0'

- bit 6-2 **SWDTPS<4:0>:** Shadow Copy of Watchdog Timer Postscaler Value from Device Configuration bits On reset, these bits are set to the values of the WDTPS <4:0> of Configuration bits.

- bit 1 WDTWINEN: Watchdog Timer Window Enable bit

- 1 = Enable windowed Watchdog Timer

- 0 = Disable windowed Watchdog Timer

- bit 0 WDTCLR: Watchdog Timer Reset bit

- 1 = Writing a '1' will clear the WDT

- 0 = Software cannot force this bit to a '0'

- **Note 1:** A read of this bit results in a '1' if the Watchdog Timer is enabled by the device configuration or software.

- 2: When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# REGISTER 16-1: ICXCON: INPUT CAPTURE 'X' CONTROL REGISTER (CONTINUED)

- bit 2-0 ICM<2:0>: Input Capture Mode Select bits

- 111 = Interrupt-Only mode (only supported while in Sleep mode or Idle mode)

- 110 = Simple Capture Event mode every edge, specified edge first and every edge thereafter

- 101 = Prescaled Capture Event mode every sixteenth rising edge

- 100 = Prescaled Capture Event mode every fourth rising edge

- 011 = Simple Capture Event mode every rising edge

- 010 = Simple Capture Event mode every falling edge

- 001 = Edge Detect mode every edge (rising and falling)

- 000 = Input Capture module is disabled

- **Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7      | Bit<br>30/22/14/6  | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |  |  |

|--------------|------------------------|--------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|--|--|

| 21.24        | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 31:24        | FRMEN                  | FRMSYNC            | FRMPOL            | MSSEN             | FRMSYPW           | F                 | FRMCNT<2:0>      |                       |  |  |

| 00.40        | R/W-0                  | U-0                | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0                 |  |  |

| 23:16        | MCLKSEL <sup>(2)</sup> | —                  | —                 | —                 | —                 | —                 | SPIFE            | ENHBUF <sup>(2)</sup> |  |  |

| 45.0         | R/W-0                  | U-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 15:8         | ON <sup>(1)</sup>      | —                  | SIDL              | DISSDO            | MODE32            | MODE16            | SMP              | CKE <sup>(3)</sup>    |  |  |

| 7.0          | R/W-0                  | R/W-0              | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0                 |  |  |

| 7:0          | SSEN                   | CKP <sup>(4)</sup> | MSTEN             | DISSDI            | STXISE            | L<1:0>            | SRXIS            | EL<1:0>               |  |  |

# REGISTER 18-1: SPIxCON: SPI CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31 FRMEN: Framed SPI Support bit

- 1 = Framed SPI support is enabled (SSx pin used as FSYNC input/output)

0 = Framed SPI support is disabled

- bit 30 **FRMSYNC:** Frame Sync Pulse Direction Control on <u>SSx</u> pin bit (Framed SPI mode only)

- 1 = Frame sync pulse input (Slave mode)

- 0 = Frame sync pulse output (Master mode)

- bit 29 **FRMPOL:** Frame Sync Polarity bit (Framed SPI mode only)

- 1 = Frame pulse is active-high

- 0 = Frame pulse is active-low

- bit 28 **MSSEN:** Master Mode Slave Select Enable bit

- 1 = Slave select SPI support enabled. The SS pin is automatically driven during transmission in Master mode. Polarity is determined by the FRMPOL bit.

- 0 = Slave select SPI support is disabled.

- bit 27 FRMSYPW: Frame Sync Pulse Width bit

- 1 = Frame sync pulse is one character wide

- 0 = Frame sync pulse is one clock wide

- bit 26-24 **FRMCNT<2:0>:** Frame Sync Pulse Counter bits. Controls the number of data characters transmitted per pulse. This bit is only valid in FRAMED\_SYNC mode.

- 111 = Reserved; do not use

- 110 = Reserved; do not use

- 101 = Generate a frame sync pulse on every 32 data characters

- 100 = Generate a frame sync pulse on every 16 data characters

- 011 = Generate a frame sync pulse on every 8 data characters

- 010 = Generate a frame sync pulse on every 4 data characters

- 001 = Generate a frame sync pulse on every 2 data characters

- 000 = Generate a frame sync pulse on every data character

- bit 23 MCLKSEL: Master Clock Enable bit<sup>(2)</sup>

- 1 = REFCLK is used by the Baud Rate Generator

- 0 = PBCLK is used by the Baud Rate Generator

- bit 22-18 Unimplemented: Read as '0'

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

| REGIST    | ER 18-1:                                                                                                                                   | SPIxCON: S                          | SPI CONTROL REGISTER (CONTINUED)                                                                                                                               |  |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| bit 17    |                                                                                                                                            |                                     | e Edge Select bit (Framed SPI mode only)                                                                                                                       |  |  |  |  |  |  |

|           |                                                                                                                                            |                                     | on pulse coincides with the first bit clock                                                                                                                    |  |  |  |  |  |  |

| h:+ 40    | <ul> <li>0 = Frame synchronization pulse precedes the first bit clock</li> <li>ENHBUF: Enhanced Buffer Enable bit<sup>(2)</sup></li> </ul> |                                     |                                                                                                                                                                |  |  |  |  |  |  |

| bit 16    |                                                                                                                                            | ed Buffer mo                        |                                                                                                                                                                |  |  |  |  |  |  |

|           |                                                                                                                                            | ed Buffer mod                       |                                                                                                                                                                |  |  |  |  |  |  |

| bit 15    |                                                                                                                                            | ripheral On bi                      |                                                                                                                                                                |  |  |  |  |  |  |

|           |                                                                                                                                            | ripheral is ena                     |                                                                                                                                                                |  |  |  |  |  |  |

|           |                                                                                                                                            | ripheral is dis                     |                                                                                                                                                                |  |  |  |  |  |  |

| bit 14    | Unimpleme                                                                                                                                  | ented: Read a                       | as '0'                                                                                                                                                         |  |  |  |  |  |  |

| bit 13    | SIDL: Stop                                                                                                                                 | in Idle Mode b                      | pit                                                                                                                                                            |  |  |  |  |  |  |

|           |                                                                                                                                            | •                                   | n when CPU enters in Idle mode                                                                                                                                 |  |  |  |  |  |  |

|           |                                                                                                                                            | ue operation i                      |                                                                                                                                                                |  |  |  |  |  |  |

| bit 12    |                                                                                                                                            | isable SDOx                         |                                                                                                                                                                |  |  |  |  |  |  |

|           |                                                                                                                                            |                                     | d by the module. Pin is controlled by associated PORT register<br>ed by the module                                                                             |  |  |  |  |  |  |

| bit 11-10 |                                                                                                                                            |                                     | t Communication Select bits                                                                                                                                    |  |  |  |  |  |  |

|           | When AUD                                                                                                                                   |                                     | Communication Select bits                                                                                                                                      |  |  |  |  |  |  |

|           | MODE32                                                                                                                                     | MODE16                              | Communication                                                                                                                                                  |  |  |  |  |  |  |

|           | 1                                                                                                                                          | 1                                   | 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                          |  |  |  |  |  |  |

|           | 1                                                                                                                                          | 0                                   | 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                          |  |  |  |  |  |  |

|           | 0                                                                                                                                          | 1                                   | 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                          |  |  |  |  |  |  |

|           | 0                                                                                                                                          | 0                                   | 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                                                                                          |  |  |  |  |  |  |

|           | When AUD                                                                                                                                   | <b>FN =</b> 0:                      |                                                                                                                                                                |  |  |  |  |  |  |

|           | MODE32                                                                                                                                     | MODE16                              | Communication                                                                                                                                                  |  |  |  |  |  |  |

|           | 1                                                                                                                                          | x                                   | 32-bit                                                                                                                                                         |  |  |  |  |  |  |

|           | 0                                                                                                                                          | 1                                   | 16-bit                                                                                                                                                         |  |  |  |  |  |  |

|           | 0                                                                                                                                          | 0                                   | 8-bit                                                                                                                                                          |  |  |  |  |  |  |

| bit 9     |                                                                                                                                            |                                     | nple Phase bit                                                                                                                                                 |  |  |  |  |  |  |

|           |                                                                                                                                            | <u>le (MSTEN =</u><br>ata sampled a | $\pm$ ).<br>at end of data output time                                                                                                                         |  |  |  |  |  |  |

|           |                                                                                                                                            |                                     | at middle of data output time                                                                                                                                  |  |  |  |  |  |  |

|           |                                                                                                                                            | • (MSTEN = 0                        |                                                                                                                                                                |  |  |  |  |  |  |

|           |                                                                                                                                            | -                                   | en SPI is used in Slave mode. The module always uses SMP = 0.                                                                                                  |  |  |  |  |  |  |

| bit 8     |                                                                                                                                            | lock Edge Se                        |                                                                                                                                                                |  |  |  |  |  |  |

|           |                                                                                                                                            |                                     | anges on transition from active clock state to Idle clock state (see CKP bit)<br>anges on transition from Idle clock state to active clock state (see CKP bit) |  |  |  |  |  |  |

| bit 7     |                                                                                                                                            | -                                   | ble (Slave mode) bit                                                                                                                                           |  |  |  |  |  |  |

|           |                                                                                                                                            | n used for Sla                      |                                                                                                                                                                |  |  |  |  |  |  |

|           |                                                                                                                                            |                                     | Slave mode, pin controlled by port function.                                                                                                                   |  |  |  |  |  |  |

| bit 6     |                                                                                                                                            | Polarity Sele                       |                                                                                                                                                                |  |  |  |  |  |  |

|           | 1 = Idle sta                                                                                                                               | te for clock is                     | a high level; active state is a low level                                                                                                                      |  |  |  |  |  |  |

|           |                                                                                                                                            |                                     | a low level; active state is a high level                                                                                                                      |  |  |  |  |  |  |

| bit 5     |                                                                                                                                            | aster Mode Er                       | hable bit                                                                                                                                                      |  |  |  |  |  |  |

|           | 1 = Master<br>0 = Slave r                                                                                                                  |                                     |                                                                                                                                                                |  |  |  |  |  |  |

|           |                                                                                                                                            | lieue                               |                                                                                                                                                                |  |  |  |  |  |  |

| Note 1:   | When using                                                                                                                                 | g the 1:1 PBC                       | LK divisor, the user software should not read or write the peripheral's SFRs in the                                                                            |  |  |  |  |  |  |

|           |                                                                                                                                            | -                                   | ely following the instruction that clears the module's ON bit.                                                                                                 |  |  |  |  |  |  |

| 2:        | This bit car                                                                                                                               | n only be writte                    | en when the ON bit = 0.                                                                                                                                        |  |  |  |  |  |  |

| 3:        | This bit is r<br>mode (FRN                                                                                                                 |                                     | e Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                  |  |  |  |  |  |  |

| 4:        | -                                                                                                                                          | -                                   | PI module functions as if the CKP bit is equal to '1', regardless of the actual value                                                                          |  |  |  |  |  |  |

|           | of CKP.                                                                                                                                    | <u> </u>                            |                                                                                                                                                                |  |  |  |  |  |  |

|           |                                                                                                                                            |                                     |                                                                                                                                                                |  |  |  |  |  |  |

# PIC32MX330/350/370/430/450/470

# REGISTER 19-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | _                 | —                 | —                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | _                 | _                 | —                 | _                 | _                | _                |

| 15.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

| Legend:           | HC = Cleared in Hardwar | е                        |                    |

|-------------------|-------------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |

## bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

- 1 = Enables the  $I^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the  $I^2$ C module; all  $I^2$ C pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- **SCLREL:** SCLx Release Control bit (when operating as I<sup>2</sup>C slave)

- 1 = Release SCLx clock

bit 12

- 0 = Hold SCLx clock low (clock stretch)

- If STREN = 1:

Bit is R/W (i.e., software can write '0' to initiate stretch and write '1' to release clock). Hardware clear at beginning of slave transmission. Hardware clear at end of slave reception.

# If STREN = 0:

Bit is R/S (i.e., software can only write '1' to release clock). Hardware clear at beginning of slave transmission.

- bit 11 STRICT: Strict I<sup>2</sup>C Reserved Address Rule Enable bit

- 1 = Strict reserved addressing is enforced. Device does not respond to reserved address space or generate addresses in reserved address space.

- 0 = Strict I<sup>2</sup>C Reserved Address Rule is not enabled

#### bit 10 A10M: 10-bit Slave Address bit

- 1 = I2CxADD is a 10-bit slave address

- 0 = I2CxADD is a 7-bit slave address

- bit 9 **DISSLW:** Disable Slew Rate Control bit

- 1 = Slew rate control is disabled

- 0 = Slew rate control is enabled

- bit 8 SMEN: SMBus Input Levels bit

- 1 = Enable I/O pin thresholds compliant with SMBus specification

- 0 = Disable SMBus input thresholds

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>31/23/15/7           | Bit<br>30/22/14/6         | Bit<br>29/21/13/5                                                                                                     | Bit<br>28/20/12/4                                                                                                                                                                | Bit<br>27/19/11/3                                                                                                                                                                                                                                                                                                                                                               | Bit<br>26/18/10/2                                                                                                                                                                                            | Bit<br>25/17/9/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit<br>24/16/8/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |

|-----------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| R                           | R                         | R                                                                                                                     | R                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                            | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |