Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| 2 0 0 0 0 0                |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Obsolete                                                                         |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 120MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 85                                                                               |

| Program Memory Size        | 256KB (256K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                | -                                                                                |

| RAM Size                   | 64K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 28x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                 |

| Supplier Device Package    | 124-VTLA (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256l-120-tl |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|          |                        | Pin Numb          | er                 |             |                |                                   |  |  |  |  |  |  |

|----------|------------------------|-------------------|--------------------|-------------|----------------|-----------------------------------|--|--|--|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP   | 124-pin<br>VTLA    | Pin<br>Type | Buffer<br>Type | Description                       |  |  |  |  |  |  |

| RE0      | 60                     | 93                | B52                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RE1      | 61                     | 94                | A64                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RE2      | 62                     | 98                | A66                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RE3      | 63                     | 99                | B56                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RE4      | 64                     | 100               | A67                | I/O         | ST             | DODIE is a hidiractional I/O part |  |  |  |  |  |  |

| RE5      | 1                      | 3                 | B2                 | I/O         | ST             | PORTE is a bidirectional I/O port |  |  |  |  |  |  |

| RE6      | 2                      | 4                 | A4                 | I/O         | ST             |                                   |  |  |  |  |  |  |

| RE7      | 3                      | 5                 | B3                 | I/O         | ST             | 1                                 |  |  |  |  |  |  |

| RE8      | —                      | 18                | A11                | I/O         | ST             | -                                 |  |  |  |  |  |  |

| RE9      | —                      | 19                | B10                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RF0      | 58                     | 87                | B49                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RF1      | 59                     | 88                | A60                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RF2      | 34(1)                  | 52                | A36                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RF3      | 33                     | 51                | A35                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RF4      | 31                     | 49                | B27                | I/O         | ST             | ]                                 |  |  |  |  |  |  |

| RF5      | 32                     | 50                | A32                | I/O         | ST             | PORTF is a bidirectional I/O port |  |  |  |  |  |  |

| RF6      | 35(1)                  | 55(1)             | B30 <sup>(1)</sup> | I/O         | ST             |                                   |  |  |  |  |  |  |

| RF7      | —                      | 54(1)             | A37 <sup>(1)</sup> | I/O         | ST             | 1                                 |  |  |  |  |  |  |

| RF8      | —                      | 53                | B29                | I/O         | ST             | 1                                 |  |  |  |  |  |  |

| RF12     | —                      | 40                | A27                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RF13     | —                      | 39                | B22                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RG0      |                        | 90                | A61                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RG1      |                        | 89                | B50                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RG2      | 37(1)                  | 57(1)             | B31                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RG3      | 36 <sup>(1)</sup>      | 56 <sup>(1)</sup> | A38                | I/O         | ST             |                                   |  |  |  |  |  |  |

| RG6      | 4                      | 10                | A7                 | I/O         | ST             |                                   |  |  |  |  |  |  |

| RG7      | 5                      | 11                | B6                 | I/O         | ST             | POPTC is a hidiractional 1/0 part |  |  |  |  |  |  |

| RG8      | 6                      | 12                | A8                 | I/O         | ST             | PORTG is a bidirectional I/O port |  |  |  |  |  |  |

| RG9      | 8                      | 14                | A9                 | I/O         | ST             |                                   |  |  |  |  |  |  |

| RG12     | —                      | 96                | A65                | I/O         | ST             | ]                                 |  |  |  |  |  |  |

| RG13     | —                      | 97                | B55                | I/O         | ST             | ]                                 |  |  |  |  |  |  |

| RG14     | —                      | 95                | B54                | I/O         | ST             | ]                                 |  |  |  |  |  |  |

| RG15     | _                      | 1                 | A2                 | I/O         | ST             |                                   |  |  |  |  |  |  |

| T1CK     | 48                     | 74                | B40                | I           | ST             | Timer1 External Clock Input       |  |  |  |  |  |  |

| T2CK     | PPS                    | PPS               | PPS                | I           | ST             | Timer2 External Clock Input       |  |  |  |  |  |  |

| ТЗСК     | PPS                    | PPS               | PPS                | I           | ST             | Timer3 External Clock Input       |  |  |  |  |  |  |

| T4CK     | PPS                    | PPS               | PPS                | I           | ST             | Timer4 External Clock Input       |  |  |  |  |  |  |

| T5CK     | PPS                    | PPS               | PPS                | 1           | ST             | Timer4 External Clock Input       |  |  |  |  |  |  |

#### TABLE 1-1-PINOLIT I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

**Note 1:** This pin is only available on devices without a USB module. 2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices.

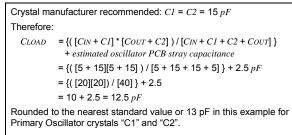

## 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

### EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

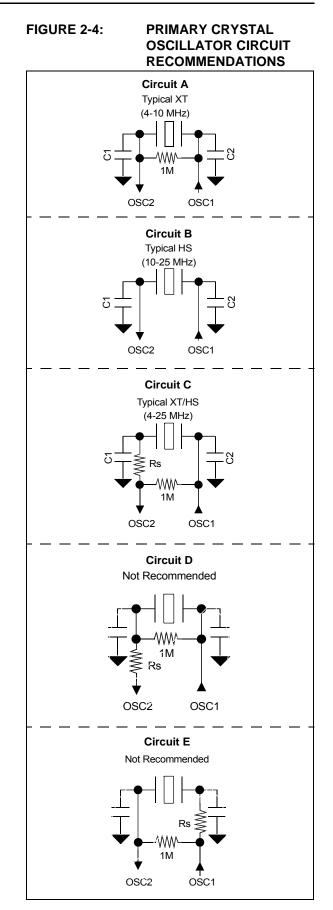

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator. The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

- Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

#### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

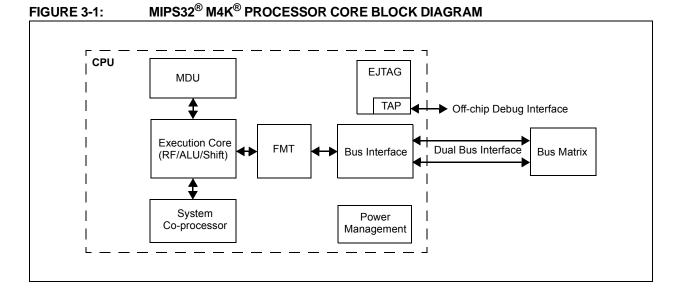

## 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at http://www.imgtec.com.

The the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX330/350/370/430/450/470 device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

## 3.1 Features

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32<sup>®</sup> Enhanced Architecture (Release 2):

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> Code Compression:

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) Mechanism:

- Simple Dual Bus Interface:

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- Autonomous Multiply/Divide Unit (MDU):

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- · Power Control:

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG Debug and Instruction Trace:

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

|              | _                 | _                 | _                 | —                 | _                 | —                 | —                | —                |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

|              | _                 | _                 | _                 | —                 | _                 | —                 | —                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8         | BMXDUDBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 7:0          |                   |                   |                   | BMXDU             | DBA<7:0>          |                   |                  |                  |  |  |  |

#### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

## Legend:

| Legena:           |                  |                                    |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4     | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-----------------------|------------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

|              | _                 | —                 | —                    | —                     | —                      | —                 | —                | _                |

| 00.40        | U-0               | U-0               | U-0                  | U-0                   | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | -                    | —                     | —                      | —                 |                  | _                |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0                   | R-0                    | U-0               | U-0              | U-0              |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR <sup>(1)</sup> | LVDSTAT <sup>(1)</sup> | —                 | —                | _                |

| 7.0          | U-0               | U-0               | U-0                  | U-0                   | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | —                 | —                 |                      | —                     |                        | NVMOF             | °<3:0>           |                  |

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | t, read as '0'     |

|-------------------|------------------|-----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

| bit 15   | WR: Write Control bit                                                                                               |

|----------|---------------------------------------------------------------------------------------------------------------------|

|          | This bit is writable when WREN = 1 and the unlock sequence is followed.                                             |

|          | 1 = Initiate a Flash operation. Hardware clears this bit when the operation completes                               |

|          | 0 = Flash operation complete or inactive                                                                            |

| bit 14   | WREN: Write Enable bit                                                                                              |

|          | 1 = Enable writes to WR bit and enables LVD circuit                                                                 |

|          | 0 = Disable writes to WR bit and disables LVD circuit                                                               |

|          | This is the only bit in this register reset by a device Reset.                                                      |

| bit 13   | WRERR: Write Error bit <sup>(1)</sup>                                                                               |

|          | This bit is read-only and is automatically set by hardware.                                                         |

|          | 1 = Program or erase sequence did not complete successfully                                                         |

|          | 0 = Program or erase sequence completed normally                                                                    |

| bit 12   | LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled) <sup>(1)</sup>                                   |

|          | This bit is read-only and is automatically set by hardware.                                                         |

|          | 1 = Low-voltage detected (possible data corruption, if WRERR is set)                                                |

|          | 0 = Voltage level is acceptable for programming                                                                     |

| bit 11   | LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled) <sup>(1)</sup>                                 |

|          | This bit is read-only and is automatically set, and cleared, by hardware.                                           |

|          | 1 = Low-voltage event active                                                                                        |

|          | 0 = Low-voltage event NOT active                                                                                    |

| bit 10-4 | Unimplemented: Read as '0'                                                                                          |

| bit 3-0  | NVMOP<3:0>: NVM Operation bits                                                                                      |

|          | These bits are writable when WREN = 0.                                                                              |

|          | 1111 = Reserved                                                                                                     |

|          | •                                                                                                                   |

|          |                                                                                                                     |

|          | 0111 = Reserved                                                                                                     |

|          | 0110 = No operation                                                                                                 |

|          | 0101 = Program Flash (PFM) erase operation: erases PFM, if all pages are not write-protected                        |

|          | 0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected                          |

|          | 0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected<br>0010 = No operation |

|          | 0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected                      |

|          | 0000 = No operation                                                                                                 |

|          |                                                                                                                     |

|          |                                                                                                                     |

**Note 1:** This bit is cleared by setting NVMOP = 0000, and initiating a Flash operation (i.e., WR).

#### **Oscillator Control Registers** 8.1

| TAB                                                            | TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP |                        |       |       |         |       |         |         |                             |        |         |                      |       |                     |      |                       |        |           |                     |

|----------------------------------------------------------------|--------------------------------------------|------------------------|-------|-------|---------|-------|---------|---------|-----------------------------|--------|---------|----------------------|-------|---------------------|------|-----------------------|--------|-----------|---------------------|

| ess                                                            |                                            | 0                      |       |       |         |       |         |         |                             |        | Bits    |                      |       |                     |      |                       |        |           | 6                   |

| Virtual Address<br>(BF80_#)<br>Register<br>Name <sup>(1)</sup> | Bit Range                                  | 31/15                  | 30/14 | 29/13 | 28/12   | 27/11 | 26/10   | 25/9    | 24/8                        | 23/7   | 22/6    | 21/5                 | 20/4  | 19/3                | 18/2 | 17/1                  | 16/0   | All Reset |                     |

| E000                                                           | F000 OSCCON                                | 31:16 — — PLLODIV<2:0> |       | >     |         |       |         | SOSCRDY | SOSCRDY PBDIVRDY PBDIV<1:0> |        |         | PLLMULT<2:0>         |       | x1xx <sup>(2)</sup> |      |                       |        |           |                     |

| F000                                                           | USCCON                                     | 15:0                   | _     |       | COSC<2: | 0>    | _       |         | NOSC<2:0                    | )>     | CLKLOCK | ULOCK <sup>(4)</sup> | SLOCK | SLPEN               | CF   | UFRCEN <sup>(4)</sup> | SOSCEN | OSWEN     | xxxx <sup>(2)</sup> |

| F010                                                           | OSCTUN                                     | 31:16                  | —     | _     | _       | _     | _       | —       | —                           |        | _       | —                    | _     | _                   |      | —                     | _      | _         | 0000                |

| 1010                                                           | 030101                                     | 15:0                   | —     | _     |         | —     | —       | —       | —                           |        | -       | _                    |       |                     | TUN  | <b>\&lt;5:0&gt;</b>   |        |           | 0000                |

| 5000                                                           | REFOCON                                    | 31:16                  | _     |       |         |       |         |         |                             |        | RODIV<  | 4:0>                 |       |                     |      |                       |        |           | 0000                |

| F020                                                           | REFUCUN                                    | 15:0                   | ON    | —     | SIDL    | OE    | RSLP    | —       | DIVSWEN                     | ACTIVE | —       | —                    | —     | —                   |      | ROSE                  | L<3:0> |           | 0000                |

| 5000                                                           | DEFOTDIM                                   | 31:16                  |       |       |         | I     | ROTRIM< | 8:0>    |                             |        |         | _                    |       | _                   | _    | _                     | _      | —         | 0000                |

| F030 H                                                         | REFOTRIM                                   | 15:0                   | _     | _     |         | _     | _       | _       | _                           |        | —       | _                    |       | _                   |      | _                     |        | _         | 0000                |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

Reset values are dependent on the DEVCFGx Configuration bits and the type of reset. 2:

This bit is only available on devices with a USB module. 3:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | —                 | _                 | _                 |                   | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | _                | CHECOH           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | —                 | -                 | —                 | _                 | DCSZ             | 2<1:0>           |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-1             | R/W-1            | R/W-1            |

| 7:0          | _                 | —                 | PREFEN<1:0>       |                   | _                 | PFMWS<2:0>        |                  | >                |

### REGISTER 9-1: CHECON: CACHE CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-17 Unimplemented: Write '0'; ignore read

- bit 16 CHECOH: Cache Coherency Setting on a PFM Program Cycle bit

- 1 = Invalidate all data and instruction lines

- 0 = Invalidate all data lnes and instruction lines that are not locked

- bit 15-10 Unimplemented: Write '0'; ignore read

- bit 9-8 DCSZ<1:0>: Data Cache Size in Lines bits

- 11 = Enable data caching with a size of 4 Lines

- 10 = Enable data caching with a size of 2 Lines

- 01 = Enable data caching with a size of 1 Line

- 00 = Disable data caching

Changing these bits induce all lines to be reinitialized to the "invalid" state.

bit 7-6 **Unimplemented:** Write '0'; ignore read

#### bit 5-4 **PREFEN<1:0>:** Predictive Prefetch Enable bits

- 11 = Enable predictive prefetch for both cacheable and non-cacheable regions

- 10 = Enable predictive prefetch for non-cacheable regions only

- 01 = Enable predictive prefetch for cacheable regions only

- 00 = Disable predictive prefetch

- bit 3 Unimplemented: Write '0'; ignore read

#### bit 2-0 PFMWS<2:0>: PFM Access Time Defined in Terms of SYSLK Wait States bits

- 111 = Seven Wait states

- 110 = Six Wait states

- 101 = Five Wait states

- 100 = Four Wait states

- 011 = Three Wait states

- 010 = Two Wait states

- 001 = One Wait state

- 000 = Zero Wait state

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 51.24        | LTAGBOOT          | —                 | —                 | —                 | —                 | -                 | _                | —                |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | LTAG<19:12>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15:0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | LTAG<11:4>        |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-0             | R/W-0             | R/W-1            | U-0              |  |  |  |

| 7.0          |                   | LTAG<             | <3:0>             |                   | LVALID            | LLOCK             | LTYPE            | —                |  |  |  |

### **REGISTER 9-3: CHETAG: CACHE TAG REGISTER**

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31 LTAGBOOT: Line TAG Address Boot bit

- 1 = The line is in the 0x1D000000 (physical) area of memory

- 0 = The line is in the 0x1FC00000 (physical) area of memory

#### bit 30-24 Unimplemented: Write '0'; ignore read

#### bit 23-4 LTAG<19:0>: Line TAG Address bits

LTAG<19:0> bits are compared against physical address to determine a hit. Because its address range and position of PFM in kernel space and user space, the LTAG PFM address is identical for virtual addresses, (system) physical addresses, and PFM physical addresses.

#### bit 3 LVALID: Line Valid bit

- 1 = The line is valid and is compared to the physical address for hit detection

- 0 = The line is not valid and is not compared to the physical address for hit detection

#### bit 2 LLOCK: Line Lock bit

- 1 = The line is locked and will not be replaced

- 0 = The line is not locked and can be replaced

#### bit 1 LTYPE: Line Type bit

- 1 = The line caches instruction words

- 0 = The line caches data words

- bit 0 Unimplemented: Write '0'; ignore read

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        | -                 | —                 | _                 | -                 | —                 | _                 | —                | —                |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 23.10        | -                 | —                 | _                 | -                 | —                 | _                 | —                | —                |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 15.0         |                   | _                 | _                 |                   | _                 | -                 |                  | _                |  |

| 7.0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |  |

| 7:0          | ID                | —                 | LSTATE            |                   | SESVD             | SESEND            |                  | VBUSVD           |  |

## REGISTER 11-3: U1OTGSTAT: USB OTG STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a Type-B cable has been plugged into the USB receptacle

- 0 = A Type-A cable has been plugged into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has been stable for the previous 1 ms

- 0 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has not been stable for the previous 1 ms

#### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 SESEND: B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

## REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

- 1 = Token packet is rejected due to CRC5 error

- 0 = Token packet is accepted

- EOFEF: EOF Error Flag bit<sup>(3,5)</sup>

- 1 = EOF error condition is detected

- 0 = No EOF error condition

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check is failed

- 0 = PID check is passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

## TABLE 12-16:PORTG REGISTER MAP FOR PIC32MX330F064H, PIC32MX350F128H, PIC32MX350F256H, PIC32MX370F512H,<br/>PIC32MX430F064H, PIC32MX450F128H, PIC32MX450F256H, AND PIC32MX470F512H DEVICES ONLY

| ess                         |                                 | 6         |       |       |       |       |       |       |              | Bi           | ts           |              |      |      |                    |                    |      |      |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|--------------|--------------|--------------|--------------|------|------|--------------------|--------------------|------|------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3               | 18/2               | 17/1 | 16/0 | All<br>Resets |

| 6600                        | ANSELG                          | 31:16     | _     | -     | _     | _     | _     |       | —            | _            | _            | —            |      |      | _                  | —                  | _    | _    | 0000          |

| 0000                        | ANSELG                          | 15:0      |       | -     | -     | -     | -     |       | ANSELG9      | ANSELG8      | ANSELG7      | ANSELG6      |      |      | _                  | —                  | —    | —    | 01C0          |

| 6610                        | TRISG                           | 31:16     | _     | -     | _     | _     | _     |       | —            | —            | -            | —            | _    | _    | —                  | —                  | _    | —    | 0000          |

| 0010                        | TRISO                           | 15:0      | _     | _     | _     | _     | _     | _     | TRISG9       | TRISG8       | TRISG7       | TRISG6       | _    | _    | TRISG3             | TRISG2             | _    | —    | xxxx          |

| 6620                        | PORTG                           | 31:16     | _     |       | -     | _     | -     |       | _            | _            |              | —            | _    |      | _                  | —                  | _    | _    | 0000          |

| 0020                        | FURIO                           | 15:0      | _     |       | -     | _     | -     |       | RG9          | RG8          | RG7          | RG6          | _    |      | RG3 <sup>(2)</sup> | RG2 <sup>(2)</sup> | _    | _    | xxxx          |

| 6630                        | LATG                            | 31:16     | _     |       | -     | —     |       |       | —            | —            |              | —            | -    |      | —                  | —                  | —    | —    | 0000          |

| 0030                        | LAIO                            | 15:0      | _     | —     | —     | —     | —     | _     | LATG9        | LATG8        | LATG7        | LATG6        | _    | _    | LATG3              | LATG2              | —    | —    | xxxx          |

| 6640                        | ODCG                            | 31:16     | _     | —     | —     | —     | —     | _     | —            | —            | _            | —            | _    | _    | —                  | —                  | —    | —    | 0000          |

| 0040                        | 0000                            | 15:0      | _     | —     | —     | —     | —     | _     | ODCG9        | ODCG8        | ODCG7        | ODCG6        | _    | _    | ODCG3              | ODCG2              | —    | —    | xxxx          |

| 6650                        | CNPUG                           | 31:16     | —     | _     | —     | —     | —     |       | —            | —            |              | —            | —    |      | —                  | —                  | _    | —    | 0000          |

| 0000                        |                                 | 15:0      | —     | _     | —     | —     | —     |       | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | —    |      | CNPUG3             | CNPUG2             | _    | —    | xxxx          |

| 6660                        | CNPDG                           | 31:16     | —     | _     | —     | —     | _     |       | —            | —            |              | —            | —    | _    | —                  | —                  | _    | —    | 0000          |

| 0000                        |                                 | 15:0      | —     | _     | —     | —     | _     |       | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       | —    | _    | CNPDG3             | CNPDG2             | _    | —    | xxxx          |

| 6670                        | CNCONG                          | 31:16     | —     | _     | —     | —     | _     |       | —            | _            |              | —            | —    | _    | —                  | —                  | _    | —    | 0000          |

| 0070                        | oncono                          | 15:0      | ON    | _     | SIDL  | —     | _     |       | —            | _            |              | —            | —    | _    | —                  | —                  | _    | —    | 0000          |

| 6680                        | CNENG                           | 31:16     | —     | _     | —     | —     | _     |       | —            | _            |              | —            | —    | _    | —                  | —                  | _    | —    | 0000          |

| 0000                        | ONLING                          | 15:0      | —     | _     | —     | —     | _     |       | CNIEG9       | CNIEG8       | CNIEG7       | CNIEG6       | —    | _    | CNIEG3             | CNIEG2             | _    | —    | xxxx          |

|                             |                                 | 31:16     | —     | _     | —     | —     | —     |       | —            | _            | _            | —            | —    |      | —                  | —                  | _    | —    | 0000          |

| 6690                        | CNSTATG                         | 15:0      | —     | -     | _     | —     | _     | -     | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 | —    |      | CN<br>STATG3       | CN<br>STATG2       | —    | —    | xxxx          |

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

2: This bit is only available on devices without a USB module.

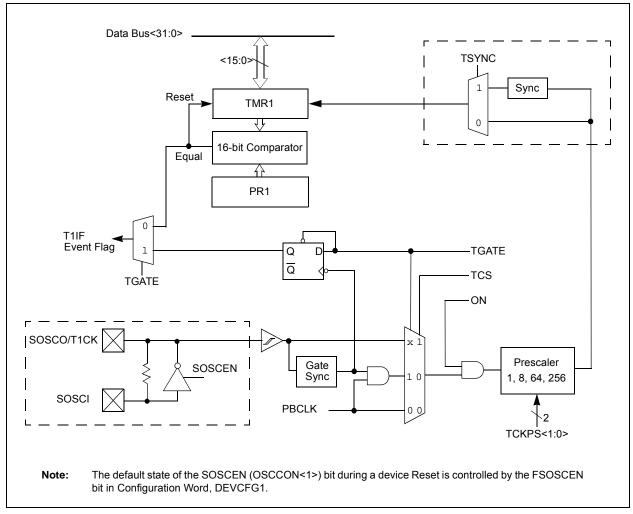

## 13.0 TIMER1

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 14. "Timers"** (DS60001105), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

This family of PIC32 devices features one synchronous/ asynchronous 16-bit timer that can operate as a freerunning interval timer for various timing applications and counting external events. This timer can also be used with the Low-Power Secondary Oscillator (Sosc) for Real-Time Clock (RTC) applications. The following modes are supported:

- · Synchronous Internal Timer

- Synchronous Internal Gated Timer

- Synchronous External Timer

- Asynchronous External Timer

## 13.1 Additional Supported Features

- · Selectable clock prescaler

- Timer operation during CPU Idle and Sleep mode

- Fast bit manipulation using CLR, SET and INV registers

- Asynchronous mode can be used with the Sosc to function as a Real-Time Clock (RTC)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 |                   | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 |                   |                   | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | _                 | _                | —                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             |                   | TCKPS<1:0>        |                   | _                 | TSYNC             | TCS              | _                |

### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER

## Legend:

| = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |

|---------------------------------|------------------|------------------------------------|--------------------|--|--|

| -n = Value at POR               | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

### bit 31-16 Unimplemented: Read as '0'

| Unimplemented: Read as 0                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ON: Timer On bit <sup>(1)</sup>                                                                                                                                                |

| 1 = Timer is enabled                                                                                                                                                           |

| 0 = Timer is disabled                                                                                                                                                          |

| Unimplemented: Read as '0'                                                                                                                                                     |

| SIDL: Stop in Idle Mode bit                                                                                                                                                    |

| <ul><li>1 = Discontinue operation when device enters Idle mode</li><li>0 = Continue operation even in Idle mode</li></ul>                                                      |

| TWDIS: Asynchronous Timer Write Disable bit                                                                                                                                    |

| <ul><li>1 = Writes to TMR1 are ignored until pending write operation completes</li><li>0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)</li></ul> |

| TWIP: Asynchronous Timer Write in Progress bit                                                                                                                                 |

| In Asynchronous Timer mode:                                                                                                                                                    |

| <ul><li>1 = Asynchronous write to TMR1 register in progress</li><li>0 = Asynchronous write to TMR1 register complete</li></ul>                                                 |

| In Synchronous Timer mode:<br>This bit is read as '0'                                                                                                                          |

| Unimplemented: Read as '0'                                                                                                                                                     |

| <b>TGATE:</b> Timer Gated Time Accumulation Enable bit                                                                                                                         |

| When $TCS = 1$ :                                                                                                                                                               |

| This bit is ignored.                                                                                                                                                           |

| When TCS = 0:                                                                                                                                                                  |

| 1 = Gated time accumulation is enabled                                                                                                                                         |

| 0 = Gated time accumulation is disabled                                                                                                                                        |

| Unimplemented: Read as '0'                                                                                                                                                     |

| TCKPS<1:0>: Timer Input Clock Prescale Select bits                                                                                                                             |

| 11 = 1:256 prescale value<br>10 = 1:64 prescale value                                                                                                                          |

| 01 = 1:8 prescale value                                                                                                                                                        |

| 00 = 1:1 prescale value                                                                                                                                                        |

| Unimplemented: Read as '0'                                                                                                                                                     |

|                                                                                                                                                                                |

|                                                                                                                                                                                |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| REGIST    | ER 18-1:                   | SPIxCON: S                                                                                                                             | SPI CONTROL REGISTER (CONTINUED)                                                                                                                               |  |  |  |  |  |  |

|-----------|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| bit 17    |                            |                                                                                                                                        | e Edge Select bit (Framed SPI mode only)                                                                                                                       |  |  |  |  |  |  |

|           |                            |                                                                                                                                        | on pulse coincides with the first bit clock                                                                                                                    |  |  |  |  |  |  |

| h:+ 40    |                            | <ul> <li>Frame synchronization pulse precedes the first bit clock</li> <li>ENHBUF: Enhanced Buffer Enable bit<sup>(2)</sup></li> </ul> |                                                                                                                                                                |  |  |  |  |  |  |

| bit 16    |                            | ed Buffer mo                                                                                                                           |                                                                                                                                                                |  |  |  |  |  |  |

|           |                            | ed Buffer mod                                                                                                                          |                                                                                                                                                                |  |  |  |  |  |  |

| bit 15    |                            | ripheral On bi                                                                                                                         |                                                                                                                                                                |  |  |  |  |  |  |

|           |                            | ripheral is ena                                                                                                                        |                                                                                                                                                                |  |  |  |  |  |  |

|           |                            | ripheral is dis                                                                                                                        |                                                                                                                                                                |  |  |  |  |  |  |

| bit 14    | Unimpleme                  | ented: Read a                                                                                                                          | as '0'                                                                                                                                                         |  |  |  |  |  |  |

| bit 13    | SIDL: Stop                 | in Idle Mode b                                                                                                                         | pit                                                                                                                                                            |  |  |  |  |  |  |

|           |                            | •                                                                                                                                      | n when CPU enters in Idle mode                                                                                                                                 |  |  |  |  |  |  |

|           |                            | ue operation i                                                                                                                         |                                                                                                                                                                |  |  |  |  |  |  |

| bit 12    |                            | isable SDOx                                                                                                                            |                                                                                                                                                                |  |  |  |  |  |  |

|           |                            |                                                                                                                                        | d by the module. Pin is controlled by associated PORT register<br>ed by the module                                                                             |  |  |  |  |  |  |

| bit 11-10 |                            |                                                                                                                                        | t Communication Select bits                                                                                                                                    |  |  |  |  |  |  |

|           | When AUD                   |                                                                                                                                        | Communication Select bits                                                                                                                                      |  |  |  |  |  |  |

|           | MODE32                     | MODE16                                                                                                                                 | Communication                                                                                                                                                  |  |  |  |  |  |  |

|           | 1                          | 1                                                                                                                                      | 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                          |  |  |  |  |  |  |

|           | 1                          | 0                                                                                                                                      | 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                          |  |  |  |  |  |  |

|           | 0                          | 1                                                                                                                                      | 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                          |  |  |  |  |  |  |

|           | 0                          | 0                                                                                                                                      | 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                                                                                          |  |  |  |  |  |  |

|           | When AUD                   | <b>FN =</b> 0:                                                                                                                         |                                                                                                                                                                |  |  |  |  |  |  |

|           | MODE32                     | MODE16                                                                                                                                 | Communication                                                                                                                                                  |  |  |  |  |  |  |

|           | 1                          | x                                                                                                                                      | 32-bit                                                                                                                                                         |  |  |  |  |  |  |

|           | 0                          | 1                                                                                                                                      | 16-bit                                                                                                                                                         |  |  |  |  |  |  |

|           | 0                          | 0                                                                                                                                      | 8-bit                                                                                                                                                          |  |  |  |  |  |  |

| bit 9     |                            |                                                                                                                                        | nple Phase bit                                                                                                                                                 |  |  |  |  |  |  |

|           |                            | <u>le (MSTEN =</u><br>ata sampled a                                                                                                    | $\pm$ ).<br>at end of data output time                                                                                                                         |  |  |  |  |  |  |

|           |                            |                                                                                                                                        | at middle of data output time                                                                                                                                  |  |  |  |  |  |  |

|           |                            | • (MSTEN = 0                                                                                                                           |                                                                                                                                                                |  |  |  |  |  |  |

|           |                            | -                                                                                                                                      | en SPI is used in Slave mode. The module always uses SMP = 0.                                                                                                  |  |  |  |  |  |  |

| bit 8     |                            | lock Edge Se                                                                                                                           |                                                                                                                                                                |  |  |  |  |  |  |

|           |                            |                                                                                                                                        | anges on transition from active clock state to Idle clock state (see CKP bit)<br>anges on transition from Idle clock state to active clock state (see CKP bit) |  |  |  |  |  |  |

| bit 7     |                            | -                                                                                                                                      | ble (Slave mode) bit                                                                                                                                           |  |  |  |  |  |  |

|           |                            | n used for Sla                                                                                                                         |                                                                                                                                                                |  |  |  |  |  |  |

|           |                            |                                                                                                                                        | Slave mode, pin controlled by port function.                                                                                                                   |  |  |  |  |  |  |

| bit 6     |                            | Polarity Sele                                                                                                                          |                                                                                                                                                                |  |  |  |  |  |  |

|           | 1 = Idle sta               | te for clock is                                                                                                                        | a high level; active state is a low level                                                                                                                      |  |  |  |  |  |  |

|           |                            |                                                                                                                                        | a low level; active state is a high level                                                                                                                      |  |  |  |  |  |  |

| bit 5     |                            | aster Mode Er                                                                                                                          | hable bit                                                                                                                                                      |  |  |  |  |  |  |

|           | 1 = Master<br>0 = Slave r  |                                                                                                                                        |                                                                                                                                                                |  |  |  |  |  |  |

|           |                            | lieue                                                                                                                                  |                                                                                                                                                                |  |  |  |  |  |  |

| Note 1:   | When using                 | g the 1:1 PBC                                                                                                                          | LK divisor, the user software should not read or write the peripheral's SFRs in the                                                                            |  |  |  |  |  |  |

|           |                            | -                                                                                                                                      | ely following the instruction that clears the module's ON bit.                                                                                                 |  |  |  |  |  |  |

| 2:        | This bit car               | n only be writte                                                                                                                       | en when the ON bit = 0.                                                                                                                                        |  |  |  |  |  |  |

| 3:        | This bit is r<br>mode (FRN |                                                                                                                                        | e Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                  |  |  |  |  |  |  |

| 4:        | -                          | -                                                                                                                                      | PI module functions as if the CKP bit is equal to '1', regardless of the actual value                                                                          |  |  |  |  |  |  |

|           | of CKP.                    | <u> </u>                                                                                                                               |                                                                                                                                                                |  |  |  |  |  |  |

|           |                            |                                                                                                                                        |                                                                                                                                                                |  |  |  |  |  |  |

## REGISTER 19-1: I2CxCON: I<sup>2</sup>C CONTROL REGISTER

|              | -                 |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | _                 | —                 | —                 | —                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | —                 | _                 | _                 | _                | _                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-1, HC         | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | SCLREL            | STRICT            | A10M              | DISSLW           | SMEN             |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0, HC         | R/W-0, HC         | R/W-0, HC         | R/W-0, HC        | R/W-0, HC        |

| 7:0          | GCEN              | STREN             | ACKDT             | ACKEN             | RCEN              | PEN               | RSEN             | SEN              |

| Legend:           | HC = Cleared in Hardware |                                    |                    |  |  |

|-------------------|--------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared               | x = Bit is unknown |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** I<sup>2</sup>C Enable bit<sup>(1)</sup>

- 1 = Enables the  $I^2C$  module and configures the SDA and SCL pins as serial port pins

- 0 = Disables the  $I^2$ C module; all  $I^2$ C pins are controlled by PORT functions

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode