Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 81                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (14x14)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256l-v-pf |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

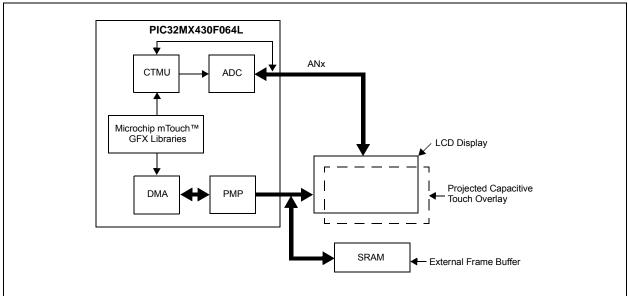

## FIGURE 2-8: LOW-COST CONTROLLERLESS (LCC) GRAPHICS APPLICATION WITH PROJECTED CAPACITIVE TOUCH

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 |                  | —                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | _                 | _                 | —                 | _                 | _                 | —                 | —                | —                |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |

| 15:8         | BMXDKPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 7:0          |                   | BMXDKPBA<7:0>     |                   |                   |                   |                   |                  |                  |  |  |

### REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

#### Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 **BMXDKPBA<15:10>:** DRM Kernel Program Base Address bits When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 BMXDKPBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2         | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|---------------------------|------------------|------------------|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                       | U-0              | U-0              |  |

| 31:24        | _                 | —                 | —                 | —                 | —                 | —                         | —                | —                |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                       | U-0              | U-0              |  |

| 23:16        | —                 | —                 | —                 | —                 | —                 | —                         | —                | —                |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0                     | R/W-0            | R/W-0            |  |

| 15:8         | _                 | —                 | _                 | —                 | —                 | SRIPL<2:0> <sup>(1)</sup> |                  |                  |  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0                     | R/W-0            | R/W-0            |  |

| 7:0          | _                 | —                 |                   |                   | VEC               | <5:0>(1)                  |                  |                  |  |

#### REGISTER 7-2: INTSTAT: INTERRUPT STATUS REGISTER

## Legend:

| Logonan                           |                  |                                    |                    |  |  |  |

|-----------------------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR                 | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-11 Unimplemented: Read as '0'

- bit 10-8 **SRIPL<2:0>:** Requested Priority Level bits<sup>(1)</sup> 111-000 = The priority level of the latest interrupt presented to the CPU

- bit 7-6 Unimplemented: Read as '0'

- bit 5-0 VEC<5:0>: Interrupt Vector bits<sup>(1)</sup> 11111-00000 = The interrupt vector that is presented to the CPU

- Note 1: This value should only be used when the interrupt controller is configured for Single Vector mode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        |                   |                   |                   | IPTMF             | <31:24>           |                   |                  |                  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | IPTMR<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | IPTMR<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | IPTMR<7:0>        |                   |                   |                   |                   |                   |                  |                  |  |

#### REGISTER 7-3: IPTMR: INTERRUPT PROXIMITY TIMER REGISTER

| Legend:           |                  |                      |                                    |  |  |

|-------------------|------------------|----------------------|------------------------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | U = Unimplemented bit, read as '0' |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown                 |  |  |

bit 31-0 **IPTMR<31:0>:** Interrupt Proximity Timer Reload bits Used by the Interrupt Proximity Timer as a reload value when the Interrupt Proximity timer is triggered by an interrupt event.

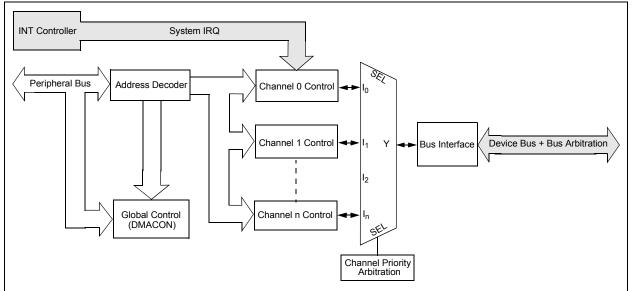

## 10.0 DIRECT MEMORY ACCESS (DMA) CONTROLLER

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 31. "Direct Memory Access (DMA) Controller" (DS60001117), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 Direct Memory Access (DMA) controller is a bus master module useful for data transfers between different devices without CPU intervention. The source and destination of a DMA transfer can be any of the memory mapped modules existent in the PIC32 (such as Peripheral Bus (PBUS) devices: SPI, UART, PMP, etc.) or memory itself.

Following are some of the key features of the DMA controller module:

- Four identical channels, each featuring:

- Auto-increment source and destination address registers

- Source and destination pointers

- Memory to memory and memory to peripheral transfers

- Automatic word-size detection:

- Transfer granularity, down to byte level

- Bytes need not be word-aligned at source and destination

- Fixed priority channel arbitration

- · Flexible DMA channel operating modes:

- Manual (software) or automatic (interrupt) DMA requests

- One-Shot or Auto-Repeat Block Transfer modes

- Channel-to-channel chaining

- · Flexible DMA requests:

- A DMA request can be selected from any of the peripheral interrupt sources

- Each channel can select any (appropriate) observable interrupt as its DMA request source

- A DMA transfer abort can be selected from any of the peripheral interrupt sources

- Pattern (data) match transfer termination

- · Multiple DMA channel status interrupts:

- DMA channel block transfer complete

- Source empty or half empty

- Destination full or half full

- DMA transfer aborted due to an external event

- Invalid DMA address generated

- DMA debug support features:

- Most recent address accessed by a DMA channel

- Most recent DMA channel to transfer data

- · CRC Generation module:

- CRC module can be assigned to any of the available channels

- CRC module is highly configurable

## FIGURE 10-1: DMA BLOCK DIAGRAM

| INE OIDTE    | REGISTER 10-8. DEFRECON: DMA CHANNEL & EVENT CONTROL REGISTER |                   |                   |                   |                   |                   |                  |                  |  |

|--------------|---------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| Bit<br>Range | Bit<br>31/23/15/7                                             | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

| 31:24        | U-0                                                           | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |

| 31.24        |                                                               | —                 | _                 | —                 | —                 | _                 | —                | —                |  |

| 22:16        | R/W-1                                                         | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |

| 23:16        | CHAIRQ<7:0> <sup>(1)</sup>                                    |                   |                   |                   |                   |                   |                  |                  |  |

| 15.0         | R/W-1                                                         | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1             | R/W-1            | R/W-1            |  |

| 15:8         | CHSIRQ<7:0> <sup>(1)</sup>                                    |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | S-0                                                           | S-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | U-0              | U-0              |  |

| 7.0          | CFORCE                                                        | CABORT            | PATEN             | SIRQEN            | AIRQEN            |                   |                  |                  |  |

#### REGISTER 10-8 DCHxECON: DMA CHANNEL 'x' EVENT CONTROL REGISTER

| Legend:           | S = Settable bit |                                    |                    |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |

## bit 31-24 Unimplemented: Read as '0'

| bit 31-24 | Unimplemented: Read as '0'                                                                                 |

|-----------|------------------------------------------------------------------------------------------------------------|

| bit 23-16 | CHAIRQ<7:0>: Channel Transfer Abort IRQ bits <sup>(1)</sup>                                                |

|           | 11111111 = Interrupt 255 will abort any transfers in progress and set CHAIF flag                           |

|           | •                                                                                                          |

|           | •                                                                                                          |

|           | •                                                                                                          |

|           | 00000001 = Interrupt 1 will abort any transfers in progress and set CHAIF flag                             |

|           | 00000000 = Interrupt 0 will abort any transfers in progress and set CHAIF flag                             |

| bit 15-8  | CHSIRQ<7:0>: Channel Transfer Start IRQ bits <sup>(1)</sup>                                                |

|           | 11111111 = Interrupt 255 will initiate a DMA transfer                                                      |

|           | •                                                                                                          |

|           | •                                                                                                          |

|           |                                                                                                            |

|           | 00000001 = Interrupt 1 will initiate a DMA transfer<br>00000000 = Interrupt 0 will initiate a DMA transfer |

| h:4 7     |                                                                                                            |

| bit 7     | CFORCE: DMA Forced Transfer bit                                                                            |

|           | 1 = A DMA transfer is forced to begin when this bit is written to a '1'                                    |

|           | 0 = This bit always reads '0'                                                                              |

| bit 6     | CABORT: DMA Abort Transfer bit                                                                             |

|           | 1 = A DMA transfer is aborted when this bit is written to a '1'                                            |

|           | 0 = This bit always reads '0'                                                                              |

| bit 5     | PATEN: Channel Pattern Match Abort Enable bit                                                              |

|           | 1 = Abort transfer and clear CHEN on pattern match                                                         |

|           | 0 = Pattern match is disabled                                                                              |

| bit 4     | SIRQEN: Channel Start IRQ Enable bit                                                                       |

|           | 1 = Start channel cell transfer if an interrupt matching CHSIRQ occurs                                     |

- Start channel cell transfer if an interrupt matching CHSIRQ occurs 0 = Interrupt number CHSIRQ is ignored and does not start a transfer

- bit 3 AIRQEN: Channel Abort IRQ Enable bit

- 1 = Channel transfer is aborted if an interrupt matching CHAIRQ occurs

- 0 = Interrupt number CHAIRQ is ignored and does not terminate a transfer

- bit 2-0 Unimplemented: Read as '0'

- Note 1: See Table 7-1: "Interrupt IRQ, Vector and Bit Location" for the list of available interrupt IRQ sources.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6          | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2      | Bit<br>25/17/9/1      | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|----------------------------|----------------------|----------------------|-------------------|------------------------|-----------------------|------------------|--|--|

| 31:24        | U-0               | U-0                        | U-0                  | U-0                  | U-0               | U-0                    | U-0                   | U-0              |  |  |

| 31.24        | -                 | -                          | -                    | -                    | —                 | -                      | —                     |                  |  |  |

| 23:16        | U-0               | U-0                        | U-0                  | U-0                  | U-0               | U-0                    | U-0                   | U-0              |  |  |

| 23.10        | -                 |                            | -                    |                      |                   |                        | —                     |                  |  |  |

| 15:8         | U-0               | U-0                        | U-0                  | U-0                  | U-0               | U-0                    | U-0                   | U-0              |  |  |

| 15.6         | -                 | -                          | -                    | -                    | —                 | -                      | —                     | -                |  |  |

|              | R/WC-0, HS        | R/WC-0, HS                 | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS            | R/WC-0, HS       |  |  |

| 7:0          | DISEE             | DMYEE                      | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF                | CRC5EF <sup>(4)</sup> | DIDEE            |  |  |

|              | BTSEF B           | BMXEF DMAEF <sup>(1)</sup> | BIUEF-               | DENGER               | UKU IDEF          | EOFEF <sup>(3,5)</sup> | PIDEF                 |                  |  |  |

### REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit         |                    |

|-------------------|-------------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 BTSEF: Bit Stuff Error Flag bit

- 1 = Packet is rejected due to bit stuff error

- 0 = Packet is accepted

- bit 6 BMXEF: Bus Matrix Error Flag bit

1 = The base address, of the BDT, or the address of an individual buffer pointed to by a BDT entry, is invalid.

0 = No address error

- bit 5 **DMAEF:** DMA Error Flag bit<sup>(1)</sup> 1 = USB DMA error condition detected

- 0 = No DMA error

- bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

- 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

#### bit 3 **DFN8EF:** Data Field Size Error Flag bit

- 1 = Data field received is not an integral number of bytes

- 0 = Data field received is an integral number of bytes

#### bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet rejected due to CRC16 error

- 0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

## TABLE 12-1: INPUT PIN SELECTION

| Peripheral Pin | [pin name]R SFR       | [pin name]R bits | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection                                                                                        |  |  |  |

|----------------|-----------------------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| INT3           | INT3R                 | INT3R<3:0>       | 0000 = RPD2<br>0001 = RPG8                                                                                                                |  |  |  |

| T2CK           | T2CKR                 | T2CKR<3:0>       | 0010 = RPF4<br>0011 = RPD10                                                                                                               |  |  |  |

| IC3            | IC3R                  | IC3R<3:0>        | 0100 = RPF1<br>0101 = RPB9                                                                                                                |  |  |  |

| U1RX           | U1RXR                 | U1RXR<3:0>       |                                                                                                                                           |  |  |  |

| U2RX           | U2RXR                 | U2RXR<3:0>       | 1000 - RFB3<br>1001 = Reserved<br>1010 = RPC1 <sup>(3)</sup>                                                                              |  |  |  |

| U5CTS          | U5CTSR <sup>(3)</sup> | U5CTSR<3:0>      | $\frac{1011}{1011} = \text{RPD14(3)}$<br>1100 = RPG1(3)                                                                                   |  |  |  |

| REFCLKI        | REFCLKIR              | REFCLKIR<3:0>    | 1100 = RPA14 <sup>(3)</sup><br>1110 = Reserved<br>1111 = RPF2 <sup>(1)</sup>                                                              |  |  |  |

| INT4           | INT4R                 | INT4R<3:0>       | 0000 = RPD3<br>0001 = RPG7                                                                                                                |  |  |  |

| T5CK<br>IC4    | T5CKR                 | T5CKR<3:0>       | 0010 = RPF5<br>0011 = RPD11                                                                                                               |  |  |  |

|                | IC4R                  | IC4R<3:0>        | 0100 = RPF0<br>0101 = RPB1                                                                                                                |  |  |  |

| U3RX           | U3RXR                 | U3RXR<3:0>       |                                                                                                                                           |  |  |  |

| U4CTS          | U4CTSR                | U4CTSR<3:0>      | 1001 = Reserved<br>1010 = RPC4 <sup>(3)</sup><br>1011 = RPD15 <sup>(3)</sup><br>1100 = RPG0 <sup>(3)</sup>                                |  |  |  |

| SDI1           | SDI1R                 | SDI1R<3:0>       |                                                                                                                                           |  |  |  |

| SDI2           | SDI2R                 | SDI2R<3:0>       | 1101 = RPA15 <sup>(3)</sup><br>1110 = RPF2 <sup>(1)</sup><br>1111 = RPF7 <sup>(2)</sup>                                                   |  |  |  |

| INT2           | INT2R                 | INT2R<3:0>       | 0000 = RPD9<br>0001 = RPG6                                                                                                                |  |  |  |

| T4CK           | T4CKR                 | T4CKR<3:0>       | 0010 = RPB8<br>0011 = RPB15                                                                                                               |  |  |  |

| IC2            | IC2R                  | IC2R<3:0>        | 0100 = RPD4<br>0101 = RPB0                                                                                                                |  |  |  |

| IC5            | IC5R                  | IC5R<3:0>        | 0110 = RPE3<br>0111 = RPB7                                                                                                                |  |  |  |

| U1CTS          | U1CTSR                | U1CTSR<3:0>      | 1000 = Reserved<br>1001 = RPF12 <sup>(3)</sup><br>1010 = RPD12 <sup>(3)</sup><br>1011 = RPF8 <sup>(3)</sup><br>1100 = RPC3 <sup>(3)</sup> |  |  |  |

| U2CTS          | U2CTSR                | U2CTSR<3:0>      |                                                                                                                                           |  |  |  |

| SS1            | SS1R                  | SS1R<3:0>        | 1101 = RPE9 <sup>(3)</sup><br>1110 = Reserved                                                                                             |  |  |  |

|                |                       |                  | 1111 <b>= RPB2</b>                                                                                                                        |  |  |  |

**Note 1:** This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

3: This selection is not available on 64-pin USB and General Purpose devices.

4: This selection is only available on General Purpose devices.

|                             |                                 | P         | C32MX         | 430F064       | L, PIC3       | 2MX450        | F128L,        | PIC32M        | X450F2       | 56L, AN      | ID PIC3      | 2MX47        | 0F512L       | DEVIC        | ES ONL       | .Y           |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                         |                                 |           |               |               |               |               |               |               |              | Bits         | 6            |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11         | 26/10         | 25/9         | 24/8         | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6300                        | ANSELD                          | 31:16     |               | —             | —             | —             | —             |               | —            | —            | —            |              | —            | —            | —            |              | —            |              | 0000          |

|                             |                                 | 15:0      | _             | —             | —             | _             | —             | —             | —            | —            | —            | _            | —            | —            | ANSELD3      | ANSELD2      | ANSELD1      | _            | 000E          |

| 6310                        | TRISD                           | 31:16     | _             | —             | —             | —             | —             | —             | —            | —            | —            |              | —            | _            | _            | _            | —            | _            | 0000          |

|                             | _                               | 15:0      | TRISD15       | TRISD14       | TRISD13       | TRISD12       | TRISD11       | TRISD10       | TRISD9       | TRISD8       | TRISD7       | TRISD6       | TRISD5       | TRISD4       | TRISD3       | TRISD2       | TRISD1       | TRISD0       | xxxx          |

| 5320                        | PORTD                           | 31:16     | _             | —             | _             | —             | —             | —             | —            | —            | —            |              | —            | —            |              | —            | —            | _            | 0000          |

|                             | _                               | 15:0      | RD15          | RD14          | RD13          | RD12          | RD11          | RD10          | RD9          | RD8          | RD7          | RD6          | RD5          | RD4          | RD3          | RD2          | RD1          | RD0          | xxxx          |

| 6330                        | LATD                            | 31:16     |               | —             | —             | —             | —             | —             | —            | —            | —            | —            | —            | —            | —            |              | —            | —            | 0000          |

|                             |                                 | 15:0      | LATD15        | LATD14        | LATD13        | LATD12        | LATD11        | LATD10        | LATD9        | LATD8        | LATD7        | LATD6        | LATD5        | LATD4        | LATD3        | LATD2        | LATD1        | LATD0        | XXXX          |

| 6340                        | ODCD                            | 31:16     | —             | —             | —             | —             | —             | —             | —            | —            | —            | —            | —            | —            | —            | —            | —            | _            | 0000          |

|                             |                                 | 15:0      | ODCD15        | ODCD14        | ODCD13        | ODCD12        | ODCD11        | ODCD10        | ODCD9        | ODCD8        | ODCD7        | ODCD6        | ODCD5        | ODCD4        | ODCD3        | ODCD2        | ODCD1        | ODCD0        | xxxx          |

| 6350                        | CNPUD                           | 31:16     | -             | —             | —             | —             | —             | -             | —            | —            | —            | —            | —            | —            | —            | —            | —            | -            | 0000          |

|                             |                                 | 15:0      | CNPUD15       | CNPUD14       | CNPUD13       | CNPUD12       | CNPUD11       | CNPUD10       |              | CNPUD8       | CNPUD7       | CNPUD6       | CNPUD5       | CNPUD4       | CNPUD3       | CNPUD2       | CNPUD1       | CNPUD0       | xxxx          |

| 6360                        | CNPDD                           | 31:16     | -             | —             | —             | —             | —             | -             | —            | —            | —            | —            | —            | —            | —            | —            | —            | _            | 0000          |

|                             |                                 |           | CNPDD15       | -             | CNPDD13       | CNPDD12       | CNPDD11       | CNPDD10       |              | CNPDD8       | -            | CNPDD6       |              | CNPDD4       | CNPDD3       | CNPDD2       | CNPDD1       | CNPDD0       | XXXX          |

| 6370                        | CNCOND                          | 31:16     | _             |               | -             |               |               |               |              |              |              |              |              |              |              | _            |              |              | 0000          |

|                             |                                 | 15:0      | ON            |               | SIDL          |               |               |               |              |              |              |              |              |              |              | _            |              |              | 0000          |

| 6380                        | CNEND                           | 31:16     | -             | -             | -             | -             |               |               | -            | -            | -            |              | -            | -            | -            | -            |              |              | 0000          |

|                             |                                 | 15:0      | CNIED15       | CNIED14       | CNIED13       | CNIED12       | CNIED11       | CNIED10       | CNIED9       | CNIED8       | CNIED7       | CNIED6       | CNIED5       | CNIED4       | CNIED3       | CNIED2       | CNIED1       | CNIED0       | XXXX          |

| 6200                        |                                 | 31:16     | -             | -             | —             | —             | —             | -             | -            | —            | -            | -            | —            | -            | —            | —            | —            | -            | 0000          |

| 6390                        | CNSTATD                         | 15:0      | CNS<br>TATD15 | CN<br>STATD14 | CN<br>STATD13 | CN<br>STATD12 | CN<br>STATD11 | CN<br>STATD10 | CN<br>STATD9 | CN<br>STATD8 | CN<br>STATD7 | CN<br>STATD6 | CN<br>STATD5 | CN<br>STATD4 | CN<br>STATD3 | CN<br>STATD2 | CN<br>STATD1 | CN<br>STATD0 | xxxx          |

## TABLE 12-7: PORTD REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

|                             |                                 | C         | ONLY  |       |               |               |       |       |      |              |              |        |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|---------------|---------------|-------|-------|------|--------------|--------------|--------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                         |                                 |           |       |       |               |               |       |       |      | Bi           | ts           |        |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13         | 28/12         | 27/11 | 26/10 | 25/9 | 24/8         | 23/7         | 22/6   | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6510                        | TRISF                           | 31:16     | _     | _     | _             |               | _     |       | _    |              |              |        | _            |              | -            |              |              |              | 0000          |

| 0310                        | TRIST                           | 15:0      | _     | —     | TRISF13       | TRISF12       | _     | _     | —    | TRISF8       | TRISF7       | TRISF6 | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | xxxx          |

| 6520                        | PORTF                           | 31:16     | —     | —     | —             | —             | _     | -     | —    | -            | —            | -      | —            | _            | _            | -            | _            | -            | 0000          |

| 0520                        | TOKI                            | 15:0      | —     | —     | RF13          | RF12          | _     | -     | —    | RF8          | RF7          | RF6    | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | xxxx          |

| 6530                        | LATF                            | 31:16     | —     | —     | —             | —             | _     | -     | —    | -            | -            | -      | —            | _            | _            | -            | _            | -            | 0000          |

| 0000                        | LAII                            | 15:0      | —     | —     | LATF13        | LATF12        | _     | -     | —    | LATF8        | LATF7        | LATF6  | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | _     |       | —             | —             | —     | _     |      | _            | _            |        | —            |              | _            | _            |              |              | 0000          |

| 0040                        | 0001                            | 15:0      | _     |       | ODCF13        | ODCF12        | —     | _     |      | ODCF8        | ODCF7        | ODCF6  | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | xxxx          |

| 6550                        | CNPUF                           | 31:16     | —     |       | —             | —             | —     | —     |      | —            | —            | _      | —            | —            | —            | —            | —            | _            | 0000          |

| 0000                        |                                 | 15:0      | —     | —     | CNPUF13       | CNPUF12       | —     | —     | —    | CNPUF8       | CNPUF7       | CNPUF6 | CNPUF5       | CNPUF4       | CNPDF3       | CNPUF2       | CNPUF1       | CNPUF0       | xxxx          |

| 6560                        | CNPDF                           | 31:16     | —     | —     | —             | —             | —     | _     | —    | —            | _            | _      | —            | _            | —            | _            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | —     | CNPDF13       | CNPDF12       | —     | -     | —    | CNPDF8       | CNPDF7       | CNPDF6 | CNPDF5       | CNPDF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | xxxx          |

| 6570                        | CNCONF                          | 31:16     | —     | —     | —             | —             | —     | -     | —    | -            | -            | _      | —            | _            | _            | -            | —            | —            | 0000          |

|                             |                                 | 15:0      | ON    | —     | SIDL          | —             | —     | -     | —    | -            | -            | _      | —            | _            | _            | -            | —            | —            | 0000          |

| 6580                        | CNENF                           | 31:16     | —     | —     | —             | —             | —     | -     | —    | -            | -            | _      | —            | _            | —            | -            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | —     | CNIEF13       | CNIEF12       | —     | -     | —    | CNIEF8       | CNIEF7       | _      | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | xxxx          |

|                             |                                 | 31:16     | —     | —     | —             | —             | —     | -     | —    | -            | -            | _      | —            | _            | -            | -            | —            | —            | 0000          |

| 6590                        | CNSTATF                         | 15:0      | _     | —     | CN<br>STATF13 | CN<br>STATF12 | _     | _     | —    | CN<br>STATF8 | CN<br>STATF7 | _      | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | xxxx          |

TABLE 12-11: PORTF REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, AND PIC32MX370F512L DEVICES

Legend: x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

## REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

|              | -                 |                   |                   |                   |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | -                 | _                 | -                 | —                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 15.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |

| 15:8         | ACKSTAT           | TRSTAT            | -                 | -                 | _                 | BCL               | GCSTAT           | ADD10            |

| 7:0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

| Legend:           | HS = Set in hardware | HSC = Hardware set/clear  | ed                |

|-------------------|----------------------|---------------------------|-------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ead as '0'        |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | C = Clearable bit |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit

(when operating as  $I^2C$  master, applicable to master transmit operation)

- 1 = Acknowledge was not received from slave

- 0 = Acknowledge was received from slave

Hardware set or clear at end of slave Acknowledge.

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

1 = A bus collision has been detected during a master operation

0 = No collision

Hardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module.

- bit 9 **GCSTAT:** General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware set when address matches general call address. Hardware clear at Stop detection.

bit 8 ADD10: 10-bit Address Status bit

1 = 10-bit address was matched

0 = 10-bit address was not matched

Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

- bit 7 IWCOL: Write Collision Detect bit

- 1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy

- 0 = No collision

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

bit 6 I2COV: Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

| REGISTE | ER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER (CONTINUED)                                                                                                                                                                                                                                                                                                                                                                              |

|---------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

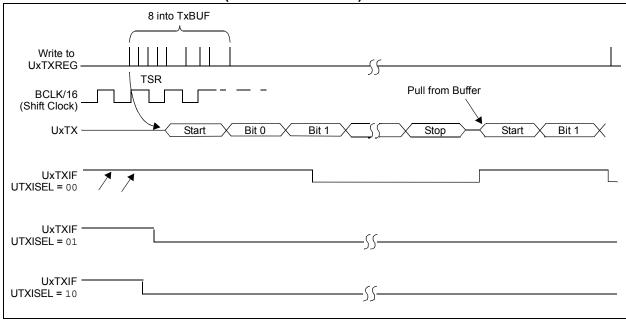

| bit 8   | <ul> <li>TRMT: Transmit Shift Register is Empty bit (read-only)</li> <li>1 = Transmit shift register is empty and transmit buffer is empty (the last transmission has completed)</li> <li>0 = Transmit shift register is not empty, a transmission is in progress or queued in the transmit buffer</li> </ul>                                                                                                                              |

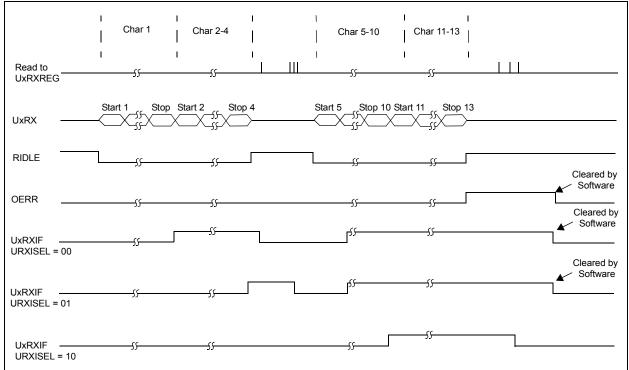

| bit 7-6 | URXISEL<1:0>: Receive Interrupt Mode Selection bit<br>11 = Reserved; do not use<br>10 = Interrupt flag bit is asserted while receive buffer is 3/4 or more full (i.e., has 6 or more data characters)<br>01 = Interrupt flag bit is asserted while receive buffer is 1/2 or more full (i.e., has 4 or more data characters)<br>00 = Interrupt flag bit is asserted while receive buffer is not empty (i.e., has at least 1 data character) |

| bit 5   | <ul> <li>ADDEN: Address Character Detect bit (bit 8 of received data = 1)</li> <li>1 = Address Detect mode is enabled. If 9-bit mode is not selected, this control bit has no effect</li> <li>0 = Address Detect mode is disabled</li> </ul>                                                                                                                                                                                               |

| bit 4   | RIDLE: Receiver Idle bit (read-only)<br>1 = Receiver is Idle<br>0 = Data is being received                                                                                                                                                                                                                                                                                                                                                 |

| bit 3   | <ul> <li>PERR: Parity Error Status bit (read-only)</li> <li>1 = Parity error has been detected for the current character</li> <li>0 = Parity error has not been detected</li> </ul>                                                                                                                                                                                                                                                        |

| bit 2   | <ul> <li>FERR: Framing Error Status bit (read-only)</li> <li>1 = Framing error has been detected for the current character</li> <li>0 = Framing error has not been detected</li> </ul>                                                                                                                                                                                                                                                     |

| bit 1   | OERR: Receive Buffer Overrun Error Status bit.                                                                                                                                                                                                                                                                                                                                                                                             |

|         | This bit is set in hardware and can only be cleared (= 0) in software. Clearing a previously set OERR bit resets the receiver buffer and RSR to empty state.                                                                                                                                                                                                                                                                               |

|         | <ul><li>1 = Receive buffer has overflowed</li><li>0 = Receive buffer has not overflowed</li></ul>                                                                                                                                                                                                                                                                                                                                          |

- bit 0 URXDA: Receive Buffer Data Available bit (read-only)

- 1 = Receive buffer has data, at least one more character can be read

- 0 = Receive buffer is empty

## 20.2 Timing Diagrams

Figure 20-2 and Figure 20-3 illustrate typical receive and transmit timing for the UART module.

## FIGURE 20-2: UART RECEPTION

#### FIGURE 20-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        |                   | —                 | —                 | _                 | —                 | —                 | —                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |  |  |  |

| 15:8         |                   | VCFG<2:0>         |                   | OFFCAL            | —                 | CSCNA             | —                | —                |  |  |  |

| 7:0          | R-0 U-0 R/W       |                   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | BUFS              | _                 |                   | SMP               | I<3:0>            |                   | BUFM             | ALTS             |  |  |  |

#### REGISTER 23-2: AD1CON2: ADC CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |  |  |  |  |

|-----|--------------------|--------------------|--|--|--|--|

| 000 | AVDD               | AVss               |  |  |  |  |

| 001 | External VREF+ pin | AVss               |  |  |  |  |

| 010 | AVDD               | External VREF- pin |  |  |  |  |

| 011 | External VREF+ pin | External VREF- pin |  |  |  |  |

| 1xx | AVDD               | AVss               |  |  |  |  |

#### bit 12 OFFCAL: Input Offset Calibration Mode Select bit

#### 1 = Enable Offset Calibration mode

Positive and negative inputs of the sample and hold amplifier are connected to VREFL

#### 0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

#### bit 11 Unimplemented: Read as '0'

- bit 10 **CSCNA:** Input Scan Select bit

- 1 = Scan inputs

0 = Do not scan inputs

#### bit 9-8 **Unimplemented:** Read as '0'

bit 7 **BUFS:** Buffer Fill Status bit

Only valid when BUFM = 1.

1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

#### bit 6 Unimplemented: Read as '0'

#### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

```

1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence

```

```

1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

```

- .

- •

0001 = Interrupts at the completion of conversion for each  $2^{nd}$  sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

#### bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

#### bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

## REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0 (CONTINUED)

- bit 11-5 **Reserved:** Write '1'

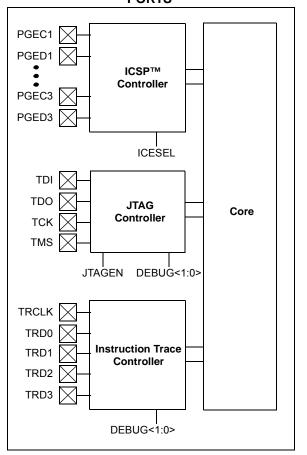

- bit 4-3 ICESEL<1:0>: In-Circuit Emulator/Debugger Communication Channel Select bits

- 11 = PGEC1/PGED1 pair is used

- 10 = PGEC2/PGED2 pair is used

- 01 = PGEC3/PGED3 pair is used

- 00 = Reserved

- bit 2 JTAGEN: JTAG Enable bit<sup>(1)</sup> 1 = JTAG is enabled 0 = JTAG is disabled

- bit 1-0 **DEBUG<1:0>:** Background Debugger Enable bits (forced to '11' if code-protect is enabled)

- 1x = Debugger is disabled0x = Debugger is enabled

- Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

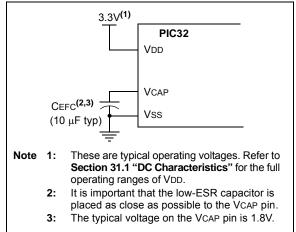

## 28.2 On-Chip Voltage Regulator

All PIC32MX330/350/370/430/450/470 devices' core and digital logic are designed to operate at a nominal 1.8V. To simplify system designs, most devices in the PIC32MX330/350/370/430/450/470 family incorporate an on-chip regulator providing the required core logic voltage from VDD.

A low-ESR capacitor (such as tantalum) must be connected to the VCAP pin (see Figure 28-1). This helps to maintain the stability of the regulator. The recommended value for the filter capacitor is provided in **Section 31.1 "DC Characteristics"**.

| Note: | It is important that the low-ESR capacitor |

|-------|--------------------------------------------|

|       | is placed as close as possible to the VCAP |

|       | pin.                                       |

## 28.2.1 HIGH VOLTAGE DETECT (HVD)

The HVD module monitors the core voltage at the VCAP pin. If a voltage above the required level is detected on VCAP, the I/O pins are disabled and the device is held in Reset as long as the HVD condition persists. See parameter HV10 (VHVD) in Table 31-11 in **Section 31.1** "**DC Characteristics**" for more information.

## 28.2.2 ON-CHIP REGULATOR AND POR

It takes a fixed delay for the on-chip regulator to generate an output. During this time, designated as TPU, code execution is disabled. TPU is applied every time the device resumes operation after any power-down, including Sleep mode.

## 28.2.3 ON-CHIP REGULATOR AND BOR

PIC32MX330/350/370/430/450/470 devices also have a simple brown-out capability. If the voltage supplied to the regulator is inadequate to maintain a regulated level, the regulator Reset circuitry will generate a Brown-out Reset. This event is captured by the BOR flag bit (RCON<1>). The brown-out voltage levels are specific in **Section 31.1 "DC Characteristics"**.

## FIGURE 28-1: CONNECTIONS FOR THE ON-CHIP REGULATOR

## 28.3 Programming and Diagnostics

PIC32MX330/350/370/430/450/470 devices provide a complete range of programming and diagnostic features that can increase the flexibility of any application using them. These features allow system designers to include:

- Simplified field programmability using two-wire In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) interfaces

- Debugging using ICSP

- Programming and debugging capabilities using the EJTAG extension of JTAG

- JTAG boundary scan testing for device and board diagnostics

PIC32 devices incorporate two programming and diagnostic modules, and a trace controller, that provide a range of functions to the application developer.

FIGURE 28-2:

#### BLOCK DIAGRAM OF PROGRAMMING, DEBUGGING AND TRACE PORTS

| DC CHARACTERISTICS |        |                                       | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                        |      |       |                                               |  |  |  |

|--------------------|--------|---------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|------|-------|-----------------------------------------------|--|--|--|

| Param.<br>No.      | Symbol | Characteristics                       | Min.                                                                                                                                                                                                                                                                                                                                                    | Typical <sup>(1)</sup> | Max. | Units | Conditions                                    |  |  |  |

| D130               | Eр     | Cell Endurance                        | 20,000                                                                                                                                                                                                                                                                                                                                                  | —                      |      | E/W   | —                                             |  |  |  |

| D131               | Vpr    | VDD for Read                          | 2.3                                                                                                                                                                                                                                                                                                                                                     | —                      | 3.6  | V     | —                                             |  |  |  |

| D132               | VPEW   | VDD for Erase or Write                | 2.3                                                                                                                                                                                                                                                                                                                                                     | —                      | 3.6  | V     | —                                             |  |  |  |

| D134               | TRETD  | Characteristic Retention              | 20                                                                                                                                                                                                                                                                                                                                                      | _                      | _    | Year  | Provided no other specifications are violated |  |  |  |

| D135               | IDDP   | Supply Current during<br>Programming  | —                                                                                                                                                                                                                                                                                                                                                       | 10                     |      | mA    | —                                             |  |  |  |

| D138               | Tww    | Word Write Cycle Time <sup>(4)</sup>  | 44                                                                                                                                                                                                                                                                                                                                                      | _                      | 59   | μs    | —                                             |  |  |  |

| D136               | Trw    | Row Write Cycle Time <sup>(2,4)</sup> | 2.8                                                                                                                                                                                                                                                                                                                                                     | 3.3                    | 3.8  | ms    | —                                             |  |  |  |

| D137               | TPE    | Page Erase Cycle Time <sup>(4)</sup>  | 22                                                                                                                                                                                                                                                                                                                                                      | —                      | 29   | ms    | —                                             |  |  |  |

| D139               | TCE    | Chip Erase Cycle Time <sup>(4)</sup>  | 86                                                                                                                                                                                                                                                                                                                                                      | —                      | 116  | ms    | —                                             |  |  |  |

## TABLE 31-12: DC CHARACTERISTICS: PROGRAM MEMORY<sup>(3)</sup>

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated.

2: The minimum SYSCLK for row programming is 8 MHz. Care should be taken to minimize bus activities during row programming, such as suspending any memory-to-memory DMA operations. If heavy bus loads are expected, selecting Bus Matrix Arbitration mode 2 (rotating priority) may be necessary. The default Arbitration mode is mode 1 (CPU has lowest priority).

- **3:** Refer to the *"PIC32 Flash Programming Specification"* (DS60001145) for operating conditions during programming and erase cycles.

- 4: This parameter depends on the FRC accuracy (see Table 31-20) and the FRC tuning values (see Register 8-2).

| DC CHARACTERISTICS         | (unless otherwise state                  | ndard Operating Conditions: 2.3V to 3.6Vless otherwise stated)erating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |                 |  |  |

|----------------------------|------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

|                            | -40°C $\leq$ TA $\leq$ +105°C for V-temp |                                                                                                                                                                                                |                 |  |  |

| Required Flash Wait States | SYSCLK                                   | Units                                                                                                                                                                                          | Conditions      |  |  |

| 0 Wait State               | 0-40                                     | MHz                                                                                                                                                                                            | -40°C to +85°C  |  |  |

|                            | 0-30                                     | MHz                                                                                                                                                                                            | -40°C to +105°C |  |  |

| 1 Wait State               | 41-80                                    | MHz                                                                                                                                                                                            | -40°C to +85°C  |  |  |

|                            | 31-60                                    | MHz                                                                                                                                                                                            | -40°C to +105°C |  |  |

| 2 Wait States              | 81-100                                   | MHz                                                                                                                                                                                            | -40°C to +85°C  |  |  |

|                            | 61-80                                    | MHz                                                                                                                                                                                            | -40°C to +105°C |  |  |

| 3 Wait States              | 101-120                                  | MHz                                                                                                                                                                                            | 0°C to +70°C    |  |  |

## TABLE 31-33: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE) (CONTINUED)

| AC CHARACTERISTICS |         |                             | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                     |      |       |                                        |                  |

|--------------------|---------|-----------------------------|------------------------------------------------------|---------------------|------|-------|----------------------------------------|------------------|

| Param.<br>No.      | Symbol  | I Characteristics           |                                                      | Min. <sup>(1)</sup> | Max. | Units | Conditions                             |                  |

| IM34               | THD:STO | Stop Condition              | 100 kHz mode                                         | Трв * (BRG + 2)     |      | ns    | —                                      |                  |

|                    |         | Hold Time                   | 400 kHz mode                                         | Трв * (BRG + 2)     | —    | ns    |                                        |                  |

|                    |         |                             | 1 MHz mode<br>(Note 2)                               | Трв * (BRG + 2)     | —    | ns    |                                        |                  |

| IM40               | TAA:SCL | SCL Output Valid from Clock | 100 kHz mode                                         | —                   | 3500 | ns    | —                                      |                  |

|                    |         |                             | 400 kHz mode                                         | —                   | 1000 | ns    | —                                      |                  |

|                    |         |                             | 1 MHz mode<br>(Note 2)                               | —                   | 350  | ns    | —                                      |                  |

| IM45               | TBF:SDA | SDA Bus Free Time           | 100 kHz mode                                         | 4.7                 | —    | μS    | The amount of time the                 |                  |

|                    |         |                             |                                                      | 400 kHz mode        | 1.3  | —     | — μs                                   | bus must be free |

|                    |         |                             | 1 MHz mode<br>(Note 2)                               | 0.5                 | —    | μS    | before a new<br>transmission can start |                  |

| IM50               | Св      | Bus Capacitive Loading      |                                                      | —                   | 400  | pF    | —                                      |                  |

| IM51               | Tpgd    | Pulse Gobbler Delay         |                                                      | 52                  | 312  | ns    | See Note 3                             |                  |

**Note 1:** BRG is the value of the I<sup>2</sup>C Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

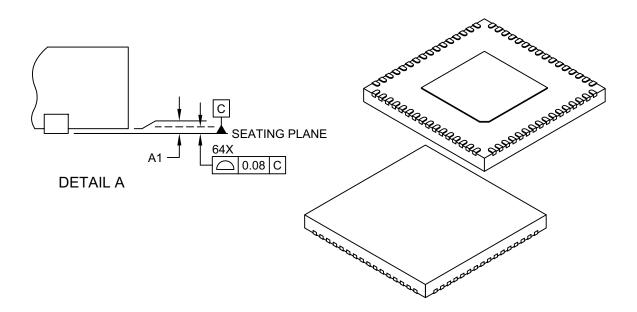

## 64-Terminal Plastic Quad Flat Pack, No Lead (RG) 9x9x0.9 mm Body [QFN] Saw Singulated

|                         | Units            | MILLIMETERS |      |      |  |

|-------------------------|------------------|-------------|------|------|--|

| Dimension               | Dimension Limits |             | NOM  | MAX  |  |

| Number of Terminals     | Ν                | 64          |      |      |  |

| Pitch                   | е                | 0.50 BSC    |      |      |  |

| Overall Height          | Α                | 0.80        | 0.85 | 0.90 |  |

| Standoff                | A1               | 0.00        | 0.02 | 0.05 |  |

| Standoff                | A3               | 0.20 REF    |      |      |  |

| Overall Width           | E                | 9.00 BSC    |      |      |  |