Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 81                                                                             |

| Program Memory Size        | 256KB (256K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 64K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 100-TQFP                                                                       |

| Supplier Device Package    | 100-TQFP (12x12)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256l-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 6: PIN NAMES FOR 124-PIN DEVICES (CONTINUED)

| 124               | -PIN VTLA (BOTTOM VIEW) <sup>(1,2,3,4,5)</sup> A17                       |                   |                  | A34                       |

|-------------------|--------------------------------------------------------------------------|-------------------|------------------|---------------------------|

|                   | AT/                                                                      |                   | B13 B29          | Conductive<br>Thermal Pad |

|                   | PIC32MX330F064L<br>PIC32MX350F128L<br>PIC32MX350F256L<br>PIC32MX370F512L |                   | B1 E<br>B56      | 341<br>A51                |

|                   | Polarity I                                                               | A1<br>tor         | A68              |                           |

| Package<br>Bump # | Full Pin Name                                                            | Package<br>Bump # |                  | Full Pin Name             |

| B7                | MCLR                                                                     | B32               | SDA2/RA3         |                           |

| B8                | Vss                                                                      | B33               | TDO/RA5          |                           |

| B9                | TMS/CTED1/RA0                                                            | B34               | OSC1/CLKI/RC12   |                           |

| B10               | RPE9/RE9                                                                 | B35               | No Connect       |                           |

| B11               | AN4/C1INB/RB4                                                            | B36               | RPA14/RA14       |                           |

| B12               | Vss                                                                      | B37               | RPD8/RTCC/RD8    |                           |

| B13               | PGEC3/AN2/C2INB/RPB2/CTED13/RB2                                          | B38               | RPD10/PMCS2/RD10 | )                         |

| B14               | PGED1/AN0/RPB0/RB0                                                       | B39               | RPD0/RD0         |                           |

| B15               | No Connect                                                               | B40               | SOSCO/RPC14/T1Ck |                           |

| B16               | PGED2/AN7/RPB7/CTED3/RB7                                                 | B41               | Vss              |                           |

| B17               | VREF+/CVREF+/PMA6/RA10                                                   | B42               | AN25/RPD2/RD2    |                           |

| B18               | AVss                                                                     | B43               | RPD12/PMD12/RD12 |                           |

| B19               | AN9/RPB9/CTED4/RB9                                                       | B44               | RPD4/PMWR/RD4    |                           |

| B20               | AN11/PMA12/RB11                                                          | B45               | PMD14/RD6        |                           |

| B21               | VDD                                                                      | B46               | No Connect       |                           |

| B22               | RPF13/RF13                                                               | B47               | No Connect       |                           |

| B23               | AN12/PMA11/RB12                                                          | B48               | VCAP             |                           |

| B24               | AN14/RPB14/CTED5/PMA1/RB14                                               | B49               | RPF0/PMD11/RF0   |                           |

| B25               | Vss                                                                      | B50               | RPG1/PMD9/RG1    |                           |

| B26               | RPD14/RD14                                                               | B51               | TRCLK/RA6        |                           |

| B27               | RPF4/PMA9/RF4                                                            | B52               | PMD0/RE0         |                           |

| B28               | No Connect                                                               | B53               | Vdd              |                           |

| B29               | RPF8/RF8                                                                 | B54               | TRD2/RG14        |                           |

| B30               | RPF6/SCKI/INT0/RF6                                                       | B55               | TRD0/RG13        |                           |

| B31               | SCL1/RG2                                                                 | B56               | RPE3/CTPLS/PMD3/ | RE3                       |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx), with the exception of RF6, can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: RPF6 (bump B30) and RPF7 (bump A37) are only remappable for input functions.

4: Shaded package bumps are 5V tolerant.

5: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 31:24        |                   |                   |                   | BMXPFN            | ISZ<31:24>        |                   |                  |                  |  |  |  |

| 22:16        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 15:8         | BMXPFMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 7:0          | BMXPFMSZ<7:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

#### REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

## Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes: 0x00010000 = Device has 64 KB Flash 0x00020000 = Device has 128 KB Flash 0x00040000 = Device has 256 KB Flash 0x00080000 = Device has 512 KB Flash

#### REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

|              |                   |                   |                   | . ,               |                   |                   |                  |                  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 24.24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 31:24        |                   | BMXBOOTSZ<31:24>  |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 23:16        |                   |                   |                   | BMXBOO            | TSZ<23:16>        |                   |                  |                  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 15:8         | BMXBOOTSZ<15:8>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 7:0          | BMXBOOTSZ<7:0>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 **BMXBOOTSZ<31:0>:** Boot Flash Memory (BFM) Size bits Static value that indicates the size of the Boot PFM in bytes: 0x00003000 = Device has 12 KB Boot Flash

## REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits<sup>(1)</sup>

- 1111 = Reserved; do not use

- 1001 = Reserved; do not use 1000 = REFCLKI 0111 = System PLL output 0110 = USB PLL output 0101 = Sosc 0100 = LPRC 0011 = FRC 0010 = POSC 0001 = PBCLK 0000 = SYSCLK

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

## 9.2 Control Registers

## TABLE 9-1: PREFETCH REGISTER MAP

| ess                         |                       |               |               |                |           |             |             |            |            | Bit        | s      |      |       |            |         |       |          |        |            |

|-----------------------------|-----------------------|---------------|---------------|----------------|-----------|-------------|-------------|------------|------------|------------|--------|------|-------|------------|---------|-------|----------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name      | Bit Range     | 31/15         | 30/14          | 29/13     | 28/12       | 27/11       | 26/10      | 25/9       | 24/8       | 23/7   | 22/6 | 21/5  | 20/4       | 19/3    | 18/2  | 17/1     | 16/0   | All Resets |

| 4000                        | CHECON <sup>(1)</sup> | 31:16         | —             | _              | —         | —           |             | _          | —          | —          | _      |      | —     |            | —       | —     |          | CHECOH | 0000       |

| 1000                        |                       | 15:0          | —             | _              |           | —           | _           | _          | DCSZ       | <1:0>      | —      |      | PREFE | N<1:0>     | —       | P     | FMWS<2:0 | )>     | 0007       |

| 4010                        | CHEACC <sup>(1)</sup> |               | CHEWEN        | —              | —         | —           | —           | —          | —          | —          | —      | —    | —     | —          | —       | —     | —        | —      | 0000       |

|                             |                       | 15:0          | —             | _              | —         | —           | —           | _          | —          | —          | —      |      | —     | —          |         | CHEID | X<3:0>   |        | 00xx       |

| 4020                        | CHETAG <sup>(1)</sup> | 31:16         | LTAGBOOT      | —              | —         | —           | —           | —          | —          | —          |        |      |       | LTAG<      | :23:16> |       |          |        | xxx0       |

| 1020                        |                       |               |               |                |           |             |             | LTAG<      | 15:4>      |            |        |      |       |            | LVALID  | LLOCK | LTYPE    | —      | xxx2       |

| 4030                        | CHEMSK <sup>(1)</sup> | 31:16         | —             | —              | —         | —           | —           | —          | —          | —          | —      | —    | —     | _          | —       | —     | —        | —      | 0000       |

|                             |                       | 15:0          |               |                |           |             | LN          | 1ASK<15:5  | >          |            |        |      |       | —          | —       | _     | —        | —      | xxxx       |

| 4040                        | CHEW0                 | 31:16         |               |                |           |             |             |            |            | CHEW0      | <31:0> |      |       |            |         |       |          |        | XXXX       |

|                             |                       | 15:0          |               |                |           |             |             |            |            |            |        |      |       |            |         |       |          |        | XXXX       |

| 4050                        | CHEW1                 | 31:16         |               |                |           |             |             |            |            | CHEW1      | <31:0> |      |       |            |         |       |          |        | xxxx       |

|                             |                       | 15:0          |               |                |           |             |             |            |            |            |        |      |       |            |         |       |          |        | xxxx       |

| 4060                        | CHEW2                 | 31:16         |               |                |           |             |             |            |            | CHEW2      | <31:0> |      |       |            |         |       |          |        | xxxx       |

|                             |                       | 15:0          |               |                |           |             |             |            |            |            |        |      |       |            |         |       |          |        | XXXX       |

| 4070                        | CHEW3                 | 31:16         |               |                |           |             |             |            |            | CHEW3      | <31:0> |      |       |            |         |       |          |        | XXXX       |

|                             |                       | 15:0          | _             | _              | _         | _           | _           | _          |            |            |        |      | CH    | IELRU<24:1 | 16>     |       |          |        | XXXX       |

| 4080                        | CHELRU                | 31:16<br>15:0 |               |                |           |             |             |            | _          | CHELRU     | <15.0> |      | CI    |            | 10-     |       |          |        | 0000       |

|                             |                       |               |               |                |           |             |             |            |            | CHELRU     | <15.0> |      |       |            |         |       |          |        | 0000       |

| 4090                        | CHEHIT                | 31:16<br>15:0 |               | CHEHIT<31:0>   |           |             |             |            |            |            |        |      |       |            |         |       |          |        |            |

|                             |                       |               |               | XXX            |           |             |             |            |            |            |        |      |       |            |         |       |          |        |            |

| 40A0                        | CHEMIS                | 31:16<br>15:0 | CHEMIS<31:0>  |                |           |             |             |            |            |            |        | xxxx |       |            |         |       |          |        |            |

|                             |                       | 31:16         |               | XXX            |           |             |             |            |            |            |        |      |       |            |         |       |          |        |            |

| 40C0                        | CHEDEADT              | 15:0          |               | CHEPFABT<31:0> |           |             |             |            |            |            |        |      |       |            |         |       |          |        |            |

| Legen                       |                       |               | n value on Re | sot = u        | nimplomon | tod road as | : '0' Reset | values are | shown in h | avadocimal |        |      |       |            |         |       |          |        | XXXX       |

Legend:

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | —                 | _                 | _                 |                   | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | _                | CHECOH           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | —                 | -                 | —                 |                   | DCSZ             | 2<1:0>           |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-1             | R/W-1            | R/W-1            |

| 7:0          | _                 | —                 | PREFE             | N<1:0>            | _                 | F                 | PFMWS<2:0>       | >                |

#### REGISTER 9-1: CHECON: CACHE CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-17 Unimplemented: Write '0'; ignore read

- bit 16 CHECOH: Cache Coherency Setting on a PFM Program Cycle bit

- 1 = Invalidate all data and instruction lines

- 0 = Invalidate all data lnes and instruction lines that are not locked

- bit 15-10 Unimplemented: Write '0'; ignore read

- bit 9-8 DCSZ<1:0>: Data Cache Size in Lines bits

- 11 = Enable data caching with a size of 4 Lines

- 10 = Enable data caching with a size of 2 Lines

- 01 = Enable data caching with a size of 1 Line

- 00 = Disable data caching

Changing these bits induce all lines to be reinitialized to the "invalid" state.

bit 7-6 **Unimplemented:** Write '0'; ignore read

#### bit 5-4 **PREFEN<1:0>:** Predictive Prefetch Enable bits

- 11 = Enable predictive prefetch for both cacheable and non-cacheable regions

- 10 = Enable predictive prefetch for non-cacheable regions only

- 01 = Enable predictive prefetch for cacheable regions only

- 00 = Disable predictive prefetch

- bit 3 Unimplemented: Write '0'; ignore read

#### bit 2-0 PFMWS<2:0>: PFM Access Time Defined in Terms of SYSLK Wait States bits

- 111 = Seven Wait states

- 110 = Six Wait states

- 101 = Five Wait states

- 100 = Four Wait states

- 011 = Three Wait states

- 010 = Two Wait states

- 001 = One Wait state

- 000 = Zero Wait state

## TABLE 12-17: PERIPHERAL PIN SELECT INPUT REGISTER MAP (CONTINUED)

| sse                         |                       |           |       |       |       |       |       |       |      | В    | its  |      |      |      |      |       |                   |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|-------------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1              | 16/0 | All Resets |

| FA54                        | U1CTSR                | 31:16     | _     | _     | _     |       | _     | _     | _    | _    | _    | _    | _    | —    |      |       |                   | _    | 0000       |

| FA04                        | UICISK                | 15:0      | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    |      | U1CTS | SR<3:0>           |      | 0000       |

|                             |                       | 31:16     | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    | _    |       | —                 | _    | 0000       |

| FA58                        | U2RXR                 | 15:0      | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    |      | U2RX  | R<3:0>            |      | 0000       |

| FA5C                        | U2CTSR                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _                 | -    | 0000       |

| FASC                        | UZCISK                | 15:0      | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    |      | U2CTS | SR<3:0>           |      | 0000       |

| FA60                        | <b>U3RXR</b>          | 31:16     | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    | _    |       | —                 | _    | 0000       |

| FAOU                        | USKAR                 | 15:0      | —     | —     | _     | _     | —     | —     |      | —    |      |      | —    | —    |      | U3RX  | R<3:0>            |      | 0000       |

| 5464                        | <b>U3CTSR</b>         | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _                 | -    | 0000       |

| FA64                        | USCISK                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U3CTS | SR<3:0>           |      | 0000       |

| 5400                        | U4RXR                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _                 | -    | 0000       |

| FA68                        | U4RXR                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U4RX  | R<3:0>            |      | 0000       |

| FA6C                        | U4CTSR                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _                 | -    | 0000       |

| FAGC                        | U4CISR                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U4CTS | SR<3:0>           |      | 0000       |

| FA70                        | U5RXR <sup>(1)</sup>  | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _                 | -    | 0000       |

| FA70                        | USRXR <sup>(1)</sup>  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | —    | _    | _    | -    |      | U5RX  | R<3:0>            |      | 0000       |

| FA74                        | U5CTSR <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | —    | _    | —    | —    | —    | —    | _    | —     | —                 | -    | 0000       |

| FA74                        | 0501580               | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | U5CTS | SR<3:0>           |      | 0000       |

| 5404                        | SDI1R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _                 | -    | 0000       |

| FA84                        | SDITR                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | —    | _    | _    | -    |      | SDI1F | R<3:0>            |      | 0000       |

| <b>FA00</b>                 | 0040                  | 31:16     | _     | _     | _     | _     | _     | _     | —    | _    | —    | —    | —    | —    | _    | —     | —                 | -    | 0000       |

| FA88                        | SS1R                  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | —    | _    | _    | _    |      | SS1F  | R<3:0>            |      | 0000       |

| FA00                        | SDI2R                 | 31:16     | _     | —     | _     |       | —     | —     |      | —    | -    |      | —    | _    | _    | —     | —                 | _    | 0000       |

| FA90                        | SDIZR                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | SDI2F | R<3:0>            |      | 0000       |

| E404                        | SS2R                  | 31:16     | _     | —     | _     |       | —     | —     |      | —    | -    |      | —    | _    | _    | —     | —                 | _    | 0000       |

| FA94                        | 552R                  | 15:0      | _     |       |       |       |       |       | 0000 |      |      |      |      |      |      |       |                   |      |            |

| FADO                        |                       | 31:16     | _     | —     | _     | _     | —     | —     |      | —    | _    |      | —    | _    | _    | _     | —                 | _    | 0000       |

| FAD0                        | REFCLKIR              | 15:0      | _     | _     | _     | —     | _     | —     | _    | —    | _    | —    | _    | _    |      | REFCL | <ir<3:0></ir<3:0> |      | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 |                   | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 | -                 | —                 | _                 | _                 | _                | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | —                 | _                 |                   | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | ?]R<3:0>         |                  |

#### REGISTER 12-1: [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

#### bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 12-1 for input pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

#### REGISTER 12-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 | —                 | —                 | _                 | _                 | -                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | —                 | _                 | —                 |                  | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 | _                 | —                 |                   | RPnR              | <3:0>            |                  |

## Legend:

| 0                 |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 12-2 for output pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

NOTES:

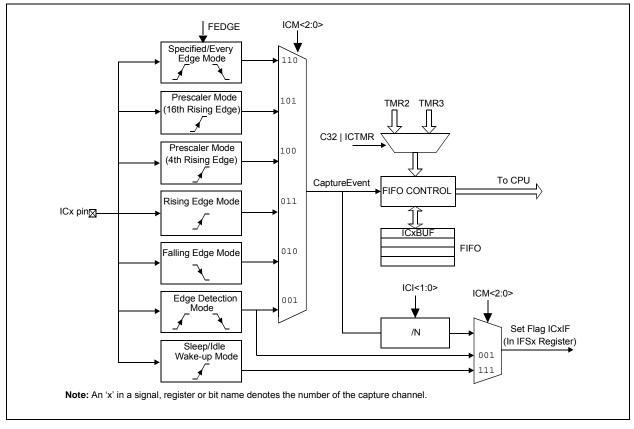

## 16.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

## FIGURE 16-1: INPUT CAPTURE BLOCK DIAGRAM

## REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | -                 | _                 | -                 | —                 |                   | _                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | _                 | _                 | _                 | —                 | _                | _                |

| 15.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |

| 15:8         | ACKSTAT           | TRSTAT            | -                 | -                 | _                 | BCL               | GCSTAT           | ADD10            |

| 7:0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |

| Legend:           | HS = Set in hardware | HSC = Hardware set/clear  | ed                |

|-------------------|----------------------|---------------------------|-------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ead as '0'        |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | C = Clearable bit |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit

(when operating as  $I^2C$  master, applicable to master transmit operation)

- 1 = Acknowledge was not received from slave

- 0 = Acknowledge was received from slave

Hardware set or clear at end of slave Acknowledge.

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

1 = A bus collision has been detected during a master operation

0 = No collision

Hardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module.

- bit 9 **GCSTAT:** General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware set when address matches general call address. Hardware clear at Stop detection.

bit 8 ADD10: 10-bit Address Status bit

1 = 10-bit address was matched

0 = 10-bit address was not matched

Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

- bit 7 IWCOL: Write Collision Detect bit

- 1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy

- 0 = No collision

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

bit 6 I2COV: Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

## PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1         | Bit<br>24/16/8/0 |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-------------------|--------------------------|------------------|

| 04.04        | U-0               | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0              |

| 31:24        | _                 | _                    | _                 | _                 | _                 | _                 | _                        | _                |

| 00.40        | U-0               | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0                      | U-0              |

| 23:16        | —                 | —                    | —                 | _                 |                   |                   | —                        | _                |

| 45.0         | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0            |

| 15:8         | PTEN<1            | 5:14> <sup>(1)</sup> | PTEN<13:8>        |                   |                   |                   |                          |                  |

| 7.0          | R/W-0             | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                    | R/W-0            |

| 7:0          |                   | PTEN<7:2>            |                   |                   |                   |                   | PTEN<1:0> <sup>(2)</sup> |                  |

#### REGISTER 21-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

## Legend:

| Legenu.           |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-16 Unimplemented: Write '0'; ignore read

- bit 15-14 **PTEN<15:14>:** PMCSx Address Port Enable bits

- 1 = PMA15 and PMA14 function as either PMA<15:14> or PMCS2 and PMCS1<sup>(1)</sup>

- 0 = PMA15 and PMA14 function as port I/O

- bit 13-2 **PTEN<13:2>:** PMP Address Port Enable bits 1 = PMA<13:2> function as PMP address lines

- 0 = PMA<13:2> function as port I/O

- bit 1-0 **PTEN<1:0>:** PMALH/PMALL Address Port Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- Note 1: The use of these pins as PMA15/PMA14 or CS2/CS1 is selected by the CSF<1:0> bits (PMCON<7:6>).

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by the ADRMUX<1:0> bits in the PMCON register.

| Bit<br>Range | Bit<br>31/23/15/7       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |

|--------------|-------------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------------|------------------|

| 31:24        | U-0                     | U-0               | U-0               | U-0               | U-0                    | U-0               | R/W-0                  | R/W-0            |

| 31.24        | —                       | —                 | _                 | —                 | —                      | —                 | CAL<9                  | :8>              |

| 00.16        | R/W-0                   | R/W-0             | R/W-0             | R/W-0             | R/W-0                  | R/W-0             | R/W-0                  | R/W-0            |

| 23:16        |                         |                   |                   | CAL<              | :7:0>                  |                   |                        |                  |

| 15.0         | R/W-0                   | U-0               | R/W-0             | U-0               | U-0                    | U-0               | U-0                    | U-0              |

| 15:8         | ON <sup>(1,2)</sup>     | —                 | SIDL              | —                 | —                      | —                 | —                      | —                |

| 7:0          | R/W-0                   | R-0               | U-0               | U-0               | R/W-0                  | R-0               | R-0                    | R/W-0            |

| 7:0          | RTSECSEL <sup>(3)</sup> | RTCCLKON          | _                 | —                 | RTCWREN <sup>(4)</sup> | RTCSYNC           | HALFSEC <sup>(5)</sup> | RTCOE            |

|              |                         |                   |                   |                   |                        |                   |                        |                  |

#### REGISTER 22-1: RTCCON: RTC CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |  |

|-------------------|------------------|---------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |  |

#### bit 31-26 Unimplemented: Read as '0'

bit 25-16 CAL<9:0>: RTC Drift Calibration bits, which contain a signed 10-bit integer value 0111111111 = Maximum positive adjustment, adds 511 RTC clock pulses every one minute 000000001 = Minimum positive adjustment, adds 1 RTC clock pulse every one minute 000000000 = No adjustment 1111111111 = Minimum negative adjustment, subtracts 1 RTC clock pulse every one minute 100000000 = Maximum negative adjustment, subtracts 512 clock pulses every one minute ON: RTCC On bit<sup>(1,2)</sup> bit 15 1 = RTCC module is enabled 0 = RTCC module is disabled bit 14 Unimplemented: Read as '0' bit 13 SIDL: Stop in Idle Mode bit 1 = Disables the PBCLK to the RTCC when CPU enters in Idle mode 0 = Continue normal operation in Idle mode Unimplemented: Read as '0' bit 12-8 bit 7 RTSECSEL: RTCC Seconds Clock Output Select bit<sup>(3)</sup> 1 = RTCC Seconds Clock is selected for the RTCC pin 0 = RTCC Alarm Pulse is selected for the RTCC pin bit 6 RTCCLKON: RTCC Clock Enable Status bit 1 = RTCC Clock is actively running 0 = RTCC Clock is not running bit 5-4 Unimplemented: Read as '0' **Note 1:** The ON bit is only writable when RTCWREN = 1. 2: When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit. 3: Requires RTCOE = 1 (RTCCON<0>) for the output to be active. 4: The RTCWREN bit can be set only when the write sequence is enabled. 5: This bit is read-only. It is cleared to '0' on a write to the seconds bit fields (RTCTIME<14:8>).

Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                 | —                 | —                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 | —                 | _                 | —                 | —                 | _                | —                |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0             | U-0              | U-0              |

| 15:8         |                   | VCFG<2:0>         |                   | OFFCAL            | —                 | CSCNA             | —                | —                |

| 7:0          | R-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | BUFS              | _                 |                   | SMP               | I<3:0>            |                   | BUFM             | ALTS             |

#### REGISTER 23-2: AD1CON2: ADC CONTROL REGISTER 2

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

|-------------------|------------------|------------------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-13 VCFG<2:0>: Voltage Reference Configuration bits

|     | VREFH              | VREFL              |

|-----|--------------------|--------------------|

| 000 | AVDD               | AVss               |

| 001 | External VREF+ pin | AVss               |

| 010 | AVDD               | External VREF- pin |

| 011 | External VREF+ pin | External VREF- pin |

| 1xx | AVDD               | AVss               |

#### bit 12 OFFCAL: Input Offset Calibration Mode Select bit

#### 1 = Enable Offset Calibration mode

Positive and negative inputs of the sample and hold amplifier are connected to VREFL

#### 0 = Disable Offset Calibration mode

The inputs to the sample and hold amplifier are controlled by AD1CHS or AD1CSSL

#### bit 11 Unimplemented: Read as '0'

- bit 10 **CSCNA:** Input Scan Select bit

- 1 = Scan inputs

0 = Do not scan inputs

#### bit 9-8 **Unimplemented:** Read as '0'

bit 7 **BUFS:** Buffer Fill Status bit

Only valid when BUFM = 1.

1 = ADC is currently filling buffer 0x8-0xF, user should access data in 0x0-0x7

0 = ADC is currently filling buffer 0x0-0x7, user should access data in 0x8-0xF

#### bit 6 Unimplemented: Read as '0'

#### bit 5-2 SMPI<3:0>: Sample/Convert Sequences Per Interrupt Selection bits

```

1111 = Interrupts at the completion of conversion for each 16<sup>th</sup> sample/convert sequence

```

```

1110 = Interrupts at the completion of conversion for each 15<sup>th</sup> sample/convert sequence

```

- .

- •

0001 = Interrupts at the completion of conversion for each  $2^{nd}$  sample/convert sequence 0000 = Interrupts at the completion of conversion for each sample/convert sequence

#### bit 1 BUFM: ADC Result Buffer Mode Select bit

- 1 = Buffer configured as two 8-word buffers, ADC1BUF7-ADC1BUF0, ADC1BUFF-ADCBUF8

- 0 = Buffer configured as one 16-word buffer ADC1BUFF-ADC1BUF0

#### bit 0 ALTS: Alternate Input Sample Mode Select bit

- 1 = Uses Sample A input multiplexer settings for first sample, then alternates between Sample B and Sample A input multiplexer settings for all subsequent samples

- 0 = Always use Sample A input multiplexer settings

## 28.0 SPECIAL FEATURES

This data sheet summarizes the features Note: of the PIC32MX330/350/370/430/450/470 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Configuration" Section 32. (DS60001124) and Section 33. "Programming and **Diagnostics**" (DS60001129), which are available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32MX330/350/370/430/450/470 family of devices include several features intended to maximize application flexibility and reliability and minimize cost through elimination of external components. These are:

- · Flexible device configuration

- Joint Test Action Group (JTAG) interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

## 28.1 Configuration Bits

The Configuration bits can be programmed using the following registers to select various device configurations.

- DEVCFG0: Device Configuration Word 0

- DEVCFG1: Device Configuration Word 1

- DEVCFG2: Device Configuration Word 2

- DEVCFG3: Device Configuration Word 3

- · CFGCON: Configuration Control Register

In addition, the DEVID register (Register 28-6) provides device and revision information.

## 30.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

## 30.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

| DC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commerci} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industria} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |         |       |       |            |

|--------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics                                                                                                                                                                                                                                                                                                                                 | Min.    | Typical | Max.  | Units | Conditions |

| Operating Voltage  |        |                                                                                                                                                                                                                                                                                                                                                 |         |         |       |       |            |

| DC10               | Vdd    | Supply Voltage                                                                                                                                                                                                                                                                                                                                  | 2.3     | _       | 3.6   | V     | _          |

| DC12               | Vdr    | RAM Data Retention Voltage (Note 1)                                                                                                                                                                                                                                                                                                             | 1.75    | —       | _     | V     | _          |

| DC16               | VPOR   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal                                                                                                                                                                                                                                                                                | 1.75    | _       | 2.1   | V     | _          |

| DC17               | SVDD   | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal                                                                                                                                                                                                                                                                             | 0.00005 | _       | 0.115 | V/µs  | _          |

## TABLE 31-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

| DC CHA        | RACTE | RISTICS                           | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |   |                      |    |                                                                               |  |

|---------------|-------|-----------------------------------|------------------------------------------------------|---|----------------------|----|-------------------------------------------------------------------------------|--|

| Param.<br>No. | Symb. | Characteristics                   | tics Min. Typ. <sup>(1)</sup> Max. Units Conditions  |   | Conditions           |    |                                                                               |  |

|               |       | Input Leakage Current<br>(Note 3) |                                                      |   |                      |    |                                                                               |  |

| DI50          | lı∟   | I/O Ports                         | —                                                    | _ | <u>+</u> 1           | μA | $Vss \le VPIN \le VDD,$ Pin at high-impedance                                 |  |

| DI51          |       | Analog Input Pins                 | —                                                    | — | <u>+</u> 1           | μA | $Vss \le VPIN \le VDD,$<br>Pin at high-impedance                              |  |

| DI55          |       | MCLR <sup>(2)</sup>               | _                                                    |   | <u>+</u> 1           | μA | $Vss \leq V \text{PIN} \leq V \text{DD}$                                      |  |

| DI56          |       | OSC1                              | —                                                    | — | <u>+</u> 1           | μA | $VSS \le VPIN \le VDD,$<br>XT and HS modes                                    |  |

|               |       |                                   |                                                      |   |                      |    | Pins with Analog functions.<br>Exceptions: [N/A] = 0 mA<br>max                |  |

| DI60a         | licl  | Input Low Injection<br>Current    | 0                                                    | _ | <sub>-5</sub> (7,10) | mA | Digital 5V tolerant desig-<br>nated pins. Exceptions:<br>[N/A] = 0 mA max     |  |

|               |       |                                   |                                                      |   |                      |    | Digital non-5V tolerant desig-<br>nated pins. Exceptions:<br>[N/A] = 0 mA max |  |

#### TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

- 7: VIL source < (VSS 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- **10:** Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (Vss 0.3)).

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

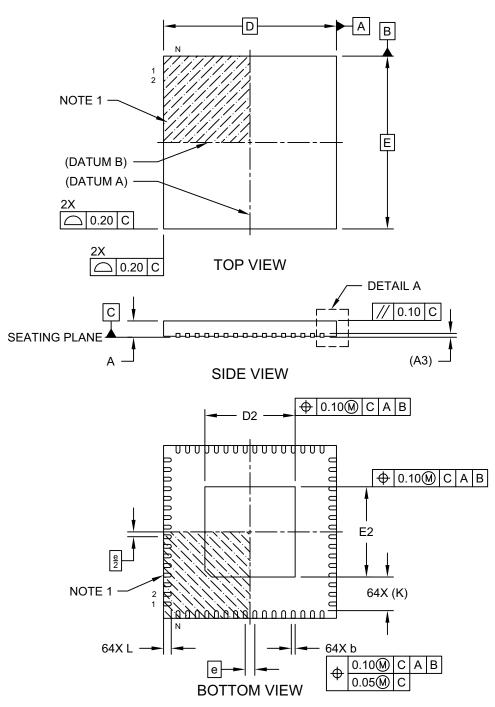

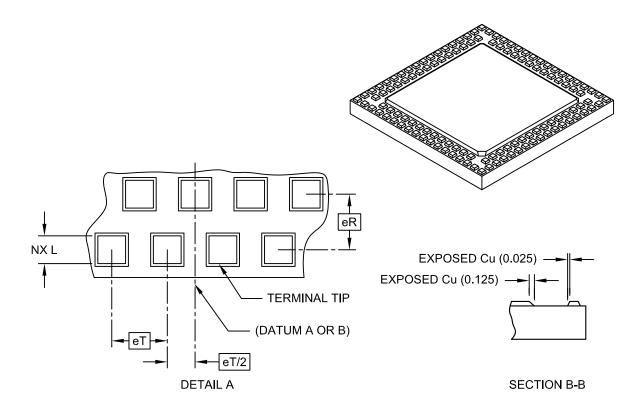

# 64-Terminal Plastic Quad Flat Pack, No Lead (RG) 9x9x0.9 mm Body [QFN] Saw Singulated

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

Microchip Technology Drawing C04-260A Sheet 1 of 2

## 124-Terminal Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                                      | MILLIMETERS |          |      |      |  |

|--------------------------------------|-------------|----------|------|------|--|

| Dimension                            | Limits      | MIN      | NOM  | MAX  |  |

| Number of Pins                       | N           | 124      |      |      |  |

| Pitch                                | еT          | 0.50 BSC |      |      |  |

| Pitch (Inner to outer terminal ring) | eR          | 0.50 BSC |      |      |  |

| Overall Height                       | Α           | 0.80     | 0.85 | 0.90 |  |

| Standoff                             | A1          | 0.00     | -    | 0.05 |  |

| Overall Width                        | E           | 9.00 BSC |      |      |  |

| Exposed Pad Width                    | E2          | 6.40     | 6.55 | 6.70 |  |

| Overall Length                       | D           | 9.00 BSC |      |      |  |

| Exposed Pad Length                   | D2          | 6.40     | 6.55 | 6.70 |  |

| Contact Width                        | b           | 0.20     | 0.25 | 0.30 |  |

| Contact Length                       | L           | 0.20     | 0.25 | 0.30 |  |

| Contact-to-Exposed Pad               | K           | 0.20     | -    | -    |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-193A Sheet 2 of 2

## **Revision E (October 2015)**

This revision includes the following updates, as listed in Table A-4.

## TABLE A-4: MAJOR SECTION UPDATES

| Section                                                  | Update Description                                                             |  |  |

|----------------------------------------------------------|--------------------------------------------------------------------------------|--|--|

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs" | Section 2.10 "Sosc Design Recommendations" was removed.                        |  |  |

| 31.0 "Electrical<br>Characteristics"                     | The Power-Down Current (IPD) DC Characteristics were updated (see Table 31-7). |  |  |

## **Revision F (September 2016)**

This revision includes the following updates, as listed in Table A-5.

## TABLE A-5: MAJOR SECTION UPDATES

| Section                                                    | Update Description                                                                                                                                                                                             |

|------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up<br>to 512 KB Flash and 128 KB | The PIC32MX450F128HB and PIC32MX470F512LB devices and Note 4 were added to the family features table (see Table 1).                                                                                            |

| SRAM) with Audio/                                          | Note 2 in the 64-pin device pin table was updated (see Table 2).                                                                                                                                               |

| Graphics/Touch (HMI), USB,<br>and Advanced Analog"         | Note 2 in the 64-pin device pin table was updated and Note 4 was removed (see Table 3).                                                                                                                        |

|                                                            | Note 2 and Note 3 in the 100-pin device pin table was updated (see Table 4).                                                                                                                                   |

|                                                            | Note 3 in the 124-pin device pin table was updated (see Table 6).                                                                                                                                              |

|                                                            | Note 2 in the 124-pin device pin table was updated (see Table 7).                                                                                                                                              |

|                                                            | RPF3 was removed from USB devices (see Table 3, Table 5, and Table 7).                                                                                                                                         |

| 1.0 "Device Overview"                                      | The Pinout I/O Descriptions for pins $\overline{\text{U5CTS}}$ , $\overline{\text{U5RTS}}$ , $\overline{\text{U5RX}}$ , and $\overline{\text{U5TX}}$ in 64-pin QFN/TQFP packages were updated (see Table 1-1). |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"   | 2.10 "EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations" was added.                                                                                                                     |

| 8.0 "Oscillator                                            | The Clock Diagram was updated (see Figure 8-1).                                                                                                                                                                |

| Configuration"                                             | The Center Frequency values in the TUN<5:0> bits (OSCTUN<5:0>) were updated (see Register 8-2).                                                                                                                |

| 12.0 "I/O Ports"                                           | Note references in the Input Pin Selection table were updated (see Table 12-1).                                                                                                                                |

|                                                            | Note references in the Output Pin Selection table were updated (see Table 12-2).                                                                                                                               |

|                                                            | PORTF Register Maps were updated (see Table 12-11 and Table 12-3).                                                                                                                                             |

|                                                            | Note 1 was added to the Peripheral Pin Select Input Register Map (see Table 12-17).                                                                                                                            |

| 31.0 "Electrical                                           | The conditions for parameter DI60b (IICH) were updated (see Table 31-8).                                                                                                                                       |

| Characteristics"                                           | Parameter DO50a (Csosc) was removed.                                                                                                                                                                           |

|                                                            | The maximum value for parameter OS10 (Fosc) was updated (see Table 31-18).                                                                                                                                     |

|                                                            | Parameter PM7 (TDHOLD) was updated (see Table 31-39).                                                                                                                                                          |

|                                                            | Note 1 was added to the DC Characteristics: Program Memory (see Table 31-12).                                                                                                                                  |

| 33.0 "Packaging<br>Information"                            | The Land Pattern for 64-pin QFN packages was updated.                                                                                                                                                          |

| "Product Identification<br>System"                         | The Software Targeting category was added.                                                                                                                                                                     |