Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                            |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 120MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 81                                                                                |

| Program Memory Size        | 256KB (256K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 64K x 8                                                                           |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 28x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 100-TQFP                                                                          |

| Supplier Device Package    | 100-TQFP (14x14)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256lt-120-pf |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 3: PIN NAMES FOR 64-PIN DEVICES

#### 64-PIN $QFN^{(1,2)}$ AND $TQFP^{(1,2)}$ (TOP VIEW) PIC32MX430F064H PIC32MX450F128H PIC32MX450F256H PIC32MX470F512H 64 1 64 $QFN^{(3)}$ TQFP Pin # Full Pin Name Pin # **Full Pin Name** 1 AN22/RPE5/PMD5/RE5 33 USBID/RF3 2 AN23/PMD6/RE6 34 VBUS AN27/PMD7/RE7 3 35 VUSB3V3 4 AN16/C1IND/RPG6/SCK2/PMA5/RG6 D-36 5 AN17/C1INC/RPG7/PMA4/RG7 37 D+ AN18/C2IND/RPG8/PMA3/RG8 6 38 Vdd MCLR 7 OSC1/CLKI/RC12 39 AN19/C2INC/RPG9/PMA2/RG9 40 OSC2/CLKO/RC15 8 Vss 41 9 Vss RPD8/RTCC/RD8 10 VDD 42 AN5/C1INA/RPB5/VBUSON/RB5 11 43 RPD9/SDA1/RD9 12 AN4/C1INB/RB4 44 RPD10/SCL1/PMCS2/RD10 13 PGED3/AN3/C2INA/RPB3/RB3 45 RPD11/PMCS1/RD11 14 PGEC3/AN2/C2INB/RPB2/CTED13/RB2 46 RPD0/INT0/RD0 PGEC1/VREF-/CVREF-/AN1/RPB1/CTED12/RB1 47 SOSCI/RPC13/RC13 15 16 PGED1/VREF+/CVREF+/AN0/RPB0/PMA6/RB0 48 SOSCO/RPC14/T1CK/RC14 PGEC2/AN6/RPB6/RB6 17 49 AN24/RPD1/RD1 18 PGED2/AN7/RPB7/CTED3//RB7 AN25/RPD2/SCK1/RD2 50 AN26/RPD3/RD3 19 AVDD 51 20 52 RPD4/PMWR/RD4 AVss 21 AN8/RPB8/CTED10//RB8 RPD5/PMRD/RD5 53 22 AN9/RPB9/CTED4/PMA7/RB9 54 RD6 TMS/CVREFOUT/AN10/RPB10/CTED11//PMA13/RB10 RD7 23 55 TDO/AN11/PMA12/RB11 56 VCAP 24 Vss 25 57 Vdd 26 Vdd 58 RPF0/RF0 27 TCK/AN12/PMA11/RB12 59 RPF1/RF1 28 TDI/AN13/PMA10/RB13 60 PMD0/RE0 AN14/RPB14/CTED5/PMA1/RB14 61 PMD1/RE1 29 AN15/RPB15/OCFB/CTED6/PMA0/RB15 AN20/PMD2/RE2 30 62 RPF4/SDA2/PMA9/RF4 63 RPE3/CTPLS/PMD3/RE3 31 32 RPF5/SCL2/PMA8/RF5 64 AN21/PMD4/RE4

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

# PIC32MX330/350/370/430/450/470

| Pin Numb                              | er                                      |                                               |                |                                                     |  |  |  |

|---------------------------------------|-----------------------------------------|-----------------------------------------------|----------------|-----------------------------------------------------|--|--|--|

| 100-pin<br>TQFP                       | 124-pin<br>VTLA                         | Pin<br>Type                                   | Buffer<br>Type | Description                                         |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             |                                                     |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             |                                                     |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             | Capture Input 1-5                                   |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             |                                                     |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             |                                                     |  |  |  |

| PPS                                   | PPS                                     | 0                                             | ST             | Output Compare Output 1                             |  |  |  |

| PPS                                   | PPS                                     | 0                                             | ST             | Output Compare Output 2                             |  |  |  |

| PPS                                   | PPS                                     | 0                                             | ST             | Output Compare Output 3                             |  |  |  |

| PPS                                   | PPS                                     | 0                                             | ST             | Output Compare Output 4                             |  |  |  |

| PPS                                   | PPS                                     | 0                                             | ST             | Output Compare Output 5                             |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             | Output Compare Fault A Input                        |  |  |  |

| 44                                    | A29                                     | Ι                                             | ST             | Output Compare Fault B Input                        |  |  |  |

| 55 <sup>(1)</sup> , 72 <sup>(2)</sup> | B30 <sup>(1)</sup> , B39 <sup>(2)</sup> | Ι                                             | ST             | External Interrupt 0                                |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             | External Interrupt 1                                |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             | External Interrupt 2                                |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             | External Interrupt 3                                |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             | External Interrupt 4                                |  |  |  |

| 17                                    | B9                                      | I/O                                           | ST             |                                                     |  |  |  |

| 38                                    | A26                                     | I/O                                           | ST             |                                                     |  |  |  |

| 58                                    | A39                                     | I/O                                           | ST             |                                                     |  |  |  |

| 59                                    | B32                                     | I/O                                           | ST             |                                                     |  |  |  |

| 60                                    | A40                                     | I/O                                           | ST             |                                                     |  |  |  |

| 61                                    | B33                                     | I/O                                           | ST             | PORTA is a bidirectional I/O port                   |  |  |  |

| 91                                    | B51                                     | I/O                                           | ST             |                                                     |  |  |  |

| 92                                    | A62                                     | I/O                                           | ST             | ]                                                   |  |  |  |

| 28                                    | A21                                     | I/O                                           | ST             | ]                                                   |  |  |  |

| 29                                    | B17                                     | I/O                                           | ST             | ]                                                   |  |  |  |

| 66                                    | B36                                     | I/O                                           | ST             | ]                                                   |  |  |  |

| 67                                    | A44                                     | I/O                                           | ST             | ]                                                   |  |  |  |

|                                       | 66<br>67<br>OS compat                   | 66 B36<br>67 A44<br>OS compatible input or ou | 66 B36 I/O     | 66B36I/OST67A44I/OSTOS compatible input or outputAn |  |  |  |

#### TABLE 1-1. PINOUT I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

O = Output

I = Input

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices.

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS50001765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS50001764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" DS50001616

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) DS50001749

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 Trace

The trace pins can be connected to a hardware trace-enabled programmer to provide a compressed real-time instruction trace. When used for trace, the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

# 2.8 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

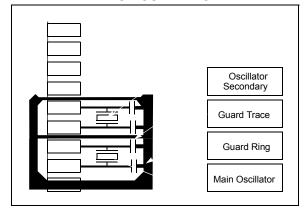

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 5.1 Control Registers

# TABLE 5-1: FLASH CONTROLLER REGISTER MAP

| ess                         |                        | 0         |       | Bits                                                                                      |       |       |       |       |      |           |          |      | 6    |      |      |      |      |      |            |

|-----------------------------|------------------------|-----------|-------|-------------------------------------------------------------------------------------------|-------|-------|-------|-------|------|-----------|----------|------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name       | Bit Range | 31/15 | 30/14                                                                                     | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8      | 23/7     | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| E400                        | NVMCON <sup>(1)</sup>  | 31:16     |       |                                                                                           | —     | —     | _     |       | —    | —         |          | —    | —    | —    | —    | —    | —    |      | 0000       |

| 1400                        | NVINCON /              | 15:0      | WR    | WR      WRER      LVDERR      LVDSTAT      —      —      —      —      —      —      0000 |       |       |       |       |      |           |          |      |      |      |      |      |      |      |            |

| F410                        | NVMKEY                 | 31:16     |       | NVMKEY<31:0>                                                                              |       |       |       |       |      |           |          |      | 0000 |      |      |      |      |      |            |

|                             |                        | 15:0      |       | 0000                                                                                      |       |       |       |       |      |           |          |      | 0000 |      |      |      |      |      |            |

| E420                        | NVMADDR <sup>(1)</sup> | 31:16     |       |                                                                                           |       |       |       |       |      | NVMADE    | D-31.05  |      |      |      |      |      |      |      | 0000       |

| 1 420                       | NVINADDIX              | 15:0      |       |                                                                                           |       |       |       |       |      | INVINADL  | 11-31.02 |      |      |      |      |      |      |      | 0000       |

| F430                        | NVMDATA                | 31:16     |       |                                                                                           |       |       |       |       |      | NVMDAT    | A-21:0>  |      |      |      |      |      |      |      | 0000       |

| F430                        | NVINDATA               | 15:0      |       |                                                                                           |       |       |       |       |      | INVIVIDAI | A<31.0>  |      |      |      |      |      |      |      | 0000       |

| F440                        | NVMSRC                 | 31:16     |       |                                                                                           |       |       |       |       |      |           | 221.05   |      |      |      |      |      |      |      | 0000       |

| F440                        | ADDR                   | 15:0      |       | NVMSRCADDR<31:0>                                                                          |       |       |       |       |      |           | 0000     |      |      |      |      |      |      |      |            |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 | _                | —                    |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 23:16        | _                 | —                 | —                 | _                 | _                 | —                 | —                | —                    |  |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |  |

| 15:8         | —                 | _                 | _                 | _                 | _                 | —                 |                  | —                    |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |  |

| 7:0          |                   |                   |                   | _                 |                   | _                 | _                | SWRST <sup>(1)</sup> |  |

# REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:           | HC = Cleared by hardware |                                    |                    |  |  |  |

|-------------------|--------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup>

- 1 = Enable software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7         | Bit<br>30/22/14/6            | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1  | Bit<br>24/16/8/0 |  |  |  |

|--------------|---------------------------|------------------------------|-------------------|-------------------|---------------------|-------------------|-------------------|------------------|--|--|--|

| 04.04        | U-0                       | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0            |  |  |  |

| 31:24        |                           | RODIV<14:8> <sup>(1,3)</sup> |                   |                   |                     |                   |                   |                  |  |  |  |

| 00.40        | R/W-0                     | R/W-0                        | R/W-0             | R/W-0             | R/W-0               | R/W-0             | R/W-0             | R/W-0            |  |  |  |

| 23:16        | RODIV<7:0> <sup>(3)</sup> |                              |                   |                   |                     |                   |                   |                  |  |  |  |

| 45.0         | R/W-0                     | U-0                          | R/W-0             | R/W-0             | R/W-0               | U-0               | R/W-0, HC         | R-0, HS, HC      |  |  |  |

| 15:8         | ON                        | _                            | SIDL              | OE                | RSLP <sup>(2)</sup> | —                 | DIVSWEN           | ACTIVE           |  |  |  |

|              | U-0                       | U-0                          | U-0               | U-0               | R/W-0               | R/W-0             | R/W-0             | R/W-0            |  |  |  |

| 7:0          |                           | _                            | _                 | _                 |                     | ROSEL             | -<3:0> <b>(1)</b> |                  |  |  |  |

### **REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER**

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |  |

|-------------------|-------------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |  |

- bit 31 Unimplemented: Read as '0'

- bit 30-16 **RODIV<14:0>:** Reference Clock Divider bits<sup>(1,3)</sup> This value selects the Reference Clock Divider bits. See Figure 8-1 for more information. bit 15 **ON:** Output Enable bit 1 = Reference Oscillator Module is enabled 0 = Reference Oscillator Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Peripheral Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12 OE: Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator Module output continues to run in Sleep

- 0 = Reference Oscillator Module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

# PIC32MX330/350/370/430/450/470

#### REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6     | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3  | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0    |

|--------------|-------------------|-----------------------|-------------------|-------------------|--------------------|-------------------|------------------|---------------------|

| 24.24        | U-0               | U-0                   | R/W-0             | R/W-0             | R/W-0              | U-0               | U-0              | R/W-0               |

| 31:24        | —                 | —                     | BYTC              | <1:0>             | WBO <sup>(1)</sup> | _                 | _                | BITO <sup>(1)</sup> |

| 00.40        | U-0               | U-0                   | U-0               | U-0               | U-0                | U-0               | U-0              | U-0                 |

| 23:16        | —                 | —                     | —                 | _                 | _                  | _                 | _                | -                   |

| 45.0         | U-0               | U-0                   | U-0               | R/W-0             | R/W-0              | R/W-0             | R/W-0            | R/W-0               |

| 15:8         | —                 | _                     | _                 |                   |                    | PLEN<4:0>         |                  |                     |

| 7.0          | R/W-0             | R/W-0                 | R/W-0             | U-0               | U-0                | R/W-0             | R/W-0            | R/W-0               |

| 7:0          | CRCEN             | CRCAPP <sup>(1)</sup> | CRCTYP            |                   | _                  | (                 | CRCCH<2:0>       |                     |

## Legend:

| Legena.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-30 Unimplemented: Read as '0'

- bit 29-28 BYTO<1:0>: CRC Byte Order Selection bits

- 11 = Endian byte swap on half-word boundaries (i.e., source half-word order with reverse source byte order per half-word)

- 10 = Swap half-words on word boundaries (i.e., reverse source half-word order with source byte order per half-word)

- 01 = Endian byte swap on word boundaries (i.e., reverse source byte order)

- 00 = No swapping (i.e., source byte order)

- bit 27 **WBO:** CRC Write Byte Order Selection bit<sup>(1)</sup>

- 1 = Source data is written to the destination re-ordered as defined by BYTO<1:0>

- 0 = Source data is written to the destination unaltered

- bit 26-25 Unimplemented: Read as '0'

- bit 24 BITO: CRC Bit Order Selection bit<sup>(1)</sup>

When CRCTYP (DCRCCON<15>) = 1 (CRC module is in IP Header mode):

- 1 = The IP header checksum is calculated Least Significant bit (LSb) first (i.e., reflected)

- 0 = The IP header checksum is calculated Most Significant bit (MSb) first (i.e., not reflected)

#### <u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode):

- 1 = The LFSR CRC is calculated Least Significant bit first (i.e., reflected)

- 0 = The LFSR CRC is calculated Most Significant bit first (i.e., not reflected)

#### bit 23-13 Unimplemented: Read as '0'

bit 12-8 **PLEN<4:0>:** Polynomial Length bits<sup>(1)</sup>

<u>When CRCTYP (DCRCCON<15>) = 1</u> (CRC module is in IP Header mode): These bits are unused.

<u>When CRCTYP (DCRCCON<15>) = 0</u> (CRC module is in LFSR mode): Denotes the length of the polynomial - 1.

- bit 7 CRCEN: CRC Enable bit

- 1 = CRC module is enabled and channel transfers are routed through the CRC module

- 0 = CRC module is disabled and channel transfers proceed normally

- Note 1: When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

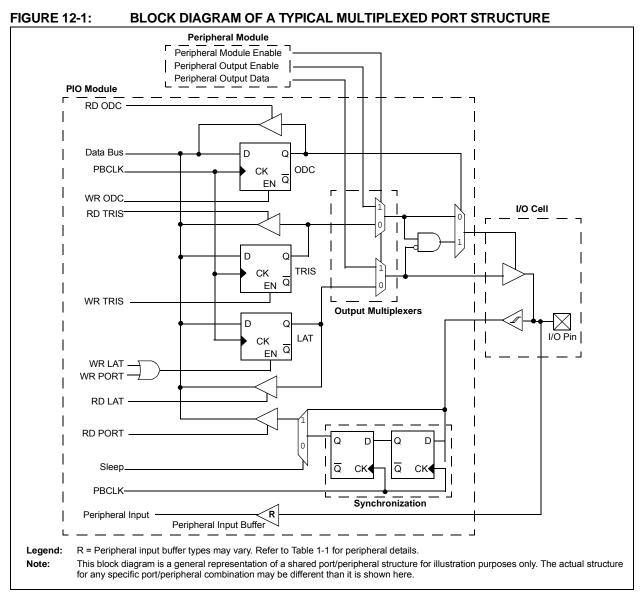

# 12.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate function(s). These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin. Following are key features of this module:

- · Individual output pin open-drain enable/disable

- · Individual input pin weak pull-up and pull-down

- Monitor selective inputs and generate interrupt when change in pin state is detected

- Operation during CPU Sleep and Idle modes

- Fast bit manipulation using CLR, SET, and INV registers

Figure 12-1 illustrates a block diagram of a typical multiplexed I/O port.

| Peripheral Pin | [pin name]R SFR      | [pin name]R bits | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection        |  |

|----------------|----------------------|------------------|-----------------------------------------------------------|--|

| INT1           | INT1R                | INT1R<3:0>       | 0000 = RPD1<br>0001 = RPG9                                |  |

| ТЗСК           | T3CKR                | T3CKR<3:0>       | 0010 = RPB14<br>0011 = RPD0                               |  |

| IC1            | IC1R                 | IC1R<3:0>        | 0100 = RPD8<br>0101 = RPB6                                |  |

| U3CTS          | U3CTSR               | U3CTSR<3:0>      | 0110 = RPD5<br>0111 = RPB2                                |  |

| U4RX           | U4RXR                | U4RXR<3:0>       | 1000 = RPF3 <sup>(4)</sup><br>1001 = RPF13 <sup>(3)</sup> |  |

| U5RX           | U5RXR <sup>(3)</sup> | U5RXR<3:0>       | 1010 = Reserved<br>1011 = RPF2 <sup>(1)</sup>             |  |

| SS2            | SS2R                 | SS2R<3:0>        | 1100 = RPC2 <sup>(3)</sup><br>1101 = RPE8 <sup>(3)</sup>  |  |

| OCFA           | OCFAR                | OCFAR<3:0>       | 1110 = Reserved<br>1111 = Reserved                        |  |

# TABLE 12-1:INPUT PIN SELECTION (CONTINUED)

Note 1: This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

3: This selection is not available on 64-pin USB and General Purpose devices.

4: This selection is only available on General Purpose devices.

NOTES:

#### REGISTER 20-1: UxMODE: UARTx MODE REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | _                 | _                 | _                 | —                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | _                 | _                 | —                 | -                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R/W-0            | R/W-0            |

| 15:8         | 0N <sup>(1)</sup> | —                 | SIDL              | IREN              | RTSMD             | _                 | UEN              | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAKE              | LPBACK            | ABAUD             | RXINV             | BRGH              | PDSEL             | <1:0>            | STSEL            |

## Legend:

| Legena.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** UARTx Enable bit<sup>(1)</sup>

- 1 = UARTx is enabled. UARTx pins are controlled by UARTx as defined by UEN<1:0> and UTXEN control bits

- UARTx is disabled. All UARTx pins are controlled by corresponding bits in the PORTx, TRISx and LATx registers; UARTx power consumption is minimal

#### bit 14 Unimplemented: Read as '0'

- bit 13 SIDL: Stop in Idle Mode bit

- 1 = Discontinue operation when device enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12 IREN: IrDA Encoder and Decoder Enable bit

- 1 = IrDA is enabled

- 0 = IrDA is disabled

- bit 11 **RTSMD:** Mode Selection for UxRTS Pin bit

- 1 =  $\overline{\text{UxRTS}}$  pin is in Simplex mode

- $0 = \overline{\text{UxRTS}}$  pin is in Flow Control mode

#### bit 10 Unimplemented: Read as '0'

#### bit 9-8 UEN<1:0>: UARTx Enable bits

- 11 = UxTX, UxRX and UxBCLK pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 10 = UxTX, UxRX,  $\overline{\text{UxCTS}}$  and  $\overline{\text{UxRTS}}$  pins are enabled and used

- 01 = UxTX, UxRX and UxRTS pins are enabled and used; UxCTS pin is controlled by corresponding bits in the PORTx register

- 00 = UxTX and UxRX pins are enabled and used; UxCTS and UxRTS/UxBCLK pins are controlled by corresponding bits in the PORTx register

- bit 7 WAKE: Enable Wake-up on Start bit Detect During Sleep Mode bit

- 1 = Wake-up is enabled

- 0 = Wake-up is disabled

- bit 6 LPBACK: UARTx Loopback Mode Select bit

- 1 = Loopback mode is enabled

- 0 = Loopback mode is disabled

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04-04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

|              | —                 | _                 | -                 | —                 | _                 | _                 | -                | —                |

| 15:8         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

|              | IBF               | IBOV              | _                 | —                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7:0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

|              | OBE               | OBUF              |                   | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

#### REGISTER 21-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | HS = Set by Hardware | SC = Cleared by software           |                    |  |

|-------------------|----------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 IBF: Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)0 = No overflow occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 **IBxF:** Input Buffer 'x' Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

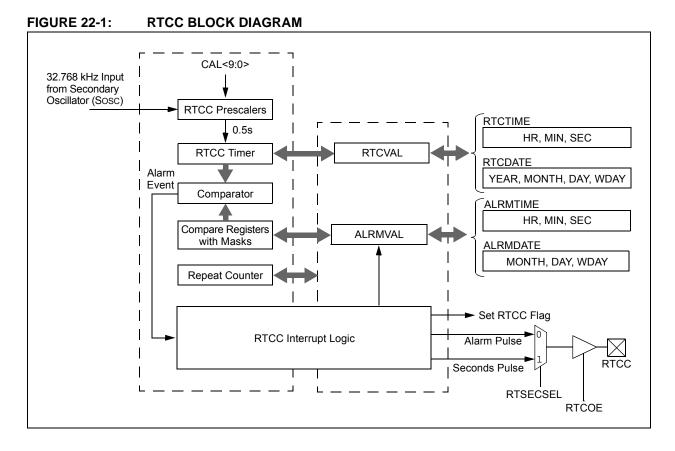

# 22.0 REAL-TIME CLOCK AND CALENDAR (RTCC)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32 RTCC module is intended for applications in which accurate time must be maintained for extended periods of time with minimal or no CPU intervention. Low-power optimization provides extended battery lifetime while keeping track of time. The following are key features of this module:

- · Time: hours, minutes and seconds

- 24-hour format (military time)

- · Visibility of one-half second period

- Provides calendar: Weekday, date, month and year

- Alarm intervals are configurable for half of a second, one second, 10 seconds, one minute, 10 minutes, one hour, one day, one week, one month and one year

- · Alarm repeat with decrementing counter

- · Alarm with indefinite repeat: Chime

- Year range: 2000 to 2099

- · Leap year correction

- · BCD format for smaller firmware overhead

- Optimized for long-term battery operation

- · Fractional second synchronization

- User calibration of the clock crystal frequency with auto-adjust

- Calibration range: ±0.66 seconds error per month

- · Calibrates up to 260 ppm of crystal error

- Requirements: External 32.768 kHz clock crystal

- Alarm pulse or seconds clock output on RTCC pin

# © 2012-2016 Microchip Technology Inc.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5   | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | —                 | —                   | _                 | —                 | _                 | —                | —                |

| 23:16        | U-0               | U-0               | U-0                 | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 | _                   | -                 | _                 | _                 | _                | —                |

| 15:8         | R/W-0             | R/W-0             | R/W-0               | U-0               | U-0               | U-0               | U-0              | R-0              |

|              | ON <sup>(1)</sup> | COE               | CPOL <sup>(2)</sup> | _                 | —                 | _                 | —                | COUT             |

| 7:0          | R/W-1             | R/W-1             | U-0                 | R/W-0             | U-0               | U-0               | R/W-1            | R/W-1            |

|              | EVPOL<1:0>        |                   | _                   | CREF              | _                 | _                 | CCH              | <1:0>            |

#### REGISTER 24-1: CMxCON: COMPARATOR CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator ON bit<sup>(1)</sup>

- 1 = Module is enabled. Setting this bit does not affect the other bits in this register

- 0 = Module is disabled and does not consume current. Clearing this bit does not affect the other bits in this register

- bit 14 **COE:** Comparator Output Enable bit

- 1 = Comparator output is driven on the output CxOUT pin

- 0 = Comparator output is not driven on the output CxOUT pin

- bit 13 **CPOL:** Comparator Output Inversion bit<sup>(2)</sup>

- 1 = Output is inverted

- 0 = Output is not inverted

- bit 12-9 Unimplemented: Read as '0'

- bit 8 **COUT:** Comparator Output bit

- 1 =Output of the Comparator is a '1'

- 0 = Output of the Comparator is a '0'

- bit 7-6 EVPOL<1:0>: Interrupt Event Polarity Select bits

- 11 = Comparator interrupt is generated on a low-to-high or high-to-low transition of the comparator output

- 10 = Comparator interrupt is generated on a high-to-low transition of the comparator output

- 01 = Comparator interrupt is generated on a low-to-high transition of the comparator output

- 00 = Comparator interrupt generation is disabled

- bit 5 Unimplemented: Read as '0'

#### bit 4 **CREF:** Comparator Positive Input Configure bit

- 1 = Comparator non-inverting input is connected to the internal CVREF

- 0 = Comparator non-inverting input is connected to the CXINA pin

#### bit 3-2 Unimplemented: Read as '0'

- bit 1-0 CCH<1:0>: Comparator Negative Input Select bits for Comparator

- 11 = Comparator inverting input is connected to the IVREF

- 10 = Comparator inverting input is connected to the CxIND pin

- 01 = Comparator inverting input is connected to the CxINC pin

- 00 = Comparator inverting input is connected to the CxINB pin

- **Note 1:** When using the 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: Setting this bit will invert the signal to the comparator interrupt generator as well. This will result in an interrupt being generated on the opposite edge from the one selected by EVPOL<1:0>.

NOTES:

The processor will exit, or 'wake-up', from Sleep on one of the following events:

- On any interrupt from an enabled source that is operating in Sleep. The interrupt priority must be greater than the current CPU priority.

- · On any form of device Reset

- On a WDT time-out

If the interrupt priority is lower than or equal to the current priority, the CPU will remain Halted, but the PBCLK will start running and the device will enter into Idle mode.

# 27.3.2 IDLE MODE

In Idle mode, the CPU is Halted but the System Clock (SYSCLK) source is still enabled. This allows peripherals to continue operation when the CPU is Halted. Peripherals can be individually configured to Halt when entering Idle by setting their respective SIDL bit. Latency, when exiting Idle mode, is very low due to the CPU oscillator source remaining active.

- Note 1: Changing the PBCLK divider ratio requires recalculation of peripheral timing. For example, assume the UART is configured for 9600 baud with a PB clock ratio of 1:1 and a Posc of 8 MHz. When the PB clock divisor of 1:2 is used, the input frequency to the baud clock is cut in half; therefore, the baud rate is reduced to 1/2 its former value. Due to numeric truncation in calculations (such as the baud rate divisor), the actual baud rate may be a tiny percentage different than expected. For this reason, any timing calculation required for a peripheral should be performed with the new PB clock frequency instead of scaling the previous value based on a change in the PB divisor ratio.

- 2: Oscillator start-up and PLL lock delays are applied when switching to a clock source that was disabled and that uses a crystal and/or the PLL. For example, assume the clock source is switched from Posc to LPRC just prior to entering Sleep in order to save power. No oscillator startup delay would be applied when exiting Idle. However, when switching back to Posc, the appropriate PLL and/or oscillator start-up/lock delays would be applied.

The device enters Idle mode when the SLPEN bit (OSCCON<4>) is clear and a  $\tt WAIT$  instruction is executed.

The processor will wake or exit from Idle mode on the following events:

- On any interrupt event for which the interrupt source is enabled. The priority of the interrupt event must be greater than the current priority of the CPU. If the priority of the interrupt event is lower than or equal to current priority of the CPU, the CPU will remain Halted and the device will remain in Idle mode.

- On any form of device Reset

- On a WDT time-out interrupt

#### 27.3.3 PERIPHERAL BUS SCALING METHOD

Most of the peripherals on the device are clocked using the PBCLK. The peripheral bus can be scaled relative to the SYSCLK to minimize the dynamic power consumed by the peripherals. The PBCLK divisor is controlled by PBDIV<1:0> (OSCCON<20:19>), allowing SYSCLK to PBCLK ratios of 1:1, 1:2, 1:4 and 1:8. All peripherals using PBCLK are affected when the divisor is changed. Peripherals such as the USB, Interrupt Controller, DMA, and the bus matrix are clocked directly from SYSCLK. As a result, they are not affected by PBCLK divisor changes.

Changing the PBCLK divisor affects:

- The CPU to peripheral access latency. The CPU has to wait for next PBCLK edge for a read to complete. In 1:8 mode, this results in a latency of one to seven SYSCLKs.

- The power consumption of the peripherals. Power consumption is directly proportional to the frequency at which the peripherals are clocked. The greater the divisor, the lower the power consumed by the peripherals.

To minimize dynamic power, the PB divisor should be chosen to run the peripherals at the lowest frequency that provides acceptable system performance. When selecting a PBCLK divider, peripheral clock requirements, such as baud rate accuracy, should be taken into account. For example, the UART peripheral may not be able to achieve all baud rate values at some PBCLK divider depending on the SYSCLK value.

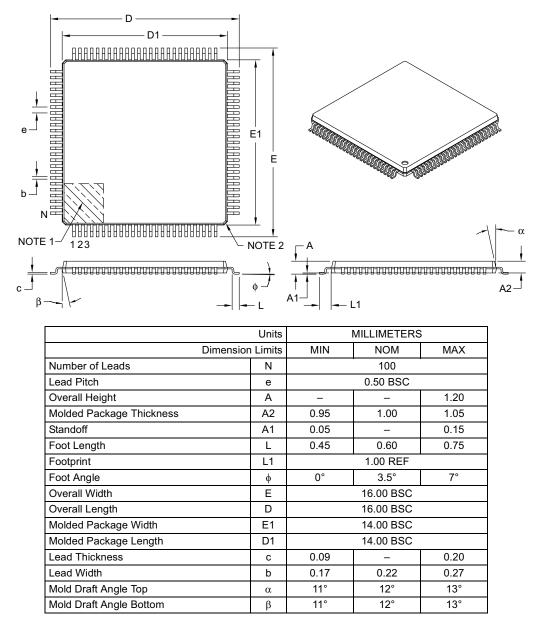

## 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B

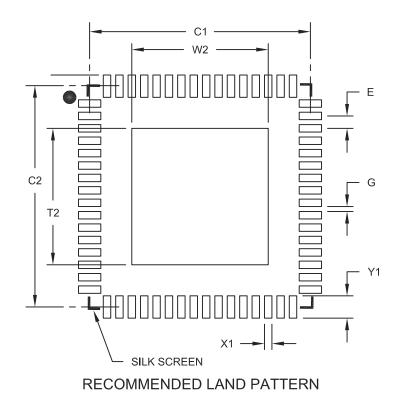

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body [QFN] With 0.40 mm Contact Length and 5.40x5.40mm Exposed Pad

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | MILLIMETERS |          |      |      |

|----------------------------|-------------|----------|------|------|

| Dimension Limits           |             | MIN      | NOM  | MAX  |

| Contact Pitch              | E           | 0.50 BSC |      |      |

| Optional Center Pad Width  | W2          |          |      | 5.50 |

| Optional Center Pad Length | T2          |          |      | 5.50 |

| Contact Pad Spacing        | C1          |          | 8.90 |      |

| Contact Pad Spacing        | C2          |          | 8.90 |      |

| Contact Pad Width (X64)    | X1          |          |      | 0.30 |

| Contact Pad Length (X64)   | Y1          |          |      | 0.85 |

| Distance Between Pads      | G           | 0.20     |      |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2154A

# PIC32MX330/350/370/430/450/470

NOTES:

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support