Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256lt-i-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Device Pin Tables**

| 64-      | -PIN QFN <sup>(1,2,3,4)</sup> AND TQFP <sup>(1,2,3,4)</sup> (TOP VII | EW)              |                       |

|----------|----------------------------------------------------------------------|------------------|-----------------------|

| Pl<br>Pl | C32MX330F064H<br>C32MX350F128H<br>C32MX350F256H<br>C32MX370F512H     |                  |                       |

|          | 64                                                                   | 1                | 64                    |

|          | QF                                                                   | N <sup>(4)</sup> | TQFP                  |

| Pin #    | Full Pin Name                                                        | Pin #            | Full Pin Name         |

| 1        | AN22/RPE5/PMD5/RE5                                                   | 33               | RPF3/RF3              |

| 2        | AN23/PMD6/RE6                                                        | 34               | RPF2/RF2              |

| 3        | AN27/PMD7/RE7                                                        | 35               | RPF6/SCK1/INT0/RF6    |

| 4        | AN16/C1IND/RPG6/SCK2/PMA5/RG6                                        | 36               | SDA1/RG3              |

| 5        | AN17/C1INC/RPG7/PMA4/RG7                                             | 37               | SCL1/RG2              |

| 6        | AN18/C2IND/RPG8/PMA3/RG8                                             | 38               | VDD                   |

| 7        | MCLR                                                                 | 39               | OSC1/CLKI/RC12        |

| 8        | AN19/C2INC/RPG9/PMA2/RG9                                             | 40               | OSC2/CLKO/RC15        |

| 9        | Vss                                                                  | 41               | Vss                   |

| 10       | Vdd                                                                  | 42               | RPD8/RTCC/RD8         |

| 11       | AN5/C1INA/RPB5/RB5                                                   | 43               | RPD9/RD9              |

| 12       | AN4/C1INB/RB4                                                        | 44               | RPD10/PMCS2/RD10      |

| 13       | PGED3/AN3/C2INA/RPB3/RB3                                             | 45               | RPD11/PMCS1/RD11      |

| 14       | PGEC3/AN2/C2INB/RPB2/CTED13/RB2                                      | 46               | RPD0/RD0              |

| 15       | PGEC1/VREF-/CVREF-/AN1/RPB1/CTED12/RB1                               | 47               | SOSCI/RPC13/RC13      |

| 16       | PGED1/VREF+/CVREF+/AN0/RPB0/PMA6/RB0                                 | 48               | SOSCO/RPC14/T1CK/RC14 |

| 17       | PGEC2/AN6/RPB6/RB6                                                   | 49               | AN24/RPD1/RD1         |

| 18       | PGED2/AN7/RPB7/CTED3//RB7                                            | 50               | AN25/RPD2/RD2         |

| 19       | AVDD                                                                 | 51               | AN26/RPD3/RD3         |

| 20       | AVss                                                                 | 52               | RPD4/PMWR/RD4         |

| 21       | AN8/RPB8/CTED10//RB8                                                 | 53               | RPD5/PMRD/RD5         |

| 22       | AN9/RPB9/CTED4/PMA7/RB9                                              | 54               | RD6                   |

| 23       | TMS/Cvrefout/AN10/RPB10/CTED11//PMA13/RB10                           | 55               | RD7                   |

| 24       | TDO/AN11/PMA12/RB11                                                  | 56               | VCAP                  |

| 25       | Vss                                                                  | 57               | VDD                   |

| 26       | Vdd                                                                  | 58               | RPF0/RF0              |

| 27       | TCK/AN12/PMA11/RB12                                                  | 59               | RPF1/RF1              |

| 28       | TDI/AN13/PMA10/RB13                                                  | 60               | PMD0/RE0              |

| 29       | AN14/RPB14/CTED5/PMA1/RB14                                           | 61               | PMD1/RE1              |

| 30       | AN15/RPB15/OCFB/CTED6/PMA0/RB15                                      | 62               | AN20/PMD2/RE2         |

| 31       | RPF4/SDA2/PMA9/RF4                                                   | 63               | RPE3/CTPLS/PMD3/RE3   |

| 32       | RPF5/SCL2/PMA8/RF5                                                   | 64               | AN21/PMD4/RE4         |

1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

Every I/O port pin (RBx-RGx), with the exception of RF6, can be used as a change notification pin (CNBx-CNGx). See Section 12.0 "I/O 2: Ports" for more information.

3: The metal plane at the bottom of the device is not connected to any pins and is recommended to be connected to Vss externally.

RPF6 (pin 35) is only available for output functions. 4:

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS

|          |                        | Pin Numb        | er                                |             |                |                                                                                                                                                                                                   |  |  |  |  |

|----------|------------------------|-----------------|-----------------------------------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA                   | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                       |  |  |  |  |

| AN0      | 16                     | 25              | B14                               |             | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN1      | 15                     | 24              | A15                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN2      | 14                     | 23              | B13                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN3      | 13                     | 22              | A13                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN4      | 12                     | 21              | B11                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN5      | 11                     | 20              | A12                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN6      | 17                     | 26              | A20                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN7      | 18                     | 27              | B16                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN8      | 21                     | 32              | A23                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN9      | 22                     | 33              | B19                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN10     | 23                     | 34              | A24                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN11     | 24                     | 35              | B20                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN12     | 27                     | 41              | B23                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN13     | 28                     | 42              | A28                               | I           | Analog         | Analog input channels.                                                                                                                                                                            |  |  |  |  |

| AN14     | 29                     | 43              | B24                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN15     | 30                     | 44              | A29                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN16     | 4                      | 10              | A7                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN17     | 5                      | 11              | B6                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN18     | 6                      | 12              | A8                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN19     | 8                      | 14              | A9                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN20     | 62                     | 98              | A66                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN21     | 64                     | 100             | A67                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN22     | 1                      | 3               | B2                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN23     | 2                      | 4               | A4                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN24     | 49                     | 76              | A52                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN25     | 50                     | 77              | B42                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN26     | 51                     | 78              | A53                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| AN27     | 3                      | 5               | B3                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |

| CLKI     | 39                     | 63              | B34                               | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                            |  |  |  |  |

| CLKO     | 40                     | 64              | A42                               | 0           | _              | Oscillator crystal output. Connects to crystal or reso-<br>nator in Crystal Oscillator mode. Optionally functions<br>as CLKO in RC and EC modes. Always associated<br>with the OSC2 pin function. |  |  |  |  |

| OSC1     | 39                     | 63              | B34                               | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                   |  |  |  |  |

| OSC2     | 40                     | 64              | A42                               | 0           | _              | Oscillator crystal output. Connects to crystal or reso-<br>nator in Crystal Oscillator mode. Optionally functions<br>as CLKO in RC and EC modes.                                                  |  |  |  |  |

| SOSCI    | 47                     | 73              | A47                               | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                    |  |  |  |  |

| SOSCO    | 48                     | 74              | B40                               | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                   |  |  |  |  |

| -        | ST = Schm              |                 | tible input or o<br>out with CMOS |             |                | alog = Analog input P = Power<br>= Output I = Input                                                                                                                                               |  |  |  |  |

TTL = TTL input buffer

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

**3:** This pin is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | —                 | —                 |                   |                   | IP3<2:0>          | IS3<              | IS3<1:0>         |                  |  |

| 23:16        | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:10        | —                 | —                 |                   | IP2<2:0>          |                   |                   | IS2<1:0>         |                  |  |

| 15:0         | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | —                 | —                 | —                 |                   | IP1<2:0>          |                   | IS1<1:0>         |                  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 7:0          | _                 | _                 |                   |                   | IP0<2:0>          |                   | IS0<             | 1:0>             |  |

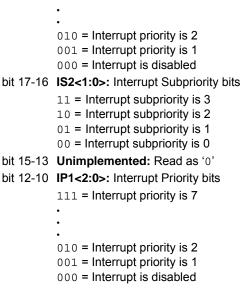

#### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

#### Legend:

| R = Readable bit  | = Readable bit W = Writable bit |                      | ead as '0'         |

|-------------------|---------------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set                | '0' = Bit is cleared | x = Bit is unknown |

**Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.

#### **Oscillator Control Registers** 8.1

| TAB                         | TABLE 8-1: OSCILLATOR CONTROL REGISTER MAP |                          |       |       |         |                            |       |       |                                   |        |         |                      |               |       |      |                       |        |       |                     |

|-----------------------------|--------------------------------------------|--------------------------|-------|-------|---------|----------------------------|-------|-------|-----------------------------------|--------|---------|----------------------|---------------|-------|------|-----------------------|--------|-------|---------------------|

| ess                         |                                            | 0                        |       |       |         | Bits                       |       |       |                                   |        |         |                      |               |       |      | 6                     |        |       |                     |

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup>            | Bit Range                | 31/15 | 30/14 | 29/13   | 28/12                      | 27/11 | 26/10 | 25/9                              | 24/8   | 23/7    | 22/6                 | 21/5          | 20/4  | 19/3 | 18/2                  | 17/1   | 16/0  | All Reset           |

| F000                        | OSCCON                                     | 31:16                    | _     | _     | PI      | PLLODIV<2:0> FRCDIV<2:0> — |       | _     | SOSCRDY PBDIVRDY PBDIV<1:0> PLLMU |        |         | LMULT<2:0            | _MULT<2:0> x1 |       |      |                       |        |       |                     |

| F000                        | USCCON                                     | 15:0                     | _     |       | COSC<2: | 0>                         | _     |       | NOSC<2:0                          | )>     | CLKLOCK | ULOCK <sup>(4)</sup> | SLOCK         | SLPEN | CF   | UFRCEN <sup>(4)</sup> | SOSCEN | OSWEN | xxxx <sup>(2)</sup> |

| F010                        | OSCTUN                                     | 31:16                    | —     | _     | _       | _                          | _     | —     | —                                 |        | _       | —                    | _             | _     |      | —                     | _      | _     | 0000                |

| 1010                        | 030101                                     | 15:0                     | —     | _     |         | —                          | —     | —     | —                                 |        | -       | _                    |               |       | TUN  | <b>\&lt;5:0&gt;</b>   |        |       | 0000                |

| 5000                        | REFOCON                                    | 31:16                    | _     |       |         |                            |       |       |                                   |        | RODIV<  | 4:0>                 |               |       |      |                       |        |       | 0000                |

| F020                        | F020 REFOCON                               |                          | ON    | —     | SIDL    | OE                         | RSLP  | —     | DIVSWEN                           | ACTIVE | —       | —                    | —             | —     |      | ROSE                  | L<3:0> |       | 0000                |

| 5000                        | DEFOTDIM                                   | SECTED 31:16 ROTRIM<8:0> |       |       |         | _                          |       | _     | _                                 | _      | _       | —                    | 0000          |       |      |                       |        |       |                     |

| F030                        | REFOTRIM                                   | 15:0                     | _     | _     |         | _                          | _     | _     | _                                 |        | —       | _                    |               | _     |      | _                     |        | _     | 0000                |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

Reset values are dependent on the DEVCFGx Configuration bits and the type of reset. 2:

This bit is only available on devices with a USB module. 3:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |  |  |

| 23:16        | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:10        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                |  |  |  |

| 15.0         | U-0               | R-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | _                 | -                 | _                 | _                 | _                 |                   | _                | —                |  |  |  |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | _                 | _                 |                   |                   | TUN<              | 5:0> <b>(1)</b>   |                  |                  |  |  |  |

## REGISTER 8-2: OSCTUN: FRC TUNING REGISTER

| Legend:           | y = Value set from Configuration bits on POR |                                    |                    |  |  |  |

|-------------------|----------------------------------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit                             | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set                             | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-6 Unimplemented: Read as '0'

**Note 1:** OSCTUN functionality has been provided to help customers compensate for temperature effects on the FRC frequency over a wide range of temperatures. The tuning step size is an approximation, and is neither characterized nor tested.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 31:24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        | CHEW1<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        | CHEW1<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | CHEW1<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          |                   |                   |                   | CHEW1             | <7:0>             |                   |                  |                  |  |  |

#### REGISTER 9-6: CHEW1: CACHE WORD 1

| Legend:           |                  |                        |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31-0 **CHEW1<31:0>:** Word 1 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

### REGISTER 9-7: CHEW2: CACHE WORD 2

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 21.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        | CHEW2<31:24>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        | CHEW2<23:16>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         | CHEW2<15:8>       |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          |                   |                   |                   | CHEW2             | <7:0>             |                   |                  |                  |  |  |

| Legend:           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31-0 **CHEW2<31:0>:** Word 2 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

## 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32 USB module includes the following features:

- USB full-speed support for host and device

- Low-speed host support

- USB OTG support

- · Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, and other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------------|-------------------------|-------------------|----------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 31.24        | _                 | _                       | _                       |                   | —                    | _                 | _                     | —                       |

| 23:16        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 23.10        | _                 | _                       | _                       |                   | —                    | _                 | _                     | —                       |

| 15:8         | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 15.0         | _                 | _                       | _                       |                   | —                    | _                 | _                     | —                       |

|              | R/WC-0, HS        | R/WC-0, HS              | R/WC-0, HS              | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS        | R-0                   | R/WC-0, HS              |

| 7:0          | STALLIF           | ATTACHIF <sup>(1)</sup> | RESUMEIF <sup>(2)</sup> | IDLEIF            | TRNIF <sup>(3)</sup> | SOFIF             | UERRIF <sup>(4)</sup> | URSTIF <sup>(5)</sup>   |

|              | OTTLE             |                         | REGOMEN                 | IDEEN             |                      | 0011              | OLIVI                 | DETACHIF <sup>(6)</sup> |

|              |                   |                         |                         |                   |                      |                   |                       | 1                       |

## REGISTER 11-6: U1IR: USB INTERRUPT REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Setta  | ble bit            |

|-------------------|-------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented b  | vit, read as '0'   |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

|       | -  |                                                                                                                                              |

|-------|----|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7 |    | <b>STALLIF:</b> STALL Handshake Interrupt bit 1 = In Host mode, a STALL handshake was received during the handshake phase of the transaction |

|       |    |                                                                                                                                              |

|       |    | In Device mode, a STALL handshake was transmitted during the handshake phase of the transaction                                              |

|       |    | 0 = STALL handshake has not been sent                                                                                                        |

| bit 6 |    | ATTACHIF: Peripheral Attach Interrupt bit <sup>(1)</sup>                                                                                     |

|       |    | 1 = Peripheral attachment was detected by the USB module                                                                                     |

|       |    | 0 = Peripheral attachment was not detected                                                                                                   |

| bit 5 |    | <b>RESUMEIF:</b> Resume Interrupt bit <sup>(2)</sup>                                                                                         |

|       |    | 1 = K-State is observed on the D+ or D- pin for 2.5 µs                                                                                       |

|       |    | 0 = K-State is not observed                                                                                                                  |

| bit 4 |    | <b>IDLEIF:</b> Idle Detect Interrupt bit                                                                                                     |

|       |    | <ul><li>1 = Idle condition detected (constant Idle state of 3 ms or more)</li><li>0 = No Idle condition detected</li></ul>                   |

| bit 3 |    | TRNIF: Token Processing Complete Interrupt bit <sup>(3)</sup>                                                                                |

| DILS  |    | 1 = Processing of current token is complete; a read of the U1STAT register will provide endpoint information                                 |

|       |    | 0 = Processing of current token not complete                                                                                                 |

| bit 2 |    | SOFIF: SOF Token Interrupt bit                                                                                                               |

|       |    | 1 = SOF token received by the peripheral or the SOF threshold reached by the host                                                            |

|       |    | 0 = SOF token was not received nor threshold reached                                                                                         |

| bit 1 |    | UERRIF: USB Error Condition Interrupt bit <sup>(4)</sup>                                                                                     |

|       |    | 1 = Unmasked error condition has occurred                                                                                                    |

|       |    | 0 = Unmasked error condition has not occurred                                                                                                |

| bit 0 |    | URSTIF: USB Reset Interrupt bit (Device mode) <sup>(5)</sup>                                                                                 |

|       |    | 1 = Valid USB Reset has occurred                                                                                                             |

|       |    | 0 = No USB Reset has occurred                                                                                                                |

| bit 0 |    | <b>DETACHIF:</b> USB Detach Interrupt bit (Host mode) <sup>(6)</sup>                                                                         |

|       |    | 1 = Peripheral detachment was detected by the USB module                                                                                     |

|       |    | 0 = Peripheral detachment was not detected                                                                                                   |

| Note  | 1: | This bit is valid only if the HOSTEN bit is set (see Register 11-11), there is no activity on the USB for                                    |

|       |    | $2.5 \mu\text{s}$ , and the current bus state is not SE0.                                                                                    |

|       | 2: | When not in Suspend mode, this interrupt should be disabled.                                                                                 |

|       | 3: | Clearing this bit will cause the STAT FIFO to advance.                                                                                       |

|       | 4: | Only error conditions enabled through the U1EIE register will set this bit.                                                                  |

|       | 5: | Device mode.                                                                                                                                 |

|       | 6: | Host mode.                                                                                                                                   |

## 15.1 Watchdog Timer Control Registers

| DS60001185F-page |  |

|------------------|--|

| е<br>—           |  |

| 78               |  |

## TABLE 15-1: WATCHDOG TIMER CONTROL REGISTER MAP

| ess                        |                                 | æ         |       |       |       |       |       |       |      |      | Bits |                                   |      |      |      |      |      |      | s          |

|----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-----------------------------------|------|------|------|------|------|------|------------|

| Virtual Addres<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6                              | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 0000                       | WDTCON                          | 31:16     | _     | _     | _     | _     | -     | -     | —    | —    | _    | —                                 | —    | _    | _    | _    | —    | —    | 0000       |

| 0000                       | WDICON                          | 15:0      | ON    |       |       |       | _     | _     | _    | _    |      | SWDTPS<4:0>     WDTWINEN WDTCLR 0 |      |      |      |      | 0000 |      |            |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6        | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|--------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0                      | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                        | _                 | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0                      | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                        | —                 | _                 |                   |                   | —                | _                |

| 45.0         | R/W-0             | R/W-0                    | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | PTEN<1            | 5:14> <sup>(1)</sup>     |                   |                   | PTEN•             | <13:8>            |                  |                  |

| 7.0          | R/W-0             | R/W-0                    | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | PTEN<1:0> <sup>(2)</sup> |                   |                   |                   |                   |                  |                  |

#### REGISTER 21-4: PMAEN: PARALLEL PORT PIN ENABLE REGISTER

## Legend:

| Legenu.           |                  |                          |                    |  |

|-------------------|------------------|--------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |  |

bit 31-16 Unimplemented: Write '0'; ignore read

- bit 15-14 **PTEN<15:14>:** PMCSx Address Port Enable bits

- 1 = PMA15 and PMA14 function as either PMA<15:14> or PMCS2 and PMCS1<sup>(1)</sup>

- 0 = PMA15 and PMA14 function as port I/O

- bit 13-2 **PTEN<13:2>:** PMP Address Port Enable bits 1 = PMA<13:2> function as PMP address lines

- 0 = PMA<13:2> function as port I/O

- bit 1-0 **PTEN<1:0>:** PMALH/PMALL Address Port Enable bits

- 1 = PMA1 and PMA0 function as either PMA<1:0> or PMALH and PMALL<sup>(2)</sup>

- 0 = PMA1 and PMA0 pads function as port I/O

- Note 1: The use of these pins as PMA15/PMA14 or CS2/CS1 is selected by the CSF<1:0> bits (PMCON<7:6>).

- 2: The use of these pins as PMA1/PMA0 or PMALH/PMALL depends on the Address/Data Multiplex mode selected by the ADRMUX<1:0> bits in the PMCON register.

| Bit<br>Range | Bit<br>31/23/15/7        | Bit<br>30/22/14/6    | Bit<br>29/21/13/5  | Bit<br>28/20/12/4       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1     | Bit<br>24/16/8/0 |  |  |  |

|--------------|--------------------------|----------------------|--------------------|-------------------------|-------------------|-------------------|----------------------|------------------|--|--|--|

| 31:24        | U-0                      | U-0                  | U-0                | U-0                     | U-0               | U-0               | U-0                  | U-0              |  |  |  |

| 31.24        | —                        | —                    | —                  | —                       | _                 | —                 | _                    | _                |  |  |  |

| 00.16        | U-0                      | U-0                  | U-0                | U-0                     | U-0               | U-0               | U-0                  | U-0              |  |  |  |

| 23:16        | —                        | —                    | —                  | —                       | _                 | —                 | _                    | _                |  |  |  |

| 45.0         | R/W-0                    | R/W-0                | R/W-0              | R-0                     | R/W-0             | R/W-0             | R/W-0                | R/W-0            |  |  |  |

| 15:8         | ALRMEN <sup>(1,2)</sup>  | CHIME <sup>(2)</sup> | PIV <sup>(2)</sup> | ALRMSYNC <sup>(3)</sup> |                   | AMASK             | <3:0> <sup>(3)</sup> |                  |  |  |  |

| 7.0          | R/W-0                    | R/W-0                | R/W-0              | R/W-0                   | R/W-0             | R/W-0             | R/W-0                | R/W-0            |  |  |  |

| 7:0          | ARPT<7:0> <sup>(3)</sup> |                      |                    |                         |                   |                   |                      |                  |  |  |  |

|              | •                        |                      |                    |                         |                   |                   |                      |                  |  |  |  |

#### REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ALRMEN: Alarm Enable bit<sup>(1,2)</sup>

- 1 = Alarm is enabled

- 0 = Alarm is disabled

#### bit 14 CHIME: Chime Enable bit<sup>(2)</sup>

- 1 = Chime is enabled ARPT<7:0> is allowed to rollover from 0x00 to 0xFF

- 0 = Chime is disabled ARPT<7:0> stops once it reaches 0x00

#### bit 13 **PIV:** Alarm Pulse Initial Value bit<sup>(2)</sup>

When ALRMEN = 0, PIV is writable and determines the initial value of the Alarm Pulse. When ALRMEN = 1, PIV is read-only and returns the state of the Alarm Pulse.

## bit 12 ALRMSYNC: Alarm Sync bit<sup>(3)</sup>

- 1 = ARPT<7:0> and ALRMEN may change as a result of a half second rollover during a read. The ARPT must be read repeatedly until the same value is read twice. This must be done since multiple bits may be changing, which are then synchronized to the PB clock domain

- 0 = ARPT<7:0> and ALRMEN can be read without concerns of rollover because the prescaler is > 32 RTC clocks away from a half-second rollover

#### bit 11-8 AMASK<3:0>: Alarm Mask Configuration bits<sup>(3)</sup>

- 0000 = Every half-second

- 0001 = Every second

- 0010 = Every 10 seconds

- 0011 = Every minute

- 0100 = Every 10 minutes

- 0101 = Every hour

- 0110 = Once a day

- 0111 = Once a week

- 1000 = Once a month

- 1001 = Once a year (except when configured for February 29, once every four years)

- 1010 = Reserved; do not use

- 1011 = Reserved; do not use

- 11xx = Reserved; do not use

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

#### REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(3)</sup> 11111111 = Alarm will trigger 256 times

0000000 = Alarm will trigger one time

The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

## TABLE 23-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  | 0             |       |       |       |       |       |       |         | В          | its      |          |      |      |      |      |      |      | ŝ          |

|-----------------------------|------------------|---------------|-------|-------|-------|-------|-------|-------|---------|------------|----------|----------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9    | 24/8       | 23/7     | 22/6     | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 9110                        | ADC1BUFA         | 31:16<br>15:0 |       |       |       |       |       |       | ADC Res | ult Word A | (ADC1BUF | A<31:0>) |      |      |      |      |      |      | 0000       |

| 9120                        | ADC1BUFB         | 31:16<br>15:0 |       |       |       |       |       |       | ADC Res | ult Word B | (ADC1BUF | B<31:0>) |      |      |      |      |      |      | 0000       |

| 9130                        | ADC1BUFC         | 31:16<br>15:0 |       |       |       |       |       |       | ADC Res | ult Word C | (ADC1BUF | C<31:0>) |      |      |      |      |      |      | 0000       |

| 9140                        | ADC1BUFD         | 31:16<br>15:0 |       |       |       |       |       |       | ADC Res | ult Word D | (ADC1BUF | D<31:0>) |      |      |      |      |      |      | 0000       |

| 9150                        | ADC1BUFE         | 31:16<br>15:0 |       |       |       |       |       |       | ADC Res | ult Word E | (ADC1BUF | E<31:0>) |      |      |      |      |      |      | 0000       |

| 9160                        | ADC1BUFF         | 31:16<br>15:0 |       |       |       |       |       |       | ADC Res | ult Word F | (ADC1BUF | F<31:0>) |      |      |      |      |      |      | 0000       |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for details.

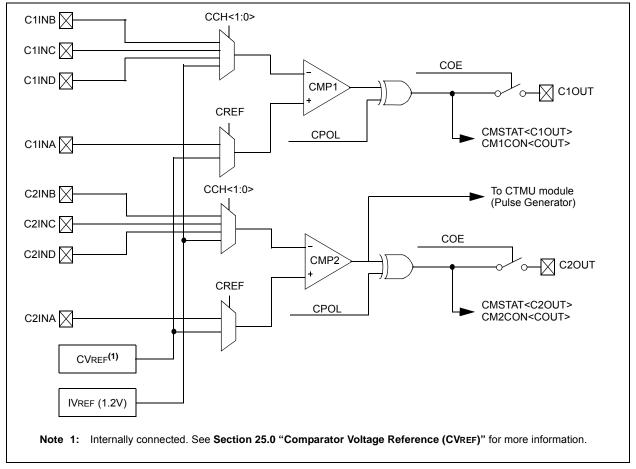

## 24.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer Section 19. to "Comparator" (DS60001110), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Analog Comparator module contains two comparators that can be configured in a variety of ways.

The following are key features of this module:

- · Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be Inverted

- Selectable interrupt generation

A block diagram of the comparator module is provided in Figure 24-1.

#### FIGURE 24-1: COMPARATOR BLOCK DIAGRAM

| DC CHA        | RACTE | RISTICS                           | Standard Oper<br>(unless otherw<br>Operating temp | vise state          | ed)<br>0°C ≤ Ta<br>-40°C ≤ T | ≤ +70°0<br>Ā ≤ +85 | <b>5 3.6V</b><br>C for Commercial<br>5°C for Industrial<br>55°C for V-temp    |

|---------------|-------|-----------------------------------|---------------------------------------------------|---------------------|------------------------------|--------------------|-------------------------------------------------------------------------------|

| Param.<br>No. | Symb. | Characteristics                   | Min.                                              | Тур. <sup>(1)</sup> | Max.                         | Units              | Conditions                                                                    |

|               |       | Input Leakage Current<br>(Note 3) |                                                   |                     |                              |                    |                                                                               |

| DI50          | lı∟   | I/O Ports                         | —                                                 | _                   | <u>+</u> 1                   | μA                 | $Vss \le VPIN \le VDD,$ Pin at high-impedance                                 |

| DI51          |       | Analog Input Pins                 | —                                                 | —                   | <u>+</u> 1                   | μA                 | $Vss \le VPIN \le VDD,$ Pin at high-impedance                                 |

| DI55          |       | MCLR <sup>(2)</sup>               | _                                                 |                     | <u>+</u> 1                   | μA                 | $Vss \leq V \text{PIN} \leq V \text{DD}$                                      |

| DI56          |       | OSC1                              | —                                                 | —                   | <u>+</u> 1                   | μA                 | $VSS \le VPIN \le VDD,$<br>XT and HS modes                                    |

|               |       |                                   |                                                   |                     |                              |                    | Pins with Analog functions.<br>Exceptions: [N/A] = 0 mA<br>max                |

| DI60a         | licl  | Input Low Injection<br>Current    | 0                                                 | _                   | <sub>-5</sub> (7,10)         | mA                 | Digital 5V tolerant desig-<br>nated pins. Exceptions:<br>[N/A] = 0 mA max     |

|               |       |                                   |                                                   |                     |                              |                    | Digital non-5V tolerant desig-<br>nated pins. Exceptions:<br>[N/A] = 0 mA max |

#### TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

**Note 1:** Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

- 7: VIL source < (VSS 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- **10:** Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (Vss 0.3)).

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

#### TABLE 31-14: COMPARATOR SPECIFICATIONS

| DC CHA        |        | STICS                                 | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |         |      |       |                                                                                        |  |  |

|---------------|--------|---------------------------------------|------------------------------------------------------|---------|------|-------|----------------------------------------------------------------------------------------|--|--|

| Param.<br>No. | Symbol | Characteristics                       | Min.                                                 | Typical | Max. | Units | Comments                                                                               |  |  |

| D300          | VIOFF  | Input Offset Voltage                  | —                                                    | ±7.5    | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                              |  |  |

| D301          | VICM   | Input Common Mode Voltage             | 0                                                    | —       | Vdd  | V     | AVdd = Vdd,<br>AVss = Vss<br>(Note 2)                                                  |  |  |

| D302          | CMRR   | Common Mode Rejection Ratio           | 55                                                   | —       | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                      |  |  |

| D303          | Tresp  | Response Time                         | —                                                    | 150     | 400  | ns    | AVdd = Vdd,<br>AVss = Vss<br>(Notes 1,2)                                               |  |  |

| D304          | ON2ov  | Comparator Enabled to Output<br>Valid | -                                                    |         | 10   | μS    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2) |  |  |

| D305          | IVREF  | Internal Voltage Reference            | 1.14                                                 | 1.2     | 1.26 | V     | —                                                                                      |  |  |

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

| AC CHARACTERISTICS <sup>(5)</sup> |            |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |              |      |       |                                                         |  |  |

|-----------------------------------|------------|--------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|------|-------|---------------------------------------------------------|--|--|

| Param.<br>No.                     | Symbol     | Characteristics                | Min.                                                                                                                                                                                                                                                                                                                                               | Typical      | Max. | Units | Conditions                                              |  |  |

| ADC Ac                            | curacy – N | leasurements with Inter        | nal VREF+/VR                                                                                                                                                                                                                                                                                                                                       | EF-          |      |       |                                                         |  |  |

| AD20d                             | Nr         | Resolution                     |                                                                                                                                                                                                                                                                                                                                                    | 10 data bits |      | bits  | (Note 3)                                                |  |  |

| AD21d                             | INL        | Integral Nonlinearity          | > -1                                                                                                                                                                                                                                                                                                                                               | _            | < 1  | LSb   | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |

| AD22d                             | DNL        | Differential Nonlinearity      | > -1                                                                                                                                                                                                                                                                                                                                               | _            | < 1  | LSb   | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Notes 2,3) |  |  |

| AD23d                             | Gerr       | Gain Error                     | > -4                                                                                                                                                                                                                                                                                                                                               | —            | < 4  | LSb   | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |

| AD24d                             | Eoff       | Offset Error                   | > -2                                                                                                                                                                                                                                                                                                                                               | —            | < 2  | LSb   | VINL = AVss = 0V,<br>AVDD = 2.5V to 3.6V<br>(Note 3)    |  |  |

| AD25d                             | _          | Monotonicity                   | —                                                                                                                                                                                                                                                                                                                                                  | —            | _    | —     | Guaranteed                                              |  |  |

| Dynami                            | c Performa | ince                           | •                                                                                                                                                                                                                                                                                                                                                  | •            |      | •     | •                                                       |  |  |

| AD31b                             | SINAD      | Signal to Noise and Distortion | 55                                                                                                                                                                                                                                                                                                                                                 | 58           | —    | dB    | (Notes 3,4)                                             |  |  |

| AD34b                             | ENOB       | Effective Number of Bits       | 9                                                                                                                                                                                                                                                                                                                                                  | 9.5          | _    | bits  | (Notes 3,4)                                             |  |  |

## TABLE 31-35: ADC MODULE SPECIFICATIONS (CONTINUED)

**Note 1:** These parameters are not characterized or tested in manufacturing.

2: With no missing codes.

3: These parameters are characterized, but not tested in manufacturing.

**4:** Characterized with a 1 kHz sine wave.

5: Overall functional device operation at VBORMIN < VDD < VDDMIN is tested, but not characterized. All device Analog modules, such as ADC, etc., will function, but with degraded performance below VDDMIN. Refer to parameter BO10 in Table 31-10 for VBORMIN values.

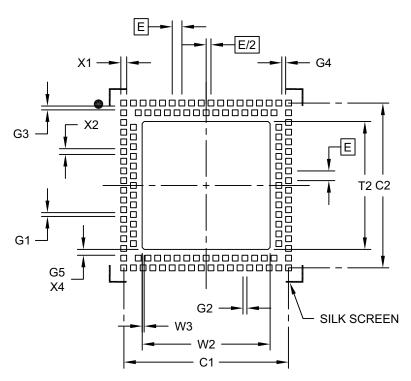

## 124-Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

## RECOMMENDED LAND PATTERN

|                                      | MILLIMETERS |      |          |      |

|--------------------------------------|-------------|------|----------|------|

| Dimension                            | Limits      | MIN  | NOM      | MAX  |

| Contact Pitch                        | E           |      | 0.50 BSC |      |

| Pad Clearance                        | G1          | 0.20 |          |      |

| Pad Clearance                        | G2          | 0.20 |          |      |

| Pad Clearance                        | G3          | 0.20 |          |      |

| Pad Clearance                        | G4          | 0.20 |          |      |

| Contact to Center Pad Clearance (X4) | G5          | 0.30 |          |      |

| Optional Center Pad Width            | T2          |      |          | 6.60 |

| Optional Center Pad Length           | W2          |      |          | 6.60 |

| Optional Center Pad Chamfer (X4)     | W3          |      | 0.10     |      |

| Contact Pad Spacing                  | C1          |      | 8.50     |      |

| Contact Pad Spacing                  | C2          |      | 8.50     |      |

| Contact Pad Width (X124)             | X1          |      |          | 0.30 |

| Contact Pad Length (X124)            | X2          |      |          | 0.30 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2193A

## **Revision C (October 2013)**

This revision includes the following updates, as listed in Table A-2.

### TABLE A-2: MAJOR SECTION UPDATES

| Section                                                               | Update Description                                                                                                                                                                |  |  |  |  |