Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

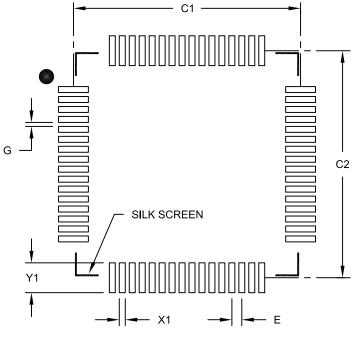

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256lt-i-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

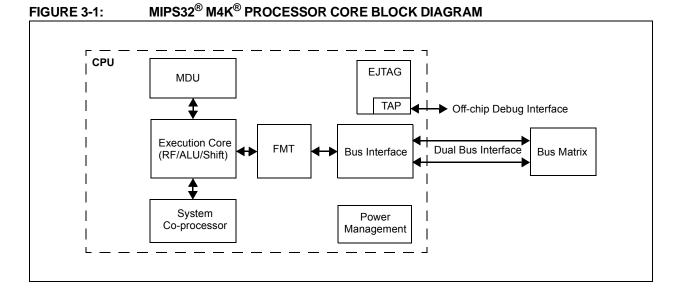

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at http://www.imgtec.com.

The the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX330/350/370/430/450/470 device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

# 3.1 Features

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32<sup>®</sup> Enhanced Architecture (Release 2):

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> Code Compression:

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) Mechanism:

- Simple Dual Bus Interface:

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- Autonomous Multiply/Divide Unit (MDU):

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- · Power Control:

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- EJTAG Debug and Instruction Trace:

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

NOTES:

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |  |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 23:16        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS9             | IFS8             |  |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 7:0          | IFS7              | IFS6              | IFS5              | IFS4              | IFS3              | IFS2              | IFS1             | IFS0             |  |  |  |  |

#### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

## Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IFS31-IFS0: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

### REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC9             | IEC8             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC7              | IEC6              | IEC5              | IEC4              | IEC3              | IEC2              | IEC1             | IEC0             |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IEC31-IEC0: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

'0' = Bit is cleared

x = Bit is unknown

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 |              |       | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|--------------|-------|-------------------|-------------------|------------------|------------------|--|--|--|

| 21.24        | R/W-x             | R/W-x             | R/W-x        | R/W-x | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | CHEHIT<31:24>     |                   |              |       |                   |                   |                  |                  |  |  |  |

| 23:16        | R/W-x             | R/W-x             | R/W-x        | R/W-x | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEHIT<23:16>     |                   |              |       |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x        | R/W-x | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEHIT<15:8>      |                   |              |       |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x        | R/W-x | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          | CHEHIT<7:0>       |                   |              |       |                   |                   |                  |                  |  |  |  |

|              |                   |                   |              |       |                   |                   |                  |                  |  |  |  |

| Legend:      |                   |                   |              |       |                   |                   |                  |                  |  |  |  |

| R = Rea      | dable bit         |                   | W = Writable | bit   | U = Unimple       | emented bit, re   | ad as '0'        |                  |  |  |  |

#### REGISTER 9-10: CHEHIT: CACHE HIT STATISTICS REGISTER

#### bit 31-0 CHEHIT<31:0>: Cache Hit Count bits

-n = Value at POR

Incremented each time the processor issues an instruction fetch or load that hits the prefetch cache from a cacheable region. Non-cacheable accesses do not modify this value.

'1' = Bit is set

|              |                                                                         |                   |                   |                   |                   | •                 |                  |                  |  |  |  |

|--------------|-------------------------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                                                       | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

| 24.24        | R/W-x                                                                   | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        | CHEMIS<31:24>                                                           |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-x                                                                   | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEMIS<23:16>                                                           |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 15.0         | R/W-x                                                                   | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEMIS<15:8>                                                            |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-x                                                                   | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          | CHEMIS<7:0>                                                             |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|              |                                                                         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend:      |                                                                         |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| R = Rea      | dable bit                                                               |                   | W = Writable      | bit               | U = Unimple       | emented bit, re   | ead as '0'       |                  |  |  |  |

| -n = Valu    | = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown |                   |                   |                   |                   |                   | known            |                  |  |  |  |

#### bit 31-0 CHEMIS<31:0>: Cache Miss Count bits

Incremented each time the processor issues an instruction fetch from a cacheable region that misses the prefetch cache. Non-cacheable accesses do not modify this value.

NOTES:

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31.24        | -                 | —                 | _                 | -                 | —                 | _                 | —                | —                |  |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23.10        | -                 | —                 | _                 | -                 | —                 | _                 | —                | —                |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15.0         |                   | _                 | _                 |                   | _                 | -                 |                  | _                |  |  |  |  |  |

| 7.0          | R-0               | U-0               | R-0               | U-0               | R-0               | R-0               | U-0              | R-0              |  |  |  |  |  |

| 7:0          | ID                | —                 | LSTATE            |                   | SESVD             | SESEND            |                  | VBUSVD           |  |  |  |  |  |

### REGISTER 11-3: U1OTGSTAT: USB OTG STATUS REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 ID: ID Pin State Indicator bit

- 1 = No cable is attached or a Type-B cable has been plugged into the USB receptacle

- 0 = A Type-A cable has been plugged into the USB receptacle

- bit 6 Unimplemented: Read as '0'

- bit 5 LSTATE: Line State Stable Indicator bit

- 1 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has been stable for the previous 1 ms

- 0 = USB line state (U1CON<SE0> and U1CON<JSTATE>) has not been stable for the previous 1 ms

#### bit 4 Unimplemented: Read as '0'

- bit 3 SESVD: Session Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A or B device

- 0 = VBUS voltage is below Session Valid on the A or B device

- bit 2 SESEND: B-Device Session End Indicator bit

- 1 = VBUS voltage is below Session Valid on the B device

- 0 = VBUS voltage is above Session Valid on the B device

#### bit 1 Unimplemented: Read as '0'

- bit 0 VBUSVD: A-Device VBUS Valid Indicator bit

- 1 = VBUS voltage is above Session Valid on the A device

- 0 = VBUS voltage is below Session Valid on the A device

# 12.4 Control Registers

|                             | PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY |           |               |               |       |       |       |               |              |      |              |              |              |              |              |              |              |              |               |

|-----------------------------|-------------------------------------------------------------------------------------|-----------|---------------|---------------|-------|-------|-------|---------------|--------------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess (                       |                                                                                     | Ð         |               |               |       |       |       |               |              | Bi   | ts           |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup>                                                     | Bit Range | 31/15         | 30/14         | 29/13 | 28/12 | 27/11 | 26/10         | 25/9         | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6000                        | ANSELA                                                                              | 31:16     | —             | —             | _     | —     | _     | —             | —            | _    | —            | —            | —            | _            | —            | —            | —            | _            | 0000          |

| 0000                        | ANOLLA                                                                              | 15:0      | —             | —             | _     | —     | _     | ANSELA10      | ANSELA9      | _    | _            |              | _            | _            |              |              | —            | _            | 0060          |

| 6010                        | TRISA                                                                               | 31:16     | —             | —             | -     | —     | _     | —             | —            |      | _            | —            | _            |              | —            | —            | _            |              | 0000          |

|                             |                                                                                     | 15:0      | TRISA15       | TRISA14       | _     | —     | _     | TRISA10       | TRISA9       | —    | TRISA7       | TRISA6       | TRISA5       | TRISA4       | TRISA3       | TRISA2       | TRISA1       | TRISA0       | xxxx          |

| 6020                        | PORTA                                                                               | 31:16     | —             | —             | _     | —     |       | —             | _            |      | _            |              | _            | —            |              |              | —            | —            | 0000          |

|                             | -                                                                                   | 15:0      | RA15          | RA14          | _     | —     | _     | RA10          | RA9          | _    | RA7          | RA6          | RA5          | RA4          | RA3          | RA2          | RA1          | RA0          | xxxx          |

| 6030                        | LATA                                                                                | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                                                                     | 15:0      | LATA15        | LATA14        | —     | —     | —     | LATA10        | LATA9        | —    | LATA7        | LATA6        | LATA5        | LATA4        | LATA3        | LATA2        | LATA1        | LATA0        | xxxx          |

| 6040                        | ODCA                                                                                | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                                                                     | 15:0      | ODCA15        | ODCA14        | —     | —     | —     | ODCA10        | ODCA9        | —    | ODCA7        | ODCA6        | ODCA5        | ODCA4        | ODCA3        | ODCA2        | ODCA1        | ODCA0        | xxxx          |

| 6050                        | CNPUA                                                                               | 31:16     |               |               | _     | —     | _     | _             |              |      | —            |              | _            | _            |              |              |              | _            | 0000          |

|                             |                                                                                     |           | CNPUA15       | CNPUA14       | _     | —     | _     | CNPUA10       | CNPUA9       | _    | CNPUA7       | CNPUA6       | CNPUA5       | CNPUA4       | CNPUA3       | CNPUA2       | CNPUA1       | CNPUA0       | _             |

| 6060                        | CNPDA                                                                               | 31:16     | —             | —             | _     | —     | _     | —             | —            | _    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                                                                     |           | CNPDA15       | CNPDA14       | —     |       | _     | CNPDA10       | CNPDA9       | _    | CNPDA7       | CNPDA6       | CNPDA5       | CNPDA4       | CNPDA3       | CNPDA2       | CNPDA1       | CNPDA0       |               |

| 6070                        | CNCONA                                                                              | 31:16     |               |               |       | —     | _     | _             |              |      | _            |              |              |              |              |              |              |              | 0000          |

|                             |                                                                                     | 15:0      | ON            |               | SIDL  | —     | _     | _             |              |      | _            |              |              |              |              |              |              |              | 0000          |

| 6080                        | CNENA                                                                               | 31:16     | -             | -             | _     | _     | _     | -             | -            | _    | -            | -            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                                                                     | 15:0      | CNIEA15       |               | _     | —     | _     | CNIEA10       | CNIEA9       | —    | CNIEA7       | CNIEA6       | CNIEA5       | CNIEA4       | CNIEA3       | CNIEA2       | CNIEA1       | CNIEA0       | XXXX          |

| 6000                        | CNSTATA                                                                             | 31:16     | -             | -             | _     | —     | _     | -             | -            | —    | -            | -            | -            | —            | -            | -            | -            | —            | 0000          |

| 0090                        | CINGTATA                                                                            | 15:0      | CN<br>STATA15 | CN<br>STATA14 | _     | —     | _     | CN<br>STATA10 | CN<br>STATA9 | —    | CN<br>STATA7 | CN<br>STATA6 | CN<br>STATA5 | CN<br>STATA4 | CN<br>STATA3 | CN<br>STATA2 | CN<br>STATA1 | CN<br>STATA0 | xxxx          |

# TABLE 12-3:PORTA REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,<br/>PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 31:24        |                   | _                 | _                 | RXBUFELM<4:0>     |                   |                   |                  |                  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

| 23.10        |                   | _                 | —                 | TXBUFELM<4:0>     |                   |                   |                  |                  |  |  |  |

| 15.0         | U-0               | U-0               | U-0               | R/C-0, HS         | R-0               | U-0               | U-0              | R-0              |  |  |  |

| 15:8         |                   | —                 | _                 | FRMERR            | SPIBUSY           | —                 | _                | SPITUR           |  |  |  |

| 7.0          | R-0               | R/W-0             | R-0               | U-0               | R-1               | U-0               | R-0              | R-0              |  |  |  |

| 7:0          | SRMT              | SPIROV            | SPIRBE            | _                 | SPITBE            |                   | SPITBF           | SPIRBF           |  |  |  |

## REGISTER 18-3: SPIxSTAT: SPI STATUS REGISTER

| Legend:           | C = Clearable bit HS = Set in hardware              |                      |                    |

|-------------------|-----------------------------------------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit U = Unimplemented bit, read as '0' |                      | ead as '0'         |

| -n = Value at POR | '1' = Bit is set                                    | '0' = Bit is cleared | x = Bit is unknown |

- bit 31-29 Unimplemented: Read as '0'

- bit 28-24 **RXBUFELM<4:0>:** Receive Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 23-21 Unimplemented: Read as '0'

- bit 20-16 **TXBUFELM<4:0>:** Transmit Buffer Element Count bits (valid only when ENHBUF = 1)

- bit 15-13 Unimplemented: Read as '0'

- bit 12 **FRMERR:** SPI Frame Error status bit

- 1 = Frame error is detected

- 0 = No Frame error is detected

- This bit is only valid when FRMEN = 1.

- bit 11 SPIBUSY: SPI Activity Status bit

- 1 = SPI peripheral is currently busy with some transactions

- 0 = SPI peripheral is currently idle

- bit 10-9 Unimplemented: Read as '0'

- bit 8 SPITUR: Transmit Under Run bit

- 1 = Transmit buffer has encountered an underrun condition

- 0 = Transmit buffer has no underrun condition

This bit is only valid in Framed Sync mode; the underrun condition must be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or writing a '0' to SPITUR.

- bit 7 **SRMT:** Shift Register Empty bit (valid only when ENHBUF = 1)

- 1 = When SPI module shift register is empty

- 0 = When SPI module shift register is not empty

- bit 6 SPIROV: Receive Overflow Flag bit

- 1 = A new data is completely received and discarded. The user software has not read the previous data in the SPIxBUF register.

- 0 = No overflow has occurred

This bit is set in hardware; can bit only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module, or by writing a '0' to SPIROV.

- bit 5 **SPIRBE:** RX FIFO Empty bit (valid only when ENHBUF = 1) 1 = RX FIFO is empty (CRPTR = SWPTR)

- 0 = RX FIFO is not empty (CRPTR  $\neq$  SWPTR)

- bit 4 Unimplemented: Read as '0'

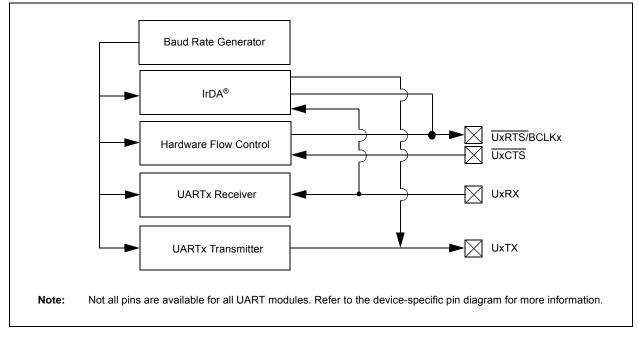

# 20.0 UNIVERSAL ASYNCHRONOUS RECEIVER TRANSMITTER (UART)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The UART module is one of the serial I/O modules available in the PIC32MX330/350/370/430/450/470 family of devices. The UART is a full-duplex, asynchronous communication channel that communicates with peripheral devices and personal computers through protocols, such as RS-232, RS-485, LIN and IrDA<sup>®</sup>. The module also supports the hardware flow control option, with UxCTS and UxRTS pins, and also includes an IrDA encoder and decoder.

The primary features of the UART module are:

- Full-duplex, 8-bit or 9-bit data transmission

- Even, Odd or No Parity options (for 8-bit data)

- · One or two Stop bits

- Hardware auto-baud feature

- · Hardware flow control option

- Fully integrated Baud Rate Generator (BRG) with 16-bit prescaler

- Baud rates ranging from 76 bps to 30 Mbps at 120 MHz

- 8-level deep First-In-First-Out (FIFO) transmit data buffer

- 8-level deep FIFO receive data buffer

- Parity, framing and buffer overrun error detection

- Support for interrupt-only on address detect (9th bit = 1)

- · Separate transmit and receive interrupts

- · Loopback mode for diagnostic support

- · LIN Protocol support

- IrDA encoder and decoder with 16x baud clock output for external IrDA encoder/decoder support

Figure 20-1 illustrates a simplified block diagram of the UART.

#### FIGURE 20-1: UART SIMPLIFIED BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | _                | —                |  |  |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 23:16        | —                 | _                 | -                 | —                 | _                 | _                 | -                | —                |  |  |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |  |  |

| 15:8         | IBF               | IBOV              | _                 | —                 | IB3F              | IB2F              | IB1F             | IB0F             |  |  |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |  |  |

| 7:0          | OBE               | OBUF              |                   | _                 | OB3E              | OB2E              | OB1E             | OB0E             |  |  |

#### REGISTER 21-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | HS = Set by Hardware | SC = Cleared by software               |  |

|-------------------|----------------------|----------------------------------------|--|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0'     |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared x = Bit is unknow |  |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 IBF: Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)0 = No overflow occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 IBxF: Input Buffer 'x' Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

| Bit<br>Range | Bit<br>31/23/15/7     | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2            | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-----------------------|-------------------|-------------------|-------------------|-------------------|------------------------------|------------------|------------------|--|--|

| 04.04        | r-1                   | r-1               | r-1               | r-1               | r-1               | r-1                          | r-1              | r-1              |  |  |

| 31:24        |                       | _                 | —                 | _                 | _                 |                              | _                | —                |  |  |

| 00.40        | r-1                   | r-1               | r-1               | r-1               | r-1               | R/P                          | R/P              | R/P              |  |  |

| 23:16        |                       | —                 | —                 | _                 | —                 | FF                           | FPLLODIV<2:0>    |                  |  |  |

| 45.0         | R/P                   | r-1               | r-1               | r-1               | r-1               | R/P                          | R/P              | R/P              |  |  |

| 15:8         | UPLLEN <sup>(1)</sup> | _                 | _                 | _                 | _                 | UPLLIDIV<2:0> <sup>(1)</sup> |                  | .(1)             |  |  |

| 7.0          | r-1                   | R/P-1             | R/P               | R/P-1             | r-1               | R/P                          | R/P              | R/P              |  |  |

| 7:0          | _                     | – FPLLMUL<2:0>    |                   |                   |                   | FPLLIDIV<2:0>                |                  |                  |  |  |

#### **DEVCFG2: DEVICE CONFIGURATION WORD 2 REGISTER 28-3:**

| Legend:           | r = Reserved bit | P = Programmable bit               |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-19 Reserved: Write '1'

bit 15

bit 7

bit 3

bit 6-4

bit 18-16 FPLLODIV<2:0>: Default PLL Output Divisor bits

111 = PLL output divided by 256 110 = PLL output divided by 64 101 = PLL output divided by 32 100 = PLL output divided by 16 011 = PLL output divided by 8 010 = PLL output divided by 4 001 = PLL output divided by 2 000 = PLL output divided by 1 UPLLEN: USB PLL Enable bit<sup>(1)</sup> 1 = Disable and bypass USB PLL 0 = Enable USB PLL bit 14-11 Reserved: Write '1' bit 10-8 UPLLIDIV<2:0>: USB PLL Input Divider bits<sup>(1)</sup> 111 = 12x divider 110 = 10x divider101 = 6x divider100 = 5x divider 011 = 4x divider 010 = 3x divider 001 = 2x divider 000 = 1x dividerReserved: Write '1' FPLLMUL<2:0>: PLL Multiplier bits 111 = 24x multiplier 110 = 21x multiplier 101 = 20x multiplier 100 = 19x multiplier 011 = 18x multiplier 010 = 17x multiplier 001 = 16x multiplier 000 = 15x multiplier Reserved: Write '1'

Note 1: This bit is available on PIC32MX4XX devices only.

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5     | Bit<br>28/20/12/4      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-----------------------|------------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.24        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | —                 | _                 | _                     | _                      | -                 |                   | _                | _                |  |  |  |

| 23:16        | U-0               | U-0               | U-0                   | U-0                    | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | —                 | -                 | -                     | _                      | _                 |                   | -                | —                |  |  |  |

| 45.0         | U-0               | U-0               | R/W-0                 | R/W-0                  | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | _                 |                   | IOLOCK <sup>(1)</sup> | PMDLOCK <sup>(1)</sup> | _                 |                   |                  | —                |  |  |  |

| 7:0          | U-0               | U-0               | U-0                   | U-0                    | R/W-0             | R/W-0             | U-0              | R/W-1            |  |  |  |

| 7:0          | _                 | _                 | _                     | _                      | JTAGEN            | TROEN             | _                | TDOEN            |  |  |  |

#### **REGISTER 28-5: CFGCON: CONFIGURATION CONTROL REGISTER**

### Legend:

| Logona.           |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

#### bit 31-14 Unimplemented: Read as '0'

- bit 13 **IOLOCK:** Peripheral Pin Select Lock bit<sup>(1)</sup>

- 1 = Peripheral Pin Select is locked. Writes to PPS registers is not allowed

- 0 = Peripheral Pin Select is not locked. Writes to PPS registers is allowed

- bit 12 PMDLOCK: Peripheral Module Disable bit<sup>(1)</sup>

- 1 = Peripheral module is locked. Writes to PMD registers is not allowed

- 0 = Peripheral module is not locked. Writes to PMD registers is allowed

#### bit 11-4 Unimplemented: Read as '0'

- bit 3 JTAGEN: JTAG Port Enable bit

- 1 = Enable the JTAG port

- 0 = Disable the JTAG port

#### bit 2 TROEN: Trace Output Enable bit

- 1 = Enable trace outputs and start trace clock (trace probe must be present)

- 0 = Disable trace outputs and stop trace clock

- bit 1 Unimplemented: Read as '0'

- bit 0 TDOEN: TDO Enable for 2-Wire JTAG

- 1 = 2-wire JTAG protocol uses TDO

- 0 = 2-wire JTAG protocol does not use TDO

- Note 1: To change this bit, the unlock sequence must be performed. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

# 29.0 INSTRUCTION SET

The PIC32MX330/350/370/430/450/470 family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

Note: Refer to "MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set" at www.imgtec.com for more information.

| DC CHARACT       | ERISTICS               |               | (unless o  | rd Operating Conditions: 2.3V to 3.6V<br>otherwise stated)<br>ng temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                                       |                           |  |  |

|------------------|------------------------|---------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|---------------------------|--|--|

| Parameter<br>No. | Typical <sup>(2)</sup> | Maximum       | Units      | S Conditions                                                                                                                                                                                                                                    |                                       |                           |  |  |

| Idle Current (I  | IDLE): Core Of         | f, Clock on E | Base Curre | nt (Note 1)                                                                                                                                                                                                                                     |                                       |                           |  |  |

| DC30a            | 1                      | 2.2           | mA         | 4 MHz                                                                                                                                                                                                                                           |                                       |                           |  |  |

| DC31a            | 3                      | 5             | mA         | 10 MHz (Note 3)                                                                                                                                                                                                                                 |                                       |                           |  |  |

| DC32a            | 5                      | 7             | mA         |                                                                                                                                                                                                                                                 | 20 MHz <b>(Note 3)</b>                |                           |  |  |

| DC33a            | 8                      | 13            | mA         |                                                                                                                                                                                                                                                 | 40 MHz <b>(Note 3)</b>                |                           |  |  |

| DC34a            | 11                     | 18            | mA         |                                                                                                                                                                                                                                                 | 60 MHz <b>(Note 3)</b>                |                           |  |  |

| DC34b            | 15                     | 24            | mA         |                                                                                                                                                                                                                                                 | 80 MHz                                |                           |  |  |

| DC34c            | 19                     | 29            | mA         | 1                                                                                                                                                                                                                                               | 100 MHz, $-40^{\circ}C \le TA \le +8$ | 35°C                      |  |  |

| DC34d            | 25                     | 34            | mA         |                                                                                                                                                                                                                                                 | 120 MHz, $0^{\circ}C \leq TA \leq +7$ | D°C                       |  |  |

| DC37a            | 100                    | —             | μA         | -40°C                                                                                                                                                                                                                                           |                                       |                           |  |  |

| DC37b            | 250                    | _             | μA         | +25°C                                                                                                                                                                                                                                           | 3.3V                                  | LPRC (31 kHz)<br>(Note 3) |  |  |

| DC37c            | 380                    | _             | μA         | +85°C                                                                                                                                                                                                                                           |                                       | (NOLE S)                  |  |  |

#### TABLE 31-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

Note 1: The test conditions for IIDLE measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode (CPU core is halted), program Flash memory Wait states = 7, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

| DC CHARACTERISTICS                  |       |                                                                       | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                     |                        |       |                                                                                                                                                                                                                                                                                              |

|-------------------------------------|-------|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|------------------------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Param.<br>No. Symb. Characteristics |       |                                                                       | Min.                                                                                                                                                                                                                                                                                                                                                | Тур. <sup>(1)</sup> | Max.                   | Units | Conditions                                                                                                                                                                                                                                                                                   |

| DI60b                               | Іісн  | Input High Injection<br>Current                                       | 0                                                                                                                                                                                                                                                                                                                                                   |                     | +5 <sup>(8,9,10)</sup> | mA    | Pins with Analog functions.<br>Exceptions: [SOSCI,<br>SOSCO, OSC1, D+, D-] = 0<br>mA max.<br>Digital 5V tolerant desig-<br>nated pins (VIH < $5.5V$ ) <sup>(9)</sup> .<br>Exceptions: [All] = 0 mA<br>max.<br>Digital non-5V tolerant desig-<br>nated pins. Exceptions:<br>[N/A] = 0 mA max. |

| DI60c                               | ∑IICT | Total Input Injection<br>Current (sum of all I/O<br>and control pins) | -20 <sup>(11)</sup>                                                                                                                                                                                                                                                                                                                                 | _                   | +20 <sup>(11)</sup>    | mA    | Absolute instantaneous sum<br>of all $\pm$ input injection cur-<br>rents from all I/O pins<br>(   IICL +   IICH   ) $\leq \sum$ IICT                                                                                                                                                         |

#### TABLE 31-8: DC CHARACTERISTICS: I/O PIN INPUT SPECIFICATIONS (CONTINUED)

Note 1: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 2: The leakage current on the MCLR pin is strongly dependent on the applied voltage level. The specified levels represent normal operating conditions. Higher leakage current may be measured at different input voltages.

- 3: Negative current is defined as current sourced by the pin.

- 4: This parameter is characterized, but not tested in manufacturing.

- 5: See the "Device Pin Tables" section for the 5V tolerant pins.

- 6: The VIH specifications are only in relation to externally applied inputs, and not with respect to the userselectable internal pull-ups. External open drain input signals utilizing the internal pull-ups of the PIC32 device are guaranteed to be recognized only as a logic "high" internally to the PIC32 device, provided that the external load does not exceed the minimum value of ICNPU. For External "input" logic inputs that require a pull-up source, to guarantee the minimum VIH of those components, it is recommended to use an external pull-up resistor rather than the internal pull-ups of the PIC32 device.

- 7: VIL source < (Vss 0.3). Characterized but not tested.

- 8: VIH source > (VDD + 0.3) for non-5V tolerant pins only.

- **9:** Digital 5V tolerant pins do not have an internal high side diode to VDD, and therefore, cannot tolerate any "positive" input injection current.

- **10:** Injection currents > | 0 | can affect the ADC results by approximately 4 to 6 counts (i.e., VIH Source > (VDD + 0.3) or VIL source < (VSS 0.3)).

- 11: Any number and/or combination of I/O pins not excluded under IICL or IICH conditions are permitted provided the "absolute instantaneous" sum of the input injection currents from all pins do not exceed the specified limit. If Note 7, IICL = (((Vss 0.3) VIL source) / Rs). If Note 8, IICH = ((IICH source (VDD + 0.3)) / RS). RS = Resistance between input source voltage and device pin. If (Vss 0.3) ≤ VSOURCE ≤ (VDD + 0.3), injection current = 0.

|        |                                                                                       |                                                                                                                            |                    | d Opera  | ating Co | ondition                                                                                                                                             | s: 2.3V to 3.6V               |  |

|--------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|--------------------|----------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|--|

| DC CHA | RACTER                                                                                | ISTICS                                                                                                                     | Operatin           | ig tempe | erature  | $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial<br>-40°C $\le TA \le +85^{\circ}C$ for Industrial<br>-40°C $\le TA \le +105^{\circ}C$ for V-temp |                               |  |

| Param. | Symbol                                                                                | Characteristic                                                                                                             | Min.               | Тур.     | Max.     | Units                                                                                                                                                | Conditions                    |  |

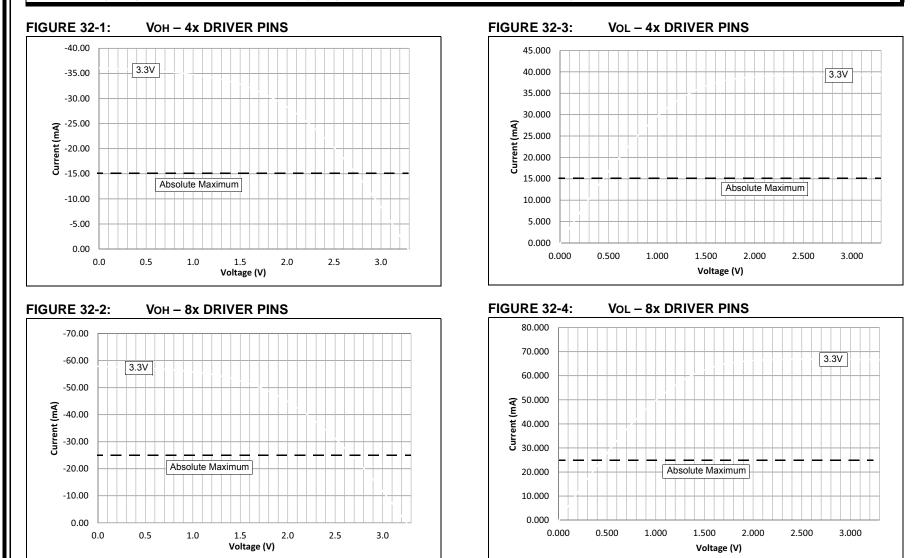

|        |                                                                                       | Output Low Voltage<br>I/O Pins:<br>4x Sink Driver Pins - All I/O<br>output pins not defined as 8x<br>Sink Driver pins      | _                  | _        | 0.4      | V                                                                                                                                                    | IOL $\leq$ 9 mA, VDD = 3.3V   |  |

|        | Output Low Voltage<br>I/O Pins:<br>8x Sink Driver Pins - RC15,<br>RD2, RD10, RF6, RG6 | _                                                                                                                          | _                  | 0.4      | v        | $\text{IOL} \leq 15 \text{ mA}, \text{ VDD} = 3.3 \text{V}$                                                                                          |                               |  |

| DO20   | Voн                                                                                   | Output High Voltage<br>I/O Pins:<br>4x Source Driver Pins - All I/O<br>output pins not defined as 8x<br>Source Driver pins | 2.4                | _        | _        | v                                                                                                                                                    | IOH ≥ -10 mA, VDD = 3.3V      |  |

|        |                                                                                       | Output High Voltage<br>I/O Pins:<br>8x Source Driver Pins - RC15,<br>RD2, RD10, RF6, RG6                                   | 2.4                | _        | _        | V                                                                                                                                                    | Ioh $\ge$ -15 mA, Vdd = 3.3V  |  |

|        |                                                                                       | Output High Voltage                                                                                                        | 1.5 <sup>(1)</sup> | _        |          |                                                                                                                                                      | IOH $\geq$ -14 mA, VDD = 3.3V |  |

|        |                                                                                       | 4x Source Driver Pins - All I/O                                                                                            | 2.0 <sup>(1)</sup> | _        | _        | V                                                                                                                                                    | IOH $\ge$ -12 mA, VDD = 3.3V  |  |

| 00204  | Vou1                                                                                  | output pins not defined as 8x<br>Sink Driver pins                                                                          | 3.0 <sup>(1)</sup> | _        |          |                                                                                                                                                      | IOH $\ge$ -7 mA, VDD = 3.3V   |  |

| DO20A  | VOHI                                                                                  | Output High Voltage<br>I/O Pins:<br>8x Source Driver Pins - RC15,                                                          | 1.5 <sup>(1)</sup> | _        | _        | v                                                                                                                                                    | IOH $\ge$ -22 mA, VDD = 3.3V  |  |

|        |                                                                                       |                                                                                                                            | 2.0 <sup>(1)</sup> | _        | _        |                                                                                                                                                      | Ioh $\geq$ -18 mA, Vdd = 3.3V |  |

|        |                                                                                       | RD2, RD10, RF6, RG6                                                                                                        | 3.0 <sup>(1)</sup> | _        | _        |                                                                                                                                                      | IOH $\ge$ -10 mA, VDD = 3.3V  |  |

#### TABLE 31-9: DC CHARACTERISTICS: I/O PIN OUTPUT SPECIFICATIONS

Note 1: Parameters are characterized, but not tested.

#### TABLE 31-14: COMPARATOR SPECIFICATIONS

| DC CHA                               |       | $ \begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \\ \end{array} $ |      |         |      |       |                                                                                        |  |

|--------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|---------|------|-------|----------------------------------------------------------------------------------------|--|

| Param.<br>No. Symbol Characteristics |       |                                                                                                                                                                                                                                                                                                                                                         | Min. | Typical | Max. | Units | Comments                                                                               |  |

| D300                                 | VIOFF | Input Offset Voltage                                                                                                                                                                                                                                                                                                                                    | —    | ±7.5    | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                              |  |

| D301                                 | VICM  | Input Common Mode Voltage                                                                                                                                                                                                                                                                                                                               | 0    | —       | Vdd  | V     | AVdd = Vdd,<br>AVss = Vss<br>(Note 2)                                                  |  |

| D302                                 | CMRR  | Common Mode Rejection Ratio                                                                                                                                                                                                                                                                                                                             | 55   | —       | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                      |  |

| D303                                 | Tresp | Response Time                                                                                                                                                                                                                                                                                                                                           | —    | 150     | 400  | ns    | AVdd = Vdd,<br>AVss = Vss<br>(Notes 1,2)                                               |  |

| D304                                 | ON2ov | Comparator Enabled to Output<br>Valid                                                                                                                                                                                                                                                                                                                   | -    |         | 10   | μS    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2) |  |

| D305                                 | IVREF | Internal Voltage Reference                                                                                                                                                                                                                                                                                                                              | 1.14 | 1.2     | 1.26 | V     | —                                                                                      |  |

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

| AC CHA        | RACTER        | ISTICS                   |                               | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |             |                               |                        |  |  |

|---------------|---------------|--------------------------|-------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------------------------|------------------------|--|--|

| Param.<br>No. | Symbol        | Charact                  | eristics                      | Min. <sup>(1)</sup>                                                                                                                                                                                 | -40<br>Max. | $O^{\circ}C \le TA \le$ Units | Conditions             |  |  |

| IM10          | TLO:SCL       | Clock Low Time           | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                     |             | μS                            |                        |  |  |

|               | 1201002       |                          | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                     |             | μs                            | _                      |  |  |

|               |               |                          | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                     |             | μs                            | -                      |  |  |

| IM11          | THI:SCL       | Clock High Time          | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                     |             | μS                            | _                      |  |  |

|               |               | _                        | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                     |             | μS                            | —                      |  |  |

|               |               |                          | 1 MHz mode<br>(Note 2)        | Трв * (BRG + 2)                                                                                                                                                                                     | _           | μs                            | _                      |  |  |

| IM20          | TF:SCL        | SDAx and SCLx            | 100 kHz mode                  |                                                                                                                                                                                                     | 300         | ns                            | CB is specified to be  |  |  |

|               |               | Fall Time                | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                         | 300         | ns                            | from 10 to 400 pF      |  |  |

|               |               |                          | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                   | 100         | ns                            |                        |  |  |

| IM21 TR:SCL   | SDAx and SCLx | 100 kHz mode             | —                             | 1000                                                                                                                                                                                                | ns          | CB is specified to be         |                        |  |  |

|               |               | Rise Time                | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                         | 300         | ns                            | from 10 to 400 pF      |  |  |

|               |               |                          | 1 MHz mode<br><b>(Note 2)</b> | —                                                                                                                                                                                                   | 300         | ns                            |                        |  |  |

| IM25          | TSU:DAT       | Data Input<br>Setup Time | 100 kHz mode                  | 250                                                                                                                                                                                                 |             | ns                            | —                      |  |  |

|               |               |                          | 400 kHz mode                  | 100                                                                                                                                                                                                 | _           | ns                            |                        |  |  |