Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | - ·                                                                             |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256lt-v-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### TABLE 7: PIN NAMES FOR 124-PIN DEVICES (CONTINUED)

| 124               | -PIN VTLA (BOTTOM VIEW) <sup>(1,2,3,4)</sup>                             | 17       |                   |                | A34           |                       |

|-------------------|--------------------------------------------------------------------------|----------|-------------------|----------------|---------------|-----------------------|

|                   | A                                                                        | 17       |                   | B13 B29        |               | nductive<br>ermal Pad |

|                   | PIC32MX430F064L<br>PIC32MX450F128L<br>PIC32MX450F256L<br>PIC32MX470F512L |          |                   | B1<br>B56      | B41           | A51                   |

|                   |                                                                          | y Indica | A1<br>tor         | A68            |               |                       |

| Package<br>Bump # | Full Pin Name                                                            |          | Package<br>Bump # |                | Full Pin Name |                       |

| B7                | MCLR                                                                     |          | B32               | SDA2/RA3       |               |                       |

| B8                | Vss                                                                      |          | B33               | TDO/RA5        |               |                       |

| B9                | TMS/CTED1/RA0                                                            |          | B34               | OSC1/CLKI/RC12 | 2             |                       |

| B10               | RPE9/RE9                                                                 |          | B35               | No Connect     |               |                       |

| B11               | AN4/C1INB/RB4                                                            |          | B36               | SCL1/RPA14/RA  | 14            |                       |

| B12               | Vss                                                                      |          | B37               | RPD8/RTCC/RD8  | 8             |                       |

| B13               | PGEC3/AN2/C2INB/RPB2/CTED13/RB2                                          |          | B38               | RPD10/SCK1/PM  | CS2/RD10      |                       |

| B14               | PGED1/AN0/RPB0/RB0                                                       |          | B39               | RPD0/INT0/RD0  |               |                       |

| B15               | No Connect                                                               |          | B40               | SOSCO/RPC14/T  | 1CK/RC14      |                       |

| B16               | PGED2/AN7/RPB7/CTED3/RB7                                                 |          | B41               | Vss            |               |                       |

| B17               | VREF+/CVREF+/PMA6/RA10                                                   |          | B42               | AN25/RPD2/RD2  |               |                       |

| B18               | AVss                                                                     |          | B43               | RPD12/PMD12/R  | D12           |                       |

| B19               | AN9/RPB9/CTED4/RB9                                                       |          | B44               | RPD4/PMWR/RD   | 4             |                       |

| B20               | AN11/PMA12/RB11                                                          |          | B45               | PMD14/RD6      |               |                       |

| B21               | Vdd                                                                      |          | B46               | No Connect     |               |                       |

| B22               | RPF13/RF13                                                               |          | B47               | No Connect     |               |                       |

| B23               | AN12/PMA11/RB12                                                          |          | B48               | VCAP           |               |                       |

| B24               | AN14/RPB14/CTED5/PMA1/RB14                                               |          | B49               | RPF0/PMD11/RF  | 0             |                       |

| B25               | Vss                                                                      |          | B50               | RPG1/PMD9/RG   | 1             |                       |

| B26               | RPD14/RD14                                                               |          | B51               | TRCLK/RA6      |               |                       |

| B27               | RPF4/PMA9/RF4                                                            |          | B52               | PMD0/RE0       |               |                       |

| B28               | No Connect                                                               |          | B53               | VDD            |               |                       |

| B29               | RPF8/RF8                                                                 |          | B54               | TRD2/RG14      |               |                       |

| B30               | VUSB3V3                                                                  |          | B55               | TRD0/RG13      |               |                       |

| B31               | D+                                                                       |          | B56               | RPE3/CTPLS/PM  | D3/RE3        |                       |

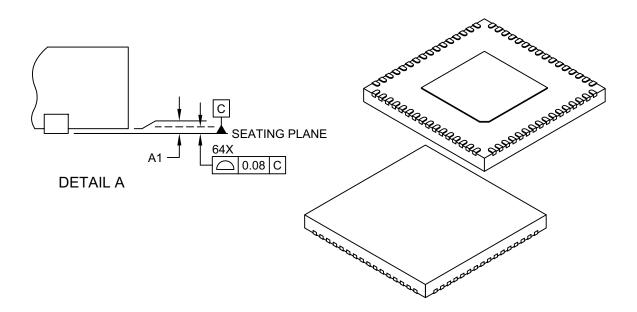

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: Shaded package bumps are 5V tolerant.

4: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

NOTES:

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/ 470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Memory" (DS60001121), Program which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX330/350/370/430/450/470 devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: On PIC32MX330/350/370/430/450/470 devices, the Flash page size is 4 KB and the row size is 512 bytes (1024 IW and 128 IW, respectively).

#### TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 3 REGISTER MAP

| ess                         |                                 | 0             |                                                                                        |                                                    |       |       |        |       |      | Bi     | its     |        |        |        |         |        |        |        |            |

|-----------------------------|---------------------------------|---------------|----------------------------------------------------------------------------------------|----------------------------------------------------|-------|-------|--------|-------|------|--------|---------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15                                                                                  | 30/14                                              | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8   | 23/7    | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH0CON                         | 31:16         | —                                                                                      | _                                                  |       | _     |        | _     | _    | _      | _       | _      | _      | _      | _       | _      | _      |        | 0000       |

| 3060                        | DCHUCON                         | 15:0          | CHBUSY                                                                                 | —                                                  | _     | —     | _      | —     | —    | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  | _       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3070                        | DCH0ECON                        | 31:16         | —                                                                                      | —                                                  | —     | —     | _      | —     | _    | —      |         | 1      | -      |        | Q<7:0>  | •      |        |        | 00FF       |

| 0070                        | DOINCEOUN                       | 15:0          |                                                                                        | CHSIRQ<7:0> CFORCE CABORT PATEN SIRQEN AIRQEN FFF8 |       |       |        |       |      |        |         |        |        |        |         |        |        |        |            |

| 3080                        | DCH0INT                         | 31:16         | —                                                                                      | —                                                  | —     | —     | -      | —     | —    | —      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0000                        | Borioitti                       | 15:0          | —                                                                                      | —                                                  | —     | —     | —      | —     | —    | —      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3090                        | DCH0SSA                         | 31:16<br>15:0 |                                                                                        | CHSSA<31:0>                                        |       |       |        |       |      |        |         |        |        |        |         |        |        |        |            |

|                             |                                 | 31:16         |                                                                                        | 0000                                               |       |       |        |       |      |        |         |        |        |        |         |        |        |        |            |

| 30A0                        | DCH0DSA                         | 15:0          |                                                                                        |                                                    |       |       |        |       |      | CHDSA  | A<31:0> |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         | _                                                                                      | _                                                  | _     |       | _      | _     | _    | _      | _       | _      | _      | _      | _       | _      |        | _      | 0000       |

| 30B0                        | DCH0SSIZ                        | 15:0          |                                                                                        |                                                    |       |       |        |       |      | CHSSIZ | Z<15:0> |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         | _                                                                                      |                                                    |       |       |        |       |      |        |         |        |        |        |         |        |        |        |            |

| 30C0                        | DCH0DSIZ                        | 15:0          |                                                                                        |                                                    |       |       |        |       |      | CHDSIZ | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 0000                        |                                 | 31:16         | —                                                                                      | _                                                  | —     | —     | —      | —     | —    | _      | —       |        | _      | —      | _       | _      | —      | _      | 0000       |

| 30D0                        | DCH0SPTR                        | 15:0          |                                                                                        |                                                    |       |       |        |       |      | CHSPT  | R<15:0> |        |        |        |         | •      |        |        | 0000       |

| 2050                        |                                 | 31:16         | _                                                                                      | _                                                  | _     | —     | _      | _     | _    | _      | _       | _      | _      | _      | _       | —      | _      | _      | 0000       |

| 30E0                        | DCH0DPTR                        | 15:0          |                                                                                        |                                                    |       |       |        |       |      | CHDPT  | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 2050                        | DCH0CSIZ                        | 31:16         | —                                                                                      |                                                    | _     | _     | _      | _     | _    | _      | _       | _      | _      | —      | _       | _      | _      | _      | 0000       |

| 30FU                        | DCHUCSIZ                        | 15:0          |                                                                                        |                                                    |       |       |        |       |      | CHCSIZ | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 3100                        | DCH0CPTR                        | 31:16         | —                                                                                      | _                                                  |       | —     |        | _     | _    | —      | _       | _      | _      | _      | _       | _      | _      |        | 0000       |

| 3100                        | DCHUCFTK                        | 15:0          |                                                                                        |                                                    |       |       |        |       |      | CHCPT  | R<15:0> |        | -      |        |         |        |        |        | 0000       |

| 3110                        | DCH0DAT                         | 31:16         | —                                                                                      | —                                                  |       | —     | _      | —     | —    | —      |         | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 5110                        | DONUDAI                         | 15:0          | —                                                                                      | —                                                  | _     | —     | _      |       | —    | —      |         |        |        | CHPDA  | AT<7:0> |        |        |        | 0000       |

| 3120                        | DCH1CON                         | 31:16         | —                                                                                      | —                                                  | _     | —     | —      |       | —    |        | —       | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 0120                        | Bonnoon                         | 15:0          | CHBUSY                                                                                 | —                                                  | —     | —     | _      | —     | —    | CHCHNS | CHEN    | CHAED  | CHCHN  | CHAEN  |         | CHEDET | CHPR   | l<1:0> | 0000       |

| 3130                        | DCH1ECON                        | 31:16         | —                                                                                      | —                                                  | —     | —     | —      | —     | —    | —      |         | 1      | -      |        | Q<7:0>  | -      |        |        | OOFF       |

| 0.00                        |                                 | 15:0          |                                                                                        |                                                    |       | CHSIR | Q<7:0> |       |      |        | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      |        | —      | FFF8       |

| 3140                        | DCH1INT                         | 31:16         | -                                                                                      | _                                                  | _     | —     | _      | —     | _    | —      | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 55                          |                                 | 15:0          | —                                                                                      | _                                                  | —     | —     | —      | —     | —    | -      | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3150                        | DCH1SSA                         | 31:16         | CHSSA<31:0>                                                                            |                                                    |       |       |        |       |      |        |         |        |        |        |         |        |        |        |            |

|                             |                                 | 15:0          |                                                                                        |                                                    |       |       |        |       |      |        |         |        |        |        |         |        |        |        | 0000       |

| 3160                        | DCH1DSA                         | 31:16         |                                                                                        |                                                    |       |       |        |       |      | CHDSA  | <31:0>  |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 15:0          | value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal. |                                                    |       |       |        |       |      |        |         |        |        |        |         |        |        |        |            |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

#### TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       |       | ,     |      |      | Bit  | s    |      |          |        |        |         |        | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | —     | —     |       | —     | _     | _     | —    | —    |      |      | —    | —        | —      | —      | —       | _      | 0000       |

| 5390                        | UIEF9                           | 15:0      | —     | _     |       |       | _     | _     | —    | —    | —    |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53A0                        | U1EP10                          | 31:16     | —     | _     |       | _     |       |       | _    |      |      |      | _    | —        | _      | _      | —       |        | 0000       |

| 53A0                        | UIEFIU                          | 15:0      | _     | _     |       | _     | -     | -     | _    | _    | _    |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 5560                        | UIEFII                          | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     | _     | _     | —     | _     | —     | —     | -    | -    | —    | —    | _    | —        | _      | _      | —       | _      | 0000       |

| 5300                        | UIEFIZ                          | 15:0      | _     | _     | —     | _     | —     | —     | -    | -    | —    | —    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     | _     |       | —     | _     | —     | —     |      | _    | _    | _    |      | —        | —      | _      | —       | _      | 0000       |

| 55D0                        | UIEF 13                         | 15:0      | _     | _     | —     | _     | —     | —     | -    | -    | —    | —    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     |       | _     | _     | _     | _     | _    | -    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     |       | _     | _     | _     | _     |      | _    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     |       | _     | _     | _     | _     |      | _    |      |      | _    | _        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     |       | _     | _     | _     | _     |      | _    | -    |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                              | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------------|------------------|

| 21.24        | U-0                                           | U-0              |

| 31:24        |                   | —                 | —                 | —                 |                   | —                 | —                                             | —                |

| 23:16        | U-0                                           | U-0              |

| 23.10        |                   |                   | _                 | _                 | _                 | _                 | _                                             | —                |

| 15:8         | U-0                                           | U-0              |

| 10.0         | _                 | _                 | _                 | _                 |                   | _                 | _                                             | —                |

|              | R/W-0                                         | R/W-0            |

| 7:0          | BTSEE             | BMXEE             | DMAEE             | BTOEE             | DFN8EE            | CRC16EE           | CRC5EE <sup>(1)</sup><br>EOFEE <sup>(2)</sup> | PIDEE            |

#### REGISTER 11-9: U1EIE: USB ERROR INTERRUPT ENABLE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | <b>BTSEE:</b> Bit Stuff Error Interrupt Enable bit |

|-------|----------------------------------------------------|

|       |                                                    |

- 1 = BTSEF interrupt is enabled

- 0 = BTSEF interrupt is disabled

- bit 6 BMXEE: Bus Matrix Error Interrupt Enable bit

- 1 = BMXEF interrupt is enabled

- 0 = BMXEF interrupt is disabled

- bit 5 **DMAEE:** DMA Error Interrupt Enable bit

- 1 = DMAEF interrupt is enabled

- 0 = DMAEF interrupt is disabled

- bit 4 BTOEE: Bus Turnaround Time-out Error Interrupt Enable bit

- 1 = BTOEF interrupt is enabled

- 0 = BTOEF interrupt is disabled

- bit 3 **DFN8EE:** Data Field Size Error Interrupt Enable bit

- 1 = DFN8EF interrupt is enabled

- 0 = DFN8EF interrupt is disabled

- bit 2 CRC16EE: CRC16 Failure Interrupt Enable bit

- 1 = CRC16EF interrupt is enabled

- 0 = CRC16EF interrupt is disabled

- bit 1 CRC5EE: CRC5 Host Error Interrupt Enable bit<sup>(1)</sup>

- 1 = CRC5EF interrupt is enabled

- 0 = CRC5EF interrupt is disabled

- EOFEE: EOF Error Interrupt Enable bit<sup>(2)</sup>

- 1 = EOF interrupt is enabled

- 0 = EOF interrupt is disabled

- bit 0 PIDEE: PID Check Failure Interrupt Enable bit

- 1 = PIDEF interrupt is enabled

- 0 = PIDEF interrupt is disabled

#### Note 1: Device mode.

2: Host mode.

Note: For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

## 12.1 Parallel I/O (PIO) Ports

All port pins have ten registers directly associated with their operation as digital I/O. The data direction register (TRISx) determines whether the pin is an input or an output. If the data direction bit is a '1', then the pin is an input. All port pins are defined as inputs after a Reset. Reads from the latch (LATx) read the latch. Writes to the latch write the latch. Reads from the port (PORTx) read the port pins, while writes to the port pins write the latch.

#### 12.1.1 OPEN-DRAIN CONFIGURATION

In addition to the PORTx, LATx, and TRISx registers for data control, some port pins can also be individually configured for either digital or open-drain output. This is controlled by the Open-Drain Control register, ODCx, associated with each port. Setting any of the bits configures the corresponding pin to act as an open-drain output.

The open-drain feature allows the presence of outputs higher than VDD (e.g., 5V) on any desired 5V-tolerant pins by using external pull-up resistors. The maximum open-drain voltage allowed is the same as the maximum VIH specification.

See the **"Device Pin Tables"** section for the available pins and their functionality.

# 12.1.2 CONFIGURING ANALOG AND DIGITAL PORT PINS

The ANSELx register controls the operation of the analog port pins. The port pins that are to function as analog inputs must have their corresponding ANSEL and TRIS bits set. In order to use port pins for I/O functionality with digital modules, such as Timers, UARTs, etc., the corresponding ANSELx bit must be cleared.

The ANSELx register has a default value of 0xFFFF; therefore, all pins that share analog functions are analog (not digital) by default.

If the TRIS bit is cleared (output) while the ANSELx bit is set, the digital output level (VOH or VOL) is converted by an analog peripheral, such as the ADC module or Comparator module.

When the PORT register is read, all pins configured as analog input channels are read as cleared (a low level).

Pins configured as digital inputs do not convert an analog input. Analog levels on any pin defined as a digital input (including the ANx pins) can cause the input buffer to consume current that exceeds the device specifications.

#### 12.1.3 I/O PORT WRITE/READ TIMING

One instruction cycle is required between a port direction change or port write operation and a read operation of the same port. Typically this instruction would be an NOP.

#### 12.1.4 INPUT CHANGE NOTIFICATION

The input change notification function of the I/O ports allows the PIC32MX330/350/370/430/450/470 devices to generate interrupt requests to the processor in response to a change-of-state on selected input pins. This feature can detect input change-of-states even in Sleep mode, when the clocks are disabled. Every I/O port pin can be selected (enabled) for generating an interrupt request on a change-of-state.

Five control registers are associated with the CN functionality of each I/O port. The CNENx registers contain the CN interrupt enable control bits for each of the input pins. Setting any of these bits enables a CN interrupt for the corresponding pins.

The CNSTATx register indicates whether a change occurred on the corresponding pin since the last read of the PORTx bit.

Each I/O pin also has a weak pull-up and every I/O pin has a weak pull-down connected to it. The pullups act as a current source or sink source connected to the pin, and eliminate the need for external resistors when push-button or keypad devices are connected. The pull-ups and pull-downs are enabled separately using the CNPUx and the CNPDx registers, which contain the control bits for each of the pins. Setting any of the control bits enables the weak pull-ups and/or pull-downs for the corresponding pins.

| Note: | Pull-ups and pull-downs on change notifi-<br>cation pins should always be disabled<br>when the port pin is configured as a digital |

|-------|------------------------------------------------------------------------------------------------------------------------------------|

|       | output. They should also be disabled on                                                                                            |

|       | 5V tolerant pins when the pin voltage can                                                                                          |

|       | exceed VDD.                                                                                                                        |

An additional control register (CNCONx) is shown in Register 12-3.

# 12.2 CLR, SET, and INV Registers

Every I/O module register has a corresponding CLR (clear), SET (set) and INV (invert) register designed to provide fast atomic bit manipulations. As the name of the register implies, a value written to a SET, CLR or INV register effectively performs the implied operation, but only on the corresponding base register and only bits specified as '1' are modified. Bits specified as '0' are not modified.

Reading SET, CLR and INV registers returns undefined values. To see the affects of a write operation to a SET, CLR or INV register, the base register must be read.

## 12.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only options.

Peripheral pin select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. Peripheral pin select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

#### 12.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

### 12.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the peripheral pin select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the peripheral pin select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral. When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

#### 12.3.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

#### 12.3.4 INPUT MAPPING

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 12-1, are used to configure peripheral input mapping (see Register 12-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 12-1.

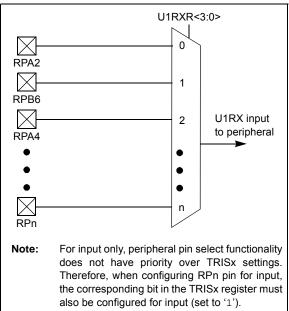

For example, Figure 12-2 illustrates the remappable pin selection for the U1RX input.

# FIGURE 12-2:

REMAPPABLE INPUT EXAMPLE FOR U1RX

### 12.4 Control Registers

|                             | PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY |           |               |               |       |       |       |               |              |      |              |              |              |              |              |              |              |              |               |

|-----------------------------|-------------------------------------------------------------------------------------|-----------|---------------|---------------|-------|-------|-------|---------------|--------------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess (                       |                                                                                     | Ð         |               |               |       |       |       |               |              | Bi   | ts           |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup>                                                     | Bit Range | 31/15         | 30/14         | 29/13 | 28/12 | 27/11 | 26/10         | 25/9         | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6000                        | ANSELA                                                                              | 31:16     | —             | —             | _     | —     | _     | —             | —            | _    | —            | —            | —            | _            | —            | —            | —            | _            | 0000          |

| 0000                        | ANOLLA                                                                              | 15:0      | —             | —             | _     | —     | _     | ANSELA10      | ANSELA9      | _    | _            |              | _            | _            |              |              | —            | _            | 0060          |

| 6010                        | TRISA                                                                               | 31:16     | —             | —             | -     | —     | _     | —             | —            |      | _            | —            | _            |              | —            | —            | _            |              | 0000          |

|                             |                                                                                     | 15:0      | TRISA15       | TRISA14       | _     | —     | _     | TRISA10       | TRISA9       | —    | TRISA7       | TRISA6       | TRISA5       | TRISA4       | TRISA3       | TRISA2       | TRISA1       | TRISA0       | xxxx          |

| 6020                        | PORTA                                                                               | 31:16     | —             | —             | _     | —     |       | —             | _            |      | _            |              | _            | —            |              |              | —            | —            | 0000          |

|                             | -                                                                                   | 15:0      | RA15          | RA14          | _     | —     | _     | RA10          | RA9          | _    | RA7          | RA6          | RA5          | RA4          | RA3          | RA2          | RA1          | RA0          | xxxx          |

| 6030                        | LATA                                                                                | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                                                                     | 15:0      | LATA15        | LATA14        | —     | —     | —     | LATA10        | LATA9        | —    | LATA7        | LATA6        | LATA5        | LATA4        | LATA3        | LATA2        | LATA1        | LATA0        | xxxx          |

| 6040                        | ODCA                                                                                | 31:16     | —             | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                                                                     | 15:0      | ODCA15        | ODCA14        | —     | —     | —     | ODCA10        | ODCA9        | —    | ODCA7        | ODCA6        | ODCA5        | ODCA4        | ODCA3        | ODCA2        | ODCA1        | ODCA0        | xxxx          |

| 6050                        | CNPUA                                                                               | 31:16     |               |               | _     | —     | _     | _             |              |      | —            |              | _            | _            |              |              |              | _            | 0000          |

|                             |                                                                                     |           | CNPUA15       | CNPUA14       | _     | —     | _     | CNPUA10       | CNPUA9       | _    | CNPUA7       | CNPUA6       | CNPUA5       | CNPUA4       | CNPUA3       | CNPUA2       | CNPUA1       | CNPUA0       | _             |

| 6060                        | CNPDA                                                                               | 31:16     | —             | —             | _     | —     | _     | —             | —            | _    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                                                                     |           | CNPDA15       | CNPDA14       | —     |       | _     | CNPDA10       | CNPDA9       | _    | CNPDA7       | CNPDA6       | CNPDA5       | CNPDA4       | CNPDA3       | CNPDA2       | CNPDA1       | CNPDA0       |               |

| 6070                        | CNCONA                                                                              | 31:16     |               |               |       | —     | _     | _             |              |      | _            |              |              |              |              |              |              |              | 0000          |

|                             |                                                                                     | 15:0      | ON            |               | SIDL  | —     | _     | _             |              |      | _            |              |              |              |              |              |              |              | 0000          |

| 6080                        | CNENA                                                                               | 31:16     | -             | -             | _     | _     | _     | -             | -            | _    | -            | -            | -            | —            | —            | —            | —            | —            | 0000          |

|                             |                                                                                     | 15:0      | CNIEA15       |               | _     | —     | _     | CNIEA10       | CNIEA9       | —    | CNIEA7       | CNIEA6       | CNIEA5       | CNIEA4       | CNIEA3       | CNIEA2       | CNIEA1       | CNIEA0       | XXXX          |

| 6000                        | CNSTATA                                                                             | 31:16     | -             | -             | _     | —     | _     | -             | -            | —    | -            | -            | -            | —            | -            | -            | -            | —            | 0000          |

| 0090                        | CINGTATA                                                                            | 15:0      | CN<br>STATA15 | CN<br>STATA14 | _     | —     | _     | CN<br>STATA10 | CN<br>STATA9 | —    | CN<br>STATA7 | CN<br>STATA6 | CN<br>STATA5 | CN<br>STATA4 | CN<br>STATA3 | CN<br>STATA2 | CN<br>STATA1 | CN<br>STATA0 | xxxx          |

# TABLE 12-3:PORTA REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,<br/>PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

NOTES:

#### 20.1 **Control Registers**

#### TABLE 20-1: UART1 THROUGH UART5 REGISTER MAP

| ess)                        |                       | Ð         |        |                               |        |       |        |       |       | Bi          | ts          |         |       |          |          |       |        |       | s          |

|-----------------------------|-----------------------|-----------|--------|-------------------------------|--------|-------|--------|-------|-------|-------------|-------------|---------|-------|----------|----------|-------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15  | 30/14                         | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2  | 17/1   | 16/0  | All Resets |

| 6000                        | U1MODE <sup>(1)</sup> | 31:16     | _      |                               | -      | _     | _      |       |       | _           | _           | —       | _     | _        |          | _     |        |       | 0000       |

| 0000                        | UTMODE: /             | 15:0      | ON     |                               | SIDL   | IREN  | RTSMD  |       | UEN   | <1:0>       | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 6010                        | U1STA <sup>(1)</sup>  | 31:16     | —      | _                             | —      | _     | —      | _     | _     | ADM_EN      |             |         |       | ADDR     | <7:0>    |       |        |       | 0000       |

| 0010                        | 01317                 | 15:0      | UTXISE | L<1:0>                        | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | FFFF       |

| 6020                        | U1TXREG               | 31:16     | —      | _                             | —      | _     | —      | _     | _     | —           | _           | _       | —     | —        | _        | —     | _      | _     | 0000       |

| 0020                        | UTIXILEO              | 15:0      | —      | _                             | —      | _     | _      | _     | _     | TX8         |             |         |       | Transmit | Register |       |        |       | 0000       |

| 6030                        | U1RXREG               | 31:16     | —      | —                             | —      | —     | —      | —     | —     | —           | —           | —       | —     | —        | —        | —     | —      | —     | 0000       |

| 0000                        | ONVILO                | 15:0      | —      | —                             | —      | —     | —      | —     | —     | RX8         |             |         |       | Receive  | Register |       |        |       | 0000       |

| 6040                        | U1BRG <sup>(1)</sup>  | 31:16     | —      | —                             | —      | —     | —      | —     | —     | —           |             | —       | —     | —        | —        | —     | —      | —     | 0000       |

| 0010                        | OTDICO                | 15:0      |        | Baud Rate Generator Prescaler |        |       |        |       |       |             |             | 0000    |       |          |          |       |        |       |            |

| 6200                        | U2MODE <sup>(1)</sup> | 31:16     | —      | —                             | —      | —     | —      | —     | —     | —           | _           | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                       | 15:0      | ON     | —                             | SIDL   | IREN  | RTSMD  | —     | UEN   |             | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 6210                        | U2STA <sup>(1)</sup>  | 31:16     | —      | —                             | —      | _     | —      | —     | —     | ADM_EN      |             |         | 1     | ADDR     |          |       |        |       | 0000       |

|                             |                       | 15:0      | UTXISE | L<1:0>                        | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | FFFF       |

| 6220                        | U2TXREG               | 31:16     | _      |                               | _      | _     | _      | _     |       | —           | _           | —       | —     |          | —        | _     | —      | _     | 0000       |

|                             |                       | 15:0      | _      |                               | _      | _     | _      | _     |       | TX8         |             |         |       | Transmit | Register |       |        |       | 0000       |

| 6230                        | U2RXREG               | 31:16     | —      | —                             | —      | —     | —      | —     | —     | —           | _           | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                       | 15:0      | —      | —                             | —      | —     | —      | —     | —     | RX8         |             |         |       | Receive  | Register |       |        |       | 0000       |

| 6240                        | U2BRG <sup>(1)</sup>  | 31:16     | _      | _                             | _      | _     | —      | —     |       | —           | _           | —       | —     | _        | —        | _     | —      | —     | 0000       |

|                             |                       | 15:0      |        |                               |        |       |        |       | Bau   | d Rate Gene | erator Pres | caler   |       |          |          |       |        |       | 0000       |

| 6400                        | U3MODE <sup>(1)</sup> | 31:16     | _      | _                             | —      | _     | —      | _     | _     | —           |             | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                       | 15:0      | ON     | _                             | SIDL   | IREN  | RTSMD  | _     | UEN   | -           | WAKE        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 6410                        | U3STA <sup>(1)</sup>  | 31:16     | —      |                               |        |       |        |       |       |             |             |         | 0000  |          |          |       |        |       |            |

|                             |                       | 15:0      | UTXISE | :L<1:0>                       | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE      | =L<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | FFFF       |

| 6420                        | U3TXREG               | 31:16     | _      | _                             |        | —     | _      | _     | _     | —<br>       | —           | —       | —     | —<br>—   | —        | -     | —      | —     | 0000       |

|                             |                       | 15:0      | -      | _                             | —      | _     | _      | _     |       | TX8         |             |         |       | Transmit | -        |       |        |       | 0000       |

| 6430                        | U3RXREG               | 31:16     | _      | _                             | _      | _     | _      | _     | _     | -           | _           | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                       | 15:0      | — [    | —                             |        |       |        |       |       |             |             |         |       |          |          |       |        |       |            |

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV registers" for more informa-Note 1: tion.

NOTES:

NOTES:

### 27.4 Peripheral Module Disable

The Peripheral Module Disable (PMD) registers provide a method to disable a peripheral module by stopping all clock sources supplied to that module. When a peripheral is disabled using the appropriate PMD control bit, the peripheral is in a minimum power consumption state. The control and status registers associated with the peripheral are also disabled, so writes to those registers do not have effect and read values are invalid. To disable a peripheral, the associated PMDx bit must be set to '1'. To enable a peripheral, the associated PMDx bit must be cleared (default). See Table 27-1 for more information.

Note: Disabling a peripheral module while it's ON bit is set, may result in undefined behavior. The ON bit for the associated peripheral module must be cleared prior to disable a module via the PMDx bits.

| TABLE 27-1: | PERIPHERAL MODULE DISABLE BITS AND LOCATIONS |

|-------------|----------------------------------------------|

|             |                                              |

| Peripheral <sup>(1)</sup>    | PMDx bit Name <sup>(1)</sup> | Register Name and Bit Location |

|------------------------------|------------------------------|--------------------------------|

| ADC1                         | AD1MD                        | PMD1<0>                        |

| СТМИ                         | CTMUMD                       | PMD1<8>                        |

| Comparator Voltage Reference | CVRMD                        | PMD1<12>                       |

| Comparator 1                 | CMP1MD                       | PMD2<0>                        |

| Comparator 2                 | CMP2MD                       | PMD2<1>                        |

| Input Capture 1              | IC1MD                        | PMD3<0>                        |

| Input Capture 2              | IC2MD                        | PMD3<1>                        |

| Input Capture 3              | IC3MD                        | PMD3<2>                        |

| Input Capture 4              | IC4MD                        | PMD3<3>                        |

| Input Capture 5              | IC5MD                        | PMD3<4>                        |

| Output Compare 1             | OC1MD                        | PMD3<16>                       |

| Output Compare 2             | OC2MD                        | PMD3<17>                       |

| Output Compare 3             | OC3MD                        | PMD3<18>                       |

| Output Compare 4             | OC4MD                        | PMD3<19>                       |

| Output Compare 5             | OC5MD                        | PMD3<20>                       |

| Timer1                       | T1MD                         | PMD4<0>                        |

| Timer2                       | T2MD                         | PMD4<1>                        |

| Timer3                       | T3MD                         | PMD4<2>                        |

| Timer4                       | T4MD                         | PMD4<3>                        |

| Timer5                       | T5MD                         | PMD4<4>                        |

| UART1                        | U1MD                         | PMD5<0>                        |

| UART2                        | U2MD                         | PMD5<1>                        |

| UART3                        | U3MD                         | PMD5<2>                        |

| UART4                        | U4MD                         | PMD5<3>                        |

| UART5                        | U5MD                         | PMD5<4>                        |

| SPI1                         | SPI1MD                       | PMD5<8>                        |

| SPI2                         | SPI2MD                       | PMD5<9>                        |

| I2C1                         | I2C1MD                       | PMD5<16>                       |

| 2C2                          | I2C2MD                       | PMD5<17>                       |

| USB <sup>(2)</sup>           | USBMD                        | PMD5<24>                       |

| RTCC                         | RTCCMD                       | PMD6<0>                        |

| Reference Clock Output       | REFOMD                       | PMD6<1>                        |

| PMP                          | PMPMD                        | PMD6<16>                       |

Note 1: Not all modules and associated PMDx bits are available on all devices. See TABLE 1: "PIC32MX330/350/ 370/430/450/470 Controller Family Features" for the lists of available peripherals.

2: Module must not be busy after clearing the associated ON bit and prior to setting the USBMD bit.

#### REGISTER 28-2: DEVCFG1: DEVICE CONFIGURATION WORD 1 (CONTINUED)

- bit 15-14 FCKSM<1:0>: Clock Switching and Monitor Selection Configuration bits

- 1x = Clock switching is disabled, Fail-Safe Clock Monitor is disabled

- 01 = Clock switching is enabled, Fail-Safe Clock Monitor is disabled

- 00 = Clock switching is enabled, Fail-Safe Clock Monitor is enabled

- bit 13-12 FPBDIV<1:0>: Peripheral Bus Clock Divisor Default Value bits

- 11 = PBCLK is SYSCLK divided by 8

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- bit 11 Reserved: Write '1'

- bit 10 OSCIOFNC: CLKO Enable Configuration bit

- 1 = CLKO output is disabled

- 0 = CLKO output signal active on the OSCO pin; Primary Oscillator must be disabled or configured for the External Clock mode (EC) for the CLKO to be active (POSCMOD<1:0> = 11 or 00)

- bit 9-8 **POSCMOD<1:0>:** Primary Oscillator Configuration bits

- 11 = Primary Oscillator is disabled

- 10 = HS Oscillator mode is selected

- 01 = XT Oscillator mode is selected

- 00 = External Clock mode is selected

- bit 7 IESO: Internal External Switchover bit

- 1 = Internal External Switchover mode is enabled (Two-Speed Start-up is enabled)

- 0 = Internal External Switchover mode is disabled (Two-Speed Start-up is disabled)

- bit 6 **Reserved:** Write '1'

- bit 5 **FSOSCEN:** Secondary Oscillator Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 4-3 Reserved: Write '1'

- bit 2-0 **FNOSC<2:0>:** Oscillator Selection bits

- 111 = Fast RC Oscillator with divide-by-N (FRCDIV)

- 110 = FRCDIV16 Fast RC Oscillator with fixed divide-by-16 postscaler

- 101 = Low-Power RC Oscillator (LPRC)

- 100 = Secondary Oscillator (Sosc)

- 011 = Primary Oscillator (Posc) with PLL module (XT+PLL, HS+PLL, EC+PLL)

- 010 = Primary Oscillator (XT, HS, EC)<sup>(1)</sup>

- 001 = Fast RC Oscillator with divide-by-N with PLL module (FRCDIV+PLL)

- 000 = Fast RC Oscillator (FRC)

- **Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

| Bit<br>3/15/7<br>R          | Bit<br>30/22/14/6<br>R | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                        | Bit<br>26/18/10/2                                                                   | Bit<br>25/17/9/1                                                                        | Bit<br>24/16/8/0                                               |  |  |  |  |  |  |

|-----------------------------|------------------------|-------------------|-------------------|------------------------------------------|-------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|----------------------------------------------------------------|--|--|--|--|--|--|

| R                           | R                      | Р                 |                   |                                          |                                                                                     |                                                                                         | 24/10/0/0                                                      |  |  |  |  |  |  |

|                             |                        | R                 | R                 | R                                        | R                                                                                   | R                                                                                       | R                                                              |  |  |  |  |  |  |

| VER<3:0> <sup>(1)</sup>     |                        |                   |                   |                                          | DEVID<27:24> <sup>(1)</sup>                                                         |                                                                                         |                                                                |  |  |  |  |  |  |

| R                           | R                      | R                 | R                 | R                                        | R                                                                                   | R                                                                                       | R                                                              |  |  |  |  |  |  |

| DEVID<23:16> <sup>(1)</sup> |                        |                   |                   |                                          |                                                                                     |                                                                                         |                                                                |  |  |  |  |  |  |

| R                           | R                      | R                 | R                 | R                                        | R                                                                                   | R                                                                                       | R                                                              |  |  |  |  |  |  |

| DEVID<15:8> <sup>(1)</sup>  |                        |                   |                   |                                          |                                                                                     |                                                                                         |                                                                |  |  |  |  |  |  |

| R                           | R                      | R                 | R                 | R                                        | R                                                                                   | R                                                                                       | R                                                              |  |  |  |  |  |  |

|                             |                        |                   | DEVID<            | 7:0>(1)                                  | DEVID<7:0> <sup>(1)</sup>                                                           |                                                                                         |                                                                |  |  |  |  |  |  |

| R                           | 2                      | R R               | R R               | DEVID<2<br>R R R R<br>DEVID<7<br>R R R R | DEVID<23:16> <sup>(1)</sup><br>R R R R R<br>DEVID<15:8> <sup>(1)</sup><br>R R R R R | DEVID<23:16> <sup>(1)</sup><br>R R R R R R<br>DEVID<15:8> <sup>(1)</sup><br>R R R R R R | DEVID<23:16>(1)   R R R R   DEVID<15:8> <sup>(1)</sup> R R R R |  |  |  |  |  |  |

#### REGISTER 28-6: DEVID: DEVICE AND REVISION ID REGISTER

#### Legend:

| Logona.           |                  |                            |                    |

|-------------------|------------------|----------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, rea | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared       | x = Bit is unknown |

bit 31-28 VER<3:0>: Revision Identifier bits<sup>(1)</sup>

bit 27-0 **DEVID<27:0>:** Device ID<sup>(1)</sup>

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

| DC CHARACTERISTICS |        |                                                                     | $\begin{tabular}{ c c c c c } \hline Standard Operating Conditions: 2.3V to 3.6V \\ \hline (unless otherwise stated) \\ \hline Operating temperature & 0°C \leq TA \leq +70°C for Commercial \\ -40°C \leq TA \leq +85°C for Industrial \\ -40°C \leq TA \leq +105°C for V-temp \\ \hline \end{tabular}$ |         |       |       |            |  |

|--------------------|--------|---------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|-------|-------|------------|--|

| Param.<br>No.      | Symbol | Characteristics                                                     | Min.                                                                                                                                                                                                                                                                                                     | Typical | Max.  | Units | Conditions |  |

| Operating Voltage  |        |                                                                     |                                                                                                                                                                                                                                                                                                          |         |       |       |            |  |

| DC10               | Vdd    | Supply Voltage                                                      | 2.3                                                                                                                                                                                                                                                                                                      | _       | 3.6   | V     | _          |  |

| DC12               | Vdr    | RAM Data Retention Voltage<br>(Note 1)                              | 1.75                                                                                                                                                                                                                                                                                                     | —       | _     | V     | _          |  |

| DC16               | VPOR   | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal    | 1.75                                                                                                                                                                                                                                                                                                     | _       | 2.1   | V     | _          |  |

| DC17               | SVDD   | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal | 0.00005                                                                                                                                                                                                                                                                                                  | _       | 0.115 | V/µs  | _          |  |

### TABLE 31-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

#### TABLE 31-10: ELECTRICAL CHARACTERISTICS: BOR

| DC CHARACTERISTICS |        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                     |         |      |       |            |

|--------------------|--------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------|---------|------|-------|------------|

| Param.<br>No.      | Symbol | Characteristics                                                                                                                                                                                                                                                                                                                                    | Min. <sup>(1)</sup> | Typical | Max. | Units | Conditions |

| BO10               | VBOR   | BOR Event on VDD transition<br>high-to-low                                                                                                                                                                                                                                                                                                         | 2.0                 | —       | 2.3  | V     | _          |

Note 1: Parameters are for design guidance only and are not tested in manufacturing.

#### TABLE 31-11: ELECTRICAL CHARACTERISTICS: HVD

| DC CHARACTERISTICS           |                                                      | Standard Operating Conditions: 2.3V to 3.6V(unless otherwise stated)Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |      |         |      |       |            |