Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 256KB (256K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 64K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx450f256lt-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## 2.9 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

## 2.10 EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations

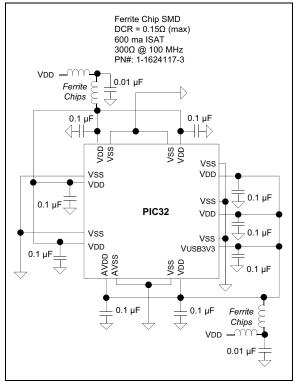

The use of LDO regulators is preferred to reduce overall system noise and provide a cleaner power source. However, when utilizing switching Buck/ Boost regulators as the local power source for PIC32 devices, as well as in electrically noisy environments or test conditions required for IEC 61000-4-4 and IEC 61000-4-2, users should evaluate the use of T-Filters (i.e., L-C-L) on the power pins, as shown in Figure 2-5. In addition to a more stable power source, use of this type of T-Filter can greatly reduce susceptibility to EMI sources and events.

FIGURE 2-5: EMI/EMC/EFT SUPPRESSION CIRCUIT

The MIPS architecture defines that the result of a multiply or divide operation be placed in the HI and LO registers. Using the Move-From-HI (MFHI) and Move-From-LO (MFLO) instructions, these values can be transferred to the General Purpose Register file.

In addition to the HI/LO targeted operations, the MIPS32<sup>®</sup> architecture also defines a multiply instruction, MUL, which places the least significant results in the primary register file instead of the HI/LO register pair. By avoiding the explicit MFLO instruction required when using the LO register, and by supporting multiple destination registers, the throughput of multiply-intensive operations is increased.

Two other instructions, Multiply-Add (MADD) and Multiply-Subtract (MSUB), are used to perform the multiply-accumulate and multiply-subtract operations. The MADD instruction multiplies two numbers and then adds the product to the current contents of the HI and LO registers. Similarly, the MSUB instruction multiplies two operands and then subtracts the product from the HI and LO registers. The MADD and MSUB operations are commonly used in DSP algorithms.

### 3.2.3 SYSTEM CONTROL COPROCESSOR (CP0)

In the MIPS architecture, CP0 is responsible for the virtual-to-physical address translation, the exception control system, the processor's diagnostics capability, the operating modes (Kernel, User and Debug) and whether interrupts are enabled or disabled. Configuration information, such as presence of options like MIPS16e<sup>®</sup>, is also available by accessing the CP0 registers, listed in Table 3-2.

| Reserved<br>HWREna<br>BadVAddr <sup>(1)</sup><br>Count <sup>(1)</sup><br>Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup> | Reserved in the PIC32MX330/350/370/430/450/470 family core.         Enables access via the RDHWR instruction to selected hardware registers.         Reports the address for the most recent address-related exception.         Processor cycle count.         Reserved in the PIC32MX330/350/370/430/450/470 family core.         Timer interrupt control. |

|--------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BadVAddr <sup>(1)</sup><br>Count <sup>(1)</sup><br>Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                       | Reports the address for the most recent address-related exception.<br>Processor cycle count.<br>Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                 |

| Count <sup>(1)</sup><br>Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                                                  | Processor cycle count.<br>Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                       |

| Reserved<br>Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                                                                          | Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                                                 |

| Compare <sup>(1)</sup><br>Status <sup>(1)</sup>                                                                                      |                                                                                                                                                                                                                                                                                                                                                             |

| Status <sup>(1)</sup>                                                                                                                | Timer interrupt control.                                                                                                                                                                                                                                                                                                                                    |

|                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                             |

| (4)                                                                                                                                  | Processor status and control.                                                                                                                                                                                                                                                                                                                               |

| IntCtl <sup>(1)</sup>                                                                                                                | Interrupt system status and control.                                                                                                                                                                                                                                                                                                                        |

| SRSCtl <sup>(1)</sup>                                                                                                                | Shadow register set status and control.                                                                                                                                                                                                                                                                                                                     |

| SRSMap <sup>(1)</sup>                                                                                                                | Provides mapping from vectored interrupt to a shadow set.                                                                                                                                                                                                                                                                                                   |

| Cause <sup>(1)</sup>                                                                                                                 | Cause of last general exception.                                                                                                                                                                                                                                                                                                                            |

| EPC <sup>(1)</sup>                                                                                                                   | Program counter at last exception.                                                                                                                                                                                                                                                                                                                          |

| PRId                                                                                                                                 | Processor identification and revision.                                                                                                                                                                                                                                                                                                                      |

| EBASE                                                                                                                                | Exception vector base register.                                                                                                                                                                                                                                                                                                                             |

| Config                                                                                                                               | Configuration register.                                                                                                                                                                                                                                                                                                                                     |

| Config1                                                                                                                              | Configuration register 1.                                                                                                                                                                                                                                                                                                                                   |

| Config2                                                                                                                              | Configuration register 2.                                                                                                                                                                                                                                                                                                                                   |

| Config3                                                                                                                              | Configuration register 3.                                                                                                                                                                                                                                                                                                                                   |

| Reserved                                                                                                                             | Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                                                 |

| Debug <sup>(2)</sup>                                                                                                                 | Debug control and exception status.                                                                                                                                                                                                                                                                                                                         |

| DEPC <sup>(2)</sup>                                                                                                                  | Program counter at last debug exception.                                                                                                                                                                                                                                                                                                                    |

| Reserved                                                                                                                             | Reserved in the PIC32MX330/350/370/430/450/470 family core.                                                                                                                                                                                                                                                                                                 |

| ErrorEPC <sup>(1)</sup>                                                                                                              | Program counter at last error.                                                                                                                                                                                                                                                                                                                              |

| DESAVE <sup>(2)</sup>                                                                                                                | Debug handler scratchpad register.                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                                      | RSMap <sup>(1)</sup><br>Cause <sup>(1)</sup><br>PC <sup>(1)</sup><br>PRId<br>BASE<br>Config<br>Config1<br>Config2<br>Config3<br>Reserved<br>Debug <sup>(2)</sup><br>DEPC <sup>(2)</sup><br>Reserved<br>ErrorEPC <sup>(1)</sup>                                                                                                                              |

TABLE 3-2: COPROCESSOR 0 REGISTERS

Note 1: Registers used in exception processing.

2: Registers used during debug.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|----------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| 24.24        | U-0               | U-0                  | R/W-y R/W-y       |                   | R/W-y             | R/W-0                 | R/W-0            | R/W-1            |

| 31:24        | _                 | —                    | Р                 | LLODIV<2:0>       | >                 | F                     | RCDIV<2:0>       |                  |

| 22:16        | U-0               | R-0                  | R-1               | R/W-y             | R/W-y             | R/W-y                 | R/W-y            | R/W-y            |

| 23:16        | —                 | SOSCRDY              | PBDIVRDY          | PBDIV             | /<1:0>            | Р                     | LLMULT<2:0>      |                  |

| 45.0         | U-0               | R-0                  | R-0               | R-0               | U-0               | R/W-y                 | R/W-y            | R/W-y            |

| 15:8         | —                 |                      | COSC<2:0>         |                   | —                 | NOSC<2:0>             |                  |                  |

| 7:0          | R/W-0             | R-0                  | R-0               | R/W-0             | R/W-0             | R/W-0                 | R/W-y            | R/W-0            |

| 7:0          | CLKLOCK           | ULOCK <sup>(1)</sup> | SLOCK             | SLPEN             | CF                | UFRCEN <sup>(1)</sup> | SOSCEN           | OSWEN            |

## Legend:

y = Value set from Configuration bits on POR

| Legena.           | y - value set nom conne |                           |                    |

|-------------------|-------------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-30 Unimplemented: Read as '0'

- bit 29-27 PLLODIV<2:0>: Output Divider for PLL

- 111 = PLL output divided by 256

- 110 = PLL output divided by 64

- 101 = PLL output divided by 32

- 100 = PLL output divided by 16

- 011 = PLL output divided by 8

- 010 = PLL output divided by 4

- 001 = PLL output divided by 2

- 000 = PLL output divided by 1

### bit 26-24 FRCDIV<2:0>: Internal Fast RC (FRC) Oscillator Clock Divider bits

- 111 = FRC divided by 256

- 110 = FRC divided by 64

- 101 = FRC divided by 32

- 100 = FRC divided by 16

- 011 = FRC divided by 8

- 010 = FRC divided by 4

- 001 = FRC divided by 2 (default setting)

- 000 = FRC divided by 1

- bit 23 Unimplemented: Read as '0'

- bit 22 SOSCRDY: Secondary Oscillator (Sosc) Ready Indicator bit

- 1 = Indicates that the Secondary Oscillator is running and is stable

- 0 = Secondary Oscillator is still warming up or is turned off

- bit 21 PBDIVRDY: Peripheral Bus Clock (PBCLK) Divisor Ready bit

- 1 = PBDIV<1:0> bits can be written

- 0 = PBDIV<1:0> bits cannot be written

- bit 20-19 **PBDIV<1:0>:** Peripheral Bus Clock (PBCLK) Divisor bits

- 11 = PBCLK is SYSCLK divided by 8 (default)

- 10 = PBCLK is SYSCLK divided by 4

- 01 = PBCLK is SYSCLK divided by 2

- 00 = PBCLK is SYSCLK divided by 1

- Note 1: This bit is available on PIC32MX4XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

## 9.2 Control Registers

## TABLE 9-1: PREFETCH REGISTER MAP

| ess                         |                       |               |               |             |           |             |             |            |            | Bit        | s       |      |       |            |         |       |          |        |              |

|-----------------------------|-----------------------|---------------|---------------|-------------|-----------|-------------|-------------|------------|------------|------------|---------|------|-------|------------|---------|-------|----------|--------|--------------|

| Virtual Address<br>(BF88_#) | Register<br>Name      | Bit Range     | 31/15         | 30/14       | 29/13     | 28/12       | 27/11       | 26/10      | 25/9       | 24/8       | 23/7    | 22/6 | 21/5  | 20/4       | 19/3    | 18/2  | 17/1     | 16/0   | All Resets   |

| 4000                        | CHECON <sup>(1)</sup> | 31:16         | —             | _           | —         | —           |             | _          | —          | —          | _       |      | —     |            | —       | —     |          | CHECOH | 0000         |

| 1000                        |                       | 15:0          | —             | _           |           | —           | _           | _          | DCSZ       | <1:0>      | —       |      | PREFE | N<1:0>     | —       | P     | FMWS<2:0 | )>     | 0007         |

| 4010                        | CHEACC <sup>(1)</sup> |               | CHEWEN        | —           | —         | —           | —           | —          | —          | —          | —       | —    | —     | —          | —       | —     | —        | —      | 0000         |

|                             |                       | 15:0          | —             | _           | —         | —           | —           | _          | —          | —          | —       |      | —     | —          |         | CHEID | X<3:0>   |        | 00xx         |

| 4020                        | CHETAG <sup>(1)</sup> | 31:16         | LTAGBOOT      | —           | —         | —           | —           | —          | —          | —          |         |      |       | LTAG<      | :23:16> |       |          |        | xxx0         |

| 1020                        |                       |               |               |             |           |             |             | LTAG<      | 15:4>      |            |         |      |       |            | LVALID  | LLOCK | LTYPE    | —      | xxx2         |

| 4030                        | CHEMSK <sup>(1)</sup> | 31:16         | —             | —           | —         | —           | —           | —          | —          | —          | —       | —    | —     | _          | —       | —     | —        | —      | 0000         |

|                             |                       | 15:0          |               |             |           |             | LN          | 1ASK<15:5  | >          |            |         |      |       | —          | —       | _     | —        | —      | xxxx         |

| 4040                        | CHEW0                 | 31:16         |               | CHEW0<31:0> |           |             |             |            |            |            |         |      |       |            |         |       |          | XXXX   |              |

|                             |                       | 15:0          |               | X           |           |             |             |            |            |            |         |      |       |            |         |       |          | XXXX   |              |

| 4050                        | CHEW1                 | 31:16         |               | CHEW1<31:0> |           |             |             |            |            |            |         |      |       |            |         |       |          | xxxx   |              |

|                             |                       | 15:0          |               |             |           |             |             |            |            |            |         |      |       |            |         |       |          |        | xxxx         |

| 4060                        | CHEW2                 | 31:16         |               |             |           |             |             |            |            | CHEW2      | <31:0>  |      |       |            |         |       |          |        | xxxx         |

|                             |                       | 15:0          |               |             |           |             |             |            |            |            |         |      |       |            |         |       |          |        | XXXX         |

| 4070                        | CHEW3                 | 31:16         |               |             |           |             |             |            |            | CHEW3      | <31:0>  |      |       |            |         |       |          |        | XXXX         |

|                             |                       | 15:0          |               |             | _         | _           | _           | _          |            |            |         |      | CH    | IELRU<24:1 | 16>     |       |          |        | XXXX         |

| 4080                        | CHELRU                | 31:16<br>15:0 |               |             |           |             |             |            | _          | CHELRU     | <15.0>  |      | CI    |            | 10-     |       |          |        | 0000         |

|                             |                       |               |               |             |           |             |             |            |            | CHELRU     | <15.0>  |      |       |            |         |       |          |        | 0000         |

| 4090                        | CHEHIT                | 31:16<br>15:0 |               |             |           |             |             |            |            | CHEHIT     | <31:0>  |      |       |            |         |       |          |        | xxxx         |

|                             |                       |               |               |             |           |             |             |            |            |            |         |      |       |            |         |       |          |        | XXXX         |

| 40A0                        | CHEMIS                | 31:16<br>15:0 |               |             |           |             |             |            |            | CHEMIS     | <31:0>  |      |       |            |         |       |          |        | xxxx         |

|                             |                       | 31:16         |               |             |           |             |             |            |            |            |         |      |       |            |         |       |          |        | xxxx         |

| 40C0                        | CHEDEADT              | 15:0          |               |             |           |             |             |            |            | CHEPFAB    | T<31:0> |      |       |            |         |       |          |        | xxxx<br>xxxx |

| Legen                       |                       |               | n value on Re | sot = u     | nimplomon | tod road as | : '0' Reset | values are | shown in h | avadocimal |         |      |       |            |         |       |          |        | XXXX         |

Legend:

x = unknown value on Reset, — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# PIC32MX330/350/370/430/450/470

|              |                   |                   |                   |                   | =                 |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 31:24        | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | CHEWEN            | —                 |                   |                   | —                 |                   |                  | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | —                 |                   | -                 | —                 |                   | -                | —                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 10.0         | —                 | —                 | _                 | -                 | —                 | —                 | -                | —                |

| 7:0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   |                   | _                 |                   |                   | CHEID             | X<3:0>           |                  |

### REGISTER 9-2: CHEACC: CACHE ACCESS REGISTER

### Legend:

| 0                 |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31 **CHEWEN:** Cache Access Enable bits for registers CHETAG, CHEMSK, CHEW0, CHEW1, CHEW2, and CHEW3

1 = The cache line selected by CHEIDX<3:0> is writeable

0 = The cache line selected by CHEIDX<3:0> is not writeable

bit 30-4 **Unimplemented:** Write '0'; ignore read

bit 3-0 CHEIDX<3:0>: Cache Line Index bits

The value selects the cache line for reading or writing.

### TABLE 10-3: DMA CHANNEL 0 THROUGH CHANNEL 3 REGISTER MAP

| ess                         |                                 | 0             |        |                 |       |       |        |       |      | Bi         | its     |        |        |        |         |        |        |        |            |

|-----------------------------|---------------------------------|---------------|--------|-----------------|-------|-------|--------|-------|------|------------|---------|--------|--------|--------|---------|--------|--------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15  | 30/14           | 29/13 | 28/12 | 27/11  | 26/10 | 25/9 | 24/8       | 23/7    | 22/6   | 21/5   | 20/4   | 19/3    | 18/2   | 17/1   | 16/0   | All Resets |

|                             | DCH0CON                         | 31:16         | —      | _               |       | _     |        | _     | _    | _          | _       | _      | _      | _      | _       | _      | _      |        | 0000       |

| 3060                        | DCHUCON                         | 15:0          | CHBUSY | —               | _     | —     | _      | —     | —    | CHCHNS     | CHEN    | CHAED  | CHCHN  | CHAEN  | _       | CHEDET | CHPR   | l<1:0> | 0000       |

| 3070                        | DCH0ECON                        | 31:16         | —      | —               | —     | —     | _      | —     | _    | —          |         | 1      | r      |        | Q<7:0>  | •      |        |        | 00FF       |

| 0070                        | DOINCEOUN                       | 15:0          |        |                 |       | CHSIR | Q<7:0> |       |      |            | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      | —      | —      | FFF8       |

| 3080                        | DCH0INT                         | 31:16         | —      | —               | —     | —     | -      | —     | —    | —          | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 0000                        | Borioitti                       | 15:0          | —      | —               | —     | —     | —      | —     | —    | —          | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3090                        | DCH0SSA                         | 31:16<br>15:0 |        |                 |       |       |        |       |      | CHSSA      | <31:0>  |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         |        |                 |       |       |        |       |      |            |         |        |        |        |         |        |        |        | 0000       |

| 30A0                        | DCH0DSA                         | 15:0          |        |                 |       |       |        |       |      | CHDSA      | A<31:0> |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 31:16         | _      | _               | _     |       | _      | _     | _    | _          | _       | _      | _      | _      | _       | _      |        | _      | 0000       |

| 30B0                        | DCH0SSIZ                        | 15:0          |        | CHSSIZ<15:0> 00 |       |       |        |       |      |            |         |        |        |        |         |        |        | 0000   |            |

|                             |                                 | 31:16         |        |                 |       |       |        |       |      |            |         |        |        |        |         | 0000   |        |        |            |

| 30C0                        | DCH0DSIZ                        | 15:0          |        |                 |       |       |        |       |      |            |         |        |        |        |         | 0000   |        |        |            |

| 0000                        |                                 | 31:16         | —      | _               | —     | —     | —      | —     | —    | _          | —       |        | _      | —      | _       | _      | —      | _      | 0000       |

| 30D0                        | DCH0SPTR                        | 15:0          |        |                 |       |       |        |       |      | CHSPT      | R<15:0> |        |        |        |         | •      |        |        | 0000       |

| 2050                        |                                 | 31:16         | _      | _               | _     | —     | _      | _     | _    | _          | _       | _      | _      | _      | _       | —      | _      | _      | 0000       |

| 30E0                        | DCH0DPTR                        | 15:0          |        |                 |       |       |        |       |      | CHDPT      | R<15:0> |        |        |        |         |        |        |        | 0000       |

| 2050                        | DCH0CSIZ                        | 31:16         | —      |                 | _     | _     | _      | _     | _    | _          | _       | _      | _      | _      | _       | —      | _      | _      | 0000       |

| 30FU                        | DCHUCSIZ                        | 15:0          |        |                 |       |       |        |       |      | CHCSIZ     | Z<15:0> |        |        |        |         |        |        |        | 0000       |

| 3100                        | DCH0CPTR                        | 31:16         | —      | _               |       | —     |        | _     | _    | —          | _       | _      | _      | _      | _       | _      | _      |        | 0000       |

| 3100                        | DCHUCFTK                        | 15:0          |        |                 |       |       |        |       |      | CHCPT      | R<15:0> |        | -      |        |         |        |        |        | 0000       |

| 3110                        | DCH0DAT                         | 31:16         | —      | —               |       | —     | _      | —     | —    | —          |         | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 5110                        | DONUDAI                         | 15:0          | —      | —               | _     | —     | _      |       | —    | —          |         |        |        | CHPDA  | AT<7:0> |        |        |        | 0000       |

| 3120                        | DCH1CON                         | 31:16         | —      | —               | _     | —     | —      |       | —    |            | —       | —      | —      | —      | —       | —      | —      | —      | 0000       |

| 0120                        | Bonnoon                         | 15:0          | CHBUSY | —               | —     | —     | _      | —     | —    | CHCHNS     | CHEN    | CHAED  | CHCHN  | CHAEN  |         | CHEDET | CHPR   | l<1:0> | 0000       |

| 3130                        | DCH1ECON                        | 31:16         | —      | —               | —     | —     | —      | —     | —    | —          |         | 1      | -      |        | Q<7:0>  | -      |        |        | OOFF       |

| 0.00                        |                                 | 15:0          |        |                 |       | CHSIR | Q<7:0> |       |      |            | CFORCE  | CABORT | PATEN  | SIRQEN | AIRQEN  | —      |        | —      | FFF8       |

| 3140                        | DCH1INT                         | 31:16         | -      | _               | _     | —     | _      | —     | _    | —          | CHSDIE  | CHSHIE | CHDDIE | CHDHIE | CHBCIE  | CHCCIE | CHTAIE | CHERIE | 0000       |

| 55                          |                                 | 15:0          | —      | _               | —     | —     | —      | —     | —    | -          | CHSDIF  | CHSHIF | CHDDIF | CHDHIF | CHBCIF  | CHCCIF | CHTAIF | CHERIF | 0000       |

| 3150                        | DCH1SSA                         | 31:16         |        |                 |       |       |        |       |      | CHSSA      | <31:0>  |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 15:0          |        |                 |       |       |        |       |      |            |         |        |        |        |         |        |        |        | 0000       |

| 3160                        | DCH1DSA                         | 31:16         |        |                 |       |       |        |       |      | CHDSA      | <31:0>  |        |        |        |         |        |        |        | 0000       |

|                             |                                 | 15:0          |        |                 |       |       |        |       |      | exadecimal |         |        |        |        |         |        |        |        | 0000       |

Legend:

x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

## 11.0 USB ON-THE-GO (OTG)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 27. "USB On-The-Go (OTG)" (DS60001126), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Universal Serial Bus (USB) module contains analog and digital components to provide a USB 2.0 full-speed and low-speed embedded host, full-speed device or OTG implementation with a minimum of external components. This module in Host mode is intended for use as an embedded host and therefore does not implement a UHCI or OHCI controller.

The USB module consists of the clock generator, the USB voltage comparators, the transceiver, the Serial Interface Engine (SIE), a dedicated USB DMA controller, pull-up and pull-down resistors, and the register interface. A block diagram of the PIC32 USB OTG module is presented in Figure 11-1.

The clock generator provides the 48 MHz clock required for USB full-speed and low-speed communication. The voltage comparators monitor the voltage on the VBUS pin to determine the state of the bus. The transceiver provides the analog translation between the USB bus and the digital logic. The SIE is a state machine that transfers data to and from the endpoint buffers and generates the hardware protocol for data transfers. The USB DMA controller transfers data between the data buffers in RAM and the SIE. The integrated pull-up and pull-down resistors eliminate the need for external signaling components. The register interface allows the CPU to configure and communicate with the module. The PIC32 USB module includes the following features:

- USB full-speed support for host and device

- Low-speed host support

- USB OTG support

- Integrated signaling resistors

- Integrated analog comparators for VBUS monitoring

- Integrated USB transceiver

- · Transaction handshaking performed by hardware

- · Endpoint buffering anywhere in system RAM

- · Integrated DMA to access system RAM and Flash

- The implementation and use of the USB Note: specifications, and other third party specifications or technologies, may require licensing; including, but not limited to, USB Implementers Forum, Inc. (also referred to as USB-IF). The user is fully responsible for investigating and satisfying any applicable licensing obligations.

### TABLE 11-1: USB REGISTER MAP (CONTINUED)

| ess                         |                                 |           |       |       |       |       |       | ,     |      |      | Bit  | s    |      |          |        |        |         |        | 6          |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|--------|--------|---------|--------|------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3   | 18/2   | 17/1    | 16/0   | All Resets |

| 5390                        | U1EP9                           | 31:16     | —     | —     |       | —     | _     | _     | —    | —    |      |      | —    | —        | —      | —      | —       | _      | 0000       |

| 5390                        | UIEF9                           | 15:0      | —     | _     |       | _     | -     | -     | —    | _    | —    |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53A0                        | U1EP10                          | 31:16     | —     | _     |       | _     |       |       | _    |      |      |      | _    | —        | _      | _      | —       |        | 0000       |

| 53A0                        | UIEFIU                          | 15:0      | _     | _     |       | _     | -     | -     | _    | _    | _    |      | —    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53B0                        | U1EP11                          | 31:16     | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | —        | _      | _      | _       | _      | 0000       |

| 5560                        | UIEFII                          | 15:0      | _     | _     | —     | _     | _     | _     | _    | _    | _    | _    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53C0                        | U1EP12                          | 31:16     | _     | _     | —     | _     | —     | —     | -    | -    | —    | —    | _    | —        | _      | _      | —       | _      | 0000       |

| 5300                        | UIEFIZ                          | 15:0      | _     | _     | —     | _     | —     | —     | -    | -    | —    | —    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 53D0                        | U1EP13                          | 31:16     | _     |       | _     | _     | —     | —     |      | _    | _    | _    |      | —        | —      | _      | —       | _      | 0000       |

| 55D0                        | UIEF 13                         | 15:0      | _     | _     | —     | _     | —     | —     | -    | -    | —    | —    | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     |       | _     | _     | _     | _     | _    | -    | _    | _    | _    | _        | _      | _      | _       | _      | 0000       |

| 53E0                        | U1EP14                          | 15:0      | _     |       | _     | _     | _     | _     |      | _    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

| 5050                        |                                 | 31:16     | _     |       | _     | _     | _     | _     |      | _    |      |      | _    | _        | _      | _      | _       | _      | 0000       |

| 53F0                        | U1EP15                          | 15:0      | _     |       | _     | _     | _     | _     |      | _    |      |      | _    | EPCONDIS | EPRXEN | EPTXEN | EPSTALL | EPHSHK | 0000       |

Legend: x = unknown value on Reset; --- = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: With the exception of those noted, all registers in this table (except as noted) have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

2: This register does not have associated SET and INV registers.

3: This register does not have associated CLR, SET and INV registers.

4: Reset value for this bit is undefined.

## 12.4 Control Registers

|                             |                                 | FI        | C32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY |               |       |       |       |               |              |      |              |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-----------------------------------------------------------------------------------|---------------|-------|-------|-------|---------------|--------------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess (                       |                                 | Ð         |                                                                                   |               |       |       |       |               |              | Bi   | ts           |              |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15                                                                             | 30/14         | 29/13 | 28/12 | 27/11 | 26/10         | 25/9         | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6000                        | ANSELA                          | 31:16     | —                                                                                 | —             | _     | —     | _     | —             | —            | _    | —            | —            | —            | _            | —            | —            | —            | _            | 0000          |

| 0000                        | ANOLLA                          | 15:0      | —                                                                                 | —             | _     | —     | _     | ANSELA10      | ANSELA9      | _    | _            |              | _            | _            |              |              | —            | _            | 0060          |

| 6010                        | TRISA                           | 31:16     | —                                                                                 | —             | -     | —     | _     | —             | —            |      | _            | —            | _            |              | —            | —            | _            |              | 0000          |

|                             |                                 | 15:0      | TRISA15                                                                           | TRISA14       | _     | —     | _     | TRISA10       | TRISA9       | —    | TRISA7       | TRISA6       | TRISA5       | TRISA4       | TRISA3       | TRISA2       | TRISA1       | TRISA0       | xxxx          |

| 6020                        | PORTA                           | 31:16     | —                                                                                 | —             | _     | —     |       | —             | _            |      | _            |              | _            | —            |              |              | —            | —            | 0000          |

|                             | -                               | 15:0      | RA15                                                                              | RA14          | _     | —     | _     | RA10          | RA9          | _    | RA7          | RA6          | RA5          | RA4          | RA3          | RA2          | RA1          | RA0          | xxxx          |

| 6030                        | LATA                            | 31:16     | —                                                                                 | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | LATA15                                                                            | LATA14        | —     | —     | —     | LATA10        | LATA9        | —    | LATA7        | LATA6        | LATA5        | LATA4        | LATA3        | LATA2        | LATA1        | LATA0        | xxxx          |

| 6040                        | ODCA                            | 31:16     | —                                                                                 | —             | —     | —     | —     | —             | —            | —    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | ODCA15                                                                            | ODCA14        | —     | —     | —     | ODCA10        | ODCA9        | —    | ODCA7        | ODCA6        | ODCA5        | ODCA4        | ODCA3        | ODCA2        | ODCA1        | ODCA0        | xxxx          |

| 6050                        | CNPUA                           | 31:16     |                                                                                   |               | _     | —     | _     | _             |              |      | —            |              | _            | _            |              |              |              | _            | 0000          |

|                             |                                 |           | CNPUA15                                                                           | CNPUA14       | _     | —     | _     | CNPUA10       | CNPUA9       | _    | CNPUA7       | CNPUA6       | CNPUA5       | CNPUA4       | CNPUA3       | CNPUA2       | CNPUA1       | CNPUA0       | _             |

| 6060                        | CNPDA                           | 31:16     | —                                                                                 | —             | _     | —     | _     | —             | —            | _    | —            | —            | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                 |           | CNPDA15                                                                           | CNPDA14       | —     |       | _     | CNPDA10       | CNPDA9       | _    | CNPDA7       | CNPDA6       | CNPDA5       | CNPDA4       | CNPDA3       | CNPDA2       | CNPDA1       | CNPDA0       |               |

| 6070                        | CNCONA                          | 31:16     |                                                                                   |               |       | —     | _     | _             |              |      | _            |              |              |              |              |              |              |              | 0000          |

|                             |                                 | 15:0      | ON                                                                                |               | SIDL  | —     | _     | _             |              |      | _            |              |              |              |              |              |              |              | 0000          |

| 6080                        | CNENA                           | 31:16     | -                                                                                 | -             | _     | —     | _     | -             | -            | _    | -            | -            | -            | —            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | CNIEA15                                                                           |               | _     | —     | _     | CNIEA10       | CNIEA9       | —    | CNIEA7       | CNIEA6       | CNIEA5       | CNIEA4       | CNIEA3       | CNIEA2       | CNIEA1       | CNIEA0       | XXXX          |

| 6000                        | CNSTATA                         | 31:16     | -                                                                                 | -             | _     | —     | _     | -             | -            | —    | -            | -            | -            | —            | -            | -            | -            | -            | 0000          |

| 0090                        | CINGTATA                        | 15:0      | CN<br>STATA15                                                                     | CN<br>STATA14 | _     | —     | _     | CN<br>STATA10 | CN<br>STATA9 | —    | CN<br>STATA7 | CN<br>STATA6 | CN<br>STATA5 | CN<br>STATA4 | CN<br>STATA3 | CN<br>STATA2 | CN<br>STATA1 | CN<br>STATA0 | xxxx          |

## TABLE 12-3:PORTA REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,<br/>PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# TABLE 12-12: PORTF REGISTER MAP FOR PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY

|                             |                                 | U         |       |       |               |               |       |       |      |              |      |      |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|---------------|---------------|-------|-------|------|--------------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                         |                                 | â         |       |       |               |               |       |       |      | Bit          | s    |      |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13         | 28/12         | 27/11 | 26/10 | 25/9 | 24/8         | 23/7 | 22/6 | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6510                        | TRISF                           | 31:16     | _     |       | —             | —             | _     | —     | _    | —            | _    | -    | —            | _            | —            | -            | —            | _            | 0000          |

| 0010                        | -                               | 15:0      | —     | —     | TRISF13       | TRISF12       | —     | —     | _    | TRISF8       | —    | —    | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | xxxx          |

| 6520                        | PORTF                           | 31:16     | _     | _     | —             |               | _     | _     |      | —            | _    |      | —            | _            | _            | _            | —            |              | 0000          |

|                             |                                 | 15:0      | —     | _     | RF13          | RF12          | —     | —     |      | RF8          | —    | _    | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | XXXX          |

| 6530                        | LATF                            | 31:16     | —     | _     | —             | _             | —     | —     |      | —            | —    | _    | —            | —            | —            | _            | —            |              | 0000          |

|                             |                                 | 15:0      | —     | _     | LATF13        | LATF12        | —     | —     |      | LATF8        | —    | _    | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | XXXX          |

| 6540                        | ODCF                            | 31:16     | —     | _     | —             | _             | —     | —     |      | —            | —    | _    | —            | —            | —            | _            | —            |              | 0000          |

|                             |                                 | 15:0      | —     | _     | ODCF13        | ODCF12        | —     | —     |      | ODCF8        | —    | _    | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | xxxx          |

| 6550                        | CNPUF                           | 31:16     | _     |       | —             |               | _     | _     |      | —            | _    |      | —            | _            |              | _            | —            |              | 0000          |

|                             |                                 | 15:0      | —     | _     | CNPUF13       | CNPUF12       | —     | _     | _    | CNPUF8       | _    |      | CNPUF5       | CNPUF4       | CNPDF3       | CNPUF2       | CNPUF1       | CNPUF0       | XXXX          |

| 6560                        | CNPDF                           | 31:16     | —     | _     | -             |               | —     | _     | _    | —            | _    |      | —            | —            | —            | —            | —            | —            | 0000          |

|                             | _                               | 15:0      | —     | _     | CNPDF13       | CNPDF12       | —     | _     | _    | CNPDF8       | _    |      | CNPDF5       | CNPFF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | XXXX          |

| 6570                        | CNCONF                          | 31:16     | _     | _     | -             |               | —     | _     | _    | —            | _    |      | —            | _            | —            | _            | _            | _            | 0000          |

|                             |                                 | 15:0      | ON    | _     | SIDL          | —             | _     | —     | _    | _            | _    | —    | —            | _            | —            | _            | _            | _            | 0000          |

| 6580                        | CNENF                           | 31:16     | —     | _     | -             |               | —     | _     | _    | —            | _    |      | —            | —            | —            | —            | —            | —            | 0000          |

|                             | _                               | 15:0      | —     | _     | CNIEF13       | CNIEF12       | —     | _     | _    | CNIEF8       | _    |      | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | XXXX          |

| 0500                        |                                 | 31:16     | —     |       | —             | —             | —     | —     | —    | —            | —    |      | —            |              | —            |              | _            |              | 0000          |

| 6590                        | CNSTATF                         | 15:0      | —     | —     | CN<br>STATF13 | CN<br>STATF12 | —     | —     | —    | CN<br>STATF8 | _    | —    | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | xxxx          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. Legend:

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

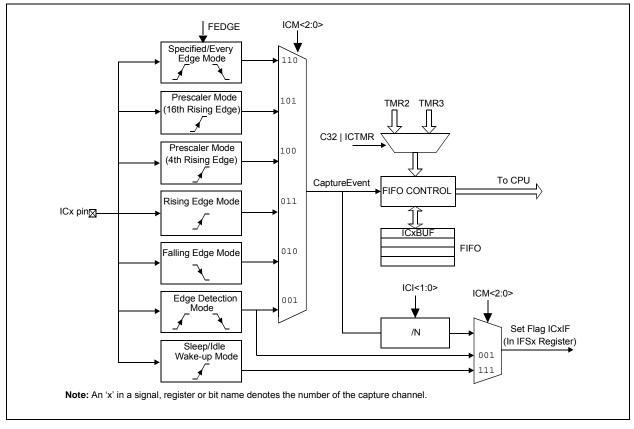

## 16.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

## FIGURE 16-1: INPUT CAPTURE BLOCK DIAGRAM

| REGIST    | ER 18-1:                                                                                                                                                     | SPIxCON: S                                                                                                                                                  | SPI CONTROL REGISTER (CONTINUED)                                                      |  |  |  |  |  |  |  |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| bit 17    |                                                                                                                                                              |                                                                                                                                                             | e Edge Select bit (Framed SPI mode only)                                              |  |  |  |  |  |  |  |

|           | <ul> <li>1 = Frame synchronization pulse coincides with the first bit clock</li> <li>0 = Frame synchronization pulse precedes the first bit clock</li> </ul> |                                                                                                                                                             |                                                                                       |  |  |  |  |  |  |  |

| h:+ 40    | <ul> <li>0 = Frame synchronization pulse precedes the first bit clock</li> <li>ENHBUF: Enhanced Buffer Enable bit<sup>(2)</sup></li> </ul>                   |                                                                                                                                                             |                                                                                       |  |  |  |  |  |  |  |

| bit 16    | ENHBUF: Enhanced Buffer Enable bit <sup>(2)</sup><br>1 = Enhanced Buffer mode is enabled                                                                     |                                                                                                                                                             |                                                                                       |  |  |  |  |  |  |  |

|           | 0 = Enhanced Buffer mode is disabled                                                                                                                         |                                                                                                                                                             |                                                                                       |  |  |  |  |  |  |  |

| bit 15    |                                                                                                                                                              | ripheral On bi                                                                                                                                              |                                                                                       |  |  |  |  |  |  |  |

|           |                                                                                                                                                              | ripheral is ena                                                                                                                                             |                                                                                       |  |  |  |  |  |  |  |

|           |                                                                                                                                                              | ripheral is dis                                                                                                                                             |                                                                                       |  |  |  |  |  |  |  |

| bit 14    | Unimpleme                                                                                                                                                    | ented: Read a                                                                                                                                               | as '0'                                                                                |  |  |  |  |  |  |  |

| bit 13    | SIDL: Stop                                                                                                                                                   | in Idle Mode b                                                                                                                                              | pit                                                                                   |  |  |  |  |  |  |  |

|           | 1 = Discontinue operation when CPU enters in Idle mode                                                                                                       |                                                                                                                                                             |                                                                                       |  |  |  |  |  |  |  |

|           | 0 = Continu                                                                                                                                                  |                                                                                                                                                             |                                                                                       |  |  |  |  |  |  |  |

| bit 12    |                                                                                                                                                              | isable SDOx                                                                                                                                                 |                                                                                       |  |  |  |  |  |  |  |

|           |                                                                                                                                                              | <ul> <li>1 = SDOx pin is not used by the module. Pin is controlled by associated PORT register</li> <li>0 = SDOx pin is controlled by the module</li> </ul> |                                                                                       |  |  |  |  |  |  |  |

| bit 11-10 |                                                                                                                                                              |                                                                                                                                                             | t Communication Select bits                                                           |  |  |  |  |  |  |  |

|           | When AUD                                                                                                                                                     |                                                                                                                                                             | Communication Select bits                                                             |  |  |  |  |  |  |  |

|           | MODE32                                                                                                                                                       | MODE16                                                                                                                                                      | Communication                                                                         |  |  |  |  |  |  |  |

|           | 1                                                                                                                                                            | 1                                                                                                                                                           | 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                 |  |  |  |  |  |  |  |

|           | 1                                                                                                                                                            | 0                                                                                                                                                           | 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                 |  |  |  |  |  |  |  |

|           | 0                                                                                                                                                            | 1                                                                                                                                                           | 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame                                 |  |  |  |  |  |  |  |

|           | 0                                                                                                                                                            | 0                                                                                                                                                           | 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                 |  |  |  |  |  |  |  |