Welcome to E-XFL.COM

Microchip Technology - PIC32MX470F512H-120/PT Datasheet

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Details                    |                                                                                  |

|----------------------------|----------------------------------------------------------------------------------|

| Product Status             | Active                                                                           |

| Core Processor             | MIPS32® M4K™                                                                     |

| Core Size                  | 32-Bit Single-Core                                                               |

| Speed                      | 120MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                    |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                       |

| Number of I/O              | 49                                                                               |

| Program Memory Size        | 512KB (512K x 8)                                                                 |

| Program Memory Type        | FLASH                                                                            |

| EEPROM Size                |                                                                                  |

| RAM Size                   | 128K x 8                                                                         |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                      |

| Data Converters            | A/D 28x10b                                                                       |

| Oscillator Type            | Internal                                                                         |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                  |

| Mounting Type              | Surface Mount                                                                    |

| Package / Case             | 64-TQFP                                                                          |

| Supplier Device Package    | 64-TQFP (10x10)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx470f512h-120-pt |

|                            |                                                                                  |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC32MX330/350/370/430/450/470

|                                          |            |              |                                    |                  | Rei             | nappab                                | ole Pe | ripher               | als                                | s)                           |                    |                     |      |     |     |      |                                          |          |      |       |

|------------------------------------------|------------|--------------|------------------------------------|------------------|-----------------|---------------------------------------|--------|----------------------|------------------------------------|------------------------------|--------------------|---------------------|------|-----|-----|------|------------------------------------------|----------|------|-------|

| Device                                   | Pins       | Packages     | Program Memory (KB) <sup>(1)</sup> | Data Memory (KB) | Remappable Pins | Timers/Capture/Compare <sup>(2)</sup> | UART   | SPI/I <sup>2</sup> S | External Interrupts <sup>(3)</sup> | 10-bit 1 Msps ADC (Channels) | Analog Comparators | USB On-The-Go (OTG) | CTMU | 1²C | РМР | RTCC | DMA Channels<br>(Programmable/Dedicated) | I/O Pins | JTAG | Trace |

| PIC32MX330F064H                          | 64         | QFN,<br>TQFP | 64+12                              | 16               | 37              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | Ν                   | Y    | 2   | Y   | Y    | 4/0                                      | 53       | Y    | N     |

| PIC32MX330F064L                          | 100<br>124 | TQFP<br>VTLA | 64+12                              | 16               | 54              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 85       | Y    | Y     |

| PIC32MX350F128H                          | 64         | QFN,<br>TQFP | 128+12                             | 32               | 37              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 53       | Y    | N     |

| PIC32MX350F128L                          | 100<br>124 | TQFP<br>VTLA | 128+12                             | 32               | 54              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 85       | Y    | Y     |

| PIC32MX350F256H                          | 64         | QFN,<br>TQFP | 256+12                             | 64               | 37              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 53       | Y    | N     |

| PIC32MX350F256L                          | 100<br>124 | TQFP         | 256+12                             | 64               | 54              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 85       | Y    | Y     |

| PIC32MX370F512H                          | 64         | QFN,<br>TQFP | 512+12                             | 128              | 37              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 53       | Y    | N     |

| PIC32MX370F512L                          | 100<br>124 | TQFP<br>VTLA | 512+12                             | 128              | 54              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | N                   | Y    | 2   | Y   | Y    | 4/0                                      | 85       | Y    | Y     |

| PIC32MX430F064H                          | 64         | QFN,<br>TQFP | 64+12                              | 16               | 34              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 49       | Y    | N     |

| PIC32MX430F064L                          | 100<br>124 | TQFP<br>VTLA | 64+12                              | 16               | 51              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 81       | Y    | Y     |

| PIC32MX450F128H                          | 64         | QFN,<br>TQFP | 128+12                             | 32               | 34              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 49       | Y    | N     |

| PIC32MX450F128HB (see Note 4)            | 64         | QFN,<br>TQFP | 128+12                             | 32               | 34              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 49       | Y    | N     |

| PIC32MX450F128L                          | 100<br>124 | TQFP<br>VTLA | 128+12                             | 32               | 51              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 81       | Y    | Y     |

| PIC32MX450F256H                          | 64         | QFN,<br>TQFP | 256+12                             | 64               | 34              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 49       | Y    | N     |

| PIC32MX450F256L                          | 100<br>124 | TQFP<br>VTLA | 256+12                             | 64               | 51              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 81       | Y    | Y     |

| PIC32MX470F512H                          | 64         | QFN,<br>TQFP | 512+12                             | 128              | 34              | 5/5/5                                 | 4      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 49       | Y    | N     |

| PIC32MX470F512L                          | 100<br>124 | TQFP<br>VTLA | 512+12                             | 128              | 51              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 81       | Y    | Y     |

| PIC32MX470F512LB<br>(see <b>Note 4</b> ) | 100<br>124 | TQFP<br>VTLA | 512+12                             | 128              | 51              | 5/5/5                                 | 5      | 2/2                  | 5                                  | 28                           | 2                  | Y                   | Y    | 2   | Y   | Y    | 4/2                                      | 81       | Y    | Y     |

### TABLE 1:PIC32MX330/350/370/430/450/470 CONTROLLER FAMILY FEATURES

Note 1: All devices feature 12 KB of Boot Flash memory.

2: Four out of five timers are remappable.

3: Four out of five external interrupts are remappable.

4: This PIC32 device is targeted to specific audio software packages that are tracked for licensing royalty purposes. All peripherals and electrical characteristics are identical to their corresponding base part numbers

# TABLE 7: PIN NAMES FOR 124-PIN DEVICES (CONTINUED)

| 124               | -PIN VTLA (BOTTOM VIEW) <sup>(1,2,3,4)</sup>                             | 17       |                   |                | A34           |                       |

|-------------------|--------------------------------------------------------------------------|----------|-------------------|----------------|---------------|-----------------------|

|                   | A                                                                        | 17       |                   | B13 B29        |               | nductive<br>ermal Pad |

|                   | PIC32MX430F064L<br>PIC32MX450F128L<br>PIC32MX450F256L<br>PIC32MX470F512L |          |                   | B1<br>B56      | B41           | A51                   |

|                   |                                                                          | y Indica | A1<br>tor         | A68            |               |                       |

| Package<br>Bump # | Full Pin Name                                                            |          | Package<br>Bump # |                | Full Pin Name |                       |

| B7                | MCLR                                                                     |          | B32               | SDA2/RA3       |               |                       |

| B8                | Vss                                                                      |          | B33               | TDO/RA5        |               |                       |

| B9                | TMS/CTED1/RA0                                                            |          | B34               | OSC1/CLKI/RC12 | 2             |                       |

| B10               | RPE9/RE9                                                                 |          | B35               | No Connect     |               |                       |

| B11               | AN4/C1INB/RB4                                                            |          | B36               | SCL1/RPA14/RA  | 14            |                       |

| B12               | Vss                                                                      |          | B37               | RPD8/RTCC/RD8  | 8             |                       |

| B13               | PGEC3/AN2/C2INB/RPB2/CTED13/RB2                                          |          | B38               | RPD10/SCK1/PM  | CS2/RD10      |                       |

| B14               | PGED1/AN0/RPB0/RB0                                                       |          | B39               | RPD0/INT0/RD0  |               |                       |

| B15               | No Connect                                                               |          | B40               | SOSCO/RPC14/T  | 1CK/RC14      |                       |

| B16               | PGED2/AN7/RPB7/CTED3/RB7                                                 |          | B41               | Vss            |               |                       |

| B17               | VREF+/CVREF+/PMA6/RA10                                                   |          | B42               | AN25/RPD2/RD2  |               |                       |

| B18               | AVss                                                                     |          | B43               | RPD12/PMD12/R  | D12           |                       |

| B19               | AN9/RPB9/CTED4/RB9                                                       |          | B44               | RPD4/PMWR/RD   | 4             |                       |

| B20               | AN11/PMA12/RB11                                                          |          | B45               | PMD14/RD6      |               |                       |

| B21               | Vdd                                                                      |          | B46               | No Connect     |               |                       |

| B22               | RPF13/RF13                                                               |          | B47               | No Connect     |               |                       |

| B23               | AN12/PMA11/RB12                                                          |          | B48               | VCAP           |               |                       |

| B24               | AN14/RPB14/CTED5/PMA1/RB14                                               |          | B49               | RPF0/PMD11/RF  | 0             |                       |

| B25               | Vss                                                                      |          | B50               | RPG1/PMD9/RG   | 1             |                       |

| B26               | RPD14/RD14                                                               |          | B51               | TRCLK/RA6      |               |                       |

| B27               | RPF4/PMA9/RF4                                                            |          | B52               | PMD0/RE0       |               |                       |

| B28               | No Connect                                                               |          | B53               | VDD            |               |                       |

| B29               | RPF8/RF8                                                                 |          | B54               | TRD2/RG14      |               |                       |

| B30               | VUSB3V3                                                                  |          | B55               | TRD0/RG13      |               |                       |

| B31               | D+                                                                       |          | B56               | RPE3/CTPLS/PM  | D3/RE3        |                       |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: Shaded package bumps are 5V tolerant.

4: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

# **Referenced Sources**

This device data sheet is based on the following individual sections of the *"PIC32 Family Reference Manual"*. These documents should be considered as the general reference for the operation of a particular module or device feature.

| Note: | To access the following documents, refer |

|-------|------------------------------------------|

|       | to the Documentation > Reference         |

|       | Manuals section of the Microchip PIC32   |

|       | website: http://www.microchip.com/pic32. |

- Section 1. "Introduction" (DS60001127)

- Section 2. "CPU" (DS60001113)

- Section 3. "Memory Organization" (DS60001115)

- Section 4. "Prefetch Cache" (DS60001119)

- Section 5. "Flash Program Memory" (DS60001121)

- Section 6. "Oscillator Configuration" (DS60001112)

- Section 7. "Resets" (DS60001118)

- Section 8. "Interrupt Controller" (DS60001108)

- Section 9. "Watchdog Timer and Power-up Timer" (DS60001114)

- Section 10. "Power-Saving Features" (DS60001130)

- Section 12. "I/O Ports" (DS60001120)

- Section 13. "Parallel Master Port (PMP)" (DS60001128)

- Section 14. "Timers" (DS60001105)

- Section 15. "Input Capture" (DS60001122)

- Section 16. "Output Compare" (DS60001111)

- Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104)

- Section 19. "Comparator" (DS60001110)

- Section 20. "Comparator Voltage Reference (CVREF)" (DS60001109)

- Section 21. "Universal Asynchronous Receiver Transmitter (UART)" (DS60001107)

- Section 23. "Serial Peripheral Interface (SPI)" (DS60001106)

- Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116)

- Section 27. "USB On-The-Go (OTG)" (DS60001126)

- Section 29. "Real-Time Clock and Calendar (RTCC)" (DS60001125)

- Section 31. "Direct Memory Access (DMA) Controller" (DS60001117)

- Section 32. "Configuration" (DS60001124)

- Section 33. "Programming and Diagnostics" (DS60001129)

- Section 37. "Charge Time Measurement Unit (CTMU)" (DS60001167)

|          |                        | Pin Numb        | er                                 |             |                |                                                                                                  |  |  |  |  |  |

|----------|------------------------|-----------------|------------------------------------|-------------|----------------|--------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA                    | Pin<br>Type | Buffer<br>Type | Description                                                                                      |  |  |  |  |  |

| CVREF-   | 15                     | 28              | A21                                | I           | Analog         | Comparator Voltage Reference (Low)                                                               |  |  |  |  |  |

| CVREF+   | 16                     | 29              | B17                                | Ι           | Analog         | Comparator Voltage Reference (High)                                                              |  |  |  |  |  |

| CVREFOUT | 23                     | 34              | A24                                | Ι           | Analog         | Comparator Voltage Reference (Output)                                                            |  |  |  |  |  |

| C1INA    | 11                     | 20              | A12                                | I           | Analog         |                                                                                                  |  |  |  |  |  |

| C1INB    | 12                     | 21              | B11                                | I           | Analog         | Comparator 1 Inputa                                                                              |  |  |  |  |  |

| C1INC    | 5                      | 11              | B6                                 | I           | Analog         | Comparator 1 Inputs                                                                              |  |  |  |  |  |

| C1IND    | 4                      | 10              | A7                                 | I           | Analog         |                                                                                                  |  |  |  |  |  |

| C2INA    | 13                     | 22              | A13                                | Ι           | Analog         |                                                                                                  |  |  |  |  |  |

| C2INB    | 14                     | 23              | B13                                | Ι           | Analog         |                                                                                                  |  |  |  |  |  |

| C2INC    | 8                      | 14              | A9                                 | Ι           | Analog         | Comparator 2 Inputs                                                                              |  |  |  |  |  |

| C2IND    | 6                      | 12              | A8                                 | I           | Analog         |                                                                                                  |  |  |  |  |  |

| C1OUT    | PPS                    | PPS             | PPS                                | 0           |                | Comparator 1 Output                                                                              |  |  |  |  |  |

| C2OUT    | PPS                    | PPS             | PPS                                | 0           |                | Comparator 2 Output                                                                              |  |  |  |  |  |

| PMALL    | 30                     | 44              | A29                                | 0           | TTL/ST         | Parallel Master Port Address Latch Enable Low Byte                                               |  |  |  |  |  |

| PMALH    | 29                     | 43              | B24                                | 0           | TTL/ST         | Parallel Master Port Address Latch Enable High Byte                                              |  |  |  |  |  |

| PMA0     | 30                     | 44              | A29                                | 0           | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes)        |  |  |  |  |  |

| PMA1     | 29                     | 43              | B24                                | 0           | TTL/ST         | Parallel Master Port Address bit 0 Input (Buffered Slave modes) and Output (Master modes)        |  |  |  |  |  |

| PMA2     | 8                      | 14              | A9                                 | 0           | TTL/ST         |                                                                                                  |  |  |  |  |  |

| PMA3     | 6                      | 12              | A8                                 | 0           | TTL/ST         |                                                                                                  |  |  |  |  |  |

| PMA4     | 5                      | 11              | B6                                 | 0           | TTL/ST         |                                                                                                  |  |  |  |  |  |

| PMA5     | 4                      | 10              | A7                                 | 0           | TTL/ST         |                                                                                                  |  |  |  |  |  |

| PMA6     | 16                     | 29              | B17                                | 0           | TTL/ST         |                                                                                                  |  |  |  |  |  |

| PMA7     | 22                     | 28              | A21                                | 0           | TTL/ST         |                                                                                                  |  |  |  |  |  |

| PMA8     | 32                     | 50              | A32                                | 0           | TTL/ST         |                                                                                                  |  |  |  |  |  |

| PMA9     | 31                     | 49              | B27                                | 0           | TTL/ST         |                                                                                                  |  |  |  |  |  |

| PMA10    | 28                     | 42              | A28                                | 0           | TTL/ST         | Devellet Meeter Dert date (Develtingered Meeter                                                  |  |  |  |  |  |

| PMA11    | 27                     | 41              | B23                                | 0           | TTL/ST         | Parallel Master Port data (Demultiplexed Master mode) or Address/Data (Multiplexed Master modes) |  |  |  |  |  |

| PMA12    | 24                     | 35              | B20                                | 0           | TTL/ST         |                                                                                                  |  |  |  |  |  |

| PMA13    | 23                     | 34              | A24                                | 0           | TTL/ST         | ]                                                                                                |  |  |  |  |  |

| PMA14    | 45                     | 71              | A46                                | 0           | TTL/ST         | ]                                                                                                |  |  |  |  |  |

| PMA15    | 44                     | 70              | B38                                | 0           | TTL/ST         | ]                                                                                                |  |  |  |  |  |

| PMCS1    | 45                     | 71              | A46                                | 0           | TTL/ST         | ST<br>ST<br>ST                                                                                   |  |  |  |  |  |

| PMCS2    | 44                     | 70              | B38                                | 0           | TTL/ST         |                                                                                                  |  |  |  |  |  |

| PMD0     | 60                     | 93              | B52                                | I/O         | TTL/ST         |                                                                                                  |  |  |  |  |  |

| PMD1     | 61                     | 94              | A64                                | I/O         | TTL/ST         |                                                                                                  |  |  |  |  |  |

| PMD2     | 62                     | 98              | A66                                | I/O         | TTL/ST         | 1                                                                                                |  |  |  |  |  |

|          | ST = Schmi             |                 | tible input or ou<br>out with CMOS |             |                | alog = Analog input P = Power<br>= Output I = Input                                              |  |  |  |  |  |

#### TARI E 1-1. PINOUT I/O DESCRIPTIONS (CONTINUED)

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices.

# 2.0 GUIDELINES FOR GETTING STARTED WITH 32-BIT MCUS

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the documents listed in the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

# 2.1 Basic Connection Requirements

Getting started with the PIC32MX330/350/370/430/ 450/470 family of 32-bit Microcontrollers (MCUs) requires attention to a minimal set of device pin connections before proceeding with development. The following is a list of pin names, which must always be connected:

- All VDD and Vss pins (see 2.2 "Decoupling Capacitors")

- All AVDD and AVss pins, even if the ADC module is not used (see 2.2 "Decoupling Capacitors")

- VCAP pin (see 2.3 "Capacitor on Internal Voltage Regulator (VCAP)")

- MCLR pin (see 2.4 "Master Clear (MCLR) Pin")

- PGECx/PGEDx pins, used for In-Circuit Serial Programming (ICSP<sup>™</sup>) and debugging purposes (see **2.5** "ICSP Pins")

- OSC1 and OSC2 pins, when external oscillator source is used (see 2.8 "External Oscillator Pins")

The following pins may be required:

VREF+/VREF- pins, used when external voltage reference for the ADC module is implemented.

**Note:** The AVDD and AVSS pins must be connected, regardless of ADC use and the ADC voltage reference source.

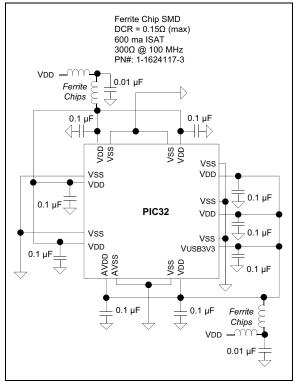

# 2.2 Decoupling Capacitors

The use of decoupling capacitors on power supply pins, such as VDD, VSS, AVDD and AVSS is required. See Figure 2-1.

Consider the following criteria when using decoupling capacitors:

- Value and type of capacitor: A value of 0.1  $\mu$ F (100 nF), 10-20V is recommended. The capacitor should be a low Equivalent Series Resistance (low-ESR) capacitor and have resonance frequency in the range of 20 MHz and higher. It is further recommended that ceramic capacitors be used.

- Placement on the printed circuit board: The decoupling capacitors should be placed as close to the pins as possible. It is recommended that the capacitors be placed on the same side of the board as the device. If space is constricted, the capacitor can be placed on another layer on the PCB using a via; however, ensure that the trace length from the pin to the capacitor is within one-quarter inch (6 mm) in length.

- Handling high frequency noise: If the board is experiencing high frequency noise, upward of tens of MHz, add a second ceramic-type capacitor in parallel to the above described decoupling capacitor. The value of the second capacitor can be in the range of 0.01  $\mu$ F to 0.001  $\mu$ F. Place this second capacitor next to the primary decoupling capacitor. In high-speed circuit designs, consider implementing a decade pair of capacitances as close to the power and ground pins as possible. For example, 0.1  $\mu$ F in parallel with 0.001  $\mu$ F.

- **Maximizing performance:** On the board layout from the power supply circuit, run the power and return traces to the decoupling capacitors first, and then to the device pins. This ensures that the decoupling capacitors are first in the power chain. Equally important is to keep the trace length between the capacitor and the power pins to a minimum thereby reducing PCB track inductance.

# 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS50001765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS50001764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" DS50001616

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) DS50001749

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

# 2.7 Trace

The trace pins can be connected to a hardware trace-enabled programmer to provide a compressed real-time instruction trace. When used for trace, the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

# 2.8 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

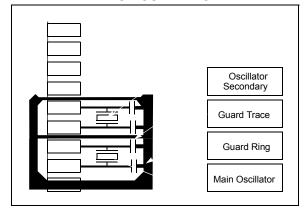

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 2.9 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

# 2.10 EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations

The use of LDO regulators is preferred to reduce overall system noise and provide a cleaner power source. However, when utilizing switching Buck/ Boost regulators as the local power source for PIC32 devices, as well as in electrically noisy environments or test conditions required for IEC 61000-4-4 and IEC 61000-4-2, users should evaluate the use of T-Filters (i.e., L-C-L) on the power pins, as shown in Figure 2-5. In addition to a more stable power source, use of this type of T-Filter can greatly reduce susceptibility to EMI sources and events.

FIGURE 2-5: EMI/EMC/EFT SUPPRESSION CIRCUIT

| Bit<br>Range | Bit<br>31/23/15/7   | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0      |

|--------------|---------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|-----------------------|

| 24.24        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 31:24        |                     | —                 | _                 | _                 |                   | _                 | -                | —                     |

| 00.40        | U-0                 | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                   |

| 23:16        | —                   | —                 | _                 | _                 | _                 | —                 | _                | —                     |

| 45.0         | R/W-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0                 |

| 15:8         | CHBUSY              | —                 | _                 | _                 | _                 | _                 | _                | CHCHNS <sup>(1)</sup> |

| 7.0          | R/W-0               | R/W-0             | R/W-0             | R/W-0             | U-0               | R-0               | R/W-0            | R/W-0                 |

| 7:0          | CHEN <sup>(2)</sup> | CHAED             | CHCHN             | CHAEN             | _                 | CHEDET            | CHPF             | RI<1:0>               |

#### REGISTER 10-7: DCHxCON: DMA CHANNEL 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 CHBUSY: Channel Busy bit

- 1 = Channel is active or has been enabled

- 0 = Channel is inactive or has been disabled

- bit 14-9 Unimplemented: Read as '0'

- bit 8 CHCHNS: Chain Channel Selection bit<sup>(1)</sup>

- 1 = Chain to channel lower in natural priority (CH1 will be enabled by CH2 transfer complete)

- 0 = Chain to channel higher in natural priority (CH1 will be enabled by CH0 transfer complete)

#### bit 7 CHEN: Channel Enable bit<sup>(2)</sup>

- 1 = Channel is enabled

- 0 = Channel is disabled

#### bit 6 CHAED: Channel Allow Events If Disabled bit

- 1 = Channel start/abort events will be registered, even if the channel is disabled

- 0 = Channel start/abort events will be ignored if the channel is disabled

#### bit CHCHN: Channel Chain Enable bit

- 1 = Allow channel to be chained

- 0 = Do not allow channel to be chained

- bit 4 CHAEN: Channel Automatic Enable bit

- 1 = Channel is continuously enabled, and not automatically disabled after a block transfer is complete

0 = Channel is disabled on block transfer complete

#### bit 3 Unimplemented: Read as '0'

- bit 2 CHEDET: Channel Event Detected bit

- 1 = An event has been detected

- 0 = No events have been detected

- bit 1-0 CHPRI<1:0>: Channel Priority bits

- 11 = Channel has priority 3 (highest)

- 10 = Channel has priority 2

- 01 = Channel has priority 1

- 00 = Channel has priority 0

- Note 1: The chain selection bit takes effect when chaining is enabled (i.e., CHCHN = 1).

- 2: When the channel is suspended by clearing this bit, the user application should poll the CHBUSY bit (if available on the device variant) to see when the channel is suspended, as it may take some clock cycles to complete a current transaction before the channel is suspended.

# REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER (CONTINUED)

- bit 1 CRC5EF: CRC5 Host Error Flag bit<sup>(4)</sup>

- 1 = Token packet is rejected due to CRC5 error

- 0 = Token packet is accepted

- EOFEF: EOF Error Flag bit<sup>(3,5)</sup>

- 1 = EOF error condition is detected

- 0 = No EOF error condition

- bit 0 PIDEF: PID Check Failure Flag bit

- 1 = PID check is failed

- 0 = PID check is passed

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

NOTES:

# REGISTER 18-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)

- bit 4 **DISSDI:** Disable SDI bit 1 = SDI pin is not used by the SPI module (pin is controlled by PORT function)

- 0 = SDI pin is controlled by the SPI module

- bit 3-2 STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

# 20.2 Timing Diagrams

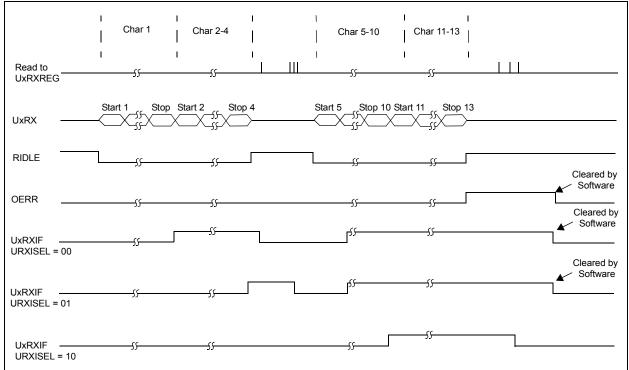

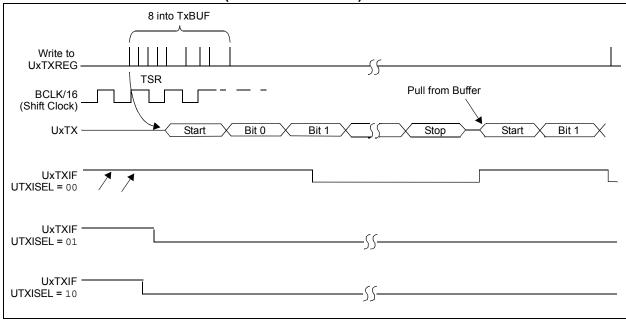

Figure 20-2 and Figure 20-3 illustrate typical receive and transmit timing for the UART module.

# FIGURE 20-2: UART RECEPTION

#### FIGURE 20-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

# 21.1 Control Registers

# TABLE 21-1: PARALLEL MASTER PORT REGISTER MAP

| ess                         |                                 | â         |            |                 |                                                                            |           |             |              |              | Bi          | ts       |        |      |      |      |      |      |      | \$         |

|-----------------------------|---------------------------------|-----------|------------|-----------------|----------------------------------------------------------------------------|-----------|-------------|--------------|--------------|-------------|----------|--------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15      | 30/14           | 29/13                                                                      | 28/12     | 27/11       | 26/10        | 25/9         | 24/8        | 23/7     | 22/6   | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 7000                        | PMCON                           | 31:16     | _          |                 | _                                                                          | _         | —           | —            | _            | _           | _        | _      | _    | _    | _    | _    | —    | _    | 0000       |

| 1000                        | 1 MOON                          | 15:0      | ON         | —               | SIDL                                                                       | ADRMU     | JX<1:0>     | PMPTTL       | PTWREN       | PTRDEN      | CSF      | <1:0>  | ALP  | CS2P | CS1P | —    | WRSP | RDSP | 0000       |

| 7010                        | PMMODE                          | 31:16     | —          | _               | _                                                                          | —         | _           | —            | _            | —           | _        | —      | _    | —    | _    | _    | —    | -    | 0000       |

| 7010                        |                                 | 15:0      | BUSY       | IRQM            | IRQM<1:0> INCM<1:0> MODE16 MODE<1:0> WAITB<1:0> WAITM<3:0> WAITE<1:0> 0000 |           |             |              |              |             |          |        | 0000 |      |      |      |      |      |            |

| 7020                        |                                 | 31:16     | -          |                 |                                                                            | _         | _           | _            |              | _           | _        | _      |      | _    |      |      | _    |      | 0000       |

| 7020                        | PMADDR                          | 15:0      | CS2        | CS1             |                                                                            |           |             |              |              |             | ADDR     | <13:0> |      |      |      |      |      |      | 0000       |

| 7030                        | PMDOUT                          | 31:16     |            |                 |                                                                            |           |             |              |              | DATAOU      | T<31.0>  |        |      |      |      |      |      |      | 0000       |

| 1000                        | TWDOOT                          | 15:0      |            |                 |                                                                            |           |             |              |              | DAIMOO      | 1 401.04 |        |      |      |      |      |      |      | 0000       |

| 7040                        | PMDIN                           | 31:16     |            |                 |                                                                            |           |             |              |              | DATAIN      | <31.0>   |        |      |      |      |      |      |      | 0000       |

| 7040                        |                                 | 15:0      |            |                 |                                                                            |           | -           | -            |              | D/ (I/ (II) | -01.04   |        |      |      |      |      | -    |      | 0000       |

| 7050                        | PMAEN                           | 31:16     | —          | _               | —                                                                          | —         | —           |              | —            | —           | _        | —      | —    | —    | —    | —    | —    | —    | 0000       |

| 7050                        | FINALIN                         | 15:0      |            | PTEN<15:0> 0000 |                                                                            |           |             |              |              |             |          |        |      |      |      |      |      |      |            |

| 7060                        | PMSTAT                          | 31:16     | _          |                 |                                                                            | _         | _           | _            |              | _           | _        | _      |      | _    |      |      | _    |      | 0000       |

| 1000                        | FINISTAT                        | 15:0      | IBF        | IBOV            |                                                                            | _         | IB3F        | IB2F         | IB1F         | IB0F        | OBE      | OBUF   | -    | _    | OB3E | OB2E | OB1E | OB0E | BFBF       |

| Legend                      | 4                               | inknow    | n value on | Reset:=         | unimpleme                                                                  | hear bate | as 'n' Rese | at values ar | e shown in l | nevadecima  | 1        |        |      |      |      |      |      |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

## REGISTER 23-1: AD1CON1: ADC CONTROL REGISTER 1 (CONTINUED)

bit 4 **CLRASAM:** Stop Conversion Sequence bit (when the first ADC interrupt is generated)

- 1 = Stop conversions when the first ADC interrupt is generated. Hardware clears the ASAM bit when the ADC interrupt is generated.

- 0 = Normal operation, buffer contents will be overwritten by the next conversion sequence

- bit 3 Unimplemented: Read as '0'

- bit 2 ASAM: ADC Sample Auto-Start bit

- 1 = Sampling begins immediately after last conversion completes; SAMP bit is automatically set.

0 = Sampling begins when SAMP bit is set

- bit 1 **SAMP:** ADC Sample Enable bit<sup>(2)</sup>

- 1 = The ADC sample and hold amplifier is sampling

- 0 = The ADC sample/hold amplifier is holding

- When ASAM = 0, writing '1' to this bit starts sampling.

- When SSRC = 000, writing '0' to this bit will end sampling and start conversion.

- bit 0 **DONE:** Analog-to-Digital Conversion Status bit<sup>(3)</sup>

- 1 = Analog-to-digital conversion is done

- 0 = Analog-to-digital conversion is not done or has not started

Clearing this bit will not affect any operation in progress.

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- 2: If ASAM = 0, software can write a '1' to start sampling. This bit is automatically set by hardware if ASAM = 1. If SSRC = 0, software can write a '0' to end sampling and start conversion. If SSRC ≠ 0, this bit is automatically cleared by hardware to end sampling and start conversion.

- **3:** This bit is automatically set by hardware when ADC is complete. Software can write a '0' to clear this bit (a write of '1' is not allowed). Clearing this bit does not affect any operation already in progress. This bit is automatically cleared by hardware at the start of a new conversion.

| DC CHA        | ARACTER   | ISTICS                                                              | (unless o | Operating<br>therwise st<br>temperatur | t <b>ated)</b><br>re 0°C<br>-40° | ≤ TA ≤ +7<br>C ≤ TA ≤ | V to 3.6V<br>′0°C for Commercial<br>+85°C for Industrial<br>+105°C for V-temp |

|---------------|-----------|---------------------------------------------------------------------|-----------|----------------------------------------|----------------------------------|-----------------------|-------------------------------------------------------------------------------|

| Param.<br>No. | Symbol    | Characteristics                                                     | Min.      | Typical                                | Max.                             | Units                 | Conditions                                                                    |

| Operati       | ng Voltag | е                                                                   |           |                                        |                                  |                       |                                                                               |

| DC10          | Vdd       | Supply Voltage                                                      | 2.3       | _                                      | 3.6                              | V                     | _                                                                             |

| DC12          | Vdr       | RAM Data Retention Voltage<br>(Note 1)                              | 1.75      | —                                      | _                                | V                     | _                                                                             |

| DC16          | VPOR      | VDD Start Voltage<br>to Ensure Internal<br>Power-on Reset Signal    | 1.75      | _                                      | 2.1                              | V                     | _                                                                             |

| DC17          | SVDD      | <b>VDD Rise Rate</b><br>to Ensure Internal<br>Power-on Reset Signal | 0.00005   | _                                      | 0.115                            | V/µs                  | _                                                                             |

# TABLE 31-4: DC TEMPERATURE AND VOLTAGE SPECIFICATIONS

Note 1: This is the limit to which VDD can be lowered without losing RAM data.

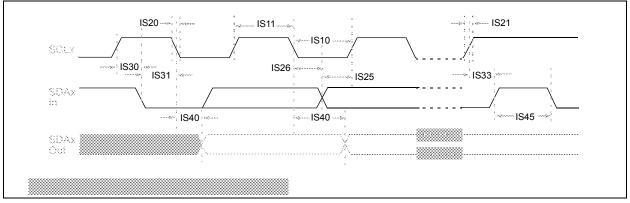

| AC CHA        | RACTER    | ISTICS          |                               | Standard Operatin<br>(unless otherwise<br>Operating tempera | e stated)<br>iture 0°(<br>-4( | C ≤ TA ≤ +<br>)°C ≤ TA ≤      | 70°C for Commercial<br>\$ +85°C for Industrial |

|---------------|-----------|-----------------|-------------------------------|-------------------------------------------------------------|-------------------------------|-------------------------------|------------------------------------------------|

| Param.<br>No. | Symbol    | Charact         | eristics                      | Min. <sup>(1)</sup>                                         | -40<br>Max.                   | $O^{\circ}C \le TA \le$ Units | Conditions                                     |

| IM10          | TLO:SCL   | Clock Low Time  | 100 kHz mode                  | Трв * (BRG + 2)                                             |                               | μS                            |                                                |

|               | 1201002   |                 | 400 kHz mode                  | Трв * (BRG + 2)                                             |                               | μs                            | _                                              |

|               |           |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             |                               | μs                            | -                                              |

| IM11          | THI:SCL   | Clock High Time | 100 kHz mode                  | Трв * (BRG + 2)                                             |                               | μS                            | _                                              |

|               |           | _               | 400 kHz mode                  | Трв * (BRG + 2)                                             |                               | μS                            | —                                              |

|               |           |                 | 1 MHz mode<br>(Note 2)        | Трв * (BRG + 2)                                             | _                             | μs                            | _                                              |

| IM20          | TF:SCL    | SDAx and SCLx   | 100 kHz mode                  |                                                             | 300                           | ns                            | CB is specified to be                          |

|               |           | Fall Time       | 400 kHz mode                  | 20 + 0.1 Св                                                 | 300                           | ns                            | from 10 to 400 pF                              |

|               |           |                 | 1 MHz mode<br><b>(Note 2)</b> | _                                                           | 100                           | ns                            |                                                |

| M21           | TR:SCL    | SDAx and SCLx   | 100 kHz mode                  | —                                                           | 1000                          | ns                            | CB is specified to be                          |

|               | Rise Time |                 | 400 kHz mode                  | 20 + 0.1 Св                                                 | 300                           | ns                            | from 10 to 400 pF                              |

|               |           |                 | 1 MHz mode<br><b>(Note 2)</b> | —                                                           | 300                           | ns                            |                                                |

| IM25          | TSU:DAT   | Data Input      | 100 kHz mode                  | 250                                                         |                               | ns                            | —                                              |

|               |           | Setup Time      | 400 kHz mode                  | 100                                                         | _                             | ns                            |                                                |

|               |           |                 | 1 MHz mode<br><b>(Note 2)</b> | 100                                                         | —                             | ns                            |                                                |

| IM26          | THD:DAT   | Data Input      | 100 kHz mode                  | 0                                                           | _                             | μS                            | —                                              |

|               |           | Hold Time       | 400 kHz mode                  | 0                                                           | 0.9                           | μS                            |                                                |

|               |           |                 | 1 MHz mode<br><b>(Note 2)</b> | 0                                                           | 0.3                           | μs                            |                                                |

| IM30          | TSU:STA   | Start Condition | 100 kHz mode                  | Трв * (BRG + 2)                                             | —                             | μS                            | Only relevant for                              |

|               |           | Setup Time      | 400 kHz mode                  | Трв * (BRG + 2)                                             |                               | μS                            | Repeated Start                                 |

|               |           |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                             | μs                            | condition                                      |

| IM31          | THD:STA   | Start Condition | 100 kHz mode                  | Трв * (BRG + 2)                                             | —                             | μS                            | After this period, the                         |

|               |           | Hold Time       | 400 kHz mode                  | Трв * (BRG + 2)                                             |                               | μS                            | first clock pulse is                           |

|               |           |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                             | μs                            | generated                                      |

| IM33          | Tsu:sto   | Stop Condition  | 100 kHz mode                  | Трв * (BRG + 2)                                             | —                             | μS                            | —                                              |

|               |           | Setup Time      | 400 kHz mode                  | Трв * (BRG + 2)                                             |                               | μS                            |                                                |

|               |           |                 | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | _                             | μS                            |                                                |

# TABLE 31-33: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

**Note 1:** BRG is the value of the  $l^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

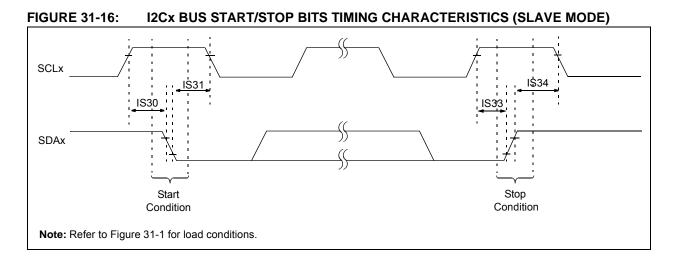

| AC CHA        | RACTERIS | STICS             |                        | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^\circ C \leq TA \leq +70^\circ C \mbox{ for Commerc} \\ & -40^\circ C \leq TA \leq +85^\circ C \mbox{ for Industr} \\ & -40^\circ C \leq TA \leq +105^\circ C \mbox{ for V-term} \end{array}$ |      |       |                            |  |  |  |

|---------------|----------|-------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-------|----------------------------|--|--|--|

| Param.<br>No. | Symbol   | Charact           | eristics               | Min.                                                                                                                                                                                                                                                                                                                                       | Max. | Units | Conditions                 |  |  |  |

| IS34          | THD:STO  | Stop Condition    | 100 kHz mode           | 4000                                                                                                                                                                                                                                                                                                                                       | _    | ns    | —                          |  |  |  |

|               |          | Hold Time         | 400 kHz mode           | 600                                                                                                                                                                                                                                                                                                                                        | _    | ns    |                            |  |  |  |

|               |          |                   | 1 MHz mode<br>(Note 1) | 250                                                                                                                                                                                                                                                                                                                                        |      | ns    |                            |  |  |  |

| IS40          | TAA:SCL  | Output Valid from | 100 kHz mode           | 0                                                                                                                                                                                                                                                                                                                                          | 3500 | ns    | —                          |  |  |  |

|               |          | Clock             | 400 kHz mode           | 0                                                                                                                                                                                                                                                                                                                                          | 1000 | ns    |                            |  |  |  |

|               |          |                   | 1 MHz mode<br>(Note 1) | 0                                                                                                                                                                                                                                                                                                                                          | 350  | ns    |                            |  |  |  |

| IS45          | TBF:SDA  | Bus Free Time     | 100 kHz mode           | 4.7                                                                                                                                                                                                                                                                                                                                        | —    | μs    | The amount of time the bus |  |  |  |

|               |          |                   | 400 kHz mode           | 1.3                                                                                                                                                                                                                                                                                                                                        |      | μs    | must be free before a new  |  |  |  |

|               |          |                   | 1 MHz mode<br>(Note 1) | 0.5                                                                                                                                                                                                                                                                                                                                        | _    | μS    | transmission can start     |  |  |  |

| IS50          | Св       | Bus Capacitive Lo | ading                  | _                                                                                                                                                                                                                                                                                                                                          | 400  | pF    | —                          |  |  |  |

# TABLE 31-34: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

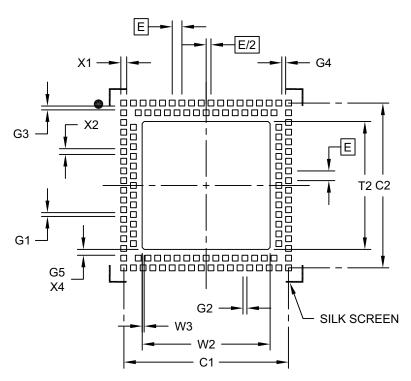

# 124-Very Thin Leadless Array Package (TL) – 9x9x0.9 mm Body [VTLA]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

# RECOMMENDED LAND PATTERN

|                                      | Units  | 1    | MILLIMETER: | S    |

|--------------------------------------|--------|------|-------------|------|

| Dimension                            | Limits | MIN  | NOM         | MAX  |

| Contact Pitch                        | E      |      | 0.50 BSC    |      |

| Pad Clearance                        | G1     | 0.20 |             |      |

| Pad Clearance                        | G2     | 0.20 |             |      |

| Pad Clearance                        | G3     | 0.20 |             |      |

| Pad Clearance                        | G4     | 0.20 |             |      |

| Contact to Center Pad Clearance (X4) | G5     | 0.30 |             |      |

| Optional Center Pad Width            | T2     |      |             | 6.60 |

| Optional Center Pad Length           | W2     |      |             | 6.60 |

| Optional Center Pad Chamfer (X4)     | W3     |      | 0.10        |      |

| Contact Pad Spacing                  | C1     |      | 8.50        |      |

| Contact Pad Spacing                  | C2     |      | 8.50        |      |

| Contact Pad Width (X124)             | X1     |      |             | 0.30 |

| Contact Pad Length (X124)            | X2     |      |             | 0.30 |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2193A

# INDEX

| Α                                         |     |

|-------------------------------------------|-----|

| AC Characteristics                        | 295 |

| 10-Bit Conversion Rate Parameters         | 318 |

| ADC Specifications                        | 316 |

| Analog-to-Digital Conversion Requirements | 319 |

| EJTAG Timing Requirements                 | 327 |

| Internal FRC Accuracy                     | 297 |

| Internal RC Accuracy                      | 297 |

| OTG Electrical Specifications             | 325 |

| Parallel Master Port Read Requirements    | 323 |

| Parallel Master Port Write                | 324 |

| Parallel Master Port Write Requirements   | 324 |

| Parallel Slave Port Requirements          | 322 |

| PLL Clock Timing                          | 297 |

| Analog-to-Digital Converter (ADC)         | 233 |

| Assembler                                 |     |

| MPASM Assembler                           | 276 |

# В

| Block Diagrams                                  |        |

|-------------------------------------------------|--------|

| ADC Module                                      | 233    |

| Comparator I/O Operating Modes                  | 243    |

| Comparator Voltage Reference                    | 247    |

| Connections for On-Chip Voltage Regulator       | 272    |

| CPU                                             | 35     |

| CTMU Configurations                             |        |

| Time Measurement                                | 251    |

| DMA                                             | 93     |

| I2C Circuit                                     | 198    |

| Input Capture                                   |        |

| Interrupt Controller                            |        |

| JTAG Programming, Debugging and Trace Ports     |        |

| Output Compare Module                           | 185    |

| PMP Pinout and Connections to External Devices. | 213    |

| Prefetch Module                                 | 83     |

| Reset System                                    | 59     |

| RTCC                                            | 223    |

| SPI Module                                      | 189    |

| Timer1                                          |        |

| Timer2/3/4/5 (16-Bit)                           |        |

| Typical Multiplexed Port Structure 137          | 7, 353 |

| UART                                            | 205    |

| WDT and Power-up Timer                          | 177    |

| Brown-out Reset (BOR)                           |        |

| and On-Chip Voltage Regulator                   | 272    |

|                                                 |        |

# С

| C Compilers                             |          |

|-----------------------------------------|----------|

| MPLAB C18                               |          |

| Charge Time Measurement Unit. See CTMU. |          |

| Clock Diagram                           | 74       |

| Comparator                              |          |

| Specifications                          | 293, 294 |

| Comparator Module                       |          |

| Comparator Voltage Reference (CVref     |          |

| Configuration Bit                       |          |

| Configuring Analog Port Pins            |          |

| CPU                                     |          |

| Architecture Overview                   |          |

| Coprocessor 0 Registers                 |          |

| Core Exception Types                    |          |

| EJTAG Debug Support                     |          |

| Power Management                        |          |

| -                                       |          |

| CPU Module<br>CTMU                   | 27, 35 |

|--------------------------------------|--------|

| Registers                            | 253    |

| Customer Change Notification Service | 359    |

| Customer Notification Service        | 359    |

| Customer Support                     | 359    |

|                                      |        |

# D

| DC and AC Characteristics              |     |

|----------------------------------------|-----|

| Graphs and Tables                      | 329 |

| DC Characteristics                     | 280 |

| I/O Pin Input Specifications           | 287 |

| I/O Pin Output Specifications          | 290 |

| Idle Current (IIDLE)                   | 283 |

| Power-Down Current (IPD)               | 284 |

| Program Memory                         | 292 |

| Temperature and Voltage Specifications | 281 |

| Development Support                    | 275 |

| Direct Memory Access (DMA) Controller  |     |

# Е

| —                                   |     |

|-------------------------------------|-----|

| Electrical Characteristics          | 279 |

| AC                                  | 295 |

| Errata                              | 14  |