Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                         |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | ·                                                                              |

| RAM Size                   | 128K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-VFQFN Exposed Pad                                                           |

| Supplier Device Package    | 64-QFN (9x9)                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx470f512h-i-mr |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

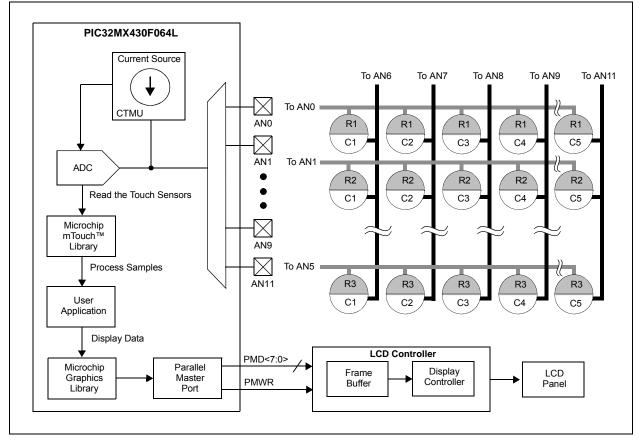

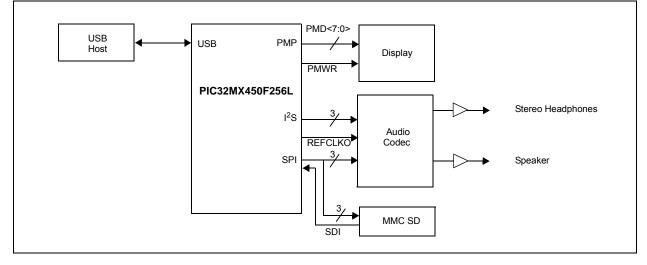

## 2.11 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-6, Figure 2-7, and Figure 2-8.

## FIGURE 2-6: CAPACITIVE TOUCH SENSING WITH GRAPHICS APPLICATION

## FIGURE 2-7: AUDIO PLAYBACK APPLICATION

## 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/ 470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Memory" (DS60001121), Program which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX330/350/370/430/450/470 devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: On PIC32MX330/350/370/430/450/470 devices, the Flash page size is 4 KB and the row size is 512 bytes (1024 IW and 128 IW, respectively).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1   | Bit<br>24/16/8/0   |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------|--------------------|

| 04.04        | U-0               | U-0               | R/W-0 U-0         |                   | U-0               | U-0               | U-0                | U-0                |

| 31:24        | —                 | —                 | HVDR              | —                 | _                 |                   | _                  | —                  |

| 00.40        | U-0                | U-0                |

| 23:16        | —                 | —                 | _                 | —                 | _                 |                   | _                  | —                  |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0, HS          | R/W-0              |

| 15:8         | —                 | —                 | —                 | —                 | _                 | —                 | CMR                | VREGS              |

| 7:0          | R/W-0, HS         | R/W-0, HS         | -0, HS U-0 R/W-0  |                   | R/W-0, HS         | R/W-0, HS         | R/W-1, HS          | R/W-1, HS          |

| 7:0          | EXTR              | SWR — WE          |                   | WDTO              | SLEEP             | IDLE              | BOR <sup>(1)</sup> | POR <sup>(1)</sup> |

#### **REGISTER 6-1: RCON: RESET CONTROL REGISTER**

| Legend:           | HS = Set by hardware | e                                               |                    |  |  |  |

|-------------------|----------------------|-------------------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit     | Writable bit U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared                            | x = Bit is unknown |  |  |  |

bit 31-30 Unimplemented: Read as '0'

- bit 29 HVDR: High Voltage Detect Reset Flag bit 1 = High Voltage Detect (HVD) Reset has occurred 0 = HVD Reset has not occurred bit 28-10 Unimplemented: Read as '0' bit 9 **CMR:** Configuration Mismatch Reset Flag bit 1 = Configuration mismatch Reset has occurred 0 = Configuration mismatch Reset has not occurred bit 8 VREGS: Voltage Regulator Standby Enable bit 1 = Regulator is enabled and is on during Sleep mode 0 = Regulator is set to Stand-by Tracking mode EXTR: External Reset (MCLR) Pin Flag bit bit 7 1 = Master Clear (pin) Reset has occurred 0 = Master Clear (pin) Reset has not occurred bit 6 SWR: Software Reset Flag bit 1 = Software Reset was executed 0 = Software Reset as not executed bit 5 Unimplemented: Read as '0' bit 4 WDTO: Watchdog Timer Time-out Flag bit 1 = WDT Time-out has occurred 0 = WDT Time-out has not occurred bit 3 **SLEEP:** Wake From Sleep Flag bit 1 = Device was in Sleep mode 0 = Device was not in Sleep mode bit 2 **IDLE:** Wake From Idle Flag bit 1 = Device was in Idle mode 0 = Device was not in Idle mode **BOR:** Brown-out Reset Flag bit<sup>(1)</sup> bit 1 1 = Brown-out Reset has occurred 0 = Brown-out Reset has not occurred bit 0 **POR:** Power-on Reset Flag bit<sup>(1)</sup> 1 = Power-on Reset has occurred

- 0 = Power-on Reset has not occurred

**Note 1:** User software must clear this bit to view next detection.

## REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits<sup>(1)</sup>

- 1111 = Reserved; do not use

- 1001 = Reserved; do not use 1000 = REFCLKI 0111 = System PLL output 0110 = USB PLL output 0101 = Sosc 0100 = LPRC 0011 = FRC 0010 = POSC 0001 = PBCLK 0000 = SYSCLK

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

| Bit<br>Range | ange 31/23/15/7 30/2 |            | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|----------------------|------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 31:24        | U-0                  | U-0        | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31.24        |                      |            |                   |                   | _                 |                   | -                | _                |  |  |  |  |

| 22:16        | U-0                  | U-0        | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        | -                    | -          | -                 | -                 | _                 | —                 | _                | _                |  |  |  |  |

| 15:8         | R/W-0                | R/W-0      | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |

| 10.0         | LMASK<10:3>          |            |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/W-0                | R/W-0      | R/W-0             | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 7:0          |                      | _MASK<2:0> |                   | _                 | _                 | _                 | _                | —                |  |  |  |  |

## REGISTER 9-4: CHEMSK: CACHE TAG MASK REGISTER

## Legend:

| Logonal           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Write '0'; ignore read

- bit 15-5 LMASK<10:0>: Line Mask bits

- 1 = Enables mask logic to force a match on the corresponding bit position in the LTAG<19:0> bits (CHETAG<23:4>) and the physical address.

- 0 = Only writeable for values of CHEIDX<3:0> bits (CHEACC<3:0>) equal to 0x0A and 0x0B. Disables mask logic.

- bit 4-0 Unimplemented: Write '0'; ignore read

|              |                   |                   | ••••              | •                 |                   |                   |                  |                  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 31:24        |                   |                   |                   | CHEW0<            | :31:24>           |                   |                  |                  |

| 23:16        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 23:10        |                   |                   |                   | CHEW0<            | :23:16>           |                   |                  |                  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 15:8         |                   |                   |                   | CHEW0             | <15:8>            |                   |                  |                  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |

| 7:0          |                   |                   | •                 | CHEWO             | )<7:0>            |                   |                  |                  |

#### REGISTER 9-5: CHEW0: CACHE WORD 0

| Legend:           |                  |                                    |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

bit 31-0 **CHEW0<31:0>:** Word 0 of the cache line selected by the CHEIDX<3:0> bits (CHEACC<3:0>) Readable only if the device is not code-protected.

## **10.1 Control Registers**

## TABLE 10-1: DMA GLOBAL REGISTER MAP

| ess                         |           | 0         |       |               |       |         |         |       |      | Bit  | S    |      |      |      |      |      |      |      | ŝ         |

|-----------------------------|-----------|-----------|-------|---------------|-------|---------|---------|-------|------|------|------|------|------|------|------|------|------|------|-----------|

| Virtual Address<br>(BF88_#) | 5         | Bit Range | 31/15 | 30/14         | 29/13 | 28/12   | 27/11   | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 2000                        | DMACON    | 31:16     | -     | _             | -     | —       | —       | _     | —    | —    | —    | —    | _    | —    | -    | —    | —    | _    | 0000      |

| 3000                        | DIVIACON  | 15:0      | ON    | _             | _     | SUSPEND | DMABUSY | —     | _    | _    | _    | —    | _    | —    | —    | _    | —    | _    | 0000      |

| 2010                        | DMASTAT   | 31:16     |       | _             | —     | —       | —       | _     | —    | —    | —    | —    | _    | _    | —    | _    | —    | _    | 0000      |

| 3010                        | DIVIASTAT | 15:0      | │     |               |       |         |         |       |      |      |      |      | 0000 |      |      |      |      |      |           |

| 2020                        | DMAADDR   | 31:16     |       | DMAADDR<31:0> |       |         |         |       |      |      |      |      |      |      |      |      |      |      |           |

| 3020                        | DIVIAADDR | 15:0      | 0000  |               |       |         |         |       |      |      |      |      |      |      |      |      |      |      |           |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

## TABLE 10-2: DMA CRC REGISTER MAP

| ess                         |          |           |               |       |       |       |       |           |      | Bi     | ts        |        | _      |      |      |      |          |      |            |

|-----------------------------|----------|-----------|---------------|-------|-------|-------|-------|-----------|------|--------|-----------|--------|--------|------|------|------|----------|------|------------|

| Virtual Address<br>(BF88_#) |          | Bit Range | 31/15         | 30/14 | 29/13 | 28/12 | 27/11 | 26/10     | 25/9 | 24/8   | 23/7      | 22/6   | 21/5   | 20/4 | 19/3 | 18/2 | 17/1     | 16/0 | All Resets |

| 2020                        |          | 31:16     | _             | —     | BYTO  | <1:0> | WBO   | —         | —    | BITO   | _         | —      | _      | _    | _    | —    | _        | _    | 0000       |

| 3030                        | DCRCCON  | 15:0      | _             | —     | _     |       |       | PLEN<4:0> |      |        | CRCEN     | CRCAPP | CRCTYP | —    | —    | C    | RCCH<2:0 | >    | 0000       |

| 3040                        | DCRCDATA | 31:16     |               |       |       |       |       |           |      | DCRCDA | TA -21.05 |        |        |      |      |      |          |      | 0000       |

| 3040                        | DCRCDAIA | 15:0      |               |       |       |       |       |           |      | DCRCDA | IA<31.0>  |        |        |      |      |      |          |      | 0000       |

| 2050                        | DCRCXOR  | 31:16     |               | 0000  |       |       |       |           |      |        |           |        |        |      |      | 0000 |          |      |            |

| 3050                        | DURUXUR  | 15:0      | DCRCXOR<31:0> |       |       |       |       |           |      |        |           |        |        |      | 0000 |      |          |      |            |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

# PIC32MX330/350/370/430/450/470

#### REGISTER 11-10: U1STAT: USB STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0 U-0           |                   | U-0               | U-0 U-0           |                  | U-0              |

| 31.24        |                   |                   |                   |                   |                   | _                 | _                | _                |

| 22.16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | —                 |                   |                   |                   | _                 | _                | _                |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.0         |                   | —                 |                   |                   |                   | _                 | _                | _                |

| 7:0          | R-x               | R-x R-x R-x       |                   | R-x               | R-x               | R-x               | U-0              | U-0              |

| 7:0          |                   | ENDP <sup>-</sup> | T<3:0>            |                   | DIR               | PPBI              |                  | _                |

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

|-------------------|------------------|---------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits (Represents the number of the BDT, updated by the last USB transfer.)

- 1111 = Endpoint 15 1110 = Endpoint 14 . . 0001 = Endpoint 1 0000 = Endpoint 0

- bit 3 **DIR:** Last BD Direction Indicator bit

- 1 = Last transaction was a transmit transfer (TX)

- 0 = Last transaction was a receive transfer (RX)

- bit 2 **PPBI:** Ping-Pong BD Pointer Indicator bit

- 1 = The last transaction was to the ODD BD bank

- 0 = The last transaction was to the EVEN BD bank

- bit 1-0 Unimplemented: Read as '0'

**Note:** The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF bit (U1IR<3>) is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

# TABLE 12-14: PORTF REGISTER MAP FOR PIC32MX430F064H, PIC32MX450F128H, PIC32MX450F256H, AND PIC32MX470F512H DEVICES ONLY

|                             |                                 | ÖNLY      |       |       |       |       |       |       |      |      |      |      |              |              |              |      |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|--------------|--------------|--------------|------|--------------|--------------|---------------|

| ess                         |                                 | 6         |       |       |       |       |       |       |      | Bi   | its  |      |              |              |              |      |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5         | 20/4         | 19/3         | 18/2 | 17/1         | 16/0         | All<br>Resets |

| 6510                        | TRISF                           | 31:16     |       | -     | —     | —     | -     | —     | —    | —    | -    | -    | —            | _            | —            | _    | —            | -            | 0000          |

| 0310                        | TRIO                            | 15:0      | _     | _     | —     | —     | _     | —     |      |      | _    |      | TRISF5       | TRISF4       | TRISF3       | _    | TRISF1       | TRISF0       | xxxx          |

| 6520                        | PORTF                           | 31:16     | —     | —     | —     | —     | —     | —     | —    | —    | —    | —    | —            | -            | —            | —    |              | —            | 0000          |

| 0020                        | TORM                            | 15:0      | _     | _     | —     | —     | _     |       |      |      | _    |      | RF5          | RF4          | RF3          | _    | RF1          | RF0          | xxxx          |

| 6530                        | LATF                            | 31:16     | —     | —     | —     | —     | _     | —     | —    | —    | _    |      | —            | —            | —            | —    |              | _            | 0000          |

| 0000                        | 5                               | 15:0      | —     | —     | —     | —     | _     | —     | —    | —    | _    | _    | LATF5        | LATF4        | LATF3        | —    | LATF1        | LATF0        | xxxx          |

| 6540                        | ODCF                            | 31:16     | —     | —     | —     | —     | _     |       | —    | —    | _    | _    | —            | —            | —            | —    |              | —            | 0000          |

| 0010                        | 0001                            | 15:0      | —     | —     | —     | —     | _     |       | —    | —    | _    | _    | ODCF5        | ODCF4        | ODCF3        | —    | ODCF1        | ODCF0        | xxxx          |

| 6550                        | CNPUF                           | 31:16     | —     | —     | —     | —     | _     | —     | —    | —    | _    | —    | —            | _            | —            | —    | _            | —            | 0000          |

| 0000                        |                                 | 15:0      | —     | —     | —     | —     | _     |       | —    | —    | _    | _    | CNPUF5       | CNPUF4       | CNPUF3       | —    | CNPUF1       | CNPUF0       | xxxx          |

| 6560                        | CNPDF                           | 31:16     | —     | —     | —     | —     | -     | —     | —    | —    | —    | _    | —            | -            | _            | —    | -            | —            | 0000          |

|                             | 0.11 5.                         | 15:0      | —     | —     | —     | —     | -     | —     | —    | —    | —    | _    | CNPDF5       | CNPDF4       | CNPDF3       | —    | CNPDF1       | CNPDF0       | xxxx          |

| 6570                        | CNCONF                          | 31:16     | _     | —     | —     | _     | _     | —     | —    | —    | —    |      | —            | _            | —            | _    |              | _            | 0000          |

| 00.0                        | 0.10011                         | 15:0      | ON    | —     | SIDL  | —     | -     | —     | —    | —    | —    | _    | —            | -            | —            | —    | —            | —            | 0000          |

| 6580                        | CNENF                           | 31:16     | —     | —     | —     | —     | -     | —     | —    | —    | —    | —    | —            | -            | _            | —    | -            | —            | 0000          |

|                             |                                 | 15:0      | —     | —     | —     | —     | -     | —     | —    | —    | —    | —    | CNIEF5       | CNIEF4       | CNIEF3       | —    | CNIEF1       | CNIEF0       | xxxx          |

|                             |                                 | 31:16     |       | —     | _     | —     | _     | —     | —    | —    | —    |      |              |              | —            | _    | -            | —            | 0000          |

| 6590                        | CNSTATF                         | 15:0      |       | _     | _     | _     | _     | _     | —    | —    | _    | _    | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | _    | CN<br>STATF1 | CN<br>STATF0 | xxxx          |

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

NOTES:

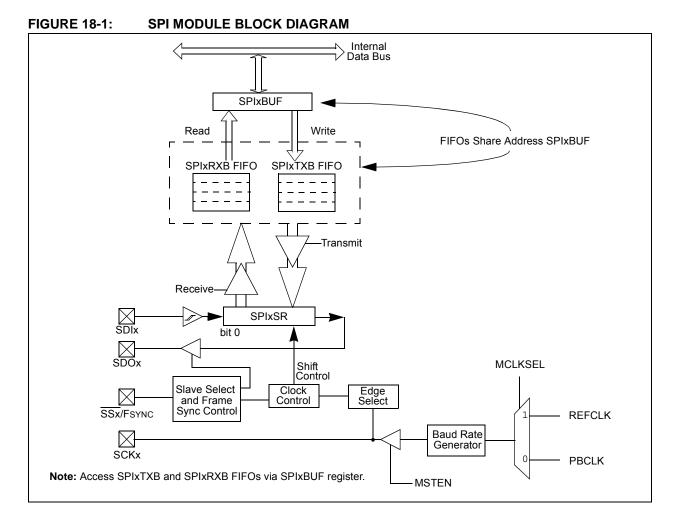

## 18.0 SERIAL PERIPHERAL INTERFACE (SPI)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 23. "Serial Peripheral Interface (SPI)" (DS60001106), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The SPI module is a synchronous serial interface that is useful for communicating with external peripherals and other microcontroller devices. These peripheral devices may be Serial EEPROMs, Shift registers, display drivers, Analog-to-Digital Converters (ADC), etc. The PIC32 SPI module is compatible with Motorola<sup>®</sup> SPI and SIOP interfaces. Some of the key features of the SPI module are:

- · Master and Slave modes support

- · Four different clock formats

- Enhanced Framed SPI protocol support

- User-configurable 8-bit, 16-bit and 32-bit data width

- Separate SPI FIFO buffers for receive and transmit

FIFO buffers act as 4/8/16-level deep FIFOs based on 32/16/8-bit data width

- Programmable interrupt event on every 8-bit, 16-bit and 32-bit data transfer

- Operation during CPU Sleep and Idle mode

- Audio Codec Support:

- I<sup>2</sup>S protocol

- Left-justified

- Right-justified

- PCM

#### **Control Registers** 19.1

## TABLE 19-1: I2C1 AND I2C2 REGISTER MAP

| ess                         |                                 |               |              |          |           |             |             |             |                       | Bi        | ts                                    |             |            |              |            |          |           |          |              |

|-----------------------------|---------------------------------|---------------|--------------|----------|-----------|-------------|-------------|-------------|-----------------------|-----------|---------------------------------------|-------------|------------|--------------|------------|----------|-----------|----------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14    | 29/13     | 28/12       | 27/11       | 26/10       | 25/9                  | 24/8      | 23/7                                  | 22/6        | 21/5       | 20/4         | 19/3       | 18/2     | 17/1      | 16/0     | All Resets   |

| 5000                        | I2C1CON                         | 31:16<br>15:0 | —<br>ON      | -        | —<br>SIDL | —<br>SCLREL | —<br>STRICT | —<br>A10M   | —<br>DISSLW           | —<br>SMEN | —<br>GCEN                             | —<br>STREN  | —<br>ACKDT | —<br>ACKEN   | —<br>RCEN  | —<br>PEN | —<br>RSEN | —<br>SEN | 0000<br>BFFF |

| 5010                        | I2C1STAT                        | 31:16         | _            | —        |           | -           | —           |             | —                     | _         | —                                     | —           | -          | —            |            | _        | —         |          | 0000         |

| 5010                        | 120131AI                        | 15:0          | ACKSTAT      | TRSTAT   |           | —           | —           | BCL         | GCSTAT                | ADD10     | IWCOL                                 | I2COV       | D_A        | Р            | S          | R_W      | RBF       | TBF      | 0000         |

| 5020                        | I2C1ADD                         | 31:16         | _            | _        |           | —           | -           |             | _                     | _         | _                                     | _           | -          | _            |            | _        | _         | -        | 0000         |

| 5020                        | 120 TADD                        | 15:0          | —            | —        |           | —           | —           |             |                       |           |                                       | -           | Address    | Register     |            |          |           |          | 0000         |

| 5030                        | I2C1MSK                         | 31:16         | —            | —        | _         | —           | —           | _           | —                     | —         |                                       |             |            |              |            |          |           |          | 0000         |

| 0000                        | 1201111010                      | 15:0          | —            | —        | —         | —           | —           | —           |                       |           |                                       |             | Address Ma | ask Register |            |          |           |          | 0000         |

| 5040                        | I2C1BRG                         | 31:16         | _            | —        | —         | -           | —           | —           | —                     | _         | _                                     | —           | —          | —            | —          | _        | —         | —        | 0000         |

|                             |                                 | 15:0          | _            | _        |           |             |             |             |                       |           | Bau                                   | id Rate Ger | erator Reg | ister        |            |          |           |          | 0000         |

| 5050                        | I2C1TRN                         | 31:16         | _            | _        |           |             |             |             | —                     | _         | _                                     | —           | _          | —            | —          | —        | —         | —        | 0000         |

|                             | -                               | 15:0          | _            | —        |           |             | —           |             | —                     | _         |                                       |             |            | Transmit     | Register   |          |           |          | 0000         |

| 5060                        | I2C1RCV                         | 31:16         | —            | —        | _         |             | —           | _           | —                     | —         | —                                     | —           | —          | —            | —          | —        | —         | —        | 0000         |

|                             |                                 | 15:0          | _            |          | —         | —           | —           | —           | —                     | —         |                                       |             |            | Receive      |            |          |           |          | 0000         |

| 5100                        | I2C2CON                         | 31:16         | _            | _        | —         | —           | —           | —           | —                     | _         | _                                     | —           | —          | —            | —          | —        | —         | _        | 0000         |

|                             |                                 | 15:0          | ON           | _        | SIDL      | SCLREL      | STRICT      | A10M        | DISSLW                | SMEN      | GCEN                                  | STREN       | ACKDT      | ACKEN        | RCEN       | PEN      | RSEN      | SEN      | BFFF         |

| 5110                        | I2C2STAT                        | 31:16         | _            |          | _         |             | _           | -           | _                     | -         |                                       | —           | -          | -            | -          |          | _         |          | 0000         |

|                             |                                 |               | ACKSTAT      | TRSTAT   |           |             |             | BCL         | GCSTAT                | ADD10     | IWCOL                                 | I2COV       | D_A        | Р            | S          | R_W      | RBF       | TBF      | 0000         |

| 5120                        | I2C2ADD                         | 31:16         | _            | —        |           | _           | —           |             | —                     | _         | _                                     | —           | —          | —            | —          | —        | —         | —        | 0000         |

|                             |                                 | 15:0<br>31:16 | _            |          | —         | _           | _           | —           |                       |           |                                       |             | Address    | Register     |            |          |           |          | 0000         |

| 5130                        | I2C2MSK                         | 15:0          | _            |          | _         |             |             |             |                       | _         | _                                     | _           |            | -            | —          |          | _         | _        | 0000         |

|                             |                                 | 31:16         |              |          |           | _           |             |             | Address Mask Register |           |                                       |             |            |              |            | 0000     |           |          |              |

| 5140                        | I2C2BRG                         | 15:0          |              |          | _         |             | _           | _           | _                     | _         | — — — — — — — — — — — — — — — — — — — |             |            |              |            |          | _         | 0000     |              |

|                             |                                 | 31:16         | _            |          |           |             | _           | _           |                       | _         | Dat                                   |             |            |              | _          |          |           |          | 0000         |

| 5150                        | I2C2TRN                         | 15:0          |              |          | _         |             |             |             |                       |           | — Transmit Register                   |             |            |              |            |          |           | 0000     |              |

|                             |                                 | 31:16         |              |          |           |             |             |             |                       |           |                                       |             |            |              |            |          |           | _        | 0000         |

| 5160                        | I2C2RCV                         | 15:0          | _            |          |           |             |             |             |                       | _         |                                       |             |            |              |            |          | 0000      |          |              |

| Legen                       | d                               |               | n value en l | Posot: - | unimplome | ntod road r | as '0' Been | t values er | shown in h            | ovadacima |                                       |             |            | RECEIVE      | i togistoi |          |           |          | 0000         |

All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information. Note 1:

## REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | —                 | —                 | -                 | -                 | —                 | _                 | -                | -                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        |                   | —                 | _                 | _                 | _                 |                   | _                |                  |  |  |  |  |  |

| 15.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |  |  |  |  |  |

| 15:8         | ACKSTAT           | TRSTAT            | -                 | _                 | _                 | BCL               | GCSTAT           | ADD10            |  |  |  |  |  |

| 7:0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |  |  |  |  |  |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |  |  |  |  |  |

| Legend:           | HS = Set in hardware | HSC = Hardware set/clear  | ed                |

|-------------------|----------------------|---------------------------|-------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ead as '0'        |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | C = Clearable bit |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit

(when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Acknowledge was not received from slave

- 0 = Acknowledge was received from slave

Hardware set or clear at end of slave Acknowledge.

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

1 = A bus collision has been detected during a master operation

0 = No collision

Hardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module.

- bit 9 **GCSTAT:** General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware set when address matches general call address. Hardware clear at Stop detection.

bit 8 ADD10: 10-bit Address Status bit

1 = 10-bit address was matched

0 = 10-bit address was not matched

Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

- bit 7 IWCOL: Write Collision Detect bit

- 1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy

- 0 = No collision

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

bit 6 I2COV: Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

#### 20.1 **Control Registers**

## TABLE 20-1: UART1 THROUGH UART5 REGISTER MAP

| ess)                        |                       | Ð         |        |        |        |       |        |       |       | Bi          | ts                                                                          |         |       |          |          |       |        |       | s          |

|-----------------------------|-----------------------|-----------|--------|--------|--------|-------|--------|-------|-------|-------------|-----------------------------------------------------------------------------|---------|-------|----------|----------|-------|--------|-------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15  | 30/14  | 29/13  | 28/12 | 27/11  | 26/10 | 25/9  | 24/8        | 23/7                                                                        | 22/6    | 21/5  | 20/4     | 19/3     | 18/2  | 17/1   | 16/0  | All Resets |

| 6000                        | U1MODE <sup>(1)</sup> | 31:16     | _      |        | _      | _     | _      |       |       | _           | _                                                                           | —       | _     | _        |          | -     |        |       | 0000       |

| 0000                        | UTMODE: /             | 15:0      | ON     |        | SIDL   | IREN  | RTSMD  |       | UEN   | <1:0>       | WAKE                                                                        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 6010                        | U1STA <sup>(1)</sup>  | 31:16     | _      | —      | —      | —     | —      | _     | _     | ADM_EN      |                                                                             |         |       |          | 0000     |       |        |       |            |

| 0010                        | 01317                 | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE                                                                      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | FFFF       |

| 6020                        | U1TXREG               | 31:16     | —      | _      | —      | —     | —      | _     | _     | —           | _                                                                           | _       | —     | —        | _        | —     | _      | _     | 0000       |

| 0020                        | UTIXILEO              | 15:0      | —      | _      |        | _     | —      | _     | _     | TX8         |                                                                             |         |       | Transmit | Register |       |        |       | 0000       |

| 6030                        | U1RXREG               | 31:16     | —      | —      | —      | —     | —      | —     | —     | —           | —                                                                           | —       | —     | —        | —        | —     | —      | —     | 0000       |

| 0000                        | ONVILO                | 15:0      | —      | —      | —      | —     | —      | —     | —     | RX8         |                                                                             |         |       | Receive  | Register |       |        |       | 0000       |

| 6040                        | U1BRG <sup>(1)</sup>  | 31:16     |        | —      |        | —     | —      | —     | —     | —           |                                                                             | —       | —     | —        | —        | —     | —      | —     | 0000       |

| 0010                        | OTDICO                | 15:0      |        |        |        |       |        |       | Bau   | d Rate Gene | erator Pres                                                                 | caler   |       |          |          |       |        |       | 0000       |

| 6200                        | U2MODE <sup>(1)</sup> | 31:16     | —      | _      | —      | —     | —      | —     | —     | —           | _                                                                           | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                       | 15:0      | ON     |        | SIDL   | IREN  | RTSMD  | —     | UEN   |             | WAKE      LPBACK      ABAUD      RXINV      BRGH      PDSEL<1:0>      STSEL |         |       |          | STSEL    | 0000  |        |       |            |

| 6210                        | U2STA <sup>(1)</sup>  | 31:16     |        |        |        | —     | —      | —     | —     | ADM_EN      |                                                                             |         | 1     | ADDR     |          |       |        |       | 0000       |

|                             |                       | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE                                                                      | EL<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | FFFF       |

| 6220                        | U2TXREG               | 31:16     | _      |        |        | _     | —      | _     |       | —           | _                                                                           | —       | —     |          | —        | _     | —      | _     | 0000       |

|                             |                       | 15:0      | _      |        |        | _     | —      | _     |       | TX8         |                                                                             |         |       | Transmit | Register |       |        |       | 0000       |

| 6230                        | U2RXREG               | 31:16     | —      | —      | —      | —     | —      | —     | —     | —           | _                                                                           | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                       | 15:0      | —      | —      | —      | —     | —      | —     | —     | RX8         |                                                                             |         |       | Receive  | Register |       |        |       | 0000       |

| 6240                        | U2BRG <sup>(1)</sup>  | 31:16     |        |        |        |       |        | _     | _     |             |                                                                             |         | _     |          | —        | _     | _      | —     | 0000       |

|                             |                       | 15:0      |        |        |        |       |        |       | Bau   | d Rate Gene | erator Pres                                                                 | caler   |       |          |          |       |        |       | 0000       |

| 6400                        | U3MODE <sup>(1)</sup> | 31:16     | _      | _      | —      | —     | —      | _     | _     | —           |                                                                             | —       | —     | —        | —        | —     | _      | —     | 0000       |

|                             |                       | 15:0      | ON     | _      | SIDL   | IREN  | RTSMD  | _     | UEN   | -           | WAKE                                                                        | LPBACK  | ABAUD | RXINV    | BRGH     | PDSEI | _<1:0> | STSEL | 0000       |

| 6410                        | U3STA <sup>(1)</sup>  | 31:16     | -      | —      | —      | -     | -      | -     | -     | ADM_EN      |                                                                             |         |       |          |          | 0000  |        |       |            |

|                             |                       | 15:0      | UTXISE | L<1:0> | UTXINV | URXEN | UTXBRK | UTXEN | UTXBF | TRMT        | URXISE                                                                      | =L<1:0> | ADDEN | RIDLE    | PERR     | FERR  | OERR   | URXDA | FFFF       |

| 6420                        | U3TXREG               | 31:16     | _      | _      | —      |       | _      | _     | _     | —<br>       | —                                                                           | —       | —     | —<br>—   | —        | —     | —      | —     | 0000       |

|                             |                       | 15:0      | _      | _      | —      | _     | _      | _     |       | TX8         |                                                                             |         |       | Transmit | -        |       |        |       | 0000       |

| 6430                        | U3RXREG               | 31:16     | _      |        | —      | _     | _      | _     | _     | -           | —                                                                           | —       | —     | —        | —        | —     | —      | —     | 0000       |

|                             |                       | 15:0      |        |        |        |       |        |       |       |             | 0000                                                                        |         |       |          |          |       |        |       |            |

x = unknown value on Reset; ---- = unimplemented, read as '0'. Reset values are shown in hexadecimal. Legend:

This register has corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV registers" for more informa-Note 1: tion.

## REGISTER 21-2: PMMODE: PARALLEL PORT MODE REGISTER (CONTINUED)

- bit 5-2 WAITM<3:0>: Data Read/Write Strobe Wait States bits<sup>(1)</sup>

- 1111 = Wait of 16 Трв • •

- 0001 = Wait of 2 Трв 0000 = Wait of 1 Трв (default)

- bit 1-0 WAITE<1:0>: Data Hold After Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Wait of 4 TPB 10 = Wait of 3 TPB 01 = Wait of 2 TPB

- 00 = Wait of 1 Трв (default)

For Read operations: 11 = Wait of 3 TPB 10 = Wait of 2 TPB 01 = Wait of 1 TPB 00 = Wait of 0 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPB cycle for a write operation; WAITB = 1 TPB cycle, WAITE = 0 TPB cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- **3:** These pins are active when MODE16 = 1 (16-bit mode).

## 25.1 Control Register

## TABLE 25-1: COMPARATOR VOLTAGE REFERENCE REGISTER MAP

| ess                       | Bits                            |           |       |       |       |       |       |       |      |      |      | ú     |      |       |      |      |      |      |           |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|-------|------|-------|------|------|------|------|-----------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6  | 21/5 | 20/4  | 19/3 | 18/2 | 17/1 | 16/0 | All Reset |

| 0000                      | CVRCON                          | 31:16     | _     | _     | _     | _     | —     | -     | —    | —    | -    | -     | _    | —     | —    | —    | —    | _    | 0000      |

| 9000                      | CVRCON                          | 15:0      | ON    | _     | _     | _     | —     | —     | —    | —    | _    | CVROE | CVRR | CVRSS |      | CVR< | 3:0> |      | 0000      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: The register in this table has corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 04.04        | R/P               | R/P               | R/P               | R/P               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | FVBUSONIO         | FUSBIDIO          | IOL1WAY           | PMDL1WAY          | —                 |                   | —                | _                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | R/P               | R/P              | R/P              |  |  |  |  |

| 23.10        | —                 | —                 | —                 | —                 | _                 | FSRSSEL<2:0>      |                  |                  |  |  |  |  |

| 15.0         | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |  |

| 15:8         | USERID<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7:0          | R/P               | R/P               | R/P               | R/P               | R/P               | R/P               | R/P              | R/P              |  |  |  |  |

| 7:0          | USERID<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

## REGISTER 28-4: DEVCFG3: DEVICE CONFIGURATION WORD 3

| Legend:           | r = Reserved bit | P = Programmable bit   |                    |

|-------------------|------------------|------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

bit 31 **FVBUSONIO:** USB VBUS\_ON Selection bit 1 = VBUSON pin is controlled by the USB module

- 0 = VBUSON pin is controlled by the OSB module0 = VBUSON pin is controlled by the port function

- bit 30 **FUSBIDIO:** USB USBID Selection bit 1 = USBID pin is controlled by the USB module 0 = USBID pin is controlled by the port function

- bit 29 IOL1WAY: Peripheral Pin Select Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 28 PMDL1WAY: Peripheral Module Disable Configuration bit

- 1 = Allow only one reconfiguration

- 0 = Allow multiple reconfigurations

- bit 27-19 Unimplemented: Read as '0'

#### bit 18-16 FSRSSEL<2:0>: Shadow Register Set Priority Select bit

These bits assign an interrupt priority to a shadow register.

- 111 = Shadow register set used with interrupt priority 7

- 110 = Shadow register set used with interrupt priority 6

- 101 = Shadow register set used with interrupt priority 5

- 100 = Shadow register set used with interrupt priority 4

- O11 = Shadow register set used with interrupt priority 3

- 010 = Shadow register set used with interrupt priority 2

- 001 = Shadow register set used with interrupt priority 1

- 000 = Shadow register set used with interrupt priority 0

- bit 15-0 USERID<15:0>: This is a 16-bit value that is user-defined and is readable via ICSP™ and JTAG

| DC CHARACT       | ERISTICS               |               | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |                 |                                       |                           |  |  |  |

|------------------|------------------------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|---------------------------------------|---------------------------|--|--|--|

| Parameter<br>No. | Typical <sup>(2)</sup> | Maximum       | Units                                                                                                                                                                                                                                                                                                                                               |                 | Conditions                            |                           |  |  |  |

| Idle Current (I  | IDLE): Core Of         | f, Clock on E | Base Curre                                                                                                                                                                                                                                                                                                                                          | nt (Note 1)     |                                       |                           |  |  |  |

| DC30a            | 1                      | 2.2           | mA                                                                                                                                                                                                                                                                                                                                                  |                 | 4 MHz                                 |                           |  |  |  |

| DC31a            | 3                      | 5             | mA                                                                                                                                                                                                                                                                                                                                                  | 10 MHz (Note 3) |                                       |                           |  |  |  |

| DC32a            | 5                      | 7             | mA                                                                                                                                                                                                                                                                                                                                                  |                 | 20 MHz <b>(Note 3)</b>                |                           |  |  |  |

| DC33a            | 8                      | 13            | mA                                                                                                                                                                                                                                                                                                                                                  |                 | 40 MHz <b>(Note 3)</b>                |                           |  |  |  |

| DC34a            | 11                     | 18            | mA                                                                                                                                                                                                                                                                                                                                                  |                 | 60 MHz <b>(Note 3)</b>                |                           |  |  |  |

| DC34b            | 15                     | 24            | mA                                                                                                                                                                                                                                                                                                                                                  |                 | 80 MHz                                |                           |  |  |  |

| DC34c            | 19                     | 29            | mA                                                                                                                                                                                                                                                                                                                                                  | 1               | 100 MHz, $-40^{\circ}C \le TA \le +8$ | 35°C                      |  |  |  |

| DC34d            | 25                     | 34            | mA                                                                                                                                                                                                                                                                                                                                                  |                 | 120 MHz, $0^{\circ}C \leq TA \leq +7$ | D°C                       |  |  |  |

| DC37a            | 100                    | —             | μA                                                                                                                                                                                                                                                                                                                                                  | -40°C           |                                       |                           |  |  |  |

| DC37b            | 250                    | _             | μA                                                                                                                                                                                                                                                                                                                                                  | +25°C           | 3.3V                                  | LPRC (31 kHz)<br>(Note 3) |  |  |  |

| DC37c            | 380                    | _             | μA                                                                                                                                                                                                                                                                                                                                                  | +85°C           |                                       | (11018-0)                 |  |  |  |

## TABLE 31-6: DC CHARACTERISTICS: IDLE CURRENT (IIDLE)

Note 1: The test conditions for IIDLE measurements are as follows:

Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)</li>

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Idle mode (CPU core is halted), program Flash memory Wait states = 7, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is cleared

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- · All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- RTCC and JTAG are disabled

- 2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: This parameter is characterized, but not tested in manufacturing.

# PIC32MX330/350/370/430/450/470

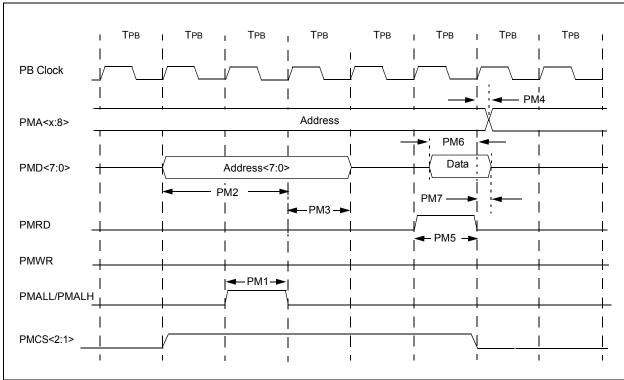

## FIGURE 31-21: PARALLEL MASTER PORT READ TIMING DIAGRAM

## TABLE 31-39: PARALLEL MASTER PORT READ TIMING REQUIREMENTS

| AC CHA        | ARACTER | ISTICS                                                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |       |      |       |            |  |  |  |  |

|---------------|---------|----------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|------------|--|--|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>                                       | Min.                                                                                                                                                                                                                                                                                                                                               | Тур.  | Max. | Units | Conditions |  |  |  |  |

| PM1           | TLAT    | PMALL/PMALH Pulse Width                                              | —                                                                                                                                                                                                                                                                                                                                                  | 1 Трв | _    | —     | _          |  |  |  |  |

| PM2           | Tadsu   | Address Out Valid to PMALL/<br>PMALH Invalid (address setup time)    | _                                                                                                                                                                                                                                                                                                                                                  | 2 Трв | —    |       | —          |  |  |  |  |

| PM3           | Tadhold | PMALL/PMALH Invalid to<br>Address Out Invalid (address<br>hold time) | _                                                                                                                                                                                                                                                                                                                                                  | 1 Трв | —    |       |            |  |  |  |  |

| PM4           | TAHOLD  | PMRD Inactive to Address Out<br>Invalid<br>(address hold time)       | 5                                                                                                                                                                                                                                                                                                                                                  | —     | —    | ns    | _          |  |  |  |  |

| PM5           | Trd     | PMRD Pulse Width                                                     | —                                                                                                                                                                                                                                                                                                                                                  | 1 Трв | _    | —     | —          |  |  |  |  |

| PM6           | TDSU    | PMRD or PMENB Active to Data<br>In Valid (data setup time)           | 15                                                                                                                                                                                                                                                                                                                                                 | —     | —    | ns    | —          |  |  |  |  |

| PM7           | TDHOLD  | PMRD or PMENB Inactive to<br>Data In Invalid (data hold time)        | 1 Трв                                                                                                                                                                                                                                                                                                                                              | —     | —    | —     | PMP Clock  |  |  |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

| AC CHA        | RACTERI | STICS                             | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |      |       |                                                                                   |  |  |  |

|---------------|---------|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------------------|--|--|--|

| Param.<br>No. | Symbol  | Characteristics <sup>(1)</sup>    | Min.                                                                                                                                                                                                                                                                                                                                               | Тур. | Max. | Units | Conditions                                                                        |  |  |  |

| USB313        | VUSB3V3 | USB Voltage                       | 3.0                                                                                                                                                                                                                                                                                                                                                |      | 3.6  | V     | Voltage on VUSB3V3<br>must be in this range<br>for proper USB<br>operation        |  |  |  |

| USB315        | VILUSB  | Input Low Voltage for USB Buffer  | —                                                                                                                                                                                                                                                                                                                                                  | _    | 0.8  | V     | —                                                                                 |  |  |  |

| USB316        | VIHUSB  | Input High Voltage for USB Buffer | 2.0                                                                                                                                                                                                                                                                                                                                                | —    | _    | V     | —                                                                                 |  |  |  |

| USB318        | VDIFS   | Differential Input Sensitivity    | —                                                                                                                                                                                                                                                                                                                                                  |      | 0.2  | V     | The difference<br>between D+ and D-<br>must exceed this value<br>while VCM is met |  |  |  |

| USB319        | VCM     | Differential Common Mode Range    | 0.8                                                                                                                                                                                                                                                                                                                                                | _    | 2.5  | V     | —                                                                                 |  |  |  |