Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                                |

|----------------------------|--------------------------------------------------------------------------------|

| Product Status             | Active                                                                         |

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 49                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 128K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 64-TQFP                                                                        |

| Supplier Device Package    | 64-TQFP (10x10)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx470f512h-v-pt |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS | (CONTINUED) |

|------------|-------------------------|-------------|

|------------|-------------------------|-------------|

|                      |                                       | Pin Numb                              | er                                      |             |                |                                                |  |  |  |

|----------------------|---------------------------------------|---------------------------------------|-----------------------------------------|-------------|----------------|------------------------------------------------|--|--|--|

| Pin Name             | 64-pin<br>QFN/<br>TQFP                | 100-pin<br>TQFP                       | 124-pin<br>VTLA                         | Pin<br>Type | Buffer<br>Type | Description                                    |  |  |  |

| U1CTS                | PPS                                   | PPS                                   | PPS                                     | I           | ST             | UART1 Clear to Send                            |  |  |  |

| U1RTS                | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART1 Ready to Send                            |  |  |  |

| U1RX                 | PPS                                   | PPS                                   | PPS                                     | I           | ST             | UART1 Receive                                  |  |  |  |

| U1TX                 | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART1 Transmit                                 |  |  |  |

| U2CTS                | PPS                                   | PPS                                   | PPS                                     | I           | ST             | UART2 Clear to Send                            |  |  |  |

| U2RTS                | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART2 Ready to Send                            |  |  |  |

| U2RX                 | PPS                                   | PPS                                   | PPS                                     | I           | ST             | UART2 Receive                                  |  |  |  |

| U2TX                 | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART2 Transmit                                 |  |  |  |

| U3CTS                | PPS                                   | PPS                                   | PPS                                     | I           | ST             | UART3 Clear to Send                            |  |  |  |

| U3RTS                | PPS                                   | PPS                                   | PPS                                     | 0           |                | UART3 Ready to Send                            |  |  |  |

| U3RX                 | PPS                                   | PPS                                   | PPS                                     |             | ST             | UART3 Receive                                  |  |  |  |

| U3TX                 | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART3 Transmit                                 |  |  |  |

| U4CTS                | PPS                                   | PPS                                   | PPS                                     | I           | ST             | UART4 Clear to Send                            |  |  |  |

| U4RTS                | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART4 Ready to Send                            |  |  |  |

| U4RX                 | PPS                                   | PPS                                   | PPS                                     | I           | ST             | UART4 Receive                                  |  |  |  |

| U4TX                 | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART4 Transmit                                 |  |  |  |

| U5CTS <sup>(3)</sup> | _                                     | PPS                                   | PPS                                     |             | ST             | UART5 Clear to Send                            |  |  |  |

| U5RTS <sup>(3)</sup> | _                                     | PPS                                   | PPS                                     | 0           |                | UART5 Ready to Send                            |  |  |  |

| U5RX <sup>(3)</sup>  | _                                     | PPS                                   | PPS                                     | I           | ST             | UART5 Receive                                  |  |  |  |

| U5TX <sup>(3)</sup>  | _                                     | PPS                                   | PPS                                     | 0           | _              | UART5 Transmit                                 |  |  |  |

| SCK1                 | 35 <sup>(1)</sup> , 50 <sup>(2)</sup> | 55 <sup>(1)</sup> , 70 <sup>(2)</sup> | B30 <sup>(1)</sup> , B38 <sup>(2)</sup> | I/O         | ST             | Synchronous Serial Clock Input/Output for SPI1 |  |  |  |

| SDI1                 | PPS                                   | PPS                                   | PPS                                     | 0           |                | SPI1 Data In                                   |  |  |  |

| SDO1                 | PPS                                   | PPS                                   | PPS                                     | I/O         | ST             | SPI1 Data Out                                  |  |  |  |

| SS1                  | PPS                                   | PPS                                   | PPS                                     | I/O         | —              | SPI1 Slave Synchronization for Frame Pulse I/O |  |  |  |

| SCK2                 | 4                                     | 10                                    | A7                                      | I/O         | ST             | Synchronous Serial Clock Input/Output for SPI2 |  |  |  |

| SDI2                 | PPS                                   | PPS                                   | PPS                                     | 0           |                | SPI2 Data In                                   |  |  |  |

| SDO2                 | PPS                                   | PPS                                   | PPS                                     | I/O         | ST             | SPI2 Data Out                                  |  |  |  |

| SS2                  | PPS                                   | PPS                                   | PPS                                     | I/O         | —              | SPI2 Slave Synchronization for Frame Pulse I/O |  |  |  |

| SCL1                 |                                       |                                       | B31 <sup>(1)</sup> , B36 <sup>(2)</sup> | I/O         | ST             | Synchronous Serial Clock Input/Output for I2C1 |  |  |  |

| SDA1                 | 36 <sup>(1)</sup> , 43 <sup>(2)</sup> | 56 <sup>(1)</sup> , 67 <sup>(2)</sup> | A38 <sup>(1)</sup> , A44 <sup>(2)</sup> | I/O         | ST             | Synchronous Serial Data Input/Output for I2C1  |  |  |  |

| SCL2                 | 32                                    | 58                                    | A39                                     | I/O         | ST             | Synchronous Serial Clock Input/Output for I2C2 |  |  |  |

| SDA2                 | 31                                    | 59                                    | B32                                     | I/O         | ST             | Synchronous Serial Data Input/Output for I2C2  |  |  |  |

| TMS                  | 23                                    | 17                                    | B9                                      |             | ST             | JTAG Test Mode Select Pin                      |  |  |  |

| ТСК                  | 27                                    | 38                                    | A26                                     | I           | ST             | JTAG Test Clock Input Pin                      |  |  |  |

| TDI                  | 28                                    | 60                                    | A40                                     | I           | _              | JTAG Test Clock Input Pin                      |  |  |  |

| TDO                  | 24                                    | 61                                    | B33                                     | 0           | —              | JTAG Test Clock Output Pin                     |  |  |  |

| RTCC                 | 42                                    | 68                                    | B37                                     | 0           | —              | Real-Time Clock Alarm Output                   |  |  |  |

ST = Schmitt Trigger input with CMOS levels

O = Output

I = Input

TTL = TTL input buffer

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices.

# PIC32MX330/350/370/430/450/470

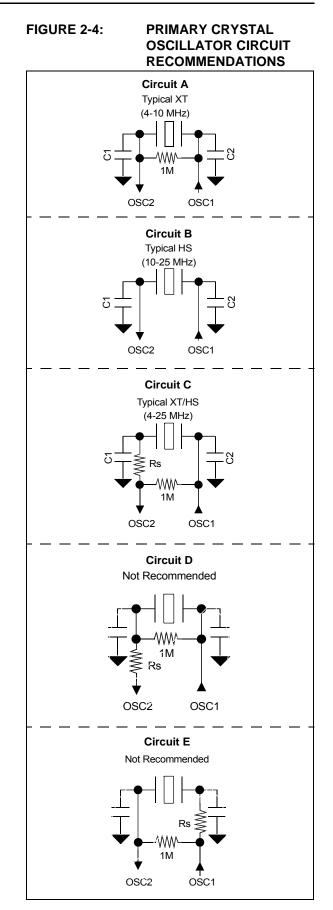

# 2.8.1 CRYSTAL OSCILLATOR DESIGN CONSIDERATION

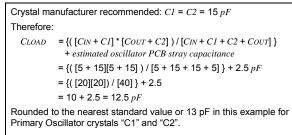

The following example assumptions are used to calculate the Primary Oscillator loading capacitor values:

- CIN = PIC32\_OSC2\_Pin Capacitance = ~4-5 pF

- COUT = PIC32\_OSC1\_Pin Capacitance = ~4-5 pF

- C1 and C2 = XTAL manufacturing recommended loading capacitance

- Estimated PCB stray capacitance, (i.e.,12 mm length) = 2.5 pF

## EXAMPLE 2-1: CRYSTAL LOAD CAPACITOR CALCULATION

The following tips are used to increase oscillator gain, (i.e., to increase peak-to-peak oscillator signal):

- Select a crystal with a lower "minimum" power drive rating

- Select an crystal oscillator with a lower XTAL manufacturing "ESR" rating.

- Add a parallel resistor across the crystal. The smaller the resistor value the greater the gain. It is recommended to stay in the range of 600k to 1M

- C1 and C2 values also affect the gain of the oscillator. The lower the values, the higher the gain.

- C2/C1 ratio also affects gain. To increase the gain, make C1 slightly smaller than C2, which will also help start-up performance.

- Note: Do not add excessive gain such that the oscillator signal is clipped, flat on top of the sine wave. If so, you need to reduce the gain or add a series resistor, RS, as shown in circuit "C" in Figure 2-4. Failure to do so will stress and age the crystal, which can result in an early failure. Adjust the gain to trim the max peak-to-peak to ~VDD-0.6V. When measuring the oscillator signal you must use a FET scope probe or a probe with ≤ 1.5 pF or the scope probe itself will unduly change the gain and peak-to-peak levels.

#### 2.8.1.1 Additional Microchip References

- AN588 "PICmicro<sup>®</sup> Microcontroller Oscillator Design Guide"

- AN826 "Crystal Oscillator Basics and Crystal Selection for rfPIC<sup>™</sup> and PICmicro<sup>®</sup> Devices"

- AN849 "Basic PICmicro<sup>®</sup> Oscillator Design"

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0 U-0           |                  | U-0              |  |  |  |  |  |

| 31:24        |                   | _                 | _                 | —                 | _                 | —                 |                  | —                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | _                 | —                 | —                 | —                 |                   | —                 | —                | —                |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |  |  |

| 15:8         | BMXDUPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |

| 7:0          |                   |                   |                   | BMXDU             | PBA<7:0>          |                   |                  |                  |  |  |  |  |  |

## REGISTER 4-4: BMXDUPBA: DATA RAM USER PROGRAM BASE ADDRESS REGISTER

## Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUPBA<15:10>: DRM User Program Base Address bits

When non-zero, the value selects the relative base address for User mode program space in RAM, BMXDUPBA must be greater than BMXDUDBA.

bit 9-0 BMXDUPBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

# 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/ 470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Memory" (DS60001121), Program which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX330/350/370/430/450/470 devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: On PIC32MX330/350/370/430/450/470 devices, the Flash page size is 4 KB and the row size is 512 bytes (1024 IW and 128 IW, respectively).

# PIC32MX330/350/370/430/450/470

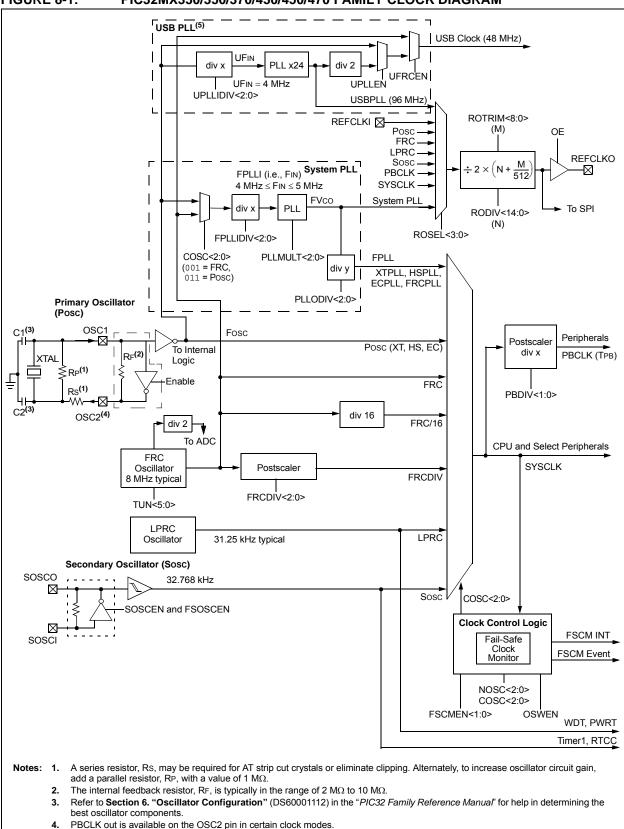

#### FIGURE 8-1: PIC32MX330/350/370/430/450/470 FAMILY CLOCK DIAGRAM

5. USB PLL is available on PIC32MX4XX devices only.

## REGISTER 10-4: DCRCCON: DMA CRC CONTROL REGISTER (CONTINUED)

bit 6 **CRCAPP:** CRC Append Mode bit<sup>(1)</sup>

- 1 = The DMA transfers data from the source into the CRC but NOT to the destination. When a block transfer completes the DMA writes the calculated CRC value to the location given by CHxDSA

- 0 = The DMA transfers data from the source through the CRC obeying WBO as it writes the data to the destination

- bit 5 **CRCTYP:** CRC Type Selection bit

- 1 = The CRC module will calculate an IP header checksum

- 0 = The CRC module will calculate a LFSR CRC

- bit 4-3 Unimplemented: Read as '0'

- bit 2-0 CRCCH<2:0>: CRC Channel Select bits

- 111 = CRC is assigned to Channel 7

- 110 = CRC is assigned to Channel 6

- 101 = CRC is assigned to Channel 5

- 100 = CRC is assigned to Channel 4

- 011 = CRC is assigned to Channel 3

- 010 = CRC is assigned to Channel 2

- 001 = CRC is assigned to Channel 1

- 000 = CRC is assigned to Channel 0

- **Note 1:** When WBO = 1, unaligned transfers are not supported and the CRCAPP bit cannot be set.

| Bit<br>Range      Bit<br>31/23/15/7        31:24      U-0         U-0 |         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1                                                                                                                                                               | Bit<br>24/16/8/0 |

|-----------------------------------------------------------------------|---------|-------------------|-------------------|-------------------|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|

| 21.24                                                                 | U-0     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                                                                                                                                                                            | U-0              |

| 31:24 -                                                               |         |                   |                   |                   |                   | —                 | _                                                                                                                                                                              | _                |

| 23:16                                                                 | U-0     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                                                                                                                                                                            | U-0              |

| 23.10                                                                 |         |                   |                   |                   |                   | —                 | /2      25/17/9/1      24/16/8        U-0      U-0        U-0      U-0        U-0      U-0        U-0      U-0        U-0      U-0        U-0      U-0        R/W-0      R/W-0 | _                |

| 15:8                                                                  | U-0     | U-0               | U-0               | U-0               | U-0               | U-0               | U-0                                                                                                                                                                            | U-0              |

| 15.0                                                                  | -       | -                 | —                 | —                 | -                 | —                 | —                                                                                                                                                                              | _                |

| 7:0                                                                   | R/W-0   | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0                                                                                                                                                                          | R/W-0            |

| 7:0                                                                   | DPPULUP | DMPULUP           | DPPULDWN          | DMPULDWN          | VBUSON            | OTGEN             | VBUSCHG                                                                                                                                                                        | VBUSDIS          |

## REGISTER 11-4: U10TGCON: USB OTG CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

| bit 7 | DPPULUP: D+ Pull-Up Enable bit |

|-------|--------------------------------|

|       |                                |

- 1 = D+ data line pull-up resistor is enabled

- 0 = D+ data line pull-up resistor is disabled

#### bit 6 **DMPULUP:** D- Pull-Up Enable bit

- 1 = D- data line pull-up resistor is enabled

- 0 = D- data line pull-up resistor is disabled

## bit 5 **DPPULDWN:** D+ Pull-Down Enable bit

- 1 = D+ data line pull-down resistor is enabled

- 0 = D+ data line pull-down resistor is disabled

#### bit 4 DMPULDWN: D- Pull-Down Enable bit

- 1 = D- data line pull-down resistor is enabled

- 0 = D- data line pull-down resistor is disabled

- bit 3 **VBUSON:** VBUS Power-on bit

- 1 = VBUS line is powered

- 0 = VBUS line is not powered

- bit 2 OTGEN: OTG Functionality Enable bit

- 1 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under software control

- 0 = DPPULUP, DMPULUP, DPPULDWN and DMPULDWN bits are under USB hardware control

#### bit 1 VBUSCHG: VBUS Charge Enable bit

- 1 = VBUS line is charged through a pull-up resistor

- 0 = VBUS line is not charged through a resistor

#### bit 0 VBUSDIS: VBUS Discharge Enable bit

- 1 = VBUS line is discharged through a pull-down resistor

- 0 = VBUS line is not discharged through a resistor

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1       | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|----------------------|----------------------|-------------------|-------------------|------------------------|------------------|--|--|--|--|

| 21.24        | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |  |

| 31:24        | -                 | -                 | -                    | -                    | —                 |                   | —                      |                  |  |  |  |  |

| 23:16        | U-0               | U-0 U-0           |                      | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |  |

| 23.10        | -                 |                   | -                    |                      |                   |                   | —                      |                  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0                  | U-0                  | U-0               | U-0               | U-0                    | U-0              |  |  |  |  |

| 15.6         | -                 | -                 | -                    | -                    | —                 | —                 | —                      | -                |  |  |  |  |

|              | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS           | R/WC-0, HS        | R/WC-0, HS        | R/WC-0, HS             | R/WC-0, HS       |  |  |  |  |

| 7:0          | BTSEF             | BMXEF             | DMAEF <sup>(1)</sup> | BTOEF <sup>(2)</sup> | DFN8EF            | CRC16EF           | CRC5EF <sup>(4)</sup>  | PIDEF            |  |  |  |  |

|              | DISEF             | DIVIAEF           | DIVIAEL, ,           | BIVEF                | DENOER            | GRUIDEF           | EOFEF <sup>(3,5)</sup> |                  |  |  |  |  |

## REGISTER 11-8: U1EIR: USB ERROR INTERRUPT STATUS REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable b               | it                 |

|-------------------|-------------------------|----------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit        | bit U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared                   | x = Bit is unknown |

#### bit 31-8 Unimplemented: Read as '0'

- bit 7 BTSEF: Bit Stuff Error Flag bit

- 1 = Packet is rejected due to bit stuff error

- 0 = Packet is accepted

- bit 6 BMXEF: Bus Matrix Error Flag bit

1 = The base address, of the BDT, or the address of an individual buffer pointed to by a BDT entry, is invalid.

0 = No address error

- bit 5 **DMAEF:** DMA Error Flag bit<sup>(1)</sup> 1 = USB DMA error condition detected

- 0 = No DMA error

- bit 4 **BTOEF:** Bus Turnaround Time-Out Error Flag bit<sup>(2)</sup>

- 1 = Bus turnaround time-out has occurred

- 0 = No bus turnaround time-out

#### bit 3 **DFN8EF:** Data Field Size Error Flag bit

- 1 = Data field received is not an integral number of bytes

- 0 = Data field received is an integral number of bytes

#### bit 2 CRC16EF: CRC16 Failure Flag bit

- 1 = Data packet rejected due to CRC16 error

- 0 = Data packet accepted

- **Note 1:** This type of error occurs when the module's request for the DMA bus is not granted in time to service the module's demand for memory, resulting in an overflow or underflow condition, and/or the allocated buffer size is not sufficient to store the received data packet causing it to be truncated.

- **2:** This type of error occurs when more than 16-bit-times of Idle from the previous End-of-Packet (EOP) has elapsed.

- **3:** This type of error occurs when the module is transmitting or receiving data and the SOF counter has reached zero.

- 4: Device mode.

- 5: Host mode.

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Periphera<br>Selection |

|----------------------|----------|-------------|--------------------------------------|

| RPD2                 | RPD2R    | RPD2R<3:0>  | 0000 = No Connect                    |

| RPG8                 | RPG8R    | RPG8R<3:0>  | 0001 = U3TX                          |

| RPF4                 | RPF4R    | RPF4R<3:0>  | 0010 = U4RTS<br>0011 = Reserved      |

| RPD10                | RPD10R   | RPD10R<3:0> | 0100 = Reserved                      |

| RPF1                 | RPF1R    | RPF1R<3:0>  | 0101 = Reserved                      |

| RPB9                 | RPB9R    | RPB9R<3:0>  | 0110 = SDO2                          |

| RPB10                | RPB10R   | RPB10R<3:0> | 0111 = Reserved<br>1000 = Reserved   |

| RPC14                | RPC14R   | RPC14R<3:0> | 1000 = Reserved                      |

| RPB5                 | RPB5R    | RPB5R<3:0>  | 1010 = Reserved                      |

| RPC1 <sup>(4)</sup>  | RPC1R    | RPC1R<3:0>  | 1011 <b>= OC3</b>                    |

| RPD14 <sup>(4)</sup> | RPD14R   | RPD14R<3:0> | 1100 = Reserved<br>1101 = C2OUT      |

| RPG1 <sup>(4)</sup>  | RPG1R    | RPG1R<3:0>  | 1110 = Reserved                      |

| RPA14 <sup>(4)</sup> | RPA14R   | RPA14R<3:0> | 1111 = Reserved                      |

| RPD3                 | RPD3R    | RPD3R<3:0>  | 0000 = No Connect                    |

| RPG7                 | RPG7R    | RPG7R<3:0>  | 0001 = U2TX                          |

| RPF5                 | RPF5R    | RPF5R<3:0>  | 0010 = Reserved                      |

| RPD11                | RPD11R   | RPD11R<3:0> |                                      |

| RPF0                 | RPF0R    | RPF0R<3:0>  | 0100 = 05RTS(*)                      |

| RPB1                 | RPB1R    | RPB1R<3:0>  | 0110 = SDO2                          |

| RPE5                 | RPE5R    | RPE5R<3:0>  | 0111 = Reserved                      |

| RPC13                | RPC13R   | RPC13R<3:0> | 1000 <b>= SDO1</b>                   |

| RPB3                 | RPB3R    | RPB3R<3:0>  | 1001 = Reserved                      |

| RPF3 <sup>(2)</sup>  | RPF3R    | RPF3R<3:0>  | 1010 = Reserved                      |

| RPC4 <sup>(4)</sup>  | RPC4R    | RPC4R<3:0>  | 1011 = OC4<br>1100 = Reserved        |

| RPD15 <sup>(4)</sup> | RPD15R   | RPD15R<3:0> | 1100 - Reserved                      |

| RPG0 <sup>(4)</sup>  | RPG0R    | RPG0R<3:0>  | 1110 = Reserved                      |

| RPA15 <sup>(4)</sup> | RPA15R   | RPA15R<3:0> | 1111 = Reserved                      |

## TABLE 12-2: OUTPUT PIN SELECTION

Note 1: This selection is only available on General Purpose devices.

**2:** This selection is only available on 64-pin General Purpose devices.

3: This selection is only available on 100-pin General Purpose devices.

4: This selection is only available on 100-pin USB and General Purpose devices.

5: This selection is not available on 64-pin USB devices.

#### TABLE 12-10: PORTE REGISTER MAP FOR PIC32MX330F064H, PIC32MX350F128H, PIC32MX350F256H, PIC32MX370F512H, PIC32MX430F064H, PIC32MX450F128H, PIC32MX450F256H, AND PIC32MX470F512H DEVICES ONLY

| ess                         |                                 |           |       |       |       |       |       |       |      | E       | Bits         |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|---------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8    | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Decete |

| 6400                        | ANSELE                          | 31:16     | _     | -     | -     | —     | _     | -     | -    | -       | —            | _            | _            | -            | _            | —            | —            |              | 000           |

| 0400 ANGLEL                 | 15:0                            | —         | _     | _     | —     | —     | _     | _     | _    | ANSELE7 | ANSELE6      | ANSELE5      | ANSELE4      | —            | ANSELE2      | —            | _            | 00F          |               |

| 6410                        | TRISE                           | 31:16     | —     | —     | —     | —     | _     | —     | —    | —       | —            | —            | —            | —            | -            | —            | —            | _            | 000           |

| 0110                        | HUGE                            | 15:0      | —     | _     | _     | —     | —     | _     | _    | _       | TRISE7       | TRISE6       | TRISE5       | TRISE4       | TRISE3       | TRISE2       | TRISE1       | TRISE0       | xxx           |

| 6420                        | PORTE                           | 31:16     | —     | _     | _     | —     | —     | _     | _    | _       | —            | —            | —            | —            | —            | —            | —            | —            | 000           |

| 0120                        | TORIE                           | 15:0      | —     | _     | _     | —     | —     | _     | _    | _       | RE7          | RE6          | RE5          | RE4          | RE3          | RE2          | RE1          | RE0          | XXX           |

| 6440                        | LATE                            | 31:16     | —     | _     | _     | —     | —     | _     | _    | _       | —            | —            | —            | —            | —            | —            | —            | —            | 000           |

|                             |                                 | 15:0      | —     | _     | _     | —     | —     | _     | _    | _       | LATE7        | LATE6        | LATE5        | LATE4        | LATE3        | LATE2        | LATE1        | LATE0        | XXX           |

| 6440                        | ODCE                            | 31:16     | —     | —     | _     | —     | _     | —     | —    | —       | —            | —            | —            | —            | _            | —            | —            | —            | 000           |

| 00                          |                                 | 15:0      | —     | -     | _     | —     | -     | _     | _    | _       | ODCE7        | ODCE6        | ODCE5        | ODCE4        | ODCE3        | ODCE2        | ODCE1        | ODCE0        | xxx           |

| 6450                        | CNPUE                           | 31:16     | —     | -     | _     | —     | -     | _     | _    | _       | —            | —            | —            | —            | -            | —            | —            | —            | 000           |

| 0.00                        | 0.11 02                         | 15:0      | —     | -     | _     | —     | -     | _     | _    | _       | CNPUE7       | CNPUE6       | CNPUE5       | CNPUE4       | CNPDE3       | CNPUE2       | CNPUE1       | CNPUE0       | xxx           |

| 6460                        | CNPDE                           | 31:16     | —     | -     | _     | —     | -     | _     | _    | _       | —            | —            | —            | —            | -            | —            | —            | —            | 000           |

| 0.00                        | 0.11.02                         | 15:0      | —     | -     | _     | —     | -     | _     | _    | _       | CNPDE7       | CNPDE6       | CNPDE5       | CNPDE4       | CNPDE3       | CNPDE2       | CNPDE1       | CNPDE0       | _             |

| 6470                        | CNCONE                          | 31:16     | —     | -     | -     | —     | -     | _     | _    | _       | —            | —            | —            | —            | -            | —            | —            | —            | 000           |

| 00                          | 0.100112                        | 15:0      | ON    | -     | SIDL  | —     | -     | _     | _    | _       | —            | —            | —            | —            | -            | —            | —            | —            | 000           |

| 6480                        | CNENE                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _       | —            | —            | —            | —            | —            | —            | —            | —            | 000           |

|                             |                                 | 15:0      | _     | —     | _     | _     | —     | _     | _    | _       | CNIEE7       | CNIEE6       | CNIEE5       | CNIEE4       | CNIEE3       | CNIEE2       | CNIEE1       | CNIEE0       | xxx           |

|                             |                                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _       | —            | —            | —            | —            | —            | —            | —            | —            | 000           |

| 6490                        | CNSTATE                         | 15:0      | —     | —     | —     | —     | _     | _     | —    | _       | CN<br>STATE7 | CN<br>STATE6 | CN<br>STATE5 | CN<br>STATE4 | CN<br>STATE3 | CN<br>STATE2 | CN<br>STATE1 | CN<br>STATE0 | xxx           |

All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 |                   | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 |                   |                   | _                 | _                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | _                 | _                | —                |

| 7.0          | R/W-0             | U-0               | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             |                   | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

## REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

| Unimplemented: Read as 0                                                                                                                                                       |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ON: Timer On bit <sup>(1)</sup>                                                                                                                                                |

| 1 = Timer is enabled                                                                                                                                                           |

| 0 = Timer is disabled                                                                                                                                                          |

| Unimplemented: Read as '0'                                                                                                                                                     |

| SIDL: Stop in Idle Mode bit                                                                                                                                                    |

| <ul><li>1 = Discontinue operation when device enters Idle mode</li><li>0 = Continue operation even in Idle mode</li></ul>                                                      |

| TWDIS: Asynchronous Timer Write Disable bit                                                                                                                                    |

| <ul><li>1 = Writes to TMR1 are ignored until pending write operation completes</li><li>0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)</li></ul> |

| TWIP: Asynchronous Timer Write in Progress bit                                                                                                                                 |

| In Asynchronous Timer mode:                                                                                                                                                    |

| <ul><li>1 = Asynchronous write to TMR1 register in progress</li><li>0 = Asynchronous write to TMR1 register complete</li></ul>                                                 |

| In Synchronous Timer mode:<br>This bit is read as '0'                                                                                                                          |

| Unimplemented: Read as '0'                                                                                                                                                     |

| <b>TGATE:</b> Timer Gated Time Accumulation Enable bit                                                                                                                         |

| When $TCS = 1$ :                                                                                                                                                               |

| This bit is ignored.                                                                                                                                                           |

| When TCS = 0:                                                                                                                                                                  |

| 1 = Gated time accumulation is enabled                                                                                                                                         |

| 0 = Gated time accumulation is disabled                                                                                                                                        |

| Unimplemented: Read as '0'                                                                                                                                                     |

| TCKPS<1:0>: Timer Input Clock Prescale Select bits                                                                                                                             |

| 11 = 1:256 prescale value<br>10 = 1:64 prescale value                                                                                                                          |

| 01 = 1:8 prescale value                                                                                                                                                        |

| 00 = 1:1 prescale value                                                                                                                                                        |

| Unimplemented: Read as '0'                                                                                                                                                     |

|                                                                                                                                                                                |

|                                                                                                                                                                                |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| REGIST    | ER 18-1:                   | SPIxCON: S                    | SPI CONTROL REGISTER (CONTINUED)                                                                                                                               |

|-----------|----------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 17    |                            |                               | e Edge Select bit (Framed SPI mode only)                                                                                                                       |

|           |                            |                               | on pulse coincides with the first bit clock                                                                                                                    |

| h:+ 40    |                            |                               | on pulse precedes the first bit clock<br>fer Enable bit <sup>(2)</sup>                                                                                         |

| bit 16    |                            | ed Buffer mo                  |                                                                                                                                                                |

|           |                            | ed Buffer mod                 |                                                                                                                                                                |

| bit 15    |                            | ripheral On bi                |                                                                                                                                                                |

|           |                            | ripheral is ena               |                                                                                                                                                                |

|           |                            | ripheral is dis               |                                                                                                                                                                |

| bit 14    | Unimpleme                  | ented: Read a                 | as '0'                                                                                                                                                         |

| bit 13    | SIDL: Stop                 | in Idle Mode b                | pit                                                                                                                                                            |

|           |                            | •                             | n when CPU enters in Idle mode                                                                                                                                 |

|           |                            | ue operation i                |                                                                                                                                                                |

| bit 12    |                            | isable SDOx                   |                                                                                                                                                                |

|           |                            |                               | d by the module. Pin is controlled by associated PORT register<br>ed by the module                                                                             |

| bit 11-10 |                            |                               | t Communication Select bits                                                                                                                                    |

|           | When AUD                   |                               | Communication Select bits                                                                                                                                      |

|           | MODE32                     | MODE16                        | Communication                                                                                                                                                  |

|           | 1                          | 1                             | 24-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                          |

|           | 1                          | 0                             | 32-bit Data, 32-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                          |

|           | 0                          | 1                             | 16-bit Data, 16-bit FIFO, 32-bit Channel/64-bit Frame                                                                                                          |

|           | 0                          | 0                             | 16-bit Data, 16-bit FIFO, 16-bit Channel/32-bit Frame                                                                                                          |

|           | When AUD                   | EN = 0:                       |                                                                                                                                                                |

|           | MODE32                     | MODE16                        | Communication                                                                                                                                                  |

|           | 1                          | x                             | 32-bit                                                                                                                                                         |

|           | 0                          | 1                             | 16-bit                                                                                                                                                         |

|           | 0                          | 0                             | 8-bit                                                                                                                                                          |

| bit 9     |                            | 0ata Input Sar<br>le (MSTEN = | nple Phase bit                                                                                                                                                 |

|           |                            |                               | $\pm$ ).<br>at end of data output time                                                                                                                         |

|           |                            |                               | at middle of data output time                                                                                                                                  |

|           | Slave mode                 | e (MSTEN = 0                  | <u>):</u>                                                                                                                                                      |

|           |                            | -                             | en SPI is used in Slave mode. The module always uses SMP = $0.$                                                                                                |

| bit 8     |                            | lock Edge Se                  |                                                                                                                                                                |

|           |                            |                               | anges on transition from active clock state to Idle clock state (see CKP bit)<br>anges on transition from Idle clock state to active clock state (see CKP bit) |

| bit 7     |                            | -                             | ble (Slave mode) bit                                                                                                                                           |

|           |                            | n used for Sla                |                                                                                                                                                                |

|           |                            |                               | Slave mode, pin controlled by port function.                                                                                                                   |

| bit 6     |                            | Polarity Sele                 |                                                                                                                                                                |

|           | 1 = Idle sta               | te for clock is               | a high level; active state is a low level                                                                                                                      |

|           |                            |                               | a low level; active state is a high level                                                                                                                      |

| bit 5     |                            | aster Mode Er                 | hable bit                                                                                                                                                      |

|           | 1 = Master<br>0 = Slave r  |                               |                                                                                                                                                                |

|           |                            | lieue                         |                                                                                                                                                                |

| Note 1:   | When using                 | g the 1:1 PBC                 | LK divisor, the user software should not read or write the peripheral's SFRs in the                                                                            |

|           |                            | -                             | ely following the instruction that clears the module's ON bit.                                                                                                 |

| 2:        | This bit car               | n only be writte              | en when the ON bit = 0.                                                                                                                                        |

| 3:        | This bit is r<br>mode (FRN |                               | e Framed SPI mode. The user should program this bit to '0' for the Framed SPI                                                                                  |

| 4:        | -                          | -                             | PI module functions as if the CKP bit is equal to '1', regardless of the actual value                                                                          |

|           | of CKP.                    | <u> </u>                      |                                                                                                                                                                |

|           |                            |                               |                                                                                                                                                                |

## REGISTER 18-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)

- bit 4 **DISSDI:** Disable SDI bit 1 = SDI pin is not used by the SPI module (pin is controlled by PORT function)

- 0 = SDI pin is controlled by the SPI module

- bit 3-2 STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

|              | -                 | -                 |                   |                   |                   |                   |                  | /                |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | —                | —                |

| 22:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | —                 | _                 | -                 | —                 | _                 | _                 | —                | —                |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | _                 | —                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              |                   | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

#### REGISTER 21-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Legend:           | HS = Set by Hardware | SC = Cleared by software  |                    |

|-------------------|----------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 IBF: Input Buffer Full Status bit

- 1 = All writable input buffer registers are full

- 0 = Some or all of the writable input buffer registers are empty

- bit 14 IBOV: Input Buffer Overflow Status bit

- 1 = A write attempt to a full input byte buffer occurred (must be cleared in software)0 = No overflow occurred

- bit 13-12 Unimplemented: Read as '0'

- bit 11-8 **IBxF:** Input Buffer 'x' Status Full bits

- 1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

- 0 = Input Buffer does not contain any unread data

- bit 7 **OBE:** Output Buffer Empty Status bit

- 1 = All readable output buffer registers are empty

- 0 = Some or all of the readable output buffer registers are full

- bit 6 **OBUF:** Output Buffer Underflow Status bit

- 1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

- bit 5-4 Unimplemented: Read as '0'

- bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

- 1 = Output buffer is empty (writing data to the buffer will clear this bit)

- 0 = Output buffer contains data that has not been transmitted

## TABLE 23-1: ADC REGISTER MAP (CONTINUED)

| ess                         |                  | 0             |       |                                    |       |       |       |       |         | В          | its      |          |      |      |      |      |      |      | ŝ          |

|-----------------------------|------------------|---------------|-------|------------------------------------|-------|-------|-------|-------|---------|------------|----------|----------|------|------|------|------|------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14                              | 29/13 | 28/12 | 27/11 | 26/10 | 25/9    | 24/8       | 23/7     | 22/6     | 21/5 | 20/4 | 19/3 | 18/2 | 17/1 | 16/0 | All Resets |

| 9110                        | ADC1BUFA         | 31:16<br>15:0 |       |                                    |       |       |       |       | ADC Res | ult Word A | (ADC1BUF | A<31:0>) |      |      |      |      |      |      | 0000       |

| 9120                        | ADC1BUFB         | 31:16<br>15:0 |       | ADC Result Word B (ADC1BUFB<31:0>) |       |       |       |       |         |            |          |          |      | 0000 |      |      |      |      |            |

| 9130                        | ADC1BUFC         | 31:16<br>15:0 |       |                                    |       |       |       |       | ADC Res | ult Word C | (ADC1BUF | C<31:0>) |      |      |      |      |      |      | 0000       |

| 9140                        | ADC1BUFD         | 31:16<br>15:0 |       |                                    |       |       |       |       | ADC Res | ult Word D | (ADC1BUF | D<31:0>) |      |      |      |      |      |      | 0000       |

| 9150                        | ADC1BUFE         | 31:16<br>15:0 |       | ADC Result Word E (ADC1BUFE<31:0>) |       |       |       |       |         |            |          |          |      | 0000 |      |      |      |      |            |

| 9160                        | ADC1BUFF         | 31:16<br>15:0 |       |                                    |       |       |       |       | ADC Res | ult Word F | (ADC1BUF | F<31:0>) |      |      |      |      |      |      | 0000       |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for details.

## TABLE 28-1: DEVCFG: DEVICE CONFIGURATION WORD SUMMARY

| ess                        |                  |           |                       |          |         |          |       |          |           | Bits     |        |        |           |       |        |           |              |       | s         |

|----------------------------|------------------|-----------|-----------------------|----------|---------|----------|-------|----------|-----------|----------|--------|--------|-----------|-------|--------|-----------|--------------|-------|-----------|

| Virtual Addres<br>(BFC0_#) | Register<br>Name | Bit Range | 31/15                 | 30/14    | 29/13   | 28/12    | 27/11 | 26/10    | 25/9      | 24/8     | 23/7   | 22/6   | 21/5      | 20/4  | 19/3   | 18/2      | 17/1         | 16/0  | All Reset |

| 2550                       | DEVCFG3          | 31:16     | FVBUSONIO             | FUSBIDIO | IOL1WAY | PMDL1WAY | _     | _        | _         |          | —      |        | _         |       | —      | FS        | RSSEL<2:0    | >     | xxxx      |

| 2660                       | DEVCEGS          | 15:0      |                       |          |         |          |       |          |           | USERID<1 | 5:0>   |        |           |       |        |           |              |       | xxxx      |

| 2554                       | DEVCFG2          | 31:16     | —                     | —        |         | —        | —     | —        | —         |          | —      |        | —         |       | -      | FP        | LLODIV<2:0   | >     | xxxx      |

| 2664                       | DEVCFGZ          | 15:0      | UPLLEN <sup>(1)</sup> | —        |         | _        | —     | UPL      | LIDIV<2:0 | (1)      | —      | FF     | PLLMUL<2: | 0>    | —      | FF        | PLLIDIV<2:0> | >     | xxxx      |

| 2550                       | DEVCFG1          | 31:16     | —                     | _        | _       | —        | _     | _        | FWDTWI    | NSZ<1:0> | FWDTEN | WINDIS | _         |       | ١      | NDTPS<4:0 | )>           |       | xxxx      |

| 2660                       | DEVCEGI          | 15:0      | FCKSM                 | <1:0>    | FPBD    | IV<1:0>  | _     | OSCIOFNC | POSCM     | OD<1:0>  | IESO   | _      | FSOSCEN   | —     | _      | F         | NOSC<2:0>    |       | xxxx      |

| 2550                       | DEVCFG0          | 31:16     | —                     | —        | _       | CP       | —     | _        | —         | BWP      | _      |        | _         |       |        | PWP       | <7:4>        |       | xxxx      |

| 2650                       | DEVCEGO          | 15:0      |                       | PWP<     | <3:0>   |          | —     | —        |           | -        | —      | _      | —         | ICESE | L<1:0> | JTAGEN    | DEBUG        | <1:0> | xxxx      |

Legend: x = unknown value on Reset; - = reserved, write as '1'. Reset values are shown in hexadecimal.

**Note 1:** This bit is only available on devices with a USB module.

## TABLE 28-2: DEVICE ID, REVISION, AND CONFIGURATION SUMMARY

| ess                         |                  | e         |                 |       |        |         |       |       |      | Bi    | ts      |       |         |                     |        |       |      |       | ú                   |

|-----------------------------|------------------|-----------|-----------------|-------|--------|---------|-------|-------|------|-------|---------|-------|---------|---------------------|--------|-------|------|-------|---------------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range | 31/15           | 30/14 | 29/13  | 28/12   | 27/11 | 26/10 | 25/9 | 24/8  | 23/7    | 22/6  | 21/5    | 20/4                | 19/3   | 18/2  | 17/1 | 16/0  | All Resets          |

| 5000                        |                  | 31:16     | _               | _     | —      | —       | _     | —     | —    | _     | —       | _     | —       | _                   | —      | _     | _    | —     | 0000                |

| F200                        | CFGCON           | 15:0      | _               | —     | IOLOCK | PMDLOCK | _     | _     | —    | —     | —       | —     | —       | _                   | JTAGEN | TROEN | _    | TDOEN | 000B                |

| F220                        | DEVID            | 31:16     |                 | VER   | <3:0>  |         |       |       |      |       |         | DEVID | <27:16> |                     |        |       |      |       | xxxx <sup>(1)</sup> |

| F220                        | DEVID            | 15:0      | DEVID<15:0> xxx |       |        |         |       |       |      |       |         |       |         | xxxx <sup>(1)</sup> |        |       |      |       |                     |

| E220                        | SYSKEY           | 31:16     | 1:16            |       |        |         |       |       |      |       |         |       |         | 0000                |        |       |      |       |                     |

| F230                        | STORET           | 15:0      |                 |       |        |         |       |       |      | STORE | 1~51.0~ |       |         |                     |        |       |      |       | 0000                |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

**Note 1:** Reset values are dependent on the device variant.

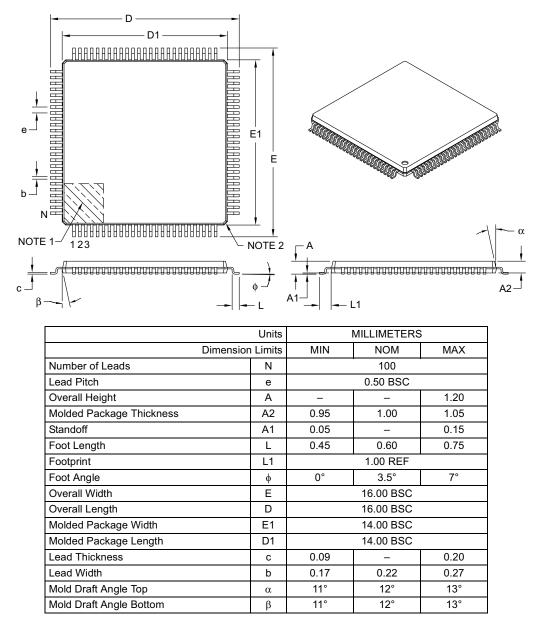

## 100-Lead Plastic Thin Quad Flatpack (PF) – 14x14x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Chamfers at corners are optional; size may vary.

3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-110B

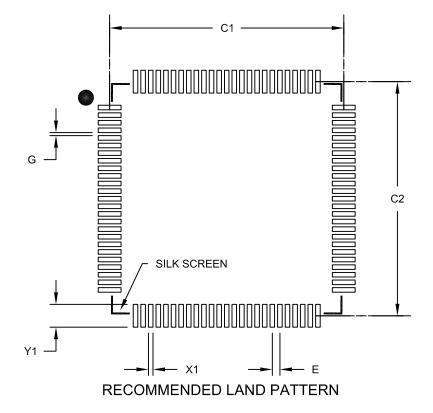

100-Lead Plastic Thin Quad Flatpack (PF) - 14x14x1 mm Body 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |      |          |      |  |  |  |

|---------------------------|-------------|------|----------|------|--|--|--|

| Dimensior                 | l Limits    | MIN  | NOM      | MAX  |  |  |  |

| Contact Pitch             | E           |      | 0.50 BSC | -    |  |  |  |

| Contact Pad Spacing       | C1          |      | 15.40    |      |  |  |  |

| Contact Pad Spacing       | C2          |      | 15.40    |      |  |  |  |

| Contact Pad Width (X100)  | X1          |      |          | 0.30 |  |  |  |

| Contact Pad Length (X100) | Y1          |      |          | 1.50 |  |  |  |

| Distance Between Pads     | G           | 0.20 |          |      |  |  |  |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2110B

# THE MICROCHIP WEB SITE

Microchip provides online support via our WWW site at www.microchip.com. This web site is used as a means to make files and information easily available to customers. Accessible by using your favorite Internet browser, the web site contains the following information:

- Product Support Data sheets and errata, application notes and sample programs, design resources, user's guides and hardware support documents, latest software releases and archived software

- General Technical Support Frequently Asked Questions (FAQ), technical support requests, online discussion groups, Microchip consultant program member listing

- Business of Microchip Product selector and ordering guides, latest Microchip press releases, listing of seminars and events, listings of Microchip sales offices, distributors and factory representatives

# CUSTOMER CHANGE NOTIFICATION SERVICE

Microchip's customer notification service helps keep customers current on Microchip products. Subscribers will receive e-mail notification whenever there are changes, updates, revisions or errata related to a specified product family or development tool of interest.

To register, access the Microchip web site at www.microchip.com. Under "Support", click on "Customer Change Notification" and follow the registration instructions.

# CUSTOMER SUPPORT

Users of Microchip products can receive assistance through several channels:

- Distributor or Representative

- Local Sales Office

- Field Application Engineer (FAE)

- Technical Support

Customers should contact their distributor, representative or Field Application Engineer (FAE) for support. Local sales offices are also available to help customers. A listing of sales offices and locations is included in the back of this document.

Technical support is available through the web site at: http://microchip.com/support