Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32 <sup>®</sup> M4K <sup>™</sup>                                            |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 49                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 128K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 64-VFQFN Exposed Pad                                                            |

| Supplier Device Package    | 64-QFN (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx470f512ht-i-mr |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

Coprocessor 0 also contains the logic for identifying and managing exceptions. Exceptions can be caused by a variety of sources, including alignment errors in data, external events or program errors. Table 3-3 lists the exception types in order of priority.

| Exception | Description                                                                                                                             |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------|

| Reset     | Assertion MCLR or a Power-on Reset (POR).                                                                                               |

| DSS       | EJTAG debug single step.                                                                                                                |

| DINT      | EJTAG debug interrupt. Caused by the assertion of the external <i>EJ_DINT</i> input or by setting the EjtagBrk bit in the ECR register. |

| NMI       | Assertion of NMI signal.                                                                                                                |

| Interrupt | Assertion of unmasked hardware or software interrupt signal.                                                                            |

| DIB       | EJTAG debug hardware instruction break matched.                                                                                         |

| AdEL      | Fetch address alignment error. Fetch reference to protected address.                                                                    |

| IBE       | Instruction fetch bus error.                                                                                                            |

| DBp       | EJTAG breakpoint (execution of SDBBP instruction).                                                                                      |

| Sys       | Execution of SYSCALL instruction.                                                                                                       |

| Вр        | Execution of BREAK instruction.                                                                                                         |

| RI        | Execution of a reserved instruction.                                                                                                    |

| CpU       | Execution of a coprocessor instruction for a coprocessor that is not enabled.                                                           |

| CEU       | Execution of a CorExtend instruction when CorExtend is not enabled.                                                                     |

| Ov        | Execution of an arithmetic instruction that overflowed.                                                                                 |

| Tr        | Execution of a trap (when trap condition is true).                                                                                      |

| DDBL/DDBS | EJTAG Data Address Break (address only) or EJTAG data value break on store (address + value).                                           |

| AdEL      | Load address alignment error. Load reference to protected address.                                                                      |

| AdES      | Store address alignment error. Store to protected address.                                                                              |

| DBE       | Load or store bus error.                                                                                                                |

| DDBL      | EJTAG data hardware breakpoint matched in load data compare.                                                                            |

# TABLE 3-3: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE EXCEPTION TYPES

# 3.3 Power Management

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core offers a number of power management features, including low-power design, active power management and power-down modes of operation. The core is a static design that supports slowing or Halting the clocks, which reduces system power consumption during Idle periods.

#### 3.3.1 INSTRUCTION-CONTROLLED POWER MANAGEMENT

The mechanism for invoking Power-Down mode is through execution of the WAIT instruction. For more information on power management, see Section 27.0 "Power-Saving Features".

### 3.3.2 LOCAL CLOCK GATING

The majority of the power consumed by the PIC32MX330/350/370/430/450/470 family core is in the clock tree and clocking registers. The PIC32MX family uses extensive use of local gated-clocks to reduce this dynamic power consumption.

# 3.4 EJTAG Debug Support

The MIPS<sup>®</sup> M4K<sup>®</sup> processor core provides for an Enhanced JTAG (EJTAG) interface for use in the software debug of application and kernel code. In addition to standard User mode and Kernel modes of operation, the M4K<sup>®</sup> core provides a Debug mode that is entered after a debug exception (derived from a hardware breakpoint, single-step exception, etc.) is taken and continues until a Debug Exception Return (DERET) instruction is executed. During this time, the processor executes the debug exception handler routine.

The EJTAG interface operates through the Test Access Port (TAP), a serial communication port used for transferring test data in and out of the core. In addition to the standard JTAG instructions, special instructions defined in the EJTAG specification define which registers are selected and how they are used.

# REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 3-0 ROSEL<3:0>: Reference Clock Source Select bits<sup>(1)</sup>

- 1111 = Reserved; do not use

- 1001 = Reserved; do not use 1000 = REFCLKI 0111 = System PLL output 0110 = USB PLL output 0101 = Sosc 0100 = LPRC 0011 = FRC 0010 = POSC 0001 = PBCLK 0000 = SYSCLK

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- 2: This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

| Bit<br>Range | Bit Bit<br>31/23/15/7 30/22/14/6 |       |       |       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |       |  |  |  |

|--------------|----------------------------------|-------|-------|-------|-------------------|------------------|------------------|-------|--|--|--|

| 31:24        | R/W-0                            | U-0   | U-0   | U-0   | U-0               | U-0              | U-0              | U-0   |  |  |  |

| 51.24        | LTAGBOOT                         | —     | —     | —     | —                 | -                | _                | —     |  |  |  |

| 23:16        | R/W-x                            | R/W-x | R/W-x | R/W-x | R/W-x             | R/W-x            | R/W-x            | R/W-x |  |  |  |

| 23.10        | LTAG<19:12>                      |       |       |       |                   |                  |                  |       |  |  |  |

| 15:0         | R/W-x                            | R/W-x | R/W-x | R/W-x | R/W-x             | R/W-x            | R/W-x            | R/W-x |  |  |  |

| 15:8         | LTAG<11:4>                       |       |       |       |                   |                  |                  |       |  |  |  |

| 7:0          | R/W-x                            | R/W-x | R/W-x | R/W-x | R/W-0             | R/W-0            | R/W-1            | U-0   |  |  |  |

| 7.0          |                                  | LTAG< | <3:0> |       | LVALID            | LLOCK            | LTYPE            | —     |  |  |  |

#### **REGISTER 9-3: CHETAG: CACHE TAG REGISTER**

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |  |

|-------------------|------------------|------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |  |

#### bit 31 LTAGBOOT: Line TAG Address Boot bit

- 1 = The line is in the 0x1D000000 (physical) area of memory

- 0 = The line is in the 0x1FC00000 (physical) area of memory

#### bit 30-24 Unimplemented: Write '0'; ignore read

#### bit 23-4 LTAG<19:0>: Line TAG Address bits

LTAG<19:0> bits are compared against physical address to determine a hit. Because its address range and position of PFM in kernel space and user space, the LTAG PFM address is identical for virtual addresses, (system) physical addresses, and PFM physical addresses.

#### bit 3 LVALID: Line Valid bit

- 1 = The line is valid and is compared to the physical address for hit detection

- 0 = The line is not valid and is not compared to the physical address for hit detection

#### bit 2 LLOCK: Line Lock bit

- 1 = The line is locked and will not be replaced

- 0 = The line is not locked and can be replaced

#### bit 1 LTYPE: Line Type bit

- 1 = The line caches instruction words

- 0 = The line caches data words

- bit 0 Unimplemented: Write '0'; ignore read

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|------------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | _                 | —                 | —                      | -                 | —                | -                |  |  |  |  |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |  |  |

| 23.10        | —                 | —                 | -                 | —                 | —                      | —                 | —                | -                |  |  |  |  |

| 45.0         | R/W-0             | U-0               | U-0               | R/W-0             | R/W-0                  | U-0               | U-0              | U-0              |  |  |  |  |

| 15:8         | 0N <sup>(1)</sup> | —                 |                   | SUSPEND           | DMABUSY <sup>(1)</sup> |                   | _                |                  |  |  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0                    | U-0               | U-0              | U-0              |  |  |  |  |

| 7:0          | _                 | _                 | _                 | _                 | _                      | _                 | _                | _                |  |  |  |  |

### REGISTER 10-1: DMACON: DMA CONTROLLER CONTROL REGISTER

#### Legend:

| R = Readable bit  | able bit W = Writable bit |                      | d as '0'           |

|-------------------|---------------------------|----------------------|--------------------|

| -n = Value at POR | '1' = Bit is set          | '0' = Bit is cleared | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 ON: DMA On bit<sup>(1)</sup>

- 1 = DMA module is enabled

- 0 = DMA module is disabled

- bit 14-13 **Unimplemented:** Read as '0'

- bit 12 **SUSPEND:** DMA Suspend bit

- 1 = DMA transfers are suspended to allow CPU uninterrupted access to data bus

- 0 = DMA operates normally

#### bit 11 DMABUSY: DMA Module Busy bit<sup>(1)</sup>

- 1 = DMA module is active

- 0 = DMA module is disabled and not actively transferring data

- bit 10-0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

# PIC32MX330/350/370/430/450/470

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|

| 21.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 31:24        | _                 | —                 | —                 |                   | —                 | —                 | -                | —                |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 23:16        | _                 | —                 | —                 | -                 | —                 | —                 | -                | —                |  |  |  |  |  |

| 15:8         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |

| 15.0         | _                 | —                 | —                 | -                 | —                 | —                 | -                | —                |  |  |  |  |  |

| 7:0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |

| 7:0          |                   |                   |                   | BDTPTR            | H<23:16>          |                   |                  |                  |  |  |  |  |  |

# REGISTER 11-18: U1BDTP2: USB BDT PAGE 2 REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 **BDTPTRH<23:16>:** BDT Base Address bits This 8-bit value provides address bits 23 through 16 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

|              | EGISTER II-13. UIBUTF3. USB BUT FAGE 3 REGISTER |       |                   |                  |                  |       |       |       |  |  |  |  |

|--------------|-------------------------------------------------|-------|-------------------|------------------|------------------|-------|-------|-------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7                               |       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |       |       |       |  |  |  |  |

| 31:24        | U-0                                             | U-0   | U-0               | U-0              | U-0              | U-0   | U-0   | U-0   |  |  |  |  |

| 31.24        | —                                               | —     | _                 | —                | -                | _     | —     | —     |  |  |  |  |

| 00.40        | U-0                                             | U-0   | U-0               | U-0              | U-0              | U-0   | U-0   | U-0   |  |  |  |  |

| 23:16        | —                                               | —     | _                 | —                | -                | _     | —     | —     |  |  |  |  |

| 15.0         | U-0                                             | U-0   | U-0               | U-0              | U-0              | U-0   | U-0   | U-0   |  |  |  |  |

| 15:8         | —                                               | —     | _                 | —                | -                | _     | —     | —     |  |  |  |  |

| 7:0          | R/W-0                                           | R/W-0 | R/W-0             | R/W-0            | R/W-0            | R/W-0 | R/W-0 | R/W-0 |  |  |  |  |

| 7:0          |                                                 |       |                   | BDTPTR           | U<31:24>         |       |       |       |  |  |  |  |

# REGISTER 11-19: U1BDTP3: USB BDT PAGE 3 REGISTER

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-8 Unimplemented: Read as '0'

bit 7-0 BDTPTRU<31:24>: BDT Base Address bits

This 8-bit value provides address bits 31 through 24 of the BDT base address, defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

## TABLE 12-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| ss                          |                       |               |       |       |       |       |       |       |      | Bi   | its  |      |      |      |      |           |             |      |            |

|-----------------------------|-----------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-----------|-------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2      | 17/1        | 16/0 | All Resets |

| FB90                        | RPC4R <sup>(1)</sup>  | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      | _    |      |      | —    | —<br>RPC4 | —<br><3:0>  | —    | 0000       |

| FBB4                        | RPC13R                | 31:16         |       | _     |       | _     |       |       | _    |      |      | _    | _    |      | —    | —         | _           | _    | 0000       |

|                             |                       | 15:0          | _     |       | _     | _     |       | _     |      | _    | _    | _    | —    | _    |      | RPC1      |             |      | 0000       |

| FBB8                        | RPC14R                | 31:16<br>15:0 |       |       |       |       |       |       |      |      |      |      |      |      |      | RPC1      | —<br>4<3:0> | -    | 0000       |

| FBC0                        | RPD0R                 | 31:16         | —     | —     | —     | —     | _     | —     | —    | _    | —    | —    | —    | —    | —    |           |             | —    | 0000       |

| 1000                        |                       | 15:0<br>31:16 |       |       | _     | —     |       |       | _    |      |      | _    | —    | _    | _    | RPDO      | )<3:0>      | _    | 0000       |

| FBC4                        | RPD1R                 | 15:0          |       |       |       |       |       |       |      |      |      |      |      |      | _    | RPD1      | <3:0>       | _    | 0000       |

| FBC8                        | RPD2R                 | 31:16         | _     | -     | —     | —     | _     | _     | —    | _    | _    | —    | —    | —    | —    | —         | —           | —    | 0000       |

| FBC0                        | RPDZR                 | 15:0          | _     | —     | —     | —     | —     | _     | _    | —    | _    | —    | _    | —    |      | RPD2      | 2<3:0>      |      | 0000       |

| FBCC                        | RPD3R                 | 31:16<br>15:0 |       |       |       | _     |       |       |      |      |      | _    |      | _    | —    | RPD3      | —<br><3·0>  | _    | 0000       |

|                             |                       | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | -         | _           |      | 0000       |

| FBD0                        | RPD4R                 | 15:0          | _     | -     | _     | _     | _     | _     | _    | —    | _    | _    | _    | _    |      | RPD4      | <3:0>       |      | 0000       |

| FBD4                        | RPD5R                 | 31:16         | _     | —     | —     | —     | _     | _     | _    | —    | _    | _    | -    | _    | —    | —         | _           | _    | 0000       |

| TDD4                        | IN DOIN               | 15:0          | _     | —     | —     | —     | _     | _     | —    | _    | _    | —    | —    | _    |      | RPD5      | 5<3:0>      |      | 0000       |

| FBE0                        | RPD8R                 | 31:16<br>15:0 |       |       |       | _     |       | _     | _    | _    |      |      | _    |      |      | -         | -           | —    | 0000       |

|                             |                       | 31:16         |       |       |       |       |       |       | _    |      |      |      |      |      |      |           | 3<3:0>      |      | 0000       |

| FBE4                        | RPD9R                 | 15:0          | _     | _     | _     | _     | _     | _     |      |      | _    |      | _    | _    |      | RPDS      | )<3:0>      |      | 0000       |

|                             |                       | 31:16         | _     | —     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | —    | _         |             |      | 0000       |

| FBE8                        | RPD10R                | 15:0          | -     | —     | _     | —     | -     | _     | —    | _    | _    | _    | —    | _    |      | RPD1      | 0<3:0>      |      | 0000       |

| FBEC                        | RPD11R                | 31:16<br>15:0 |       | -     | _     | -     |       |       |      |      |      | _    | _    | _    | —    | RPD1      |             | —    | 0000       |

|                             |                       | 31:16         |       | _     | _     | _     |       |       |      |      |      | _    | _    | _    |      |           |             | _    | 0000       |

| FBF0                        | RPD12R <sup>(1)</sup> | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    |      |      | _    |      |      | RPD1      | 2<3:0>      |      | 0000       |

|                             | DDD ( (D(1)           | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | —         | _           | —    | 0000       |

| FBF8                        | RPD14R <sup>(1)</sup> | 15:0          |       |       |       | —     | _     | _     | —    | _    | _    |      | —    |      |      | RPD1      | 4<3:0>      |      | 0000       |

| FBFC                        | RPD15R <sup>(1)</sup> | 31:16<br>15:0 |       |       |       | _     |       |       | _    |      |      |      |      |      | —    | RPD1      | —<br>5<3:0> |      | 0000       |

| <u> </u>                    |                       | 31:16         |       |       |       |       |       |       |      |      |      |      | _    |      |      | _         |             | _    | 0000       |

| FC0C                        | RPE3R                 | 15:0          |       | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPE3      | <3:0>       |      | 0000       |

PIC32MX330/350/370/430/450/470

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

2: This register is only available on devices without a USB module.

3: This register is not available on 64-pin devices with a USB module.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | _                 | —                 | _                 |                   | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        |                   | _                 | -                 | —                 | _                 | _                 | _                | —                |

| 15.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | _                 | _                 | _                 | —                 | _                 |                   | _                | —                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                 | _                 |                   | [pin name         | ?]R<3:0>         |                  |

#### REGISTER 12-1: [pin name]R: PERIPHERAL PIN SELECT INPUT REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-4 Unimplemented: Read as '0'

#### bit 3-0 [*pin name*]R<3:0>: Peripheral Pin Select Input bits Where [*pin name*] refers to the pins that are used to configure peripheral input mapping. See Table 12-1 for input pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

#### REGISTER 12-2: RPnR: PERIPHERAL PIN SELECT OUTPUT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 | _                 | —                 | _                 | _                 | -                | _                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 | _                 | —                 | _                 | _                 | -                | _                |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | —                 | _                 | _                 | —                 | _                 | —                 |                  | _                |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | —                 | _                 | —                 |                   | RPnR              | <3:0>            |                  |

# Legend:

| 0                 |                  |                                    |                    |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |

bit 31-4 Unimplemented: Read as '0'

bit 3-0 **RPnR<3:0>:** Peripheral Pin Select Output bits See Table 12-2 for output pin selection values.

**Note:** Register values can only be changed if the IOLOCK Configuration bit (CFGCON<13>) = 0.

# REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER (CONTINUED)

- bit 2 TSYNC: Timer External Clock Input Synchronization Selection bit

- When TCS = 1:1 = External clock input is synchronized0 = External clock input is not synchronizedWhen TCS = 0:This bit is ignored.

- bit 1 **TCS:** Timer Clock Source Select bit 1 = External clock from TxCKI pin 0 = Internal peripheral clock

- bit 0 Unimplemented: Read as '0'

- **Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

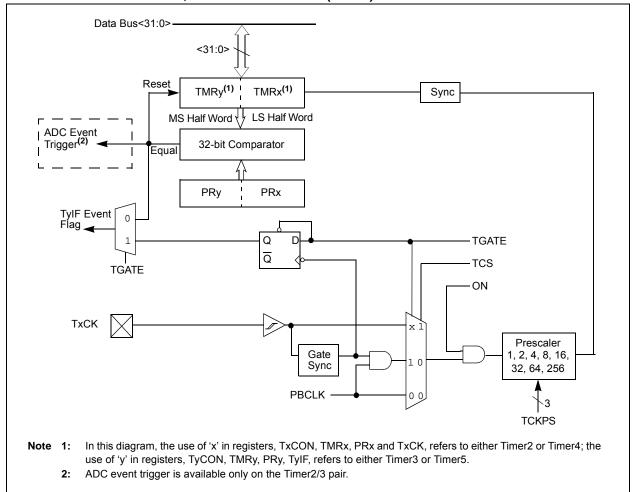

### FIGURE 14-2: TIMER2/3, 4/5 BLOCK DIAGRAM (32-BIT)<sup>(1)</sup>

#### **Control Registers** 19.1

# TABLE 19-1: I2C1 AND I2C2 REGISTER MAP

| ess                         |                                 |               |              |            |           |              |             |              |              | Bi        | ts        |              |            |              |           |          |           |          |              |

|-----------------------------|---------------------------------|---------------|--------------|------------|-----------|--------------|-------------|--------------|--------------|-----------|-----------|--------------|------------|--------------|-----------|----------|-----------|----------|--------------|

| Virtual Address<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range     | 31/15        | 30/14      | 29/13     | 28/12        | 27/11       | 26/10        | 25/9         | 24/8      | 23/7      | 22/6         | 21/5       | 20/4         | 19/3      | 18/2     | 17/1      | 16/0     | All Resets   |

| 5000                        | I2C1CON                         | 31:16<br>15:0 | —<br>ON      | -          | —<br>SIDL | —<br>SCLREL  | —<br>STRICT | —<br>A10M    | —<br>DISSLW  | —<br>SMEN | —<br>GCEN | —<br>STREN   | —<br>ACKDT | —<br>ACKEN   | —<br>RCEN | —<br>PEN | —<br>RSEN | —<br>SEN | 0000<br>BFFF |

| 5010                        | I2C1STAT                        | 31:16         | _            | —          |           | —            | _           |              | —            | _         | _         | —            | —          | —            |           | —        | —         |          | 0000         |

| 5010                        | 120131AI                        | 15:0          | ACKSTAT      | TRSTAT     | _         | —            | —           | BCL          | GCSTAT       | ADD10     | IWCOL     | I2COV        | D_A        | Р            | S         | R_W      | RBF       | TBF      | 0000         |

| 5020                        | I2C1ADD                         | 31:16         | _            | _          | -         | _            | _           |              | _            | _         | _         | _            | _          | _            |           | _        | —         | -        | 0000         |

| 5020                        | 120 TADD                        | 15:0          | —            | —          |           | —            | —           |              |              |           |           |              | Address    | Register     |           |          |           |          | 0000         |

| 5030                        | I2C1MSK                         | 31:16         | —            | —          | —         | —            | —           | _            | —            | —         | —         | —            |            | —            | —         | —        | —         | —        | 0000         |

| 0000                        | 1201111010                      | 15:0          | —            | —          | _         | —            | —           | —            |              |           |           |              | Address Ma | ask Registe  |           |          |           |          | 0000         |

| 5040                        | I2C1BRG                         | 31:16         | _            | —          | _         | —            | —           | —            | —            | _         | —         | —            | _          | —            | —         | —        | -         |          | 0000         |

|                             |                                 | 15:0          | _            | _          |           |              |             |              |              |           | Bau       | id Rate Ger  | erator Reg | ister        |           |          |           |          | 0000         |

| 5050                        | I2C1TRN                         | 31:16         | _            | _          |           |              | _           |              |              | _         |           | —            | —          | —            | _         | —        | —         | —        | 0000         |

|                             | -                               | 15:0          | _            | —          | _         |              |             |              | —            | —         |           |              |            | Transmit     | Register  |          |           |          | 0000         |

| 5060                        | I2C1RCV                         | 31:16         | —            | —          | —         |              | —           | _            | —            | —         | —         | _            | —          | _            | —         | —        | _         | _        | 0000         |

|                             |                                 | 15:0          | _            |            | _         |              |             | _            | _            |           |           |              |            | Receive      |           |          |           |          | 0000         |

| 5100                        | I2C2CON                         | 31:16         | -            | —          | -         | -            | —           | —            | —            | -         | —         | _            | —          | —            | —         |          | —         | _        | 0000         |

|                             |                                 | 15:0          | ON           | _          | SIDL      | SCLREL       | STRICT      | A10M         | DISSLW       | SMEN      | GCEN      | STREN        | ACKDT      | ACKEN        | RCEN      | PEN      | RSEN      | SEN      | BFFF         |

| 5110                        | I2C2STAT                        | 31:16         | -            | -          |           |              |             | -            | -            | -         | -         | —            | —          | -            |           | —        | -         | -        | 0000         |

|                             |                                 | 15:0<br>31:16 | ACKSTAT      | TRSTAT     | _         | _            | _           | BCL          | GCSTAT       | ADD10     | IWCOL     | I2COV        | D_A        | Р            | S         | R_W      | RBF       | TBF      | 0000         |

| 5120                        | I2C2ADD                         |               | _            |            | —         | _            | _           | _            | —            |           | _         |              |            | —            | _         | _        | _         | —        | 0000         |

|                             |                                 | 15:0<br>31:16 |              |            |           |              | _           |              |              |           |           |              | Address    | Register     |           |          |           |          | 0000         |

| 5130                        | I2C2MSK                         | 15:0          | _            |            | _         |              |             |              |              | _         | _         | _            |            | ask Register | —         | _        | _         | —        | 0000         |

|                             |                                 | 31:16         |              |            |           | _            |             |              | _            |           |           |              |            |              |           |          | _         | _        | 0000         |

| 5140                        | I2C2BRG                         | 15:0          |              |            |           |              |             |              |              |           |           | I d Rate Ger | erator Reg | istor        |           |          | _         |          | 0000         |

|                             |                                 | 31:16         | _            |            |           |              | _           | _            |              | _         |           |              |            |              | _         |          |           |          | 0000         |

| 5150                        | I2C2TRN                         | 15:0          |              |            |           |              |             |              |              |           |           |              |            | Transmit     | Register  |          |           |          | 0000         |

|                             |                                 | 31:16         | _            |            |           |              |             |              |              |           |           |              | _          |              |           |          |           | _        | 0000         |

| 5160                        | I2C2RCV                         | 15:0          | _            | _          | _         | _            | _           | _            | _            | _         |           |              | 1          | Receive      | Register  |          |           |          | 0000         |

| Legen                       | d∙ v=u                          |               | n value on l | Reset: — = | unimpleme | ented read a | as '0' Rese | t values are | e shown in h | exadecima | 1         |              |            |              |           |          |           |          |              |

All registers in this table except I2CxRCV have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information. Note 1:

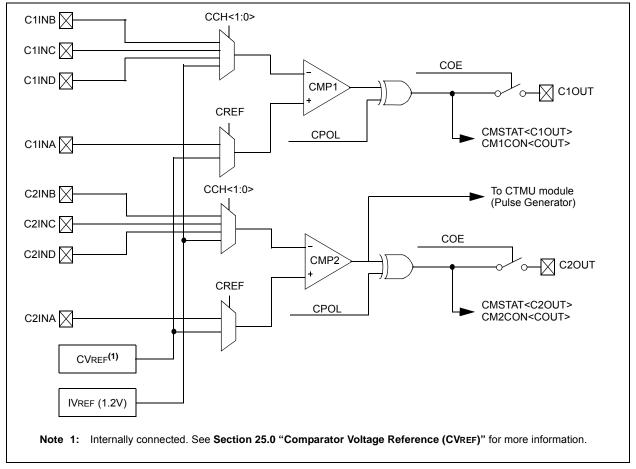

# 24.0 COMPARATOR

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer Section 19. to "Comparator" (DS60001110), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Analog Comparator module contains two comparators that can be configured in a variety of ways.

The following are key features of this module:

- · Selectable inputs available include:

- Analog inputs multiplexed with I/O pins

- On-chip internal absolute voltage reference (IVREF)

- Comparator voltage reference (CVREF)

- · Outputs can be Inverted

- Selectable interrupt generation

A block diagram of the comparator module is provided in Figure 24-1.

#### FIGURE 24-1: COMPARATOR BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2     | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|------------------|------------------|

| 04.04        | r-0               | r-1               | r-1               | R/P               | r-1               | r-1                   | r-1              | R/P              |

| 31:24        | _                 | —                 | —                 | CP                | —                 | —                     | —                | BWP              |

| 00.40        | r-1               | r-1               | r-1               | r-1               | R/P               | R/P                   | R/P              | R/P              |

| 23:16        | —                 | —                 | —                 | —                 |                   | PWP                   | <7:4>            |                  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | r-1                   | r-1              | r-1              |

| 15:8         |                   | PWP<              | <3:0>             |                   | —                 | —                     | _                | —                |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P               | R/P                   | R/P              | R/P              |

| 7:0          |                   | _                 | —                 | ICESE             | L<1:0>            | JTAGEN <sup>(1)</sup> | DEBU             | G<1:0>           |

#### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:         r = Reserved bit         P = Programmable bit |                  |                      |                    |

|---------------------------------------------------------------|------------------|----------------------|--------------------|

| R = Readable bit                                              | W = Writable bit | U = Unimplemented b  | it, read as '0'    |

| -n = Value at POR                                             | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

bit 31 **Reserved:** Write '0'

bit 30-29 Reserved: Write '1'

bit 28 **CP:** Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device.

1 = Protection is disabled

0 = Protection is enabled

#### bit 27-25 Reserved: Write '1'

bit 24 BWP: Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable

0 = Boot Flash is not writable

bit 23-20 Reserved: Write '1'

bit 19-12 **PWP<7:0>:** Program Flash Write-Protect bits

Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages.

| 11111111 = Disabled    |

|------------------------|

| 11111110 = 0xBD00_0FFF |

| 11111101 = 0xBD00_1FFF |

| 11111100 = 0xBD00_2FFF |

| 11111011 = 0xBD00_3FFF |

| 11111010 = 0xBD00_4FFF |

| 11111001 = 0xBD00_5FFF |

| 11111000 = 0xBD00_6FFF |

| 11110111 = 0xBD00_7FFF |

| 11110110 = 0xBD00 8FFF |

| 11110101 = 0xBD00_9FFF |

| 11110100 = 0xBD00_AFFF |

| 11110011 = 0xBD00 BFFF |

| 11110010 = 0xBD00 CFFF |

| 11110001 = 0xBD00 DFFF |

| 11110000 = 0xBD00 EFFF |

| 11101111 = 0xBD00 FFFF |

| . –                    |

|                        |

|                        |

| 01111111 = 0xBD07 FFFF |

| _                      |

|                        |

Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

# 29.0 INSTRUCTION SET

The PIC32MX330/350/370/430/450/470 family instruction set complies with the MIPS32<sup>®</sup> Release 2 instruction set architecture. The PIC32 device family does not support the following features:

- · Core extend instructions

- Coprocessor 1 instructions

- Coprocessor 2 instructions

Note: Refer to "MIPS32<sup>®</sup> Architecture for Programmers Volume II: The MIPS32<sup>®</sup> Instruction Set" at www.imgtec.com for more information.

## 30.11 Demonstration/Development Boards, Evaluation Kits, and Starter Kits

A wide variety of demonstration, development and evaluation boards for various PIC MCUs and dsPIC DSCs allows quick application development on fully functional systems. Most boards include prototyping areas for adding custom circuitry and provide application firmware and source code for examination and modification.

The boards support a variety of features, including LEDs, temperature sensors, switches, speakers, RS-232 interfaces, LCD displays, potentiometers and additional EEPROM memory.

The demonstration and development boards can be used in teaching environments, for prototyping custom circuits and for learning about various microcontroller applications.

In addition to the PICDEM<sup>™</sup> and dsPICDEM<sup>™</sup> demonstration/development board series of circuits, Microchip has a line of evaluation kits and demonstration software for analog filter design, KEELOQ<sup>®</sup> security ICs, CAN, IrDA<sup>®</sup>, PowerSmart battery management, SEEVAL<sup>®</sup> evaluation system, Sigma-Delta ADC, flow rate sensing, plus many more.

Also available are starter kits that contain everything needed to experience the specified device. This usually includes a single application and debug capability, all on one board.

Check the Microchip web page (www.microchip.com) for the complete list of demonstration, development and evaluation kits.

# 30.12 Third-Party Development Tools

Microchip also offers a great collection of tools from third-party vendors. These tools are carefully selected to offer good value and unique functionality.

- Device Programmers and Gang Programmers from companies, such as SoftLog and CCS

- Software Tools from companies, such as Gimpel and Trace Systems

- Protocol Analyzers from companies, such as Saleae and Total Phase

- Demonstration Boards from companies, such as MikroElektronika, Digilent<sup>®</sup> and Olimex

- Embedded Ethernet Solutions from companies, such as EZ Web Lynx, WIZnet and IPLogika<sup>®</sup>

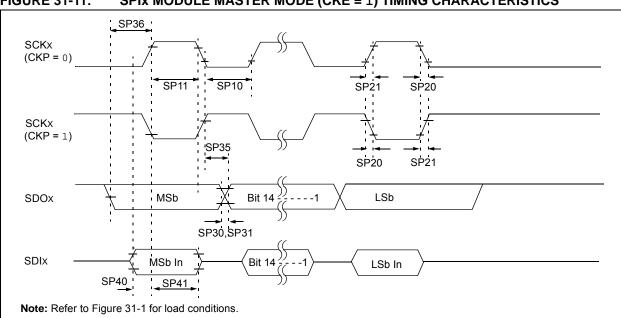

#### **FIGURE 31-11:** SPIx MODULE MASTER MODE (CKE = 1) TIMING CHARACTERISTICS

#### TABLE 31-30: SPIX MODULE MASTER MODE (CKE = 1) TIMING REQUIREMENTS

| AC CHA        |                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |        |                     |      |       |                    |

|---------------|----------------------|------------------------------------------------------|--------|---------------------|------|-------|--------------------|

| Param.<br>No. | Symbol               | Characteristics <sup>(1)</sup>                       | Min.   | Тур. <sup>(2)</sup> | Max. | Units | Conditions         |

| SP10          | TscL                 | SCKx Output Low Time (Note 3)                        | Tsck/2 | —                   |      | ns    | _                  |

| SP11          | TscH                 | SCKx Output High Time (Note 3)                       | Tsck/2 |                     |      | ns    | —                  |

| SP20          | TscF                 | SCKx Output Fall Time (Note 4)                       | _      | _                   | _    | ns    | See parameter DO32 |

| SP21          | TscR                 | SCKx Output Rise Time (Note 4)                       | _      | _                   | _    | ns    | See parameter DO32 |

| SP30          | TDOF                 | SDOx Data Output Fall Time (Note 4)                  | _      | —                   | _    | ns    | See parameter DO32 |

| SP31          | TDOR                 | SDOx Data Output Rise Time (Note 4)                  | —      | —                   | _    | ns    | See parameter DO31 |

| SP35          | TscH2doV,            | SDOx Data Output Valid after                         | _      |                     | 15   | ns    | VDD > 2.7V         |

|               | TscL2DoV             | SCKx Edge                                            | _      |                     | 20   | ns    | VDD < 2.7V         |

| SP36          | TDOV2sc,<br>TDOV2scL | SDOx Data Output Setup to<br>First SCKx Edge         | 15     | —                   | _    | ns    | —                  |

| SP40          | TDIV2scH,            | Setup Time of SDIx Data Input to                     | 15     | _                   | _    | ns    | VDD > 2.7V         |

|               | TDIV2scL             | SCKx Edge                                            | 20     | —                   |      | ns    | VDD < 2.7V         |

| SP41          | TscH2DIL,            | Hold Time of SDIx Data Input                         | 15     | —                   |      | ns    | VDD > 2.7V         |

| TscL2DIL      |                      | to SCKx Edge                                         | 20     | _                   |      | ns    | VDD < 2.7V         |

Note 1: These parameters are characterized, but not tested in manufacturing.

- Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only 2: and are not tested.

- The minimum clock period for SCKx is 40 ns. Therefore, the clock generated in Master mode must not 3: violate this specification.

- Assumes 50 pF load on all SPIx pins. 4:

#### TABLE 31-31: SPIX MODULE SLAVE MODE (CKE = 0) TIMING REQUIREMENTS (CONTINUED)

| AC CHARACTERISTICS |                      |                                | $\begin{array}{llllllllllllllllllllllllllllllllllll$ |                     |      |       |            |  |

|--------------------|----------------------|--------------------------------|------------------------------------------------------|---------------------|------|-------|------------|--|

| Param.<br>No.      | Symbol               | Characteristics <sup>(1)</sup> | Min.                                                 | Тур. <sup>(2)</sup> | Max. | Units | Conditions |  |

| SP52               | TscH2ssH<br>TscL2ssH | SSx after SCKx Edge            | Тscк +<br>20                                         |                     | _    | ns    | _          |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

**3:** The minimum clock period for SCKx is 40 ns.

4: Assumes 50 pF load on all SPIx pins.

| AC CHA        | RACTERIS  |                            | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ & -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |      |      |       |                            |

|---------------|-----------|----------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|----------------------------|

| Param.<br>No. | Symbol    | Characteristics            |                                                                                                                                                                                                                                                                                                                                                        | Min. | Max. | Units | Conditions                 |

| IS34          | THD:STO   | Stop Condition             | 100 kHz mode                                                                                                                                                                                                                                                                                                                                           | 4000 | _    | ns    | —                          |

|               | Hold Time | 400 kHz mode               | 600                                                                                                                                                                                                                                                                                                                                                    | _    | ns   |       |                            |

|               |           |                            | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                                                                                                 | 250  |      | ns    |                            |

| IS40          | TAA:SCL   | Output Valid from<br>Clock | 100 kHz mode                                                                                                                                                                                                                                                                                                                                           | 0    | 3500 | ns    | —                          |

|               |           |                            | 400 kHz mode                                                                                                                                                                                                                                                                                                                                           | 0    | 1000 | ns    |                            |

|               |           |                            | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                                                                                                 | 0    | 350  | ns    |                            |

| IS45          | TBF:SDA   | Bus Free Time              | 100 kHz mode                                                                                                                                                                                                                                                                                                                                           | 4.7  | —    | μs    | The amount of time the bus |

|               |           |                            | 400 kHz mode                                                                                                                                                                                                                                                                                                                                           | 1.3  |      | μs    | must be free before a new  |

|               |           |                            | 1 MHz mode<br>(Note 1)                                                                                                                                                                                                                                                                                                                                 | 0.5  | —    | μS    | transmission can start     |

| IS50          | Св        | Bus Capacitive Lo          | ading                                                                                                                                                                                                                                                                                                                                                  | _    | 400  | pF    | —                          |

# TABLE 31-34: I2Cx BUS DATA TIMING REQUIREMENTS (SLAVE MODE) (CONTINUED)

**Note 1:** Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

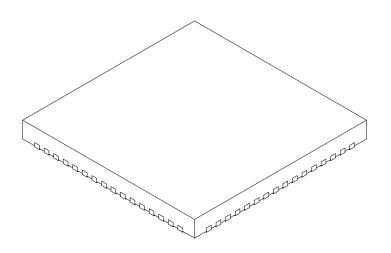

# 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | Units  |      |          | s    |

|------------------------|--------|------|----------|------|

| Dimension              | Limits | MIN  | NOM      | MAX  |

| Number of Pins         | N      |      | 64       |      |

| Pitch                  | е      |      | 0.50 BSC |      |

| Overall Height         | А      | 0.80 | 0.90     | 1.00 |

| Standoff               | A1     | 0.00 | 0.02     | 0.05 |

| Contact Thickness      | A3     |      | 0.20 REF |      |

| Overall Width          | Е      |      | 9.00 BSC |      |

| Exposed Pad Width      | E2     | 5.30 | 5.40     | 5.50 |

| Overall Length         | D      |      | 9.00 BSC |      |

| Exposed Pad Length     | D2     | 5.30 | 5.40     | 5.50 |

| Contact Width          | b      | 0.20 | 0.25     | 0.30 |

| Contact Length         | L      | 0.30 | 0.40     | 0.50 |

| Contact-to-Exposed Pad | К      | 0.20 | -        | -    |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2 of 2

# PIC32MX330/350/370/430/450/470

NOTES:

# **PRODUCT IDENTIFICATION SYSTEM**

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.

| PIC32 MX 3XX F 064 H B T - XXX I/PT - XXX       Example:         Microchip Brand |                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

|----------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Flash Memory Far                                                                 | nily                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Architecture                                                                     | MX = 32-bit RISC MCU core                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Product Groups                                                                   | 3XX = General purpose microcontroller family<br>4XX = General purpose with USB microcontroller family                                                                                                                                                                                                                                                                                           |  |  |  |  |  |

| Flash Memory Family                                                              | F = Flash program memory                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Program Memory Size                                                              | 064 = 6 4KB<br>128 = 128KB<br>256 = 256KB<br>512 = 512KB                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| Pin Count                                                                        | H = 64-pin<br>L = 100-pin                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |  |

| Software Targeting                                                               | B = Targeted for Bluetooth Audio Break-in devices                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| Speed                                                                            | blank = up to 100 MHz<br>120   = up to 120 MHz                                                                                                                                                                                                                                                                                                                                                  |  |  |  |  |  |

| Temperature Range                                                                | blank = 0°C to +70°C (Commercial)<br>I = -40°C to +85°C (Industrial)<br>V = -40°C to +105°C (V-Temp)                                                                                                                                                                                                                                                                                            |  |  |  |  |  |

| Package                                                                          | MR = 64-Lead (9x9x0.9 mm) QFN with 5.40x5.40 Exposed Pad (Plastic Quad Flat)<br>RG = 64-Lead (9x9x0.9 mm) QFN with 4.7x4.7 Exposed Pad (Plastic Quad Flat)<br>PT = 64-Lead (10x10x1 mm) TQFP (Thin Quad Flatpack)<br>PT = 100-Lead (12x12x1 mm) TQFP (Thin Quad Flatpack)<br>PF = 100-Lead (14x14x1 mm) TQFP (Thin Quad Flatpack)<br>TL = 124-Lead (9x9x0.9 mm) VTLA (Very Thin Leadless Array) |  |  |  |  |  |

| Pattern                                                                          | Three-digit QTP, SQTP, Code or Special Requirements (blank otherwise)<br>ES = Engineering Sample                                                                                                                                                                                                                                                                                                |  |  |  |  |  |