#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

·XF

| Product Status             | Obsolete                                                                       |

|----------------------------|--------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                   |

| Core Size                  | 32-Bit Single-Core                                                             |

| Speed                      | 80MHz                                                                          |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                  |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                     |

| Number of I/O              | 85                                                                             |

| Program Memory Size        | 512KB (512K x 8)                                                               |

| Program Memory Type        | FLASH                                                                          |

| EEPROM Size                | -                                                                              |

| RAM Size                   | 128K x 8                                                                       |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                    |

| Data Converters            | A/D 28x10b                                                                     |

| Oscillator Type            | Internal                                                                       |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                             |

| Mounting Type              | Surface Mount                                                                  |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                               |

| Supplier Device Package    | 124-VTLA (9x9)                                                                 |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx470f512l-v-tl |

|                            |                                                                                |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 5: PIN NAMES FOR 100-PIN DEVICES (CONTINUED)

| 100-PIN TQFP | (TOP VIEW) <sup>(1,2)</sup> |

|--------------|-----------------------------|

|--------------|-----------------------------|

PIC32MX430F064L PIC32MX450F128L PIC32MX450F256L PIC32MX470F512L

100

|       |                       |       | 1                   |

|-------|-----------------------|-------|---------------------|

| Pin # | Full Pin Name         | Pin # | Full Pin Name       |

| 71    | RPD11/PMCS1/RD11      | 86    | VDD                 |

| 72    | RPD0/INT0/RD0         | 87    | RPF0/PMD11/RF0      |

| 73    | SOSCI/RPC13/RC13      | 88    | RPF1/PMD10/RF1      |

| 74    | SOSCO/RPC14/T1CK/RC14 | 89    | RPG1/PMD9/RG1       |

| 75    | Vss                   | 90    | RPG0/PMD8/RG0       |

| 76    | AN24/RPD1/RD1         | 91    | TRCLK/RA6           |

| 77    | AN25/RPD2/RD2         | 92    | TRD3/CTED8/RA7      |

| 78    | AN26/RPD3/RD3         | 93    | PMD0/RE0            |

| 79    | RPD12/PMD12/RD12      | 94    | PMD1/RE1            |

| 80    | PMD13/RD13            | 95    | TRD2/RG14           |

| 81    | RPD4/PMWR/RD4         | 96    | TRD1/RG12           |

| 82    | RPD5/PMRD/RD5         | 97    | TRD0/RG13           |

| 83    | PMD14/RD6             | 98    | AN20/CTPLS/PMD2/RE2 |

| 84    | PMD15/RD7             | 99    | RPE3/PMD3/RE3       |

| 85    | VCAP                  | 100   | AN21/PMD4/RE4       |

Note

1:

The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RBx-RGx) can be used as a change notification pin (CNBx-CNGx). See Section 12.0 "I/O Ports" for more information.

## TABLE 6: PIN NAMES FOR 124-PIN DEVICES

|                   | -PIN VTLA (BOTTOM VIEW) <sup>(1,2,3,4,5)</sup> A1                        | 1      |                   |                                   |                           |

|-------------------|--------------------------------------------------------------------------|--------|-------------------|-----------------------------------|---------------------------|

|                   |                                                                          |        | I                 | B13 B29                           | Conductive<br>Thermal Pad |

|                   | PIC32MX330F064L<br>PIC32MX350F128L<br>PIC32MX350F256L<br>PIC32MX370F512L |        |                   | B1<br>B56                         | B41<br>A51                |

|                   |                                                                          |        | A1                |                                   |                           |

|                   | Polarity                                                                 | Indica | ator              | A68                               |                           |

| Package<br>Bump # | Full Pin Name                                                            |        | Package<br>Bump # |                                   | Full Pin Name             |

| A1                | No Connect                                                               |        | A38               | SDA1/RG3                          |                           |

| A2                | RG15                                                                     | 1      | A39               | SCL2/RA2                          |                           |

| A3                | Vss                                                                      | 1      | A40               | TDI/CTED9/RA4                     |                           |

| A4                | AN23/PMD6/RE6                                                            | -      | A41               | Vdd                               |                           |

| A5                | RPC1/RC1                                                                 | 1      | A42               | OSC2/CLKO/RC15                    |                           |

| A6                | RPC3/RC3                                                                 | -      | A43               | Vss                               |                           |

| A7                | AN16/C1IND/RPG6/SCK2/PMA5/RG6                                            | _      | A44               | RPA15/RA15                        |                           |

| A8                | AN18/C2IND/RPG8/PMA3/RG8                                                 | _      | A45               | RPD9/RD9                          |                           |

| A9                | AN19/C2INC/RPG9/PMA2/RG9                                                 | _      | A46               | RPD11/PMCS1/RD                    | 11                        |

| A10               | VDD                                                                      | -      | A47               | SOSCI/RPC13/RC1                   |                           |

| A11               | RPE8/RE8                                                                 | -      | A48               | VDD                               | <u> </u>                  |

| A12               | AN5/C1INA/RPB5/RB5                                                       | -      | A49               | No Connect                        |                           |

| A13               | PGED3/AN3/C2INA/RPB3/RB3                                                 | -      | A50               | No Connect                        |                           |

| A14               |                                                                          | _      | A51               | No Connect                        |                           |

| A15               | PGEC1/AN1/RPB1/CTED12/RB1                                                | _      | A52               | AN24/RPD1/RD1                     |                           |

| A16               | No Connect                                                               | -      | A53               | AN26/RPD3/RD3                     |                           |

| A17               | No Connect                                                               | -      | A54               | PMD13/RD13                        |                           |

| A18               | No Connect                                                               | _      | A54<br>A55        | RPD5/PMRD/RD5                     |                           |

| A10<br>A19        | No Connect                                                               | _      | A55<br>A56        | PMD15/RD7                         |                           |

| -                 |                                                                          | _      |                   | No Connect                        |                           |

| A20<br>A21        | PGEC2/AN6/RPB6/RB6<br>Vref-/CVref-/PMA7/RA9                              | _      | A57               | No Connect                        |                           |

|                   |                                                                          | _      | A58               |                                   |                           |

| A22               |                                                                          | _      | A59               |                                   |                           |

| A23               |                                                                          |        | A60               | RPF1/PMD10/RF1                    |                           |

| A24               | CVREFOUT/AN10/RPB10/CTED11/PMA13/RB10                                    |        | A61               | RPG0/PMD8/RG0                     |                           |

| A25               |                                                                          |        | A62               | TRD3/CTED8/RA7                    |                           |

| A26               | TCK/CTED2/RA1                                                            |        | A63               | Vss                               |                           |

| A27               | RPF12/RF12                                                               |        | A64               | PMD1/RE1                          |                           |

| A28               | AN13/PMA10/RB13                                                          |        | A65               | TRD1/RG12<br>AN20/PMD2/RE2        |                           |

| A29               | AN15/RPB15/OCFB/CTED6/PMA0/RB15                                          |        | A66               | AN20/PMD2/RE2<br>AN21/PMD4/RE4    |                           |

| A30               |                                                                          |        | A67               |                                   |                           |

| A31               | RPD15/RD15                                                               |        | A68               | No Connect                        |                           |

| A32               | RPF5/PMA8/RF5                                                            |        | B1                |                                   | DEF                       |

| A33               | No Connect                                                               | 4      | B2                | AN22/RPE5/PMD5/                   | KED                       |

| A34               | No Connect                                                               | 4      | B3                | AN27/PMD7/RE7                     |                           |

| A35               | RPF3/RF3                                                                 |        | B4                | RPC2/RC2                          |                           |

| A36<br>A37        | RPF2/RF2<br>RPF7/RF7                                                     | 4      | B5<br>B6          | RPC4/CTED7/RC4<br>AN17/C1INC/RPG7 |                           |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx), with the exception of RF6, can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: RPF6 (bump B30) and RPF7 (bump A37) are only remappable for input functions.

4: Shaded package bumps are 5V tolerant.

5: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 04.04        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |

| 31:24        | 24 NVMKEY<31:24>  |                   |                   |                   |                   |                   |                  |                  |  |  |

| 00.40        | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |

| 23:16        | NVMKEY<23:16>     |                   |                   |                   |                   |                   |                  |                  |  |  |

| 45.0         | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |

| 15:8         | NVMKEY<15:8>      |                   |                   |                   |                   |                   |                  |                  |  |  |

| 7:0          | W-0               | W-0               | W-0               | W-0               | W-0               | W-0               | W-0              | W-0              |  |  |

|              |                   |                   |                   | NVMK              | EY<7:0>           |                   |                  | •                |  |  |

#### REGISTER 5-2: NVMKEY: PROGRAMMING UNLOCK REGISTER

## Legend:

| Legena.           |                  |                      |                    |

|-------------------|------------------|----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bi | t, read as '0'     |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared | x = Bit is unknown |

## bit 31-0 NVMKEY<31:0>: Unlock Register bits

These bits are write-only, and read as '0' on any read

Note: This register is used as part of the unlock sequence to prevent inadvertent writes to the PFM.

## REGISTER 5-3: NVMADDR: FLASH ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 31:24        | 31:24 NVMADDR<31:24> |                   |                   |                   |                   |                   |                  |                  |  |

| 00.40        | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 23:16        | NVMADDR<23:16>       |                   |                   |                   |                   |                   |                  |                  |  |

| 15.0         | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

| 15:8         | NVMADDR<15:8>        |                   |                   |                   |                   |                   |                  |                  |  |

| 7:0          | R/W-0                | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |

|              |                      |                   |                   | NVMAE             | )DR<7:0>          |                   |                  |                  |  |

| Legend:           |                  |                                    |                    |

|-------------------|------------------|------------------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |

bit 31-0 **NVMADDR<31:0>:** Flash Address bits Bulk/Chip/PFM Erase: Address is ignored Page Erase: Address identifies the page to erase Row Program: Address identifies the row to program Word Program: Address identifies the word to program

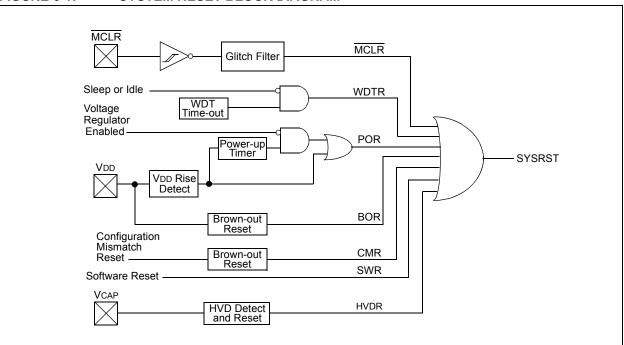

## 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Master Clear Reset pin

- · SWR: Software Reset

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CMR: Configuration Mismatch Reset

- HVDR: High Voltage Detect Reset

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

## FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0     |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|----------------------|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | _                 | _                | —                    |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 23:16        | —                 | —                 | —                 | _                 | _                 | —                 | —                | —                    |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0                  |

| 15:8         | —                 | _                 | _                 | _                 | _                 | —                 |                  | —                    |

| 7.0          | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | W-0, HC              |

| 7:0          |                   |                   |                   | _                 |                   | _                 | _                | SWRST <sup>(1)</sup> |

## REGISTER 6-2: RSWRST: SOFTWARE RESET REGISTER

| Legend:           | HC = Cleared by hardware |                                    |                    |  |  |

|-------------------|--------------------------|------------------------------------|--------------------|--|--|

| R = Readable bit  | W = Writable bit         | U = Unimplemented bit, read as '0' |                    |  |  |

| -n = Value at POR | '1' = Bit is set         | '0' = Bit is cleared               | x = Bit is unknown |  |  |

bit 31-1 Unimplemented: Read as '0'

- bit 0 SWRST: Software Reset Trigger bit<sup>(1)</sup>

- 1 = Enable software Reset event

- 0 = No effect

- Note 1: The system unlock sequence must be performed before the SWRST bit can be written. Refer to Section 6. "Oscillator" (DS60001112) in the "PIC32 Family Reference Manual" for details.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | —                 | —                 | _                 | _                 |                   | _                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23:16        | —                 | —                 | —                 | _                 | —                 | —                 | _                | CHECOH           |

| 45.0         | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | R/W-0            | R/W-0            |

| 15:8         | —                 | —                 | —                 | -                 | —                 |                   | DCSZ             | 2<1:0>           |

| 7.0          | U-0               | U-0               | R/W-0             | R/W-0             | U-0               | R/W-1             | R/W-1            | R/W-1            |

| 7:0          | _                 | —                 | PREFEN<1:0>       |                   | _                 | PFMWS<2:0>        |                  |                  |

#### REGISTER 9-1: CHECON: CACHE CONTROL REGISTER

#### Legend:

| Readable bit W = Writable bit |                  | U = Unimplemented bit, read as '0' |                    |  |

|-------------------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR             | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-17 Unimplemented: Write '0'; ignore read

- bit 16 CHECOH: Cache Coherency Setting on a PFM Program Cycle bit

- 1 = Invalidate all data and instruction lines

- 0 = Invalidate all data lnes and instruction lines that are not locked

- bit 15-10 Unimplemented: Write '0'; ignore read

- bit 9-8 DCSZ<1:0>: Data Cache Size in Lines bits

- 11 = Enable data caching with a size of 4 Lines

- 10 = Enable data caching with a size of 2 Lines

- 01 = Enable data caching with a size of 1 Line

- 00 = Disable data caching

Changing these bits induce all lines to be reinitialized to the "invalid" state.

bit 7-6 **Unimplemented:** Write '0'; ignore read

#### bit 5-4 **PREFEN<1:0>:** Predictive Prefetch Enable bits

- 11 = Enable predictive prefetch for both cacheable and non-cacheable regions

- 10 = Enable predictive prefetch for non-cacheable regions only

- 01 = Enable predictive prefetch for cacheable regions only

- 00 = Disable predictive prefetch

- bit 3 Unimplemented: Write '0'; ignore read

#### bit 2-0 PFMWS<2:0>: PFM Access Time Defined in Terms of SYSLK Wait States bits

- 111 = Seven Wait states

- 110 = Six Wait states

- 101 = Five Wait states

- 100 = Four Wait states

- 011 = Three Wait states

- 010 = Two Wait states

- 001 = One Wait state

- 000 = Zero Wait state

## TABLE 12-1: INPUT PIN SELECTION

| Peripheral Pin | [pin name]R SFR       | [pin name]R bits | [ <i>pin name</i> ]R Value to<br>RPn Pin Selection                                      |  |

|----------------|-----------------------|------------------|-----------------------------------------------------------------------------------------|--|

| INT3           | INT3R                 | INT3R<3:0>       | 0000 = RPD2<br>0001 = RPG8                                                              |  |

| T2CK           | T2CKR                 | T2CKR<3:0>       | 0010 = RPF4<br>0011 = RPD10                                                             |  |

| IC3            | IC3R                  | IC3R<3:0>        | 0100 = RPF1<br>0101 = RPB9                                                              |  |

| U1RX           | U1RXR                 | U1RXR<3:0>       |                                                                                         |  |

| U2RX           | U2RXR                 | U2RXR<3:0>       | 1000 = Ri B3<br>1001 = Reserved<br>1010 = RPC1 <sup>(3)</sup>                           |  |

| U5CTS          | U5CTSR <sup>(3)</sup> | U5CTSR<3:0>      | 1011 = RPD14 <sup>(3)</sup><br>1100 = RPG1 <sup>(3)</sup>                               |  |

| REFCLKI        | REFCLKIR              | REFCLKIR<3:0>    | 1101 = RPA14 <sup>(3)</sup><br>1110 = Reserved<br>1111 = RPF2 <sup>(1)</sup>            |  |

| INT4           | INT4R                 | INT4R<3:0>       | 0000 = RPD3<br>0001 = RPG7                                                              |  |

| T5CK           | T5CKR                 | T5CKR<3:0>       | 0010 = RPF5<br>0011 = RPD11                                                             |  |

| IC4            | IC4R                  | IC4R<3:0>        | 0100 = RPF0<br>0101 = RPB1                                                              |  |

| U3RX           | U3RXR                 | U3RXR<3:0>       |                                                                                         |  |

| U4CTS          | U4CTSR                | U4CTSR<3:0>      | 1001 = Reserved<br>1010 = RPC4 <sup>(3)</sup>                                           |  |

| SDI1           | SDI1R                 | SDI1R<3:0>       | 1011 = RPD15 <sup>(3)</sup><br>1100 = RPG0 <sup>(3)</sup>                               |  |

| SDI2           | SDI2R                 | SDI2R<3:0>       | 1101 = RPA15 <sup>(3)</sup><br>1110 = RPF2 <sup>(1)</sup><br>1111 = RPF7 <sup>(2)</sup> |  |

| INT2           | INT2R                 | INT2R<3:0>       | 0000 = RPD9<br>0001 = RPG6                                                              |  |

| T4CK           | T4CKR                 | T4CKR<3:0>       | 0010 = RPB8<br>0011 = RPB15                                                             |  |

| IC2            | IC2R                  | IC2R<3:0>        | 0100 = RPD4<br>0101 = RPB0                                                              |  |

| IC5            | IC5R                  | IC5R<3:0>        | - 0110 = RPE3<br>0111 = RPB7<br>1000 = Reserved                                         |  |

| U1CTS          | U1CTSR                | U1CTSR<3:0>      | 1000 = Reserved<br>1001 = RPF12 <sup>(3)</sup><br>1010 = RPD12 <sup>(3)</sup>           |  |

| U2CTS          | U2CTSR                | U2CTSR<3:0>      | 1011 = RPF8 <sup>(3)</sup><br>1100 = RPC3 <sup>(3)</sup>                                |  |

| SS1            | SS1R                  | SS1R<3:0>        | 1101 = RPE9 <sup>(3)</sup><br>1110 = Reserved                                           |  |

|                | SS1R                  | SS1R<3:0>        | 1110 <b>–</b> Reserved<br>1111 <b>–</b> RPB2                                            |  |

**Note 1:** This selection is not available on 64-pin USB devices.

2: This selection is only available on 100-pin General Purpose devices.

3: This selection is not available on 64-pin USB and General Purpose devices.

4: This selection is only available on General Purpose devices.

## TABLE 12-17: PERIPHERAL PIN SELECT INPUT REGISTER MAP

| SSS                         |                  |               |       |       |       |       |       |       |      | Bi   | ts   |      |      |      |      |       |            |      |            |

|-----------------------------|------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|------------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1       | 16/0 | All Resets |

| FA04                        | INT1R            | 31:16         | Ι     | _     | _     | _     | _     | _     |      | _    | —    | —    | _    |      | _    |       |            |      | 0000       |

|                             |                  | 15:0          | -     | _     | —     | _     | _     | _     | _    | —    | _    | —    | —    | _    |      | INT1F | <3:0>      |      | 0000       |

| FA08                        | INT2R            | 31:16         | _     | _     | _     | _     |       |       | _    | _    | _    | _    | _    |      |      |       |            | —    | 0000       |

|                             |                  | 15:0          | _     |       |       |       | _     |       |      |      | _    | _    |      |      |      | INT2F | (<3:0>     |      | 0000       |

| FA0C                        | INT3R            | 31:16<br>15:0 | _     |       |       |       |       |       |      |      |      | _    | _    |      |      | INT3F |            |      | 0000       |

|                             |                  | 31:16         | _     |       |       |       |       |       |      |      | _    |      | _    |      | _    |       |            | _    | 0000       |

| FA10                        | INT4R            | 15:0          | _     | _     |       |       |       |       |      |      |      |      |      |      |      | INT4F |            |      | 0000       |

|                             |                  | 31:16         | _     | _     | _     |       |       |       |      |      | _    | _    |      |      |      | _     | _          |      | 0000       |

| FA18                        | T2CKR            | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | T2CKF | २<3:0>     |      | 0000       |

|                             |                  | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _          | _    | 0000       |

| FA1C                        | T3CKR            | 15:0          | _     | _     | _     | _     | _     | _     |      | _    | _    | —    | —    |      |      | T3CKF | २<3:0>     |      | 0000       |

| FA20                        | T4CKR            | 31:16         | _     | _     | —     | —     | _     |       |      | _    | —    | -    | _    | _    |      |       |            |      | 0000       |

| FAZU                        | 14CKK            | 15:0          | _     | _     | —     | —     | _     | _     | _    | —    | _    | _    | _    | _    |      | T4CKF | R<3:0>     |      | 0000       |

| FA24                        | T5CKR            | 31:16         | —     | —     | _     | _     | _     | _     | _    | —    | —    | _    | —    | _    | —    | —     | —          |      | 0000       |

| 1712-7                      | TOORIC           | 15:0          | _     | _     | _     | _     | _     |       |      | _    | _    | _    | _    |      |      | T5CKF | R<3:0>     |      | 0000       |

| FA28                        | IC1R             | 31:16         | -     | —     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    | —    | —     | —          | _    | 0000       |

|                             | -                | 15:0          | -     | _     | _     | _     | _     |       |      |      | _    | —    | —    |      |      | IC1R  | <3:0>      |      | 0000       |

| FA2C                        | IC2R             | 31:16         | _     | _     | _     | _     | _     |       |      | _    | _    | _    | _    | _    | —    | -     | —          | —    | 0000       |

|                             |                  | 15:0<br>31:16 | _     |       |       |       |       |       |      | _    |      | _    | _    |      |      | IC2R  |            |      | 0000       |

| FA30                        | IC3R             | 15:0          | _     |       | _     |       |       |       |      |      | _    |      | _    |      | —    | IC3R  | —<br><3·0> | _    | 0000       |

|                             |                  | 31:16         | _     | _     |       | _     |       |       |      | _    | _    | _    |      |      |      | _     |            | _    | 0000       |

| FA34                        | IC4R             | 15:0          | _     | _     | _     |       |       |       |      |      | _    | _    |      |      |      | IC4R  | <3:0>      |      | 0000       |

|                             |                  | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _          | _    | 0000       |

| FA38                        | IC5R             | 15:0          | _     | _     | _     | _     | _     |       |      | _    | _    | _    | _    |      |      | IC5R  | <3:0>      |      | 0000       |

| <b>FA 10</b>                | 0.0515           | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | —    | _    | —    | —     | —          | _    | 0000       |

| FA48                        | OCFAR            | 15:0          | _     | _     |       |       |       |       |      |      |      | _    | _    |      |      | OCFA  | R<3:0>     |      | 0000       |

| FA50                        | U1RXR            | 31:16         | —     | —     | _     | —     | _     | _     | _    | _    | _    | —    | —    | _    | —    | —     | —          |      | 0000       |

| FASU                        | UIKAK            | 15:0          | _     | _     | _     | _     |       |       |      | _    | _    | —    | -    |      |      | U1RXI | R<3:0>     |      | 0000       |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

DS60001185F-page 159

## REGISTER 18-1: SPIxCON: SPI CONTROL REGISTER (CONTINUED)

- bit 4 **DISSDI:** Disable SDI bit 1 = SDI pin is not used by the SPI module (pin is controlled by PORT function)

- 0 = SDI pin is controlled by the SPI module

- bit 3-2 STXISEL<1:0>: SPI Transmit Buffer Empty Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is not full (has one or more empty elements)

- 10 = Interrupt is generated when the buffer is empty by one-half or more

- 01 = Interrupt is generated when the buffer is completely empty

- 00 = Interrupt is generated when the last transfer is shifted out of SPISR and transmit operations are complete

- bit 1-0 SRXISEL<1:0>: SPI Receive Buffer Full Interrupt Mode bits

- 11 = Interrupt is generated when the buffer is full

- 10 = Interrupt is generated when the buffer is full by one-half or more

- 01 = Interrupt is generated when the buffer is not empty

- 00 = Interrupt is generated when the last word in the receive buffer is read (i.e., buffer is empty)

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read or write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit can only be written when the ON bit = 0.

- **3:** This bit is not used in the Framed SPI mode. The user should program this bit to '0' for the Framed SPI mode (FRMEN = 1).

- 4: When AUDEN = 1, the SPI module functions as if the CKP bit is equal to '1', regardless of the actual value of CKP.

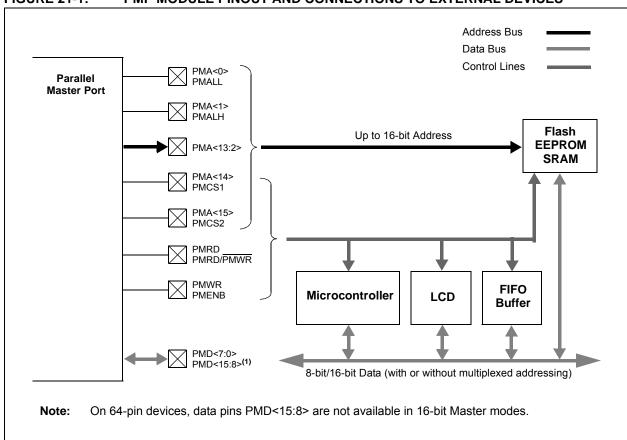

## 21.0 PARALLEL MASTER PORT (PMP)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 13. "Parallel Master Port (PMP)" (DS60001128), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PMP is a parallel 8-bit/16-bit input/output module specifically designed to communicate with a wide variety of parallel devices, such as communications peripherals, LCDs, external memory devices and microcontrollers. Because the interface to parallel peripherals varies significantly, the PMP module is highly configurable. The following are key features of the PMP module:

- 8-bit,16-bit interface

- · Up to 16 programmable address lines

- · Up to two Chip Select lines

- Programmable strobe options

- Individual read and write strobes, or

- Read/write strobe with enable strobe

- Address auto-increment/auto-decrement

- Programmable address/data multiplexing

- · Programmable polarity on control signals

- Parallel Slave Port support

- Legacy addressable

- Address support

- 4-byte deep auto-incrementing buffer

- · Programmable Wait states

- Operate during CPU Sleep and Idle modes

- Fast bit manipulation using CLR, SET and INV registers

- Freeze option for in-circuit debugging

Note: On 64-pin devices, data pins PMD<15:8> are not available in 16-bit Master modes.

## FIGURE 21-1: PMP MODULE PINOUT AND CONNECTIONS TO EXTERNAL DEVICES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5  | Bit<br>28/20/12/4   | Bit<br>27/19/11/3   | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|--------------------|---------------------|---------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0                | U-0                 | U-0                 | U-0               | U-0              | U-0              |

| 31.24        | —                 | —                 | —                  | —                   | —                   | _                 | —                | _                |

| 22:16        | U-0               | U-0               | U-0                | U-0                 | U-0                 | U-0               | U-0              | U-0              |

| 23:16        | —                 | —                 | —                  | —                   | —                   | _                 | —                | _                |

| 15:8         | R/W-0             | U-0               | R/W-0              | R/W-0               | R/W-0               | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | ON <sup>(1)</sup> | —                 | SIDL               | ADRMU               | JX<1:0>             | PMPTTL            | PTWREN           | PTRDEN           |

| 7.0          | R/W-0             | R/W-0             | R/W-0              | R/W-0               | R/W-0               | U-0               | R/W-0            | R/W-0            |

| 7:0          | CSF<              | 1:0> <b>(2)</b>   | ALP <sup>(2)</sup> | CS2P <sup>(2)</sup> | CS1P <sup>(2)</sup> | _                 | WRSP             | RDSP             |

#### REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Parallel Master Port Enable bit<sup>(1)</sup>

- 1 = PMP is enabled

- 0 = PMP is disabled, no off-chip access performed

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12-11 ADRMUX<1:0>: Address/Data Multiplexing Selection bits

- 11 = Lower 8 bits of address are multiplexed on PMD<15:0> pins

- 10 = All 16 bits of address are multiplexed on PMD<7:0> pins

- 01 = Lower 8 bits of address are multiplexed on PMD<7:0> pins, upper bits are on PMA<15:8>

- 00 = Address and data appear on separate pins

- bit 10 PMPTTL: PMP Module TTL Input Buffer Select bit

- 1 = PMP module uses TTL input buffers

- 0 = PMP module uses Schmitt Trigger input buffer

- bit 9 **PTWREN:** Write Enable Strobe Port Enable bit

- 1 = PMWR/PMENB port is enabled

- 0 = PMWR/PMENB port is disabled

- bit 8 **PTRDEN:** Read/Write Strobe Port Enable bit

- 1 = PMRD/PMWR port is enabled

- 0 = PMRD/PMWR port is disabled

- bit 7-6 **CSF<1:0>:** Chip Select Function bits<sup>(2)</sup>

- 11 = Reserved

- 10 = PMCS1 and PMCS2 function as Chip Select

- 01 = PMCS1 functions as address bit 14; PMCS2 functions as Chip Select

- 00 = PMCS1 and PMCS2 function as address bits 14 and 15, respectively

- bit 5 ALP: Address Latch Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMALL and PMALH)

- $0 = \text{Active-low} (\overline{\text{PMALL}} \text{ and } \overline{\text{PMALH}})$

- bit 4 **CS2P:** Chip Select 0 Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMCS2)

- $0 = \text{Active-low}(\overline{\text{PMCS2}})$

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

## PIC32MX330/350/370/430/450/470

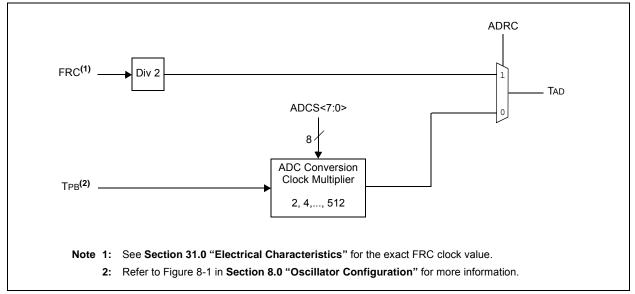

## FIGURE 23-2: ADC CONVERSION CLOCK PERIOD BLOCK DIAGRAM

| DC CHARAG  |                     | ICS         | Standard Operating Conditions: 2.3V to 3.6V (unless otherwise stated)Operating temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial $-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |                      |                         |  |  |

|------------|---------------------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|-------------------------|--|--|

| Param. No. | Тур. <sup>(2)</sup> | Max.        | Units                                                                                                                                                                                                                                                   |                      | Conditions              |  |  |

| PIC32MX350 | )F256 De            | evices O    | nly                                                                                                                                                                                                                                                     |                      |                         |  |  |

| Power-Dow  | n Curren            | nt (IPD) (N | lote 1)                                                                                                                                                                                                                                                 |                      |                         |  |  |

| DC40k      | 38                  | 80          | μA                                                                                                                                                                                                                                                      | -40°C                |                         |  |  |

| DC40I      | 57                  | 80          | μΑ                                                                                                                                                                                                                                                      | +25°C                | Base Power-Down Current |  |  |

| DC40n      | 220                 | 352         | μΑ                                                                                                                                                                                                                                                      | +85°C                | Base Fowel-Down Current |  |  |

| DC40m      | 513                 | 749         | μA                                                                                                                                                                                                                                                      | +105°C               |                         |  |  |

| PIC32MX450 | )F256 De            | evices O    | nly                                                                                                                                                                                                                                                     |                      |                         |  |  |

| Power-Down | n Curren            | nt (IPD) (N | lote 1)                                                                                                                                                                                                                                                 |                      |                         |  |  |

| DC40k      | 26                  | 42          | μΑ                                                                                                                                                                                                                                                      | -40°C                |                         |  |  |

| DC40o      | 26                  | 42          | μA                                                                                                                                                                                                                                                      | 0°C <b>(5)</b>       |                         |  |  |

| DC40I      | 26                  | 42          | μA                                                                                                                                                                                                                                                      | +25°C                | Base Power-Down Current |  |  |

| DC40p      | 250                 | 352         | μA                                                                                                                                                                                                                                                      | +70°C <sup>(5)</sup> |                         |  |  |

| DC40n      | 250                 | 352         | μA                                                                                                                                                                                                                                                      | +85°C                |                         |  |  |

| DC40m      | 513                 | 749         | μA                                                                                                                                                                                                                                                      | +105°C               |                         |  |  |

## TABLE 31-7: DC CHARACTERISTICS: POWER-DOWN CURRENT (IPD) (CONTINUED)

Note 1: The test conditions for IPD measurements are as follows:

- Oscillator mode is EC (for 8 MHz and below) and EC+PLL (for above 8 MHz) with OSC1 driven by external square wave from rail-to-rail, (OSC1 input clock input over/undershoot < 100 mV required)

- OSC2/CLKO is configured as an I/O input pin

- USB PLL oscillator is disabled if the USB module is implemented, PBCLK divisor = 1:8

- CPU is in Sleep mode, program Flash memory Wait states = 7, Program Cache and Prefetch are disabled and SRAM data memory Wait states = 1

- No peripheral modules are operating, (ON bit = 0), but the associated PMD bit is set

- WDT, Clock Switching, Fail-Safe Clock Monitor, and Secondary Oscillator are disabled

- All I/O pins are configured as inputs and pulled to Vss

- MCLR = VDD

- · RTCC and JTAG are disabled

- Voltage regulator is off during Sleep mode (VREGS bit in the RCON register = 0)

- 2: Data in the "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

- 3: The ∆ current is the additional current consumed when the module is enabled. This current should be added to the base IPD current.

- 4: Test conditions for ADC module differential current are as follows: Internal ADC RC oscillator enabled.

- 5: 120 MHz commercial devices only (0°C to +70°C).

| AC CHARACTERISTICS |         |                                   | $ \begin{array}{ c c c c c } \hline Standard Operating Conditions: 2.3V to 3.6V \\ \hline (unless otherwise stated) \\ \hline Operating temperature & 0^{\circ}C \leq TA \leq +70^{\circ}C \text{ for Commercia} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \text{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \text{ for V-temp} \\ \hline \end{array} $ |      |      |       |                                                                                   |  |  |

|--------------------|---------|-----------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|-------|-----------------------------------------------------------------------------------|--|--|

| Param.<br>No.      | Symbol  | Characteristics <sup>(1)</sup>    | Min.                                                                                                                                                                                                                                                                                                                                                                    | Тур. | Max. | Units | Conditions                                                                        |  |  |

| USB313             | VUSB3V3 | USB Voltage                       | 3.0                                                                                                                                                                                                                                                                                                                                                                     |      | 3.6  | V     | Voltage on VUSB3V3<br>must be in this range<br>for proper USB<br>operation        |  |  |

| USB315             | VILUSB  | Input Low Voltage for USB Buffer  | —                                                                                                                                                                                                                                                                                                                                                                       | _    | 0.8  | V     | —                                                                                 |  |  |

| USB316             | VIHUSB  | Input High Voltage for USB Buffer | 2.0                                                                                                                                                                                                                                                                                                                                                                     | —    | _    | V     | —                                                                                 |  |  |

| USB318             | VDIFS   | Differential Input Sensitivity    | —                                                                                                                                                                                                                                                                                                                                                                       |      | 0.2  | V     | The difference<br>between D+ and D-<br>must exceed this value<br>while VCM is met |  |  |

| USB319             | VCM     | Differential Common Mode Range    | 0.8                                                                                                                                                                                                                                                                                                                                                                     | _    | 2.5  | V     | —                                                                                 |  |  |

| USB320             | Zout    | Driver Output Impedance           | 28.0                                                                                                                                                                                                                                                                                                                                                                    | —    | 44.0 | Ω     | —                                                                                 |  |  |

| USB321             | Vol     | Voltage Output Low                | 0.0                                                                                                                                                                                                                                                                                                                                                                     | _    | 0.3  | V     | 1.425 kΩ load<br>connected to VUSB3V3                                             |  |  |

| USB322             | Vон     | Voltage Output High               | 2.8                                                                                                                                                                                                                                                                                                                                                                     | —    | 3.6  | V     | 14.25 k $\Omega$ load connected to ground                                         |  |  |

## TABLE 31-41: OTG ELECTRICAL SPECIFICATIONS

Note 1: These parameters are characterized, but not tested in manufacturing.

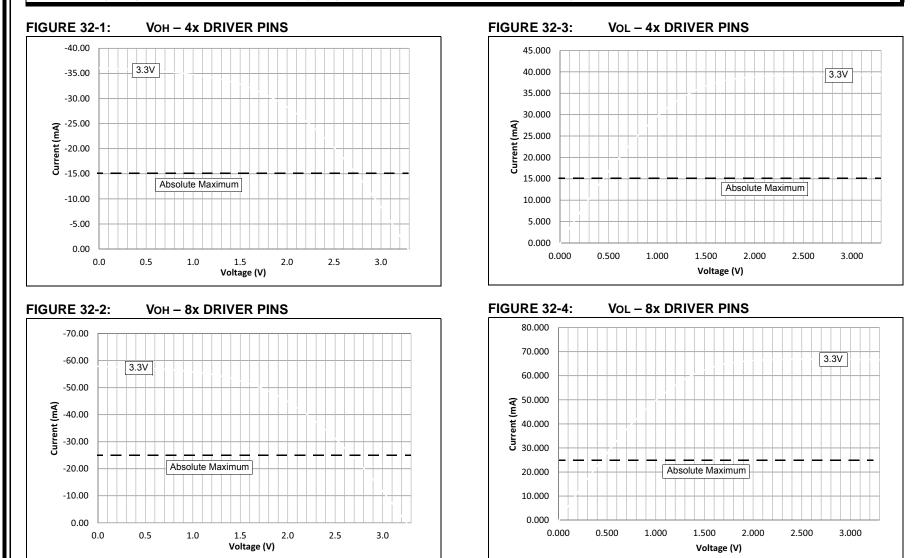

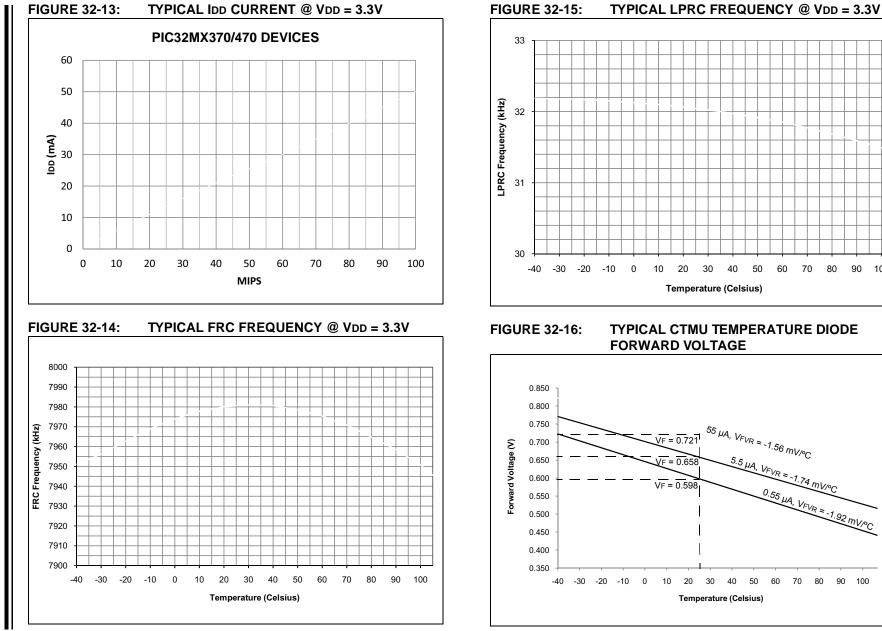

## 32.0 DC AND AC DEVICE CHARACTERISTICS GRAPHS

Note: The graphs provided following this note are a statistical summary based on a limited number of samples and are provided for design guidance purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

PIC32MX330/350/370/430/450/470

100

# PIC32MX330/350/370/430/450/470

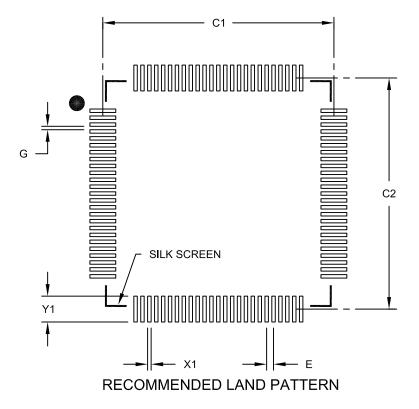

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | MILLIMETERS |      |          |      |

|---------------------------|-------------|------|----------|------|

| Dimensior                 | ı Limits    | MIN  | NOM      | MAX  |

| Contact Pitch             | E           |      | 0.40 BSC |      |

| Contact Pad Spacing       | C1          |      | 13.40    |      |

| Contact Pad Spacing       | C2          |      | 13.40    |      |

| Contact Pad Width (X100)  | X1          |      |          | 0.20 |

| Contact Pad Length (X100) | Y1          |      |          | 1.50 |

| Distance Between Pads     | G           | 0.20 |          |      |

Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B

## APPENDIX A: REVISION HISTORY

## Revision A (July 2012)

This is the initial released version of the document.

## Revision B (April 2013)

| Note: | The status of this data sheet was updated<br>to Preliminary; however, any electrical<br>specifications listed for PIC32MX370/470 |

|-------|----------------------------------------------------------------------------------------------------------------------------------|

|       | devices is to be considered Advance                                                                                              |

|       | Information and is marked accordingly.                                                                                           |

This revision includes the following updates, as shown in Table A-1.

## TABLE A-1: MAJOR SECTION UPDATES

| Section                                                                                    | Update Description                                                                                             |

|--------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 512                                                        | SRAM was changed from 32 KB to 64 KB.                                                                          |

| KB Flash and 128 KB SRAM) with<br>Audio/Graphics/Touch (HMI), USB,<br>and Advanced Analog" | Data Memory (KB) was changed from 32 to 64 for the following devices (see Table 1):                            |

|                                                                                            | • PIC32MX350F256H                                                                                              |

|                                                                                            | • PIC32MX350F256L                                                                                              |

|                                                                                            | • PIC32MX450F256H                                                                                              |

|                                                                                            | • PIC32MX450F256L                                                                                              |

|                                                                                            | The following devices were added:                                                                              |

|                                                                                            | • PIC32MX370F512H                                                                                              |

|                                                                                            | • PIC32MX370F512L                                                                                              |

|                                                                                            | • PIC32MX470F512H                                                                                              |

|                                                                                            | • PIC32MX470F512L                                                                                              |

| 4.0 "Memory Organization"                                                                  | The Memory Map for Devices with 256 KB of Program Memory was updated (see Figure 4-3).                         |

|                                                                                            | The Memory Map for Devices with 512 KB of Program Memory was added (see Figure 4-4).                           |

| 7.0 "Interrupt Controller"                                                                 | Updated the Interrupt IRQ, Vector and Bit Locations (see Table 7-1).                                           |

| 20.0 "Parallel Master Port (PMP)"                                                          | Added the CS2 bit and updated the ADDR bits in the Parallel Port Address register (see Register 20-3).         |

| 27.0 "Special Features"                                                                    | Updated the PWP bit in the Device Configuration Word 3 register (see Register 27-4).                           |

| 30.0 "Electrical Characteristics"                                                          | Note 2 in the DC Characteristics: Operating Current (IDD) were updated (see Table 30-5).                       |

|                                                                                            | Note 1 in the DC Characteristics: Idle Current (IIDLE) were updated (see Table 30-6).                          |

|                                                                                            | Note 1 in the DC Characteristics: Power-down Current (IPD) were updated (see Table 30-7).                      |

|                                                                                            | Updated Program Memory values for parameters D135 (Tww), D136 (Trw), and D137 (TPE and TCE) (see Table 30-12). |

| 31.0 "DC and AC Device<br>Characteristics Graphs"                                          | New IDD, IIDLE, and IPD current graphs were added for PIC32MX330/430 devices and PIC32MX350/450 devices.       |

## **Revision C (October 2013)**

This revision includes the following updates, as listed in Table A-2.

## TABLE A-2: MAJOR SECTION UPDATES

| Section                                                               | Update Description                                                                                                                                                                |

|-----------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| "32-bit Microcontrollers (up to 512<br>KB Flash and 128 KB SRAM) with | The Operating Conditions and Core sections were updated in support of 100 MHz (-40°C to +85°C) devices.                                                                           |

| Audio/Graphics/Touch (HMI), USB,<br>and Advanced Analog"              | Added Notes 2 and 3 regarding the conductive thermal pad to the 124-pin VTLA pin diagrams.                                                                                        |

| 2.0 "Guidelines for Getting Started                                   | Updated the recommended minimum connection (see Figure 2-1).                                                                                                                      |

| with 32-bit MCUs"                                                     | Added 2.10 "Sosc Design Recommendation".                                                                                                                                          |

| 20.0 "Parallel Master Port (PMP)"                                     | Updated the Parallel Port Control register, PMCON (see Register 20-1).                                                                                                            |

|                                                                       | Updated the Parallel Port Mode register, PMMODE (see Register 20-2).                                                                                                              |

|                                                                       | Updated the Parallel Port Pin Enable register, PMAEN (see Register 20-4).                                                                                                         |

| 30.0 "Electrical Characteristics"                                     | Removed Note 4 from the Absolute Maximum Ratings.                                                                                                                                 |

|                                                                       | The maximum frequency for parameter DC5 In Operating MIPS vs. Voltage was changed to 100 MHz (see Table 30-1).                                                                    |

|                                                                       | Parameter DC25a was added to DC Characteristics: Operating Current (IDD) (see Table 30-5).                                                                                        |

|                                                                       | Parameter DC34c was added to DC Characteristics: Idle Current (IIDLE) (see Table 30-5).                                                                                           |

|                                                                       | Added parameters for PIC32MX370/470 devices and removed Note 5 from DC Characteristics: Power-Down Current (IPD) (see Table 30-7).                                                |

|                                                                       | Updated the Minimum, Typical, and Maximum values and added a reference to Note 3 for parameter DI30 (ICNPU) in DC Characteristics: I/O Pin Input Specifications (see Table 30-8). |

|                                                                       | The SYSCLK values for all required Flash Wait states were updated (see Table 30-13).                                                                                              |

|                                                                       | Added parameter DO50A (Csosc) to the Capacitive Loading Requirements on Output Pins (see Table 30-16).                                                                            |

|                                                                       | Updated the maximum values for parameter OS10, and the Characteristics definition of parameter OS42 (GM) in the External Clock Timing Characteristics (see Table 30-17).          |

| 31.0 "DC and AC Device<br>Characteristics Graphs"                     | Updated the IPD, IIDLE, and IDD graphs, and added new graphs for the PIC32MX370/470 devices (see Figure 31-5 through Figure 31-13).                                               |

## Revision D (March 2015)

This revision includes the following updates, as listed in Table A-3.

## TABLE A-3: MAJOR SECTION UPDATES

| Section                                                                                                                               | Update Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| "32-bit Microcontrollers (up to<br>512 KB Flash and 128 KB<br>SRAM) with Audio/Graphics/<br>Touch (HMI), USB, and<br>Advanced Analog" | 100 MHz and 120 MHz operation information was added.<br>Pins 59 through 63 of the 64-pin QFN and TQFP pin diagrams were updated.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |

| 2.0 "Guidelines for Getting<br>Started with 32-bit MCUs"                                                                              | Added 2.8.1 "Crystal Oscillator Design Consideration".                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |

| 12.0 "I/O Ports"                                                                                                                      | The Block Diagram of a Typical Multiplexed Port Structure was updated (see Figure 12-1).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

| 21.0 "Parallel Master Port<br>(PMP)"                                                                                                  | The PMADDR: Parallel Port Address Register was updated (see Register 21-3).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 31.0 "Electrical<br>Characteristics"                                                                                                  | <ul> <li>Specifications for 120 MHz operation were added to the following tables:</li> <li>Table 31-1: "Operating MIPS vs. Voltage"</li> <li>Table 31-5: "DC Characteristics: Operating Current (IDD)"</li> <li>Table 31-6: "DC Characteristics: Idle Current (IDLE)"</li> <li>Table 31-7: "DC Characteristics: Idle Current (IPD)"</li> <li>Table 31-13: "DC Characteristics: Program Flash Memory Wait State"</li> <li>Table 31-18: "External Clock Timing Requirements"</li> <li>The unit of measure for IIDLE Current parameters DC37a, DC37b, and DC37c were updated (see Table 31-6).</li> <li>Parameter D312 (TSET) was removed from the Comparator Specifications (see Table 31-14).</li> <li>Comparator Voltage Reference Specifications were added (see Table 31-15).</li> <li>Parameter USB321 (VOL) in the OTG Electrical Specifications was updated (see Table 31-41).</li> </ul> |  |  |  |  |