#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                          |

|----------------------------|-----------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                      |

| Core Size                  | 32-Bit Single-Core                                                                |

| Speed                      | 120MHz                                                                            |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                     |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                        |

| Number of I/O              | 85                                                                                |

| Program Memory Size        | 512KB (512K x 8)                                                                  |

| Program Memory Type        | FLASH                                                                             |

| EEPROM Size                |                                                                                   |

| RAM Size                   | 128K x 8                                                                          |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                       |

| Data Converters            | A/D 28x10b                                                                        |

| Oscillator Type            | Internal                                                                          |

| Operating Temperature      | 0°C ~ 70°C (TA)                                                                   |

| Mounting Type              | Surface Mount                                                                     |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                  |

| Supplier Device Package    | 124-VTLA (9x9)                                                                    |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx470f512lt-120-tl |

|                            |                                                                                   |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

### TABLE 6: PIN NAMES FOR 124-PIN DEVICES (CONTINUED)

| 124               | -PIN VTLA (BOTTOM VIEW) <sup>(1,2,3,4,5)</sup> A17                       |                   |                  | A34                       |

|-------------------|--------------------------------------------------------------------------|-------------------|------------------|---------------------------|

|                   | AT/                                                                      |                   | B13 B29          | Conductive<br>Thermal Pad |

|                   | PIC32MX330F064L<br>PIC32MX350F128L<br>PIC32MX350F256L<br>PIC32MX370F512L |                   | B1 E<br>B56      | 341<br>A51                |

|                   | Polarity I                                                               | A1<br>tor         | A68              |                           |

| Package<br>Bump # | Full Pin Name                                                            | Package<br>Bump # |                  | Full Pin Name             |

| B7                | MCLR                                                                     | B32               | SDA2/RA3         |                           |

| B8                | Vss                                                                      | B33               | TDO/RA5          |                           |

| B9                | TMS/CTED1/RA0                                                            | B34               | OSC1/CLKI/RC12   |                           |

| B10               | RPE9/RE9                                                                 | B35               | No Connect       |                           |

| B11               | AN4/C1INB/RB4                                                            | B36               | RPA14/RA14       |                           |

| B12               | Vss                                                                      | B37               | RPD8/RTCC/RD8    |                           |

| B13               | PGEC3/AN2/C2INB/RPB2/CTED13/RB2                                          | B38               | RPD10/PMCS2/RD10 | )                         |

| B14               | PGED1/AN0/RPB0/RB0                                                       | B39               | RPD0/RD0         |                           |

| B15               | No Connect                                                               | B40               | SOSCO/RPC14/T1Ck |                           |

| B16               | PGED2/AN7/RPB7/CTED3/RB7                                                 | B41               | Vss              |                           |

| B17               | VREF+/CVREF+/PMA6/RA10                                                   | B42               | AN25/RPD2/RD2    |                           |

| B18               | AVss                                                                     | B43               | RPD12/PMD12/RD12 |                           |

| B19               | AN9/RPB9/CTED4/RB9                                                       | B44               | RPD4/PMWR/RD4    |                           |

| B20               | AN11/PMA12/RB11                                                          | B45               | PMD14/RD6        |                           |

| B21               | VDD                                                                      | B46               | No Connect       |                           |

| B22               | RPF13/RF13                                                               | B47               | No Connect       |                           |

| B23               | AN12/PMA11/RB12                                                          | B48               | VCAP             |                           |

| B24               | AN14/RPB14/CTED5/PMA1/RB14                                               | B49               | RPF0/PMD11/RF0   |                           |

| B25               | Vss                                                                      | B50               | RPG1/PMD9/RG1    |                           |

| B26               | RPD14/RD14                                                               | B51               | TRCLK/RA6        |                           |

| B27               | RPF4/PMA9/RF4                                                            | B52               | PMD0/RE0         |                           |

| B28               | No Connect                                                               | B53               | Vdd              |                           |

| B29               | RPF8/RF8                                                                 | B54               | TRD2/RG14        |                           |

| B30               | RPF6/SCKI/INT0/RF6                                                       | B55               | TRD0/RG13        |                           |

| B31               | SCL1/RG2                                                                 | B56               | RPE3/CTPLS/PMD3/ | RE3                       |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx), with the exception of RF6, can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: RPF6 (bump B30) and RPF7 (bump A37) are only remappable for input functions.

4: Shaded package bumps are 5V tolerant.

5: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

#### TABLE 1-1: PINOUT I/O DESCRIPTIONS

|          |                        | Pin Numb        | er                                |             |                |                                                                                                                                                                                                   |  |  |  |  |  |

|----------|------------------------|-----------------|-----------------------------------|-------------|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Pin Name | 64-pin<br>QFN/<br>TQFP | 100-pin<br>TQFP | 124-pin<br>VTLA                   | Pin<br>Type | Buffer<br>Type | Description                                                                                                                                                                                       |  |  |  |  |  |

| AN0      | 16                     | 25              | B14                               |             | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN1      | 15                     | 24              | A15                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN2      | 14                     | 23              | B13                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN3      | 13                     | 22              | A13                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN4      | 12                     | 21              | B11                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN5      | 11                     | 20              | A12                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN6      | 17                     | 26              | A20                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN7      | 18                     | 27              | B16                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN8      | 21                     | 32              | A23                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN9      | 22                     | 33              | B19                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN10     | 23                     | 34              | A24                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN11     | 24                     | 35              | B20                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN12     | 27                     | 41              | B23                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN13     | 28                     | 42              | A28                               | I           | Analog         | Analog input channels.                                                                                                                                                                            |  |  |  |  |  |

| AN14     | 29                     | 43              | B24                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN15     | 30                     | 44              | A29                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN16     | 4                      | 10              | A7                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN17     | 5                      | 11              | B6                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN18     | 6                      | 12              | A8                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN19     | 8                      | 14              | A9                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN20     | 62                     | 98              | A66                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN21     | 64                     | 100             | A67                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN22     | 1                      | 3               | B2                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN23     | 2                      | 4               | A4                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN24     | 49                     | 76              | A52                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN25     | 50                     | 77              | B42                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN26     | 51                     | 78              | A53                               | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| AN27     | 3                      | 5               | B3                                | I           | Analog         |                                                                                                                                                                                                   |  |  |  |  |  |

| CLKI     | 39                     | 63              | B34                               | I           | ST/CMOS        | External clock source input. Always associated with OSC1 pin function.                                                                                                                            |  |  |  |  |  |

| CLKO     | 40                     | 64              | A42                               | 0           | _              | Oscillator crystal output. Connects to crystal or reso-<br>nator in Crystal Oscillator mode. Optionally functions<br>as CLKO in RC and EC modes. Always associated<br>with the OSC2 pin function. |  |  |  |  |  |

| OSC1     | 39                     | 63              | B34                               | I           | ST/CMOS        | Oscillator crystal input. ST buffer when configured in RC mode; CMOS otherwise.                                                                                                                   |  |  |  |  |  |

| OSC2     | 40                     | 64              | A42                               | 0           | _              | Oscillator crystal output. Connects to crystal or reso-<br>nator in Crystal Oscillator mode. Optionally functions<br>as CLKO in RC and EC modes.                                                  |  |  |  |  |  |

| SOSCI    | 47                     | 73              | A47                               | I           | ST/CMOS        | 32.768 kHz low-power oscillator crystal input; CMOS otherwise.                                                                                                                                    |  |  |  |  |  |

| SOSCO    | 48                     | 74              | B40                               | 0           | —              | 32.768 kHz low-power oscillator crystal output.                                                                                                                                                   |  |  |  |  |  |

| -        | ST = Schm              |                 | tible input or o<br>out with CMOS |             |                | alog = Analog input P = Power<br>= Output I = Input                                                                                                                                               |  |  |  |  |  |

TTL = TTL input buffer

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

**3:** This pin is not available on 64-pin devices.

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS50001765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS50001764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" DS50001616

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) DS50001749

## 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

### 2.7 Trace

The trace pins can be connected to a hardware trace-enabled programmer to provide a compressed real-time instruction trace. When used for trace, the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

## 2.8 External Oscillator Pins

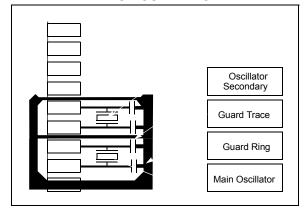

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

#### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6       | Bit<br>29/21/13/5       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3    | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

|--------------|-------------------|-------------------------|-------------------------|-------------------|----------------------|-------------------|-----------------------|-------------------------|

| 31:24        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 31.24        | _                 | _                       | _                       |                   | —                    | _                 | _                     | —                       |

| 23:16        | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 23.10        | _                 | _                       | _                       |                   | —                    | _                 | _                     | —                       |

| 15:8         | U-0               | U-0                     | U-0                     | U-0               | U-0                  | U-0               | U-0                   | U-0                     |

| 15.0         | _                 | _                       | _                       |                   | —                    | _                 | _                     | —                       |

|              | R/WC-0, HS        | R/WC-0, HS              | R/WC-0, HS              | R/WC-0, HS        | R/WC-0, HS           | R/WC-0, HS        | R-0                   | R/WC-0, HS              |

| 7:0          | STALLIF           | ATTACHIF <sup>(1)</sup> | RESUMEIF <sup>(2)</sup> | IDLEIF            | TRNIF <sup>(3)</sup> | SOFIF             | UERRIF <sup>(4)</sup> | URSTIF <sup>(5)</sup>   |

|              | OTTLE             |                         | REGOMEN                 | IDEEN             |                      | 0011              | OLIVI                 | DETACHIF <sup>(6)</sup> |

|              |                   |                         |                         |                   |                      |                   |                       | 1                       |

### REGISTER 11-6: U1IR: USB INTERRUPT REGISTER

| Legend:           | WC = Write '1' to clear | HS = Hardware Settable bit |                    |  |  |  |  |

|-------------------|-------------------------|----------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented b        | vit, read as '0'   |  |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared       | x = Bit is unknown |  |  |  |  |

#### bit 31-8 Unimplemented: Read as '0'

|       | -  |                                                                                                                                              |

|-------|----|----------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7 |    | <b>STALLIF:</b> STALL Handshake Interrupt bit 1 = In Host mode, a STALL handshake was received during the handshake phase of the transaction |

|       |    |                                                                                                                                              |

|       |    | In Device mode, a STALL handshake was transmitted during the handshake phase of the transaction                                              |

|       |    | 0 = STALL handshake has not been sent                                                                                                        |

| bit 6 |    | ATTACHIF: Peripheral Attach Interrupt bit <sup>(1)</sup>                                                                                     |

|       |    | 1 = Peripheral attachment was detected by the USB module                                                                                     |

|       |    | 0 = Peripheral attachment was not detected                                                                                                   |

| bit 5 |    | <b>RESUMEIF:</b> Resume Interrupt bit <sup>(2)</sup>                                                                                         |

|       |    | 1 = K-State is observed on the D+ or D- pin for 2.5 µs                                                                                       |

|       |    | 0 = K-State is not observed                                                                                                                  |

| bit 4 |    | <b>IDLEIF:</b> Idle Detect Interrupt bit                                                                                                     |

|       |    | <ul><li>1 = Idle condition detected (constant Idle state of 3 ms or more)</li><li>0 = No Idle condition detected</li></ul>                   |

| bit 3 |    | TRNIF: Token Processing Complete Interrupt bit <sup>(3)</sup>                                                                                |

| DILS  |    | 1 = Processing of current token is complete; a read of the U1STAT register will provide endpoint information                                 |

|       |    | 0 = Processing of current token not complete                                                                                                 |

| bit 2 |    | SOFIF: SOF Token Interrupt bit                                                                                                               |

|       |    | 1 = SOF token received by the peripheral or the SOF threshold reached by the host                                                            |

|       |    | 0 = SOF token was not received nor threshold reached                                                                                         |

| bit 1 |    | UERRIF: USB Error Condition Interrupt bit <sup>(4)</sup>                                                                                     |

|       |    | 1 = Unmasked error condition has occurred                                                                                                    |

|       |    | 0 = Unmasked error condition has not occurred                                                                                                |

| bit 0 |    | URSTIF: USB Reset Interrupt bit (Device mode) <sup>(5)</sup>                                                                                 |

|       |    | 1 = Valid USB Reset has occurred                                                                                                             |

|       |    | 0 = No USB Reset has occurred                                                                                                                |

| bit 0 |    | <b>DETACHIF:</b> USB Detach Interrupt bit (Host mode) <sup>(6)</sup>                                                                         |

|       |    | 1 = Peripheral detachment was detected by the USB module                                                                                     |

|       |    | 0 = Peripheral detachment was not detected                                                                                                   |

| Note  | 1: | This bit is valid only if the HOSTEN bit is set (see Register 11-11), there is no activity on the USB for                                    |

|       |    | $2.5 \mu\text{s}$ , and the current bus state is not SE0.                                                                                    |

|       | 2: | When not in Suspend mode, this interrupt should be disabled.                                                                                 |

|       | 3: | Clearing this bit will cause the STAT FIFO to advance.                                                                                       |

|       | 4: | Only error conditions enabled through the U1EIE register will set this bit.                                                                  |

|       | 5: | Device mode.                                                                                                                                 |

|       | 6: | Host mode.                                                                                                                                   |

## 13.2 Control Registers

### TABLE 13-1: TIMER1 REGISTER MAP

| ess                       | Register<br>Name <sup>(1)</sup> | 0         |       |       |       |       |       |       |      | Bi   | its    |      |      |        |      |       |      |      | s          |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|--------|------|------|--------|------|-------|------|------|------------|

| Virtual Addre<br>(BF80_#) |                                 | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7   | 22/6 | 21/5 | 20/4   | 19/3 | 18/2  | 17/1 | 16/0 | All Resets |

| 0600                      | T1CON                           | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _      | _    | —    | —      | —    | —     | _    | _    | 0000       |

| 0600                      | TICON                           | 15:0      | ON    | _     | SIDL  | TWDIS | TWIP  | _     | _    | _    | TGATE  | _    | TCKP | S<1:0> | —    | TSYNC | TCS  | _    | 0000       |

| 0610                      | TMR1                            | 31:16     |       | _     | —     | —     | —     | _     | —    | _    | —      | —    | _    | —      | —    | —     | —    | —    | 0000       |

| 0010                      |                                 | 15:0      |       |       |       |       |       |       |      | TMR1 | <15:0> |      |      |        |      |       |      |      | 0000       |

| 0620                      | PR1 31:16                       |           |       |       |       |       |       |       |      |      | _      | 0000 |      |        |      |       |      |      |            |

| 0020                      | FRI                             | 15:0      |       |       |       |       |       |       |      | PR1< | 15:0>  |      |      |        |      |       |      |      | FFFF       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | —                 | _                 |                   | _                 | _                 | _                 | _                | —                |

| 23:16        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | —                 | _                 |                   |                   | _                 | _                 | _                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | R/W-0             | R-0               | U-0               | U-0              | U-0              |

| 15:8         | 0N <sup>(1)</sup> | _                 | SIDL              | TWDIS             | TWIP              | _                 | _                | —                |

| 7.0          | R/W-0 U-0         |                   | R/W-0             | R/W-0             | U-0               | R/W-0             | R/W-0            | U-0              |

| 7:0          | TGATE             |                   | TCKPS             | S<1:0>            | _                 | TSYNC             | TCS              | _                |

### REGISTER 13-1: T1CON: TYPE A TIMER CONTROL REGISTER

### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |  |  |  |

|-------------------|------------------|------------------------------------|--------------------|--|--|--|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |  |  |  |

#### bit 31-16 Unimplemented: Read as '0'

| DIL 31-10 | ommplemented: Read as 0                                                                                                                                                        |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 15    | ON: Timer On bit <sup>(1)</sup>                                                                                                                                                |

|           | 1 = Timer is enabled                                                                                                                                                           |

|           | 0 = Timer is disabled                                                                                                                                                          |

| bit 14    | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 13    | SIDL: Stop in Idle Mode bit                                                                                                                                                    |

|           | <ul><li>1 = Discontinue operation when device enters Idle mode</li><li>0 = Continue operation even in Idle mode</li></ul>                                                      |

| bit 12    | TWDIS: Asynchronous Timer Write Disable bit                                                                                                                                    |

|           | <ul><li>1 = Writes to TMR1 are ignored until pending write operation completes</li><li>0 = Back-to-back writes are enabled (Legacy Asynchronous Timer functionality)</li></ul> |

| bit 11    | TWIP: Asynchronous Timer Write in Progress bit                                                                                                                                 |

|           | In Asynchronous Timer mode:                                                                                                                                                    |

|           | 1 = Asynchronous write to TMR1 register in progress                                                                                                                            |

|           | 0 = Asynchronous write to TMR1 register complete                                                                                                                               |

|           | In Synchronous Timer mode:<br>This bit is read as '0'.                                                                                                                         |

| bit 10-8  | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 7     | TGATE: Timer Gated Time Accumulation Enable bit                                                                                                                                |

|           | When TCS = 1:                                                                                                                                                                  |

|           | This bit is ignored.                                                                                                                                                           |

|           | When TCS = 0:<br>1 = Gated time accumulation is enabled                                                                                                                        |

|           | 0 = Gated time accumulation is disabled                                                                                                                                        |

| bit 6     | Unimplemented: Read as '0'                                                                                                                                                     |

| bit 5-4   | TCKPS<1:0>: Timer Input Clock Prescale Select bits                                                                                                                             |

|           | 11 = 1:256 prescale value                                                                                                                                                      |

|           | 10 = 1:64 prescale value                                                                                                                                                       |

|           | 01 = 1:8 prescale value<br>00 = 1:1 prescale value                                                                                                                             |

| bit 3     |                                                                                                                                                                                |

| DILO      | Unimplemented: Read as '0'                                                                                                                                                     |

|           |                                                                                                                                                                                |

**Note 1:** When using 1:1 PBCLK divisor, the user's software should not read/write the peripheral SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## 15.1 Watchdog Timer Control Registers

| DS60001185F-page |  |

|------------------|--|

| е<br>—           |  |

| 78               |  |

## TABLE 15-1: WATCHDOG TIMER CONTROL REGISTER MAP

| ess                                                           |           | æ     |       |       |       | Bits  |       |      |      |      |      |      |          |      |      |          |        |            | s    |

|---------------------------------------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|----------|------|------|----------|--------|------------|------|

| Virtual Addres<br>(BF80_#)<br>Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3 | 18/2 | 17/1     | 16/0   | All Resets |      |

| 0000                                                          |           | 31:16 | _     | _     | _     | _     | -     | -    | —    | —    | _    | —    | —        | _    | _    | _        | —      | —          | 0000 |

| 0000 WDTCON                                                   | 15:0      | ON    |       |       |       | _     | _     | _    | _    |      |      | SI   | VDTPS<4: | )>   |      | WDTWINEN | WDTCLR | 0000       |      |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

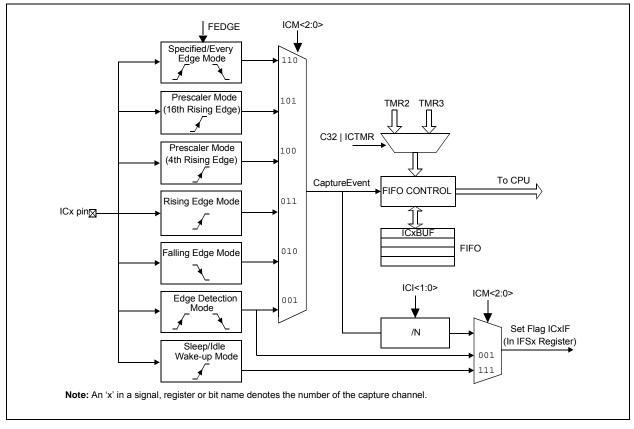

## 16.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

### FIGURE 16-1: INPUT CAPTURE BLOCK DIAGRAM

# 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/ pic32). The I<sup>2</sup>C module provides complete hardware support for both Slave and Multi-Master modes of the I<sup>2</sup>C serial communication standard. Figure 19-1 illustrates the I<sup>2</sup>C module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

| REGISTE | R 19-1: I2CxCON: I <sup>2</sup> C CONTROL REGISTER (CONTINUED)                                                                                                                                                                                                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | <ul> <li>GCEN: General Call Enable bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)</li> <li>0 = General call address disabled</li> </ul>                                                                                              |

| bit 6   | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with SCLREL bit.<br>1 = Enable software or receive clock stretching<br>0 = Disable software or receive clock stretching                                                                                                                     |

| bit 5   | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge<br>0 = Send ACK during Acknowledge                                                                                        |

| bit 4   | <ul> <li>ACKEN: Acknowledge Sequence Enable bit</li> <li>(when operating as I<sup>2</sup>C master, applicable during master receive)</li> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.<br/>Hardware clear at end of master Acknowledge sequence.</li> <li>0 = Acknowledge sequence not in progress</li> </ul> |

| bit 3   | <ul> <li>RCEN: Receive Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte.</li> <li>0 = Receive sequence not in progress</li> </ul>                                                                                               |

| bit 2   | <ul> <li>PEN: Stop Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.</li> <li>0 = Stop condition not in progress</li> </ul>                                                                                                       |

| bit 1   | <ul> <li>RSEN: Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence.</li> <li>0 = Repeated Start condition not in progress</li> </ul>                                                              |

| bit 0   | <b>SEN:</b> Start Condition Enable bit (when operating as I <sup>2</sup> C master)<br>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.<br>0 = Start condition not in progress                                                                                                                          |

**Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

#### REGISTER 21-1: PMCON: PARALLEL PORT CONTROL REGISTER (CONTINUED)

- bit 3 **CS1P:** Chip Select 0 Polarity bit<sup>(2)</sup>

- 1 = Active-high (PMCS1)

- $0 = \text{Active-low}(\overline{\text{PMCS1}})$

- bit 2 Unimplemented: Read as '0'

- bit 1 WRSP: Write Strobe Polarity bit

- For Slave Modes and Master mode 2 (MODE<1:0> = 00,01,10):

- 1 = Write strobe active-high (PMWR)

- $0 = Write strobe active-low (\overline{PMWR})$

For Master mode 1 (MODE<1:0> = 11):

- 1 = Enable strobe active-high (PMENB)

- 0 = Enable strobe active-low (PMENB)

- bit 0 RDSP: Read Strobe Polarity bit

For Slave modes and Master mode 2 (MODE<1:0> = 00,01,10):

- 1 = Read Strobe active-high (PMRD)

- 0 = Read Strobe active-low (PMRD)

For Master mode 1 (MODE<1:0> = 11):

- 1 = Read/write strobe active-high (PMRD/ $\overline{PMWR}$ )

- 0 = Read/write strobe active-low (PMRD/PMWR)

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON control bit.

- 2: These bits have no effect when their corresponding pins are used as address lines.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5         | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|---------------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0                       | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        |                   | _                 | _                         | _                 | _                 | _                 | _                | _                |

| 00.40        | U-0               | U-0               | U-0                       | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 |                           | _                 | _                 | _                 | _                | _                |

| 45.0         | R-0               | R/W-0             | R/W-0                     | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | BUSY              | IRQM<1:0>         |                           | INCM<1:0>         |                   | MODE16            | MODE             | <1:0>            |

| 7.0          | R/W-0             | R/W-0             | R/W-0                     | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | WAITB<1:0>(1)     |                   | WAITM<3:0> <sup>(1)</sup> |                   |                   |                   | WAITE<1:0>(1)    |                  |

### REGISTER 21-2: PMMODE: PARALLEL PORT MODE REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

- bit 15 **BUSY:** Busy bit (Master mode only)

- 1 = Port is busy

- 0 = Port is not busy

#### bit 14-13 IRQM<1:0>: Interrupt Request Mode bits

- 11 = Reserved, do not use

- 10 = Interrupt generated when Read Buffer 3 is read or Write Buffer 3 is written (Buffered PSP mode) or on a read or write operation when PMA<1:0> =11 (Addressable Slave mode only)

- 01 = Interrupt generated at the end of the read/write cycle

- 00 = No Interrupt generated

- bit 12-11 INCM<1:0>: Increment Mode bits

- 11 = Slave mode read and write buffers auto-increment (MODE<1:0> = 00 only)

- 10 = Decrement ADDR<15:0> by 1 every read/write cycle<sup>(2)</sup>

- 01 = Increment ADDR<15:0> by 1 every read/write cycle<sup>(2)</sup>

- 00 = No increment or decrement of address

- bit 10 **MODE16:** 8/16-bit Mode bit

- 1 = 16-bit mode: a read or write to the data register invokes a single 16-bit transfer

- 0 = 8-bit mode: a read or write to the data register invokes a single 8-bit transfer

- bit 9-8 MODE<1:0>: Parallel Port Mode Select bits

- 11 = Master mode 1 (PMCSx, PMRD/PMWR, PMENB, PMA<x:0>, PMD<7:0> and PMD<8:15><sup>(3)</sup>)

- 10 = Master mode 2 (PMCSx, PMRD, PMWR, PMA<x:0>, PMD<7:0> and PMD<8:15><sup>(3)</sup>)

- 01 = Enhanced Slave mode, control signals (PMRD, PMWR, PMCS, PMD<7:0> and PMA<1:0>)

- 00 = Legacy Parallel Slave Port, control signals (PMRD, PMWR, PMCS and PMD<7:0>)

#### bit 7-6 WAITB<1:0>: Data Setup to Read/Write Strobe Wait States bits<sup>(1)</sup>

- 11 = Data wait of 4 TPB; multiplexed address phase of 4 TPB

- 10 = Data wait of 3 TPB; multiplexed address phase of 3 TPB

- 01 = Data wait of 2 TPB; multiplexed address phase of 2 TPB

- 00 = Data wait of 1 TPB; multiplexed address phase of 1 TPB (default)

- **Note 1:** Whenever WAITM<3:0> = 0000, WAITB and WAITE bits are ignored and forced to 1 TPB cycle for a write operation; WAITB = 1 TPB cycle, WAITE = 0 TPB cycles for a read operation.

- 2: Address bits, A15 and A14, are not subject to automatic increment/decrement if configured as Chip Select CS2 and CS1.

- 3: These pins are active when MODE16 = 1 (16-bit mode).

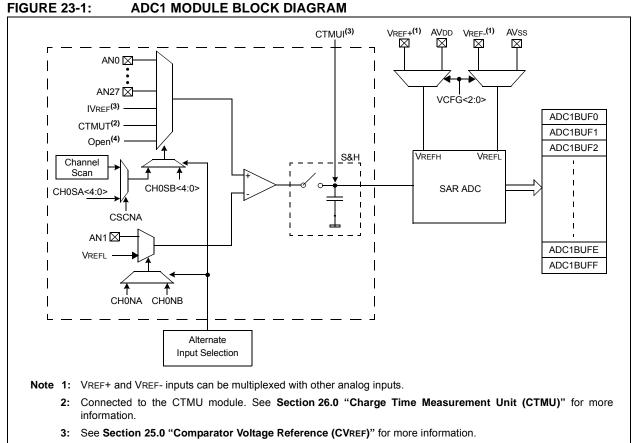

## 23.0 10-BIT ANALOG-TO-DIGITAL CONVERTER (ADC)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 17. "10-bit Analog-to-Digital Converter (ADC)" (DS60001104), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32). The 10-bit Analog-to-Digital Converter (ADC) includes the following features:

- Successive Approximation Register (SAR) conversion

- Up to 1 Msps conversion speed

- · Up to 28 analog input pins

- External voltage reference input pins

- One unipolar, differential Sample and Hold Amplifier (SHA)

- · Automatic Channel Scan mode

- Selectable conversion trigger source

- · 16-word conversion result buffer

- · Selectable buffer fill modes

- · Eight conversion result format options

- · Operation during CPU Sleep and Idle modes

A block diagram of the 10-bit ADC is illustrated in Figure 23-1. The 10-bit ADC has up to 28 analog input pins, designated AN0-AN27. In addition, there are two analog input pins for external voltage reference connections. These voltage reference inputs may be shared with other analog input pins and may be common to other analog module references.

4: This selection is only used with CTMU capacitive and time measurement.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | —                 | _                 | -                 | -                 | —                 | _                 | -                | _                |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   | _                 | _                 | _                 | —                 |                   | _                | -                |

| 45.0         | R/W-0             | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | _                 | _                 | —                 | _                 | _                | _                |

| 7:0          | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | CVROE             | CVRR              | CVRSS             | CVR<3:0>          |                   |                  |                  |

#### **REGISTER 25-1: CVRCON: COMPARATOR VOLTAGE REFERENCE CONTROL REGISTER**

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, I | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Comparator Voltage Reference On bit<sup>(1)</sup>

- 1 = Module is enabled

Setting this bit does not affect other bits in the register.

- 0 = Module is disabled and does not consume current

- Clearing this bit does not affect the other bits in the register.

- bit 14-7 Unimplemented: Read as '0'

- bit 6 **CVROE:** CVREFOUT Enable bit

- 1 = Voltage level is output on CVREFOUT pin

- 0 = Voltage level is disconnected from CVREFOUT pin

- bit 5 CVRR: CVREF Range Selection bit

- 1 = 0 to 0.67 CVRSRC, with CVRSRC/24 step size

- 0 = 0.25 CVRSRC to 0.75 CVRSRC, with CVRSRC/32 step size

- bit 4 **CVRSS:** CVREF Source Selection bit

- 1 = Comparator voltage reference source, CVRSRC = (VREF+) (VREF-)

- 0 = Comparator voltage reference source, CVRSRC = AVDD AVSS

bit 3-0 **CVR<3:0>:** CVREF Value Selection  $0 \le CVR<3:0> \le 15$  bits

$\frac{\text{When CVRR = 1:}}{\text{CVREF = (CVR<3:0>/24) \bullet (CVRSRC)}}$  $\frac{\text{When CVRR = 0:}}{\text{CVREF = 1/4 \bullet (CVRSRC) + (CVR<3:0>/32) \bullet (CVRSRC)}}$

**Note 1:** When using 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2                | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------------------|------------------|------------------|--|

| 04.04        | r-0               | r-1               | r-1               | R/P               | r-1               | r-1                              | r-1              | R/P              |  |

| 31:24        | _                 | —                 | —                 | CP                | —                 | —                                | —                | BWP              |  |

| 00.40        | r-1               | r-1               | r-1               | r-1               | R/P               | R/P                              | R/P              | R/P              |  |

| 23:16        | —                 | —                 | —                 | —                 | PWP<7:4>          |                                  |                  |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P               | r-1               | r-1                              | r-1              | r-1              |  |

| 15:8         |                   | PWP<              | <3:0>             |                   | —                 | —                                | _                | —                |  |

| 7.0          | r-1               | r-1               | r-1               | R/P               | R/P               | R/P                              | R/P              | R/P              |  |

| 7:0          |                   | _                 | —                 | ICESE             | L<1:0>            | JTAGEN <sup>(1)</sup> DEBUG<1:0> |                  |                  |  |

#### REGISTER 28-1: DEVCFG0: DEVICE CONFIGURATION WORD 0

| Legend:           | r = Reserved bit | r = Reserved bit P = Programmable bit |                    |  |

|-------------------|------------------|---------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented b                   | it, read as '0'    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared                  | x = Bit is unknown |  |

bit 31 **Reserved:** Write '0'

bit 30-29 Reserved: Write '1'

bit 28 **CP:** Code-Protect bit

Prevents boot and program Flash memory from being read or modified by an external programming device.

1 = Protection is disabled

0 = Protection is enabled

#### bit 27-25 Reserved: Write '1'

bit 24 BWP: Boot Flash Write-Protect bit

Prevents boot Flash memory from being modified during code execution.

1 = Boot Flash is writable

0 = Boot Flash is not writable

bit 23-20 Reserved: Write '1'

bit 19-12 **PWP<7:0>:** Program Flash Write-Protect bits

Prevents selected program Flash memory pages from being modified during code execution. The PWP bits represent the one's compliment of the number of write protected program Flash memory pages.

| 11111111 = Disabled    |

|------------------------|

| 11111110 = 0xBD00_0FFF |

| 11111101 = 0xBD00_1FFF |

| 11111100 = 0xBD00_2FFF |

| 11111011 = 0xBD00_3FFF |

| 11111010 = 0xBD00_4FFF |

| 11111001 = 0xBD00_5FFF |

| 11111000 = 0xBD00_6FFF |

| 11110111 = 0xBD00_7FFF |

| 11110110 = 0xBD00 8FFF |

| 11110101 = 0xBD00_9FFF |

| 11110100 = 0xBD00_AFFF |

| 11110011 = 0xBD00 BFFF |

| 11110010 = 0xBD00 CFFF |

| 11110001 = 0xBD00 DFFF |

| 11110000 = 0xBD00 EFFF |

| 11101111 = 0xBD00 FFFF |

| . –                    |

|                        |

|                        |

| 01111111 = 0xBD07 FFFF |

| _                      |

|                        |

Note 1: This bit sets the value for the JTAGEN bit in the CFGCON register.

| Bit<br>31/23/15/7           | Bit<br>30/22/14/6         | Bit<br>29/21/13/5                                                                                                     | Bit<br>28/20/12/4                                                                                                                                                                | Bit<br>27/19/11/3                                                                                                                                                                                                                                                                                                                                                               | Bit<br>26/18/10/2                                                                                                                                                                                            | Bit<br>25/17/9/1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Bit<br>24/16/8/0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

|-----------------------------|---------------------------|-----------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| R                           | R                         | R                                                                                                                     | R                                                                                                                                                                                | R                                                                                                                                                                                                                                                                                                                                                                               | R                                                                                                                                                                                                            | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | R                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |