Welcome to **E-XFL.COM**

What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded - Microcontrollers</u>"

| Details                    |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

|                            |                                                                                 |

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 128K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                               |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx470f512lt-i-pt |

### TABLE 4: PIN NAMES FOR 100-PIN DEVICES (CONTINUED)

**100-PIN TQFP (TOP VIEW)**(1,2,3)

PIC32MX330F064L PIC32MX350F128L PIC32MX350F256L PIC32MX370F512L

100

1

| Pin# | Full Pin Name         |

|------|-----------------------|

| 71   | RPD11/PMCS1/RD11      |

| 72   | RPD0/RD0              |

| 73   | SOSCI/RPC13/RC13      |

| 74   | SOSCO/RPC14/T1CK/RC14 |

| 75   | Vss                   |

| 76   | AN24/RPD1/RD1         |

| 77   | AN25/RPD2/RD2         |

| 78   | AN26/RPD3/RD3         |

| 79   | RPD12/PMD12/RD12      |

| 80   | PMD13/RD13            |

| 81   | RPD4/PMWR/RD4         |

| 82   | RPD5/PMRD/RD5         |

| 83   | PMD14/RD6             |

| 84   | PMD15/RD7             |

| 85   | VCAP                  |

| Pin# | Full Pin Name       |

|------|---------------------|

| 86   | VDD                 |

| 87   | RPF0/PMD11/RF0      |

| 88   | RPF1/PMD10/RF1      |

| 89   | RPG1/PMD9/RG1       |

| 90   | RPG0/PMD8/RG0       |

| 91   | TRCLK/RA6           |

| 92   | TRD3/CTED8/RA7      |

| 93   | PMD0/RE0            |

| 94   | PMD1/RE1            |

| 95   | TRD2/RG14           |

| 96   | TRD1/RG12           |

| 97   | TRD0/RG13           |

| 98   | AN20/PMD2/RE2       |

| 99   | RPE3/CTPLS/PMD3/RE3 |

| 100  | AN21/PMD4/RE4       |

### Note

- 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

- 2: Every I/O port pin (RAx-RGx), with the exception of RF6, can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

- 3: RPF6 (pin 55) and RPF7 (pin 54) are only remappable for input functions.

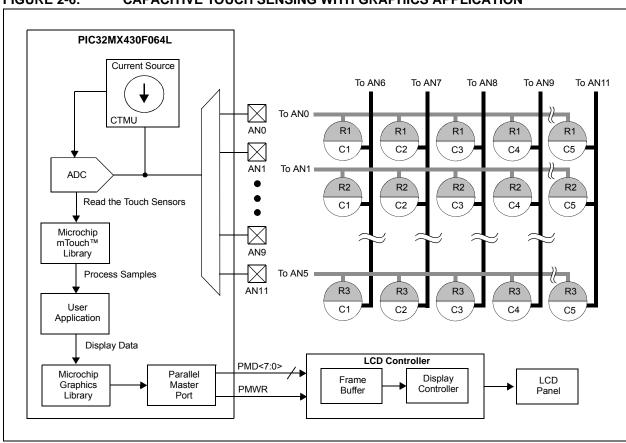

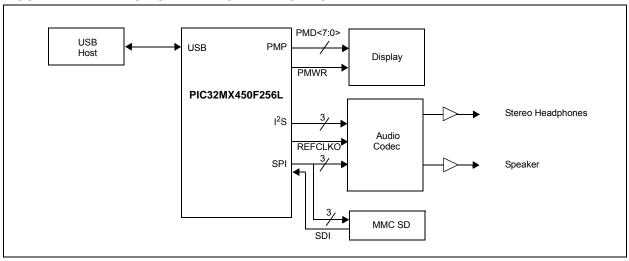

# 2.11 Typical Application Connection Examples

Examples of typical application connections are shown in Figure 2-6, Figure 2-7, and Figure 2-8.

FIGURE 2-6: CAPACITIVE TOUCH SENSING WITH GRAPHICS APPLICATION

### FIGURE 2-7: AUDIO PLAYBACK APPLICATION

### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit Bit 30/22/14/6 29/21/1 |       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|----------------------------|-------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.24        | U-0               | U-0                        | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        | _                 | _                          | _     | _                 | _                 | _                 | _                | _                |  |  |  |  |  |  |

| 22.40        | U-0               | U-0                        | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 23:16        | _                 | _                          | _     | _                 | _                 | _                 | _                | _                |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0                      | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |  |  |  |

| 15:8         |                   | BMXDUDBA<15:8>             |       |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R-0               | R-0                        | R-0   | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |

| 7:0          |                   |                            |       | BMXDU             | DBA<7:0>          |                   |                  |                  |  |  |  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: Read-Only bits

Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

#### REGISTER 5-1: NVMCON: PROGRAMMING CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4 | Bit<br>27/19/11/3      | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|----------------------|-------------------|------------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0 U-0 U-0       |                      | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 31.24        |                   |                   | _                    | _                 | _                      | _                 | _                | _                |

| 22:46        | U-0               | U-0 U-0 U-0       |                      | U-0               | U-0                    | U-0               | U-0              | U-0              |

| 23:16        | _                 | 1                 | _                    | _                 | _                      | _                 | _                | _                |

| 45.0         | R/W-0             | R/W-0             | R-0                  | R-0               | R-0                    | U-0               | U-0              | U-0              |

| 15:8         | WR                | WREN              | WRERR <sup>(1)</sup> | LVDERR(1)         | LVDSTAT <sup>(1)</sup> | _                 | _                | _                |

| 7:0          | U-0               | U-0               | U-0                  | U-0               | R/W-0                  | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | _                 | _                 | _                    | _                 |                        | NVMOF             |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 WR: Write Control bit

This bit is writable when WREN = 1 and the unlock sequence is followed.

1 = Initiate a Flash operation. Hardware clears this bit when the operation completes

0 = Flash operation complete or inactive

bit 14 WREN: Write Enable bit

1 = Enable writes to WR bit and enables LVD circuit

0 = Disable writes to WR bit and disables LVD circuit

This is the only bit in this register reset by a device Reset.

bit 13 **WRERR:** Write Error bit<sup>(1)</sup>

This bit is read-only and is automatically set by hardware.

1 = Program or erase sequence did not complete successfully

0 = Program or erase sequence completed normally

bit 12 LVDERR: Low-Voltage Detect Error bit (LVD circuit must be enabled)<sup>(1)</sup>

This bit is read-only and is automatically set by hardware.

1 = Low-voltage detected (possible data corruption, if WRERR is set)

0 = Voltage level is acceptable for programming

bit 11 LVDSTAT: Low-Voltage Detect Status bit (LVD circuit must be enabled)<sup>(1)</sup>

This bit is read-only and is automatically set, and cleared, by hardware.

1 = Low-voltage event active

0 = Low-voltage event NOT active

bit 10-4 Unimplemented: Read as '0'

bit 3-0 NVMOP<3:0>: NVM Operation bits

These bits are writable when WREN = 0.

1111 = Reserved

•

0111 = Reserved

0110 = No operation

0101 = Program Flash (PFM) erase operation: erases PFM, if all pages are not write-protected

0100 = Page erase operation: erases page selected by NVMADDR, if it is not write-protected

0011 = Row program operation: programs row selected by NVMADDR, if it is not write-protected

0010 = No operation

0001 = Word program operation: programs word selected by NVMADDR, if it is not write-protected

0000 = No operation

Note 1: This bit is cleared by setting NVMOP = 0000, and initiating a Flash operation (i.e., WR).

#### REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0 U-0           |                  | U-0              |

| 31.24        | _                 | _                 | _                 | _                 | _                 | -                 | _                | _                |

| 22.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | SS0              |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | _                 | _                 | _                 | MVEC              | _                 |                   |                  |                  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          | _                 | _                 | _                 | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-17 **Unimplemented:** Read as '0'

bit 16 SS0: Single Vector Shadow Register Set bit

1 = Single vector is presented with a shadow register set

0 = Single vector is not presented with a shadow register set

bit 15-13 Unimplemented: Read as '0'

bit 12 MVEC: Multi Vector Configuration bit

1 = Interrupt controller configured for multi vectored mode

0 = Interrupt controller configured for single vectored mode

bit 11 Unimplemented: Read as '0'

bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

001 = Interrupts of group priority 1 start the Interrupt Proximity timer

000 = Disables Interrupt Proximity timer

bit 7-5 Unimplemented: Read as '0'

bit 4 **INT4EP:** External Interrupt 4 Edge Polarity Control bit

1 = Rising edge

0 = Falling edge

bit 3 **INT3EP:** External Interrupt 3 Edge Polarity Control bit

1 = Rising edge

0 = Falling edge

bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

1 = Rising edge

0 = Falling edge

bit 1 **INT1EP:** External Interrupt 1 Edge Polarity Control bit

1 = Rising edge

0 = Falling edge

bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

1 = Rising edge

0 = Falling edge

#### REGISTER 7-6: IPCx: INTERRUPT PRIORITY CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit Bit 28/20/12/4 27/19/11/3 |          | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------------------|----------|-------------------|------------------|------------------|--|--|

| 31:24        | U-0               | U-0               | U-0 R/W-0 R/W-0   |                               | R/W-0    | R/W-0             | R/W-0            |                  |  |  |

| 31.24        | _                 | _                 | _                 |                               | IP3<2:0> |                   | IS3<1:0>         |                  |  |  |

| 22:16        | U-0               | U-0               | U-0               | R/W-0 R/W-0                   |          | R/W-0             | R/W-0            | R/W-0            |  |  |

| 23:16        | _                 | _                 | _                 |                               | IP2<2:0> |                   | IS2<1:0>         |                  |  |  |

| 15.0         | U-0               | U-0               | U-0               | R/W-0                         | R/W-0    | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | _                 | _                 | _                 |                               | IP1<2:0> |                   | IS1<1:0>         |                  |  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0 R/W-0                   |          | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          | _                 | _                 | _                 |                               | IP0<2:0> |                   | IS0<             | 1:0>             |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-29 Unimplemented: Read as '0'

bit 28-26 IP3<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

•

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 25-24 IS3<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 23-21 Unimplemented: Read as '0'

bit 20-18 IP2<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

.

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

bit 17-16 IS2<1:0>: Interrupt Subpriority bits

11 = Interrupt subpriority is 3

10 = Interrupt subpriority is 2

01 = Interrupt subpriority is 1

00 = Interrupt subpriority is 0

bit 15-13 Unimplemented: Read as '0'

bit 12-10 IP1<2:0>: Interrupt Priority bits

111 = Interrupt priority is 7

•

,

010 = Interrupt priority is 2

001 = Interrupt priority is 1

000 = Interrupt is disabled

**Note:** This register represents a generic definition of the IPCx register. Refer to Table 7-1 for the exact bit definitions.

#### **REGISTER 11-10: U1STAT: USB STATUS REGISTER**

| Bit<br>Range | Bit<br>31/23/15/7 | Bit Bit 30/22/14/6 29/21/13 |        | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-----------------------------|--------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0                         | U-0    | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _                           | -      | _                 |                   |                   | -                | _                |

| 23:16        | U-0               | U-0                         | U-0    | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _                           | -      | _                 | -                 | -                 | -                | _                |

| 15:8         | U-0               | U-0                         | U-0    | U-0               | U-0               | U-0               | U-0              | U-0              |

| 13.6         | -                 | _                           |        |                   | _                 | -                 | -                | _                |

| 7:0          | R-x               | R-x R-x                     |        | R-x R-x           |                   | R-x               | U-0              | U-0              |

| 7.0          |                   | ENDP <sup>*</sup>           | T<3:0> |                   | DIR               | PPBI              |                  | _                |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-4 **ENDPT<3:0>:** Encoded Number of Last Endpoint Activity bits

(Represents the number of the BDT, updated by the last USB transfer.)

1111 = Endpoint 15

1110 = Endpoint 14

:

:

0001 = Endpoint 1

0000 = Endpoint 0

bit 3 DIR: Last BD Direction Indicator bit

1 = Last transaction was a transmit transfer (TX)

0 = Last transaction was a receive transfer (RX)

bit 2 **PPBI:** Ping-Pong BD Pointer Indicator bit

1 = The last transaction was to the ODD BD bank

0 = The last transaction was to the EVEN BD bank

bit 1-0 Unimplemented: Read as '0'

Note: The U1STAT register is a window into a 4-byte FIFO maintained by the USB module. U1STAT value is only valid when the TRNIF bit (U1IR<3>) is active. Clearing the TRNIF bit advances the FIFO. Data in register is invalid when the TRNIF bit = 0.

### REGISTER 11-16: U1SOF: USB SOF THRESHOLD REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 |       |       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------|-------|-------------------|-------------------|-------------------|------------------|------------------|

| 31:24        | U-0               | U-0   | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31.24        | -                 | _     | _     | _                 | _                 | -                 | -                | _                |

| 23:16        | U-0               | U-0   | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23.10        | -                 | _     | _     | _                 | _                 | -                 | _                | _                |

| 15:8         | U-0               | U-0   | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |

| 15.6         | _                 | _     | _     | _                 | _                 | _                 | _                | _                |

| 7:0          | R/W-0             | R/W-0 | R/W-0 | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7.0          |                   |       |       | CNT               | <7:0>             |                   |                  |                  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-0 CNT<7:0>: SOF Threshold Value bits

> Typical values of the threshold are: 01001010 = 64-byte packet 00101010 = 32-byte packet 00011010 = 16-byte packet

00010010 = 8-byte packet

### REGISTER 11-17: U1BDTP1: USB BDT PAGE 1 REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit Bit 30/22/14/6 29/21/13/5 |       | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------------------|-------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 31:24        | U-0               | U-0                           | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31.24        | -                 | _                             | -     | _                 | -                 | _                 | -                | _                |  |  |  |

| 23:16        | U-0               | U-0                           | U-0   | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23.10        | _                 | _                             | _     | _                 | _                 | _                 | _                | _                |  |  |  |

| 15:8         | U-0               | U-0                           | U-0   | U-0               | U-0 U-0           |                   | U-0              | U-0              |  |  |  |

| 15.6         | -                 | _                             | -     | _                 | -                 | _                 | -                | _                |  |  |  |

| 7:0          | R/W-0 R/W-0       |                               | R/W-0 | R/W-0 R/W-0       |                   | R/W-0 R/W-0       |                  | U-0              |  |  |  |

| 7.0          | BDTPTRL<15:9>     |                               |       |                   |                   |                   |                  |                  |  |  |  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-8 Unimplemented: Read as '0'

bit 7-1 BDTPTRL<15:9>: BDT Base Address bits

> This 7-bit value provides address bits 15 through 9 of the BDT base address, which defines the starting location of the BDT in system memory.

The 32-bit BDT base address is 512-byte aligned.

bit 0 Unimplemented: Read as '0'

**TABLE 12-2: OUTPUT PIN SELECTION**

| RPn Port Pin         | RPnR SFR | RPnR bits   | RPnR Value to Peripheral<br>Selection      |

|----------------------|----------|-------------|--------------------------------------------|

| RPD2                 | RPD2R    | RPD2R<3:0>  | 0000 = No Connect                          |

| RPG8                 | RPG8R    | RPG8R<3:0>  | 0001 = U3TX                                |

| RPF4                 | RPF4R    | RPF4R<3:0>  | 0010 = U4RTS<br>0011 = Reserved            |

| RPD10                | RPD10R   | RPD10R<3:0> | 0110 = Reserved                            |

| RPF1                 | RPF1R    | RPF1R<3:0>  | 0101 = Reserved                            |

| RPB9                 | RPB9R    | RPB9R<3:0>  | 0110 = SDO2                                |

| RPB10                | RPB10R   | RPB10R<3:0> | 0111 = Reserved<br>1000 = Reserved         |

| RPC14                | RPC14R   | RPC14R<3:0> | 1000 - Reserved                            |

| RPB5                 | RPB5R    | RPB5R<3:0>  | 1010 = Reserved                            |

| RPC1 <sup>(4)</sup>  | RPC1R    | RPC1R<3:0>  | 1011 = OC3                                 |

| RPD14 <sup>(4)</sup> | RPD14R   | RPD14R<3:0> | 1100 = Reserved<br>1101 = C2OUT            |

| RPG1 <sup>(4)</sup>  | RPG1R    | RPG1R<3:0>  | 11101 - G2001<br>1110 = Reserved           |

| RPA14 <sup>(4)</sup> | RPA14R   | RPA14R<3:0> | 1111 = Reserved                            |

| RPD3                 | RPD3R    | RPD3R<3:0>  | 0000 = No Connect                          |

| RPG7                 | RPG7R    | RPG7R<3:0>  | 0001 <b>= U2TX</b>                         |

| RPF5                 | RPF5R    | RPF5R<3:0>  | 0010 = Reserved                            |

| RPD11                | RPD11R   | RPD11R<3:0> | 0011 = U1TX<br>0100 = U5RTS <sup>(4)</sup> |

| RPF0                 | RPF0R    | RPF0R<3:0>  | 0100 = OSRTS( )<br>0101 = Reserved         |

| RPB1                 | RPB1R    | RPB1R<3:0>  | 0110 = SDO2                                |

| RPE5                 | RPE5R    | RPE5R<3:0>  | 0111 = Reserved                            |

| RPC13                | RPC13R   | RPC13R<3:0> | 1000 = SDO1                                |

| RPB3                 | RPB3R    | RPB3R<3:0>  | 1001 = Reserved                            |

| RPF3 <sup>(2)</sup>  | RPF3R    | RPF3R<3:0>  | 1010 = Reserved                            |

| RPC4 <sup>(4)</sup>  | RPC4R    | RPC4R<3:0>  | 1011 = OC4<br>1100 = Reserved              |

| RPD15 <sup>(4)</sup> | RPD15R   | RPD15R<3:0> | 1100 = Reserved                            |

| RPG0 <sup>(4)</sup>  | RPG0R    | RPG0R<3:0>  | 1110 = Reserved                            |

| RPA15 <sup>(4)</sup> | RPA15R   | RPA15R<3:0> | 1111 = Reserved                            |

Note 1: This selection is only available on General Purpose devices.

**<sup>2:</sup>** This selection is only available on 64-pin General Purpose devices.

<sup>3:</sup> This selection is only available on 100-pin General Purpose devices.

<sup>4:</sup> This selection is only available on 100-pin USB and General Purpose devices.

<sup>5:</sup> This selection is not available on 64-pin USB devices.

### 12.4 Control Registers

TABLE 12-3: PORTA REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L, PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY

| ess (                       |                                 | ø.        |               |               |       |       |       |               |              | Bi   | ts           |              |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|---------------|---------------|-------|-------|-------|---------------|--------------|------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15         | 30/14         | 29/13 | 28/12 | 27/11 | 26/10         | 25/9         | 24/8 | 23/7         | 22/6         | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6000                        | ANSELA                          | 31:16     | _             | _             | _     | _     | _     | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        | ANOLLA                          | 15:0      | _             | _             | _     | _     |       | ANSELA10      | ANSELA9      | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0060          |

| 6010                        | TRISA                           | 31:16     | _             | _             | _     | _     |       | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0010                        | 11(10/1                         | 15:0      | TRISA15       | TRISA14       | _     | _     |       | TRISA10       | TRISA9       | _    | TRISA7       | TRISA6       | TRISA5       | TRISA4       | TRISA3       | TRISA2       | TRISA1       | TRISA0       | xxxx          |

| 6020                        | PORTA                           | 31:16     | _             | _             | _     | _     |       | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0020                        | TORTA                           | 15:0      | RA15          | RA14          | _     | _     |       | RA10          | RA9          | _    | RA7          | RA6          | RA5          | RA4          | RA3          | RA2          | RA1          | RA0          | xxxx          |

| 6030                        | LATA                            | 31:16     | _             | _             | _     | _     |       | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        | Litti                           | 15:0      | LATA15        | LATA14        | _     | _     |       | LATA10        | LATA9        | _    | LATA7        | LATA6        | LATA5        | LATA4        | LATA3        | LATA2        | LATA1        | LATA0        | xxxx          |

| 6040                        | ODCA                            | 31:16     | _             | _             | _     | _     |       | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0040                        | ODOM                            | 15:0      | ODCA15        | ODCA14        | _     | _     |       | ODCA10        | ODCA9        | _    | ODCA7        | ODCA6        | ODCA5        | ODCA4        | ODCA3        | ODCA2        | ODCA1        | ODCA0        | xxxx          |

| 6050                        | CNPUA                           | 31:16     | _             | _             | _     | _     |       | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        | 0111 071                        | 15:0      | CNPUA15       | CNPUA14       | _     | _     |       | CNPUA10       | CNPUA9       | _    | CNPUA7       | CNPUA6       | CNPUA5       | CNPUA4       | CNPUA3       | CNPUA2       | CNPUA1       | CNPUA0       | xxxx          |

| 6060                        | CNPDA                           | 31:16     | _             | _             | _     | _     |       | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        | OIVI D/V                        | 15:0      | CNPDA15       | CNPDA14       | _     | _     |       | CNPDA10       | CNPDA9       | _    | CNPDA7       | CNPDA6       | CNPDA5       | CNPDA4       | CNPDA3       | CNPDA2       | CNPDA1       | CNPDA0       | xxxx          |

| 6070                        | CNCONA                          | 31:16     | _             | _             | _     | _     |       | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0010                        | OHOOH (                         | 15:0      | ON            | _             | SIDL  | _     |       | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 6080                        | CNENA                           | 31:16     | _             | _             | _     | _     |       | _             | _            | _    | _            | _            | _            | _            | _            | _            | _            | _            | 0000          |

| 0000                        | ONLIVE                          | 15:0      | CNIEA15       | CNIEA14       | _     | _     |       | CNIEA10       | CNIEA9       | _    | CNIEA7       | CNIEA6       | CNIEA5       | CNIEA4       | CNIEA3       | CNIEA2       | CNIEA1       | CNIEA0       | xxxx          |

|                             |                                 | 31:16     | _             | _             |       | _     |       | _             | _            | _    | _            | _            | _            |              | _            | _            | _            |              | 0000          |

| 6090                        | CNSTATA                         | 15:0      | CN<br>STATA15 | CN<br>STATA14 | _     | _     | _     | CN<br>STATA10 | CN<br>STATA9 | _    | CN<br>STATA7 | CN<br>STATA6 | CN<br>STATA5 | CN<br>STATA4 | CN<br>STATA3 | CN<br>STATA2 | CN<br>STATA1 | CN<br>STATA0 | xxxx          |

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

| IABL | E 12-18: | PER | RIPHERAL PIN SELECT | OUTPUT | REGISTER MAP |

|------|----------|-----|---------------------|--------|--------------|

|      |          |     |                     |        |              |

| SS                          |                       |           |       | Bits  |       |       |       |       |      |      |      |      |      |      |      |       |        |      |            |

|-----------------------------|-----------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|-------|--------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2  | 17/1   | 16/0 | All Resets |

| FB38                        | RPA14R <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    |       |        |      | 0000       |

| 1 030                       | KFA 14K**             | 15:0      |       | _     | _     | _     |       | _     | _    |      | _    |      | _    | _    |      | RPA14 | l<3:0> |      | 0000       |

| FB3C                        | RPA15R <sup>(1)</sup> | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| 1 550                       | KFA ISK.              | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPA15 | 5<3:0> |      | 0000       |

| FB40                        | RPB0R                 | 31:16     |       | _     | _     | _     |       | _     | _    |      | _    |      | _    | _    | _    | _     | _      | _    | 0000       |

| FB40                        | KEBOK                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB0  | <3:0>  |      | 0000       |

| FB44                        | RPB1R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | -     |        | -    | 0000       |

| 1 044                       | KEDIK                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB1  | <3:0>  |      | 0000       |

| FB48                        | RPB2R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | -     |        | -    | 0000       |

| FB40                        | KFB2K                 | 15:0      | 1     | _     |       | _     | -     | _     | _    | -    | _    | -    | _    |      |      | RPB2  | <3:0>  |      | 0000       |

| FB4C                        | DDD2D                 | 31:16     | -     | _     | _     | _     | _     | _     | _    | -    | _    | _    | _    | _    | _    | ı     |        | -    | 0000       |

| FB4C                        | RPB3R                 | 15:0      |       | _     | _     | _     | _     | _     | _    |      | _    | _    | _    | _    |      | RPB3  | <3:0>  |      | 0000       |

| FB54                        | RPB5R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB34                        | RPBOR                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB5  | <3:0>  |      | 0000       |

| ED E O                      | RPB6R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB58                        |                       | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB6  | <3:0>  |      | 0000       |

| FB5C                        | RPB7R                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FBSC                        | RPB/R                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB7  | <3:0>  |      | 0000       |

| ED.CO                       | DDDOD                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB60                        | RPB8R                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB8  | <3:0>  |      | 0000       |

| EDC4                        | DDDOD                 | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB64                        | RPB9R                 | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB9  | <3:0>  |      | 0000       |

| ED.CO                       | DDD40D                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB68                        | RPB10R                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB10 | )<3:0> |      | 0000       |

|                             | 555445                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB78                        | RPB14R                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB14 | 1<3:0> |      | 0000       |

| ED70                        | DDD45D                | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB7C                        | RPB15R                | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPB15 | 5<3:0> |      | 0000       |

|                             | DD0 (D(1)             | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB84                        | RPC1R <sup>(1)</sup>  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC1  | <3:0>  |      | 0000       |

|                             | (4)                   | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB88                        | RPC2R <sup>(1)</sup>  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC2  | <3:0>  |      | 0000       |

|                             | (4)                   | 31:16     | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _     | _      | _    | 0000       |

| FB8C                        | RPC3R <sup>(1)</sup>  | 15:0      | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPC3  | <3:0>  |      | 0000       |

**Legend:** x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: This register is not available on 64-pin devices.

<sup>2:</sup> This register is only available on devices without a USB module.

<sup>3:</sup> This register is not available on 64-pin devices with a USB module.

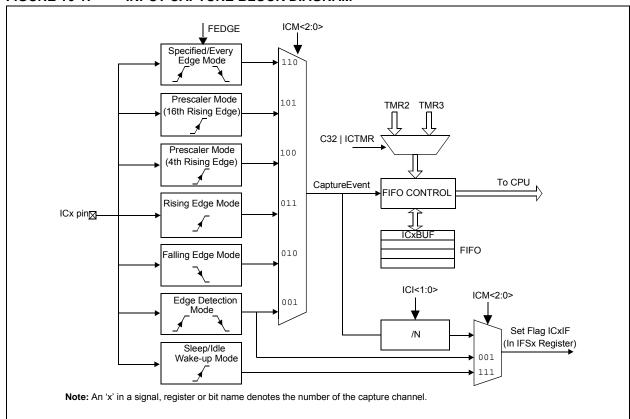

### 16.0 INPUT CAPTURE

Note:

This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 15. "Input Capture"** (DS60001122), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- · Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- · Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

#### FIGURE 16-1: INPUT CAPTURE BLOCK DIAGRAM

### REGISTER 21-5: PMSTAT: PARALLEL PORT STATUS REGISTER (SLAVE MODES ONLY)

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | _                 | -                 | _                 | -                 | _                 | -                | _                |

| 22:46        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |

| 23:16        | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |

| 45.0         | R-0               | R/W-0, HS, SC     | U-0               | U-0               | R-0               | R-0               | R-0              | R-0              |

| 15:8         | IBF               | IBOV              | -                 | _                 | IB3F              | IB2F              | IB1F             | IB0F             |

| 7.0          | R-1               | R/W-0, HS, SC     | U-0               | U-0               | R-1               | R-1               | R-1              | R-1              |

| 7:0          | OBE               | OBUF              | _                 | _                 | OB3E              | OB2E              | OB1E             | OB0E             |

Legend:HS = Set by HardwareSC = Cleared by softwareR = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15 IBF: Input Buffer Full Status bit

1 = All writable input buffer registers are full

0 = Some or all of the writable input buffer registers are empty

bit 14 IBOV: Input Buffer Overflow Status bit

1 = A write attempt to a full input byte buffer occurred (must be cleared in software)

0 = No overflow occurred

bit 13-12 Unimplemented: Read as '0'

bit 11-8 IBxF: Input Buffer 'x' Status Full bits

1 = Input Buffer contains data that has not been read (reading buffer will clear this bit)

0 = Input Buffer does not contain any unread data

bit 7 **OBE:** Output Buffer Empty Status bit

1 = All readable output buffer registers are empty

0 = Some or all of the readable output buffer registers are full

bit 6 **OBUF:** Output Buffer Underflow Status bit

1 = A read occurred from an empty output byte buffer (must be cleared in software)

0 = No underflow occurred

bit 5-4 Unimplemented: Read as '0'

bit 3-0 **OBxE:** Output Buffer 'x' Status Empty bits

1 = Output buffer is empty (writing data to the buffer will clear this bit)

0 = Output buffer contains data that has not been transmitted

### REGISTER 23-5: AD1CSSL: ADC INPUT SCAN SELECT REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.24        | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | _                 | CSSL30            | CSSL29            | CSSL28            | CSSL27            | CSSL26            | CSSL25           | CSSL24           |

| 00:40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | CSSL23            | CSSL21            | CSSL21            | CSSL20            | CSSL19            | CSSL18            | CSSL17           | CSSL16           |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 15:8         | CSSL15            | CSSL14            | CSSL13            | CSSL12            | CSSL11            | CSSL10            | CSSL9            | CSSL8            |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | CSSL7             | CSSL6             | CSSL5             | CSSL4             | CSSL3             | CSSL2             | CSSL1            | CSSL0            |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 31-16 Unimplemented: Read as '0'

bit 15-0 CSSL<30:0>: ADC Input Pin Scan Selection bits(1,2)

1 = Select ANx for input scan0 = Skip ANx for input scan

**Note 1:** CSSL = ANx, where x = 0-27; CSSL30 selects Vss for scan; CSSL29 selects CTMU input for scan; CSSL28 selects IVREF for scan.

2: On devices with less than 28 analog inputs, all CSSLx bits can be selected; however, inputs selected for scan without a corresponding input on the device will convert to VREFL.

### 24.1 Control Registers

### TABLE 24-1: COMPARATOR REGISTER MAP

| ess                         | Register<br>Name(1) |           |       | Bits  |       |       |       |       |      |      |      |        |      |      |      |      | S     |       |            |

|-----------------------------|---------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#) |                     | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0  | All Resets |

| 4000                        | CM1CON              | 31:16     | _     |       |       |       |       |       |      |      |      |        | _    |      |      | _    | _     |       | 0000       |

| A000                        | CIVITCON            | 15:0      | ON    | COE   | CPOL  | _     | _     | _     | _    | COUT | EVPO | L<1:0> | _    | CREF | _    | _    | CCH   | <1:0> | E1C3       |

| A010                        | CM2CON              | 31:16     | _     |       | _     | -     | 1     | -     | _    | -    | -    | _      | _    | 1    | -    | _    | _     | _     | 0000       |

| AUTU                        | CIVIZCON            | 15:0      | ON    | COE   | CPOL  | -     | 1     | -     | _    | COUT | EVPO | L<1:0> | _    | CREF | -    | _    | CCH   | <1:0> | E1C3       |

| A060                        | CMSTAT              | 31:16     | _     | _     |       |       |       |       | I    |      | _    |        | _    | _    |      | _    |       | 1     | 0000       |

| A000                        | CIVISTAT            | 15:0      | _     | _     | SIDL  |       |       |       | I    |      | _    |        | _    | _    |      | _    | C2OUT | C10UT | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

PIC32MX330/350/370/430/450/470

'0' = Bit is cleared

x = Bit is unknown

### REGISTER 28-6: DEVID: DEVICE AND REVISION ID REGISTER

| Bit<br>Range | Bit<br>31/23/15/7          | Bit<br>30/22/14/6 | Bit<br>29/21/13/5    | Bit<br>28/20/12/4 | Bit<br>27/19/11/3           | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|----------------------------|-------------------|----------------------|-------------------|-----------------------------|-------------------|------------------|------------------|--|--|

| 04.04        | R                          | R                 | R                    | R                 | R                           | R                 | R                | R                |  |  |

| 31:24        |                            | VER<              | <3:0> <sup>(1)</sup> |                   | DEVID<27:24> <sup>(1)</sup> |                   |                  |                  |  |  |

| 22.46        | R                          | R                 | R                    | R                 | R                           | R                 | R                | R                |  |  |

| 23:16        | DEVID<23:16>(1)            |                   |                      |                   |                             |                   |                  |                  |  |  |

| 45.0         | R                          | R                 | R                    | R                 | R                           | R                 | R                | R                |  |  |

| 15:8         | DEVID<15:8> <sup>(1)</sup> |                   |                      |                   |                             |                   |                  |                  |  |  |

| 7.0          | R                          | R                 | R                    | R                 | R                           | R                 | R                | R                |  |  |

| 7:0          |                            |                   |                      | DEVID<            | 7:0>(1)                     |                   |                  |                  |  |  |

| Legend:          |                  |                                    |

|------------------|------------------|------------------------------------|

| R = Readable bit | W = Writable bit | U = Unimplemented bit, read as '0' |

'1' = Bit is set

bit 31-28 **VER<3:0>:** Revision Identifier bits<sup>(1)</sup>

bit 27-0 **DEVID<27:0>:** Device ID<sup>(1)</sup>

-n = Value at POR

Note 1: See the "PIC32 Flash Programming Specification" (DS60001145) for a list of Revision and Device ID values.

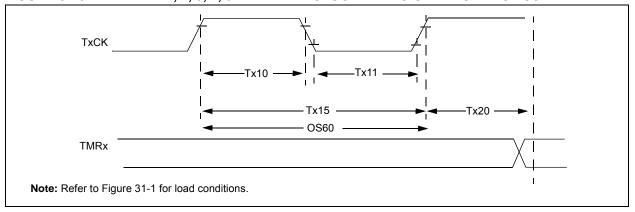

FIGURE 31-6: TIMER1, 2, 3, 4, 5 EXTERNAL CLOCK TIMING CHARACTERISTICS

### TABLE 31-24: TIMER1 EXTERNAL CLOCK TIMING REQUIREMENTS<sup>(1)</sup>

|                    | Standard Operating Co<br>(unless otherwise stat |                                                                                                           |

|--------------------|-------------------------------------------------|-----------------------------------------------------------------------------------------------------------|

| AC CHARACTERISTICS | Operating temperature                           | $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial $-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial |

|                    |                                                 | $-40^{\circ}$ C $\leq$ TA $\leq$ +105 $^{\circ}$ C for V-temp                                             |

| Param.<br>No. | Symbol                                                           | Charac                                                                                         | teristics <sup>(2)</sup>     | Min.                                    | Typical | Max. | Units | Conditions                         |

|---------------|------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------------------------------|-----------------------------------------|---------|------|-------|------------------------------------|

| TA10          | TA10 TTXH TXI<br>Hig                                             |                                                                                                | Synchronous, with prescaler  | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns       | _       | _    | ns    | Must also meet parameter TA15      |

|               |                                                                  |                                                                                                | Asynchronous, with prescaler | 10                                      | _       | _    | ns    | _                                  |

| TA11          | TTXL                                                             | TxCK<br>Low Time                                                                               | Synchronous, with prescaler  | [(12.5 ns or 1 TPB)/N]<br>+ 25 ns       | _       | _    | ns    | Must also meet parameter TA15      |

|               |                                                                  |                                                                                                | Asynchronous, with prescaler | 10                                      | _       | _    | ns    | _                                  |

| TA15          | ТтхР                                                             | TxCK<br>Input Period                                                                           | Synchronous, with prescaler  | [(Greater of 25 ns or 2 TPB)/N] + 30 ns | _       | _    | ns    | VDD > 2.7V                         |

|               |                                                                  |                                                                                                |                              | [(Greater of 25 ns or 2 TPB)/N] + 50 ns | _       | _    | ns    | VDD < 2.7V                         |

|               |                                                                  |                                                                                                | Asynchronous, with prescaler | 20                                      | _       | _    | ns    | V <sub>DD</sub> > 2.7V<br>(Note 3) |

|               |                                                                  |                                                                                                |                              | 50                                      | _       | _    | ns    | V <sub>DD</sub> < 2.7V<br>(Note 3) |

| OS60          | Fт1                                                              | SOSC1/T1CK Oscillator Input Frequency Range (oscillator enabled by setting TCS bit (T1CON<1>)) |                              | 32                                      | _       | 100  | kHz   | _                                  |

| TA20          | TCKEXTMRL Delay from External TxCK Clock Edge to Timer Increment |                                                                                                | _                            |                                         | 1       | Трв  | _     |                                    |

Note 1: Timer1 is a Type A.

2: This parameter is characterized, but not tested in manufacturing.

**3:** N = Prescale Value (1, 8, 64, 256).

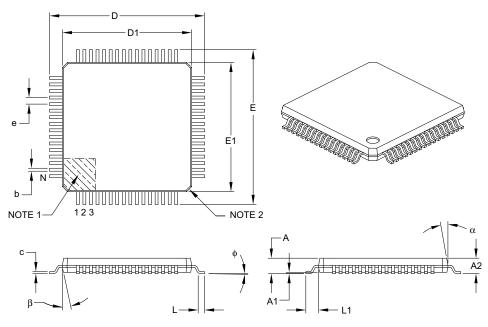

### 33.2 Package Details

The following sections give the technical details of the packages.

### 64-Lead Plastic Thin Quad Flatpack (PT) – 10x10x1 mm Body, 2.00 mm [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                          | Units         |           | MILLIMETERS | }    |  |  |  |

|--------------------------|---------------|-----------|-------------|------|--|--|--|

| Dime                     | ension Limits | MIN       | NOM         | MAX  |  |  |  |

| Number of Leads          | N             |           | 64          |      |  |  |  |

| Lead Pitch               | е             |           | 0.50 BSC    |      |  |  |  |

| Overall Height           | А             | -         | _           | 1.20 |  |  |  |

| Molded Package Thickness | A2            | 0.95      | 1.00        | 1.05 |  |  |  |

| Standoff                 | A1            | 0.05      | _           | 0.15 |  |  |  |

| Foot Length              | L             | 0.45      | 0.60        | 0.75 |  |  |  |

| Footprint                | L1            |           | 1.00 REF    |      |  |  |  |

| Foot Angle               | ф             | 0°        | 3.5°        | 7°   |  |  |  |

| Overall Width            | E             |           | 12.00 BSC   |      |  |  |  |

| Overall Length           | D             |           | 12.00 BSC   |      |  |  |  |

| Molded Package Width     | E1            | 10.00 BSC |             |      |  |  |  |

| Molded Package Length    | D1            |           | 10.00 BSC   |      |  |  |  |

| Lead Thickness           | С             | 0.09      | _           | 0.20 |  |  |  |

| Lead Width               | b             | 0.17      | 0.22        | 0.27 |  |  |  |

| Mold Draft Angle Top     | α             | 11°       | 12°         | 13°  |  |  |  |

| Mold Draft Angle Bottom  | β             | 11°       | 12°         | 13°  |  |  |  |

#### Notes:

- 1. Pin 1 visual index feature may vary, but must be located within the hatched area.

- 2. Chamfers at corners are optional; size may vary.

- 3. Dimensions D1 and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed 0.25 mm per side.

- 4. Dimensioning and tolerancing per ASME Y14.5M.

- BSC: Basic Dimension. Theoretically exact value shown without tolerances.

- REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-085B

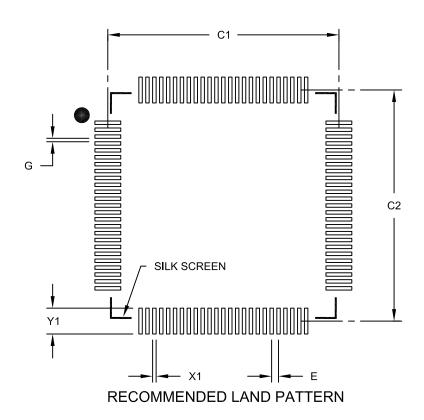

100-Lead Plastic Thin Quad Flatpack (PT)-12x12x1mm Body, 2.00 mm Footprint [TQFP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                           | N                | <b>IILLIMETER</b> | S        |      |  |  |  |

|---------------------------|------------------|-------------------|----------|------|--|--|--|

| Dimension                 | Dimension Limits |                   |          |      |  |  |  |

| Contact Pitch             | Е                |                   | 0.40 BSC |      |  |  |  |

| Contact Pad Spacing       | C1               |                   | 13.40    |      |  |  |  |

| Contact Pad Spacing       | C2               |                   | 13.40    |      |  |  |  |

| Contact Pad Width (X100)  | X1               |                   |          | 0.20 |  |  |  |

| Contact Pad Length (X100) | Y1               |                   |          | 1.50 |  |  |  |

| Distance Between Pads     | G                | 0.20              |          |      |  |  |  |

#### Notes:

1. Dimensioning and tolerancing per ASME Y14.5M

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing No. C04-2100B

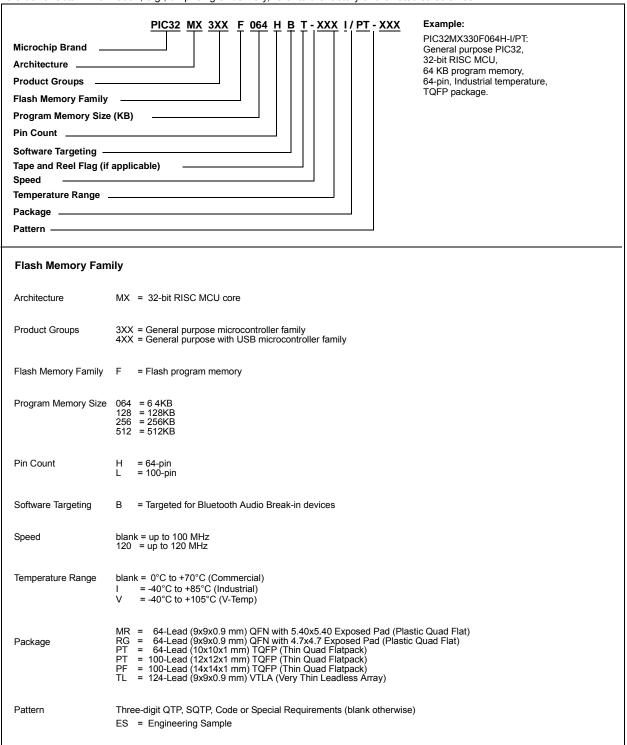

### PRODUCT IDENTIFICATION SYSTEM

To order or obtain information, e.g., on pricing or delivery, refer to the factory or the listed sales office.