Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFl

| 2 0 0 0 0 0                |                                                                                 |

|----------------------------|---------------------------------------------------------------------------------|

| Product Status             | Active                                                                          |

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                |                                                                                 |

| RAM Size                   | 128K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (14x14)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx470f512lt-v-pf |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

NOTES:

| TABLE 1-1: | PINOUT I/O DESCRIPTIONS | (CONTINUED) |

|------------|-------------------------|-------------|

|------------|-------------------------|-------------|

|                      |                                       | Pin Numb                              | er                                      |             |                | Description                                    |  |  |

|----------------------|---------------------------------------|---------------------------------------|-----------------------------------------|-------------|----------------|------------------------------------------------|--|--|

| Pin Name             | 64-pin<br>QFN/<br>TQFP                | 100-pin<br>TQFP                       | 124-pin<br>VTLA                         | Pin<br>Type | Buffer<br>Type |                                                |  |  |

| U1CTS                | PPS                                   | PPS                                   | PPS                                     | I           | ST             | UART1 Clear to Send                            |  |  |

| U1RTS                | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART1 Ready to Send                            |  |  |

| U1RX                 | PPS                                   | PPS                                   | PPS                                     | I           | ST             | UART1 Receive                                  |  |  |

| U1TX                 | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART1 Transmit                                 |  |  |

| U2CTS                | PPS                                   | PPS                                   | PPS                                     | I           | ST             | UART2 Clear to Send                            |  |  |

| U2RTS                | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART2 Ready to Send                            |  |  |

| U2RX                 | PPS                                   | PPS                                   | PPS                                     | I           | ST             | UART2 Receive                                  |  |  |

| U2TX                 | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART2 Transmit                                 |  |  |

| U3CTS                | PPS                                   | PPS                                   | PPS                                     |             | ST             | UART3 Clear to Send                            |  |  |

| U3RTS                | PPS                                   | PPS                                   | PPS                                     | 0           |                | UART3 Ready to Send                            |  |  |

| U3RX                 | PPS                                   | PPS                                   | PPS                                     |             | ST             | UART3 Receive                                  |  |  |

| U3TX                 | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART3 Transmit                                 |  |  |

| U4CTS                | PPS                                   | PPS                                   | PPS                                     | I           | ST             | UART4 Clear to Send                            |  |  |

| U4RTS                | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART4 Ready to Send                            |  |  |

| U4RX                 | PPS                                   | PPS                                   | PPS                                     | I           | ST             | UART4 Receive                                  |  |  |

| U4TX                 | PPS                                   | PPS                                   | PPS                                     | 0           | _              | UART4 Transmit                                 |  |  |

| U5CTS <sup>(3)</sup> | _                                     | PPS                                   | PPS                                     |             | ST             | UART5 Clear to Send                            |  |  |

| U5RTS <sup>(3)</sup> | _                                     | PPS                                   | PPS                                     | 0           |                | UART5 Ready to Send                            |  |  |

| U5RX <sup>(3)</sup>  | _                                     | PPS                                   | PPS                                     | I           | ST             | UART5 Receive                                  |  |  |

| U5TX <sup>(3)</sup>  | _                                     | PPS                                   | PPS                                     | 0           | _              | UART5 Transmit                                 |  |  |

| SCK1                 | 35 <sup>(1)</sup> , 50 <sup>(2)</sup> | 55 <sup>(1)</sup> , 70 <sup>(2)</sup> | B30 <sup>(1)</sup> , B38 <sup>(2)</sup> | I/O         | ST             | Synchronous Serial Clock Input/Output for SPI1 |  |  |

| SDI1                 | PPS                                   | PPS                                   | PPS                                     | 0           |                | SPI1 Data In                                   |  |  |

| SDO1                 | PPS                                   | PPS                                   | PPS                                     | I/O         | ST             | SPI1 Data Out                                  |  |  |

| SS1                  | PPS                                   | PPS                                   | PPS                                     | I/O         | —              | SPI1 Slave Synchronization for Frame Pulse I/O |  |  |

| SCK2                 | 4                                     | 10                                    | A7                                      | I/O         | ST             | Synchronous Serial Clock Input/Output for SPI2 |  |  |

| SDI2                 | PPS                                   | PPS                                   | PPS                                     | 0           |                | SPI2 Data In                                   |  |  |

| SDO2                 | PPS                                   | PPS                                   | PPS                                     | I/O         | ST             | SPI2 Data Out                                  |  |  |

| SS2                  | PPS                                   | PPS                                   | PPS                                     | I/O         | —              | SPI2 Slave Synchronization for Frame Pulse I/O |  |  |

| SCL1                 |                                       |                                       | B31 <sup>(1)</sup> , B36 <sup>(2)</sup> | I/O         | ST             | Synchronous Serial Clock Input/Output for I2C1 |  |  |

| SDA1                 | 36 <sup>(1)</sup> , 43 <sup>(2)</sup> | 56 <sup>(1)</sup> , 67 <sup>(2)</sup> | A38 <sup>(1)</sup> , A44 <sup>(2)</sup> | I/O         | ST             | Synchronous Serial Data Input/Output for I2C1  |  |  |

| SCL2                 | 32                                    | 58                                    | A39                                     | I/O         | ST             | Synchronous Serial Clock Input/Output for I2C2 |  |  |

| SDA2                 | 31                                    | 59                                    | B32                                     | I/O         | ST             | Synchronous Serial Data Input/Output for I2C2  |  |  |

| TMS                  | 23                                    | 17                                    | B9                                      |             | ST             | JTAG Test Mode Select Pin                      |  |  |

| ТСК                  | 27                                    | 38                                    | A26                                     | I           | ST             | JTAG Test Clock Input Pin                      |  |  |

| TDI                  | 28                                    | 60                                    | A40                                     | I           | _              | JTAG Test Clock Input Pin                      |  |  |

| TDO                  | 24                                    | 61                                    | B33                                     | 0           | —              | JTAG Test Clock Output Pin                     |  |  |

| RTCC                 | 42                                    | 68                                    | B37                                     | 0           | —              | Real-Time Clock Alarm Output                   |  |  |

ST = Schmitt Trigger input with CMOS levels

O = Output

I = Input

TTL = TTL input buffer

**Note 1:** This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices.

## 3.2 Architecture Overview

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core contains several logic blocks working together in parallel, providing an efficient high-performance computing engine. The following blocks are included with the core:

- Execution Unit

- Multiply/Divide Unit (MDU)

- System Control Coprocessor (CP0)

- Fixed Mapping Translation (FMT)

- Dual Internal Bus interfaces

- Power Management

- MIPS16e<sup>®</sup> Support

- Enhanced JTAG (EJTAG) Controller

## 3.2.1 EXECUTION UNIT

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The core contains thirty-two 32-bit General Purpose Registers (GPRs) used for integer operations and address calculation. One additional register file shadow set (containing thirty-two registers) is added to minimize context switching overhead during interrupt/exception processing. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Address unit for calculating the next instruction

address

- Logic for branch determination and branch target address calculation

- · Load aligner

- Bypass multiplexers used to avoid stalls when executing instruction streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter and store aligner

## 3.2.2 MULTIPLY/DIVIDE UNIT (MDU)

The MIPS32<sup>®</sup> M4K<sup>®</sup> processor core includes a Multiply/Divide Unit (MDU) that contains a separate pipeline for multiply and divide operations. This pipeline operates in parallel with the Integer Unit (IU) pipeline and does not stall when the IU pipeline stalls. This allows MDU operations to be partially masked by system stalls and/or other integer unit instructions.

The high-performance MDU consists of a 32x16 booth recoded multiplier, result/accumulation registers (HI and LO), a divide state machine, and the necessary multiplexers and control logic. The first number shown ('32' of 32x16) represents the *rs* operand. The second number ('16' of 32x16) represents the *rt* operand. The PIC32 core only checks the value of the latter (*rt*) operand to determine how many times the operation must pass through the multiplier. The 16x16 and 32x16 operations pass through the multiplier once. A 32x32 operation passes through the multiplier twice.

The MDU supports execution of one 16x16 or 32x16 multiply operation every clock cycle; 32x32 multiply operations can be issued every other clock cycle. Appropriate interlocks are implemented to stall the issuance of back-to-back 32x32 multiply operations. The multiply operand size is automatically determined by logic built into the MDU.

Divide operations are implemented with a simple 1 bit per clock iterative algorithm. An early-in detection checks the sign extension of the dividend (*rs*) operand. If *rs* is 8 bits wide, 23 iterations are skipped. For a 16-bit wide *rs*, 15 iterations are skipped and for a 24-bit wide *rs*, 7 iterations are skipped. Any attempt to issue a subsequent MDU instruction while a divide is still active causes an IU pipeline stall until the divide operation is completed.

Table 3-1 lists the repeat rate (peak issue rate of cycles until the operation can be reissued) and latency (number of cycles until a result is available) for the PIC32 core multiply and divide instructions. The approximate latency and repeat rates are listed in terms of pipeline clocks.

| Divide UNIT LATENCIES AND REPEAT RATES |                                                |         |             |  |  |  |  |  |  |

|----------------------------------------|------------------------------------------------|---------|-------------|--|--|--|--|--|--|

| Op code                                | Operand Size (mul <i>rt</i> ) (div <i>rs</i> ) | Latency | Repeat Rate |  |  |  |  |  |  |

| MULT/MULTU, MADD/MADDU,                | 16 bits                                        | 1       | 1           |  |  |  |  |  |  |

| MSUB/MSUBU                             | 32 bits                                        | 2       | 2           |  |  |  |  |  |  |

| MUL                                    | 16 bits                                        | 2       | 1           |  |  |  |  |  |  |

|                                        | 32 bits                                        | 3       | 2           |  |  |  |  |  |  |

| DIV/DIVU                               | 8 bits                                         | 12      | 11          |  |  |  |  |  |  |

|                                        | 16 bits                                        | 19      | 18          |  |  |  |  |  |  |

|                                        | 24 bits                                        | 26      | 25          |  |  |  |  |  |  |

|                                        | 32 bits                                        | 33      | 32          |  |  |  |  |  |  |

## TABLE 3-1: MIPS32<sup>®</sup> M4K<sup>®</sup> PROCESSOR CORE HIGH-PERFORMANCE INTEGER MULTIPLY/ DIVIDE UNIT LATENCIES AND REPEAT RATES

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 24.04        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 31:24        | BMXPFMSZ<31:24>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 22:16        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 23:16        | BMXPFMSZ<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 15:8         | BMXPFMSZ<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |

| 7:0          |                   |                   |                   | BMXPF             | MSZ<7:0>          |                   |                  |                  |  |  |  |

## REGISTER 4-7: BMXPFMSZ: PROGRAM FLASH (PFM) SIZE REGISTER

# Legend:

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 BMXPFMSZ<31:0>: Program Flash Memory (PFM) Size bits

Static value that indicates the size of the PFM in bytes: 0x00010000 = Device has 64 KB Flash 0x00020000 = Device has 128 KB Flash 0x00040000 = Device has 256 KB Flash 0x00080000 = Device has 512 KB Flash

#### REGISTER 4-8: BMXBOOTSZ: BOOT FLASH (IFM) SIZE REGISTER

|              |                   |                   |                   | . ,               |                   |                   |                  |                  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

| 24.24        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 31:24        | BMXBOOTSZ<31:24>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 00.40        | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 23:16        | BMXBOOTSZ<23:16>  |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 45.0         | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 15:8         | BMXBOOTSZ<15:8>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |

| 7.0          | R                 | R                 | R                 | R                 | R                 | R                 | R                | R                |  |  |  |  |

| 7:0          |                   |                   |                   | BMXBO             | OTSZ<7:0>         |                   |                  |                  |  |  |  |  |

| Legend:           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-0 **BMXBOOTSZ<31:0>:** Boot Flash Memory (BFM) Size bits Static value that indicates the size of the Boot PFM in bytes: 0x00003000 = Device has 12 KB Boot Flash

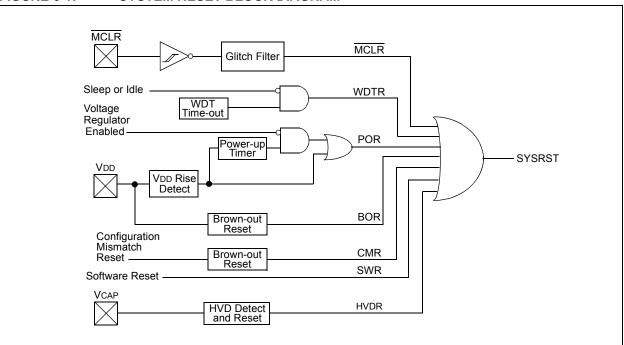

# 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Master Clear Reset pin

- · SWR: Software Reset

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CMR: Configuration Mismatch Reset

- HVDR: High Voltage Detect Reset

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

## FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

## 6.1 Reset Control Registers

## TABLE 6-1: SYSTEM CONTROL REGISTER MAP

| ess                       |                                 | 6         | Bits  |       |       |       |       |       |      |       |      |      |      |      | ts    |      |      |       |                     |

|---------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|-------|------|------|------|------|-------|------|------|-------|---------------------|

| Virtual Addre<br>(BF80_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8  | 23/7 | 22/6 | 21/5 | 20/4 | 19/3  | 18/2 | 17/1 | 16/0  | All Reset           |

| F600                      | RCON                            | 31:16     | _     | —     | HVDR  | _     | —     | —     | _    | _     | —    | _    | _    | —    | —     | _    | _    | —     | 0000                |

| FOUU                      | RCON                            | 15:0      | Ι     | —     |       | _     | _     | _     | CMR  | VREGS | EXTR | SWR  | —    | WDTO | SLEEP | IDLE | BOR  | POR   | xxxx <sup>(2)</sup> |

| E610                      | RSWRST                          | 31:16     | Ι     | —     |       | _     | _     | _     | —    | _     | —    |      | —    | —    | —     | _    | _    | —     | 0000                |

| FUIU                      | ROWROI                          | 15:0      | _     | _     | _     | -     | _     | _     | _    | -     | _    | _    | -    | _    | _     | -    | _    | SWRST | 0000                |

Legend: x = unknown value on Reset; - = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

2: Reset values are dependent on the DEVCFGx Configuration bits and the type of reset.

## REGISTER 8-1: OSCCON: OSCILLATOR CONTROL REGISTER (CONTINUED)

- bit 2 UFRCEN: USB FRC Clock Enable bit<sup>(1)</sup>

- 1 = Enable FRC as the clock source for the USB clock source

- 0 = Use the Primary Oscillator or USB PLL as the USB clock source

- bit 1 SOSCEN: Secondary Oscillator (Sosc) Enable bit

- 1 = Enable Secondary Oscillator

- 0 = Disable Secondary Oscillator

- bit 0 **OSWEN:** Oscillator Switch Enable bit

- 1 = Initiate an oscillator switch to selection specified by NOSC<2:0> bits

- 0 = Oscillator switch is complete

- Note 1: This bit is available on PIC32MX4XX devices only.

**Note:** Writes to this register require an unlock sequence. Refer to **Section 6. "Oscillator"** (DS60001112) in the *"PIC32 Family Reference Manual"* for details.

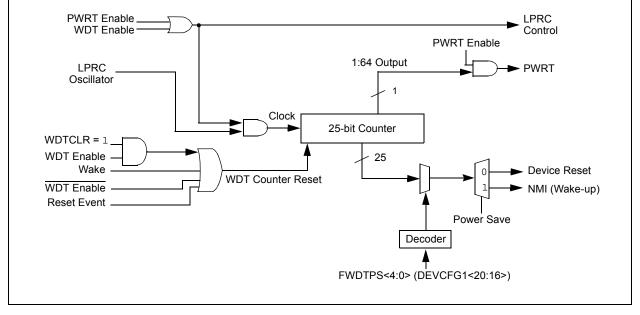

# 15.0 WATCHDOG TIMER (WDT)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 9. "Watchdog, Deadman, and Power-up Timers" (DS60001114), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32). The WDT, when enabled, operates from the internal Low-Power Oscillator (LPRC) clock source and can be used to detect system software malfunctions by resetting the device if the WDT is not cleared periodically in software. Various WDT time-out periods can be selected using the WDT postscaler. The WDT can also be used to wake the device from Sleep or Idle mode.

The following are some of the key features of the WDT module:

- · Configuration or software controlled

- User-configurable time-out period

- Can wake the device from Sleep or Idle

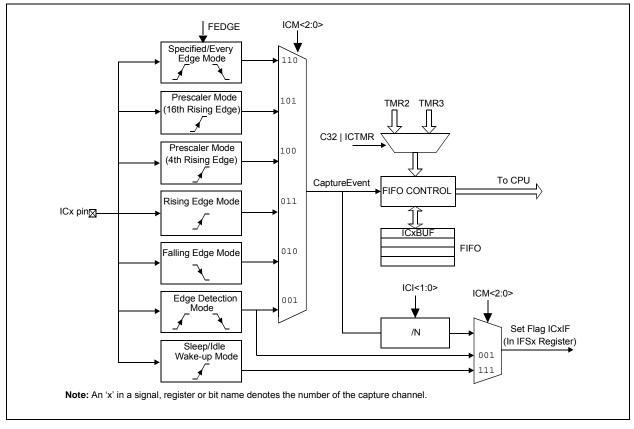

# 16.0 INPUT CAPTURE

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 15. "Input Capture" (DS60001122), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Input Capture module is useful in applications requiring frequency (period) and pulse measurement.

The Input Capture module captures the 16-bit or 32-bit value of the selected Time Base registers when an event occurs at the ICx pin. The following events cause capture events:

- Simple capture event modes:

- Capture timer value on every falling edge of input at ICx pin

- Capture timer value on every rising edge of input at ICx pin

- Capture timer value on every edge (rising and falling)

- Capture timer value on every edge (rising and falling), specified edge first.

- Prescaler capture event modes:

- Capture timer value on every 4th rising edge of input at ICx pin

- Capture timer value on every 16th rising edge of input at ICx pin

Each input capture channel can select between one of two 16-bit timers (Timer2 or Timer3) for the time base, or two 16-bit timers (Timer2 and Timer3) together to form a 32-bit timer. The selected timer can use either an internal or external clock.

Other operational features include:

- Device wake-up from capture pin during CPU Sleep and Idle modes

- · Interrupt on input capture event

- 4-word FIFO buffer for capture values Interrupt optionally generated after 1, 2, 3, or 4 buffer locations are filled

- Input capture can also be used to provide additional sources of external interrupts

## FIGURE 16-1: INPUT CAPTURE BLOCK DIAGRAM

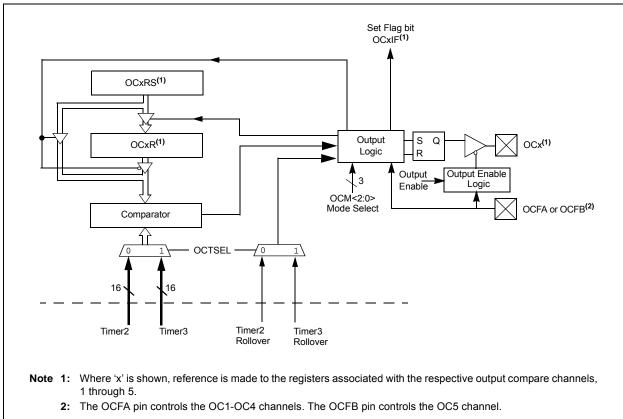

# 17.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Output Compare" (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are key features of this module:

- Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

## FIGURE 17-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4    | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|----------------------|-------------------|-------------------|------------------|------------------|

| 21.24        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 31:24        | _                 | —                 | -                 | -                    | _                 | _                 | —                | —                |

| 00.40        | U-0               | U-0               | U-0               | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 23:16        |                   |                   | _                 | _                    | _                 | _                 | —                | —                |

| 45.0         | R/W-0             | U-0               | R/W-0             | U-0                  | U-0               | U-0               | U-0              | U-0              |

| 15:8         | ON <sup>(1)</sup> | _                 | SIDL              | _                    | _                 | _                 | —                | —                |

| 7.0          | U-0               | U-0               | R/W-0             | R-0                  | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          |                   | -                 | OC32              | OCFLT <sup>(2)</sup> | OCTSEL            |                   | OCM<2:0>         |                  |

## REGISTER 17-1: OCxCON: OUTPUT COMPARE 'x' CONTROL REGISTER

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, i | read as '0'        |

|-------------------|------------------|--------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

- bit 15 **ON:** Output Compare Peripheral On bit<sup>(1)</sup>

- 1 = Output Compare peripheral is enabled

- 0 = Output Compare peripheral is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Stop in Idle Mode bit

- 1 = Discontinue operation when CPU enters Idle mode

- 0 = Continue operation in Idle mode

- bit 12-6 Unimplemented: Read as '0'

- bit 5 OC32: 32-bit Compare Mode bit

- 1 = OCxR<31:0> and/or OCxRS<31:0> are used for comparisions to the 32-bit timer source 0 = OCxR<15:0> and OCxRS<15:0> are used for comparisons to the 16-bit timer source

- bit 4 OCFLT: PWM Fault Condition Status bit<sup>(2)</sup>

- 1 = PWM Fault condition has occurred (cleared in HW only)

- 0 = No PWM Fault condition has occurred

- bit 3 OCTSEL: Output Compare Timer Select bit

- 1 = Timer3 is the clock source for this Output Compare module

- 0 = Timer2 is the clock source for this Output Compare module

- bit 2-0 OCM<2:0>: Output Compare Mode Select bits

- 111 = PWM mode on OCx; Fault pin is enabled

- 110 = PWM mode on OCx; Fault pin is disabled

- 101 = Initialize OCx pin low; generate continuous output pulses on OCx pin

- 100 = Initialize OCx pin low; generate single output pulse on OCx pin

- 011 = Compare event toggles OCx pin

- 010 = Initialize OCx pin high; compare event forces OCx pin low

- 001 = Initialize OCx pin low; compare event forces OCx pin high

- 000 = Output compare peripheral is disabled but continues to draw current

- **Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

- **2:** This bit is only used when OCM<2:0> = '111'. It is read as '0' in all other modes.

## REGISTER 19-2: I2CxSTAT: I<sup>2</sup>C STATUS REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 31:24        | —                 | —                 | -                 | -                 | —                 | _                 | -                | _                |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |

| 23:16        |                   | —                 | _                 | _                 | _                 |                   | _                | -                |  |  |  |  |

| 45.0         | R-0, HSC          | R-0, HSC          | U-0               | U-0               | U-0               | R/C-0, HS         | R-0, HSC         | R-0, HSC         |  |  |  |  |

| 15:8         | ACKSTAT           | TRSTAT            | -                 | _                 | _                 | BCL               | GCSTAT           | ADD10            |  |  |  |  |

| 7:0          | R/C-0, HS         | R/C-0, HS         | R-0, HSC          | R/C-0, HSC        | R/C-0, HSC        | R-0, HSC          | R-0, HSC         | R-0, HSC         |  |  |  |  |

| 7:0          | IWCOL             | I2COV             | D_A               | Р                 | S                 | R_W               | RBF              | TBF              |  |  |  |  |

| Legend:           | HS = Set in hardware | ware HSC = Hardware set/cleared    |                   |

|-------------------|----------------------|------------------------------------|-------------------|

| R = Readable bit  | W = Writable bit     | U = Unimplemented bit, read as '0' |                   |

| -n = Value at POR | '1' = Bit is set     | '0' = Bit is cleared               | C = Clearable bit |

#### bit 31-16 Unimplemented: Read as '0'

bit 15 ACKSTAT: Acknowledge Status bit

(when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Acknowledge was not received from slave

- 0 = Acknowledge was received from slave

Hardware set or clear at end of slave Acknowledge.

- bit 14 **TRSTAT:** Transmit Status bit (when operating as I<sup>2</sup>C master, applicable to master transmit operation)

- 1 = Master transmit is in progress (8 bits + ACK)

- 0 = Master transmit is not in progress

Hardware set at beginning of master transmission. Hardware clear at end of slave Acknowledge.

- bit 13-11 Unimplemented: Read as '0'

- bit 10 BCL: Master Bus Collision Detect bit

1 = A bus collision has been detected during a master operation

0 = No collision

Hardware set at detection of bus collision. This condition can only be cleared by disabling (ON bit = 0) and re-enabling (ON bit = 1) the module.

- bit 9 **GCSTAT:** General Call Status bit

- 1 = General call address was received

- 0 = General call address was not received

Hardware set when address matches general call address. Hardware clear at Stop detection.

bit 8 ADD10: 10-bit Address Status bit

1 = 10-bit address was matched

0 = 10-bit address was not matched

Hardware set at match of 2nd byte of matched 10-bit address. Hardware clear at Stop detection.

- bit 7 IWCOL: Write Collision Detect bit

- 1 = An attempt to write the I2CxTRN register failed because the I<sup>2</sup>C module is busy

- 0 = No collision

Hardware set at occurrence of write to I2CxTRN while busy (cleared by software).

bit 6 I2COV: Receive Overflow Flag bit

1 = A byte was received while the I2CxRCV register is still holding the previous byte 0 = No overflow

Hardware set at attempt to transfer I2CxRSR to I2CxRCV (cleared by software).

- bit 5 **D\_A:** Data/Address bit (when operating as I<sup>2</sup>C slave)

- 1 = Indicates that the last byte received was data

- 0 = Indicates that the last byte received was device address

Hardware clear at device address match. Hardware set by reception of slave byte.

#### REGISTER 22-2: RTCALRM: RTC ALARM CONTROL REGISTER (CONTINUED)

bit 7-0 ARPT<7:0>: Alarm Repeat Counter Value bits<sup>(3)</sup> 11111111 = Alarm will trigger 256 times

0000000 = Alarm will trigger one time

The counter decrements on any alarm event. The counter only rolls over from 0x00 to 0xFF if CHIME = 1.

- **Note 1:** Hardware clears the ALRMEN bit anytime the alarm event occurs, when ARPT<7:0> = 00 and CHIME = 0.

- 2: This field should not be written when the RTCC ON bit = '1' (RTCCON<15>) and ALRMSYNC = 1.

- 3: This assumes a CPU read will execute in less than 32 PBCLKs.

Note: This register is reset only on a Power-on Reset (POR).

| Bit<br>Range                      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5                  | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|-----------------------------------|-------------------|-------------------|------------------------------------|-------------------|-----------------------------------------|-------------------|------------------|------------------|

| 04.04                             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |

| 31:24                             |                   | HR10              | <3:0>                              |                   |                                         | HR01              | <3:0>            |                  |

| 23:16                             | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |

|                                   | MIN10<3:0>        |                   |                                    | MIN01<3:0>        |                                         |                   |                  |                  |

| 45.0                              | R/W-x             | R/W-x             | R/W-x                              | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |

| 15:8                              | SEC10<3:0>        |                   |                                    |                   | SEC01<3:0>                              |                   |                  |                  |

| 7.0                               | U-0               | U-0               | U-0                                | U-0               | U-0                                     | U-0               | U-0              | U-0              |

| 7:0                               | _                 | _                 | _                                  |                   | _                                       | _                 |                  | —                |

|                                   |                   |                   |                                    |                   |                                         |                   |                  |                  |

| Legend:                           |                   |                   |                                    |                   |                                         |                   |                  |                  |

| R = Readable bit W = Writable bit |                   |                   | U = Unimplemented bit, read as '0' |                   |                                         |                   |                  |                  |

| -n = Value at POR                 |                   |                   | '1' = Bit is se                    | t                 | '0' = Bit is cleared x = Bit is unknown |                   |                  | known            |

## REGISTER 22-5: ALRMTIME: ALARM TIME VALUE REGISTER

bit 31-28 HR10<3:0>: Binary Coded Decimal value of hours bits, 10s place digits; contains a value from 0 to 2

bit 27-24 HR01<3:0>: Binary Coded Decimal value of hours bits, 1s place digit; contains a value from 0 to 9

bit 23-20 MIN10<3:0>: Binary Coded Decimal value of minutes bits, 10s place digits; contains a value from 0 to 5

bit 19-16 MIN01<3:0>: Binary Coded Decimal value of minutes bits, 1s place digit; contains a value from 0 to 9

bit 15-12 SEC10<3:0>: Binary Coded Decimal value of seconds bits, 10s place digits; contains a value from 0 to 5

bit 11-8 SEC01<3:0>: Binary Coded Decimal value of seconds bits, 1s place digit; contains a value from 0 to 9

bit 7-0 Unimplemented: Read as '0'

| Bit<br>Range | Bit<br>31/23/15/7    | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|----------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | CH0NB                | _                 | —                 | CH0SB<4:0>        |                   |                   |                  |                  |  |  |  |

| 00.40        | R/W-0                | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | CH0NA <sup>(3)</sup> | _                 | —                 | CH0SA<4:0>        |                   |                   |                  |                  |  |  |  |

| 45.0         | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 15:8         | —                    | -                 | —                 | _                 | _                 |                   | _                | _                |  |  |  |

| 7:0          | U-0                  | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 7:0          | —                    | _                 | _                 | _                 | _                 | _                 | _                | _                |  |  |  |

#### REGISTER 23-4: AD1CHS: ADC INPUT SELECT REGISTER

## Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

| bit 31    | CH0NB: Negative Input Select bit for Sample B                                      |

|-----------|------------------------------------------------------------------------------------|

|           | 1 = Channel 0 negative input is AN1                                                |

|           | 0 = Channel 0 negative input is VREFL                                              |

| bit 30-29 | Unimplemented: Read as '0'                                                         |

| bit 28-24 | CH0SB<4:0>: Positive Input Select bits for Sample B                                |

|           | 11110 = Channel 0 positive input is Open <sup>(1)</sup>                            |

|           | 11101 = Channel 0 positive input is CTMU temperature sensor (CTMUT) <sup>(2)</sup> |

|           | 11100 = Channel 0 positive input is IVREF <sup>(3)</sup>                           |

|           | 11011 = Channel 0 positive input is AN27                                           |

|           | •                                                                                  |

|           | •                                                                                  |

|           | •                                                                                  |

|           | 00001 = Channel 0 positive input is AN1                                            |

|           | 00000 = Channel 0 positive input is AN0                                            |

| bit 23    | CH0NA: Negative Input Select bit for Sample A Multiplexer Setting <sup>(3)</sup>   |

|           | 1 = Channel 0 negative input is AN1                                                |

|           | 0 = Channel 0 negative input is VREFL                                              |

| bit 22-21 | Unimplemented: Read as '0'                                                         |

| bit 20-16 | CH0SA<4:0>: Positive Input Select bits for Sample A Multiplexer Setting            |

|           | 11110 = Channel 0 positive input is Open <sup>(1)</sup>                            |

|           | 11101 = Channel 0 positive input is CTMU temperature sensor (CTMUT) <sup>(2)</sup> |

|           | 11100 = Channel 0 positive input is IVREF <sup>(3)</sup>                           |

|           | 11011 = Channel 0 positive input is AN27                                           |

|           | •                                                                                  |

|           | •                                                                                  |

|           | •                                                                                  |

|           | 00001 = Channel 0 positive input is AN1                                            |

|           | 00000 = Channel 0 positive input is AN0                                            |

| bit 15-0  | Unimplemented: Read as '0'                                                         |

| Note 1:   | This selection is only used with CTMU capacitive and time measurement.             |

| 2:        | See Section 26.0 "Charge Time Measurement Unit (CTMU)" for more information.       |

3: See Section 25.0 "Comparator Voltage Reference (CVREF)" for more information.

# REGISTER 26-1: CTMUCON: CTMU CONTROL REGISTER (CONTINUED)

| REGIST    | ER 26-1: CIMUCON: CIMU CONTROL REGISTER (CONTINUE                                                                                     |

|-----------|---------------------------------------------------------------------------------------------------------------------------------------|

| bit 24    | EDG1STAT: Edge 1 Status bit                                                                                                           |

|           | Indicates the status of Edge 1 and can be written to control edge source                                                              |

|           | 1 = Edge 1 has occurred                                                                                                               |

|           | 0 = Edge 1 has not occurred                                                                                                           |

| bit 23    | EDG2MOD: Edge 2 Edge Sampling Select bit                                                                                              |

|           | 1 = Input is edge-sensitive                                                                                                           |

|           | 0 = Input is level-sensitive                                                                                                          |

| bit 22    | EDG2POL: Edge 2 Polarity Select bit                                                                                                   |

|           | 1 = Edge 2 programmed for a positive edge response                                                                                    |

|           | 0 = Edge 2 programmed for a negative edge response                                                                                    |

| DIT 21-18 | EDG2SEL<3:0>: Edge 2 Source Select bits                                                                                               |

|           | 1111 = Reserved                                                                                                                       |

|           | 1110 = C2OUT pin is selected<br>1101 = C1OUT pin is selected                                                                          |

|           | 1100 = PBCLK clock is selected                                                                                                        |

|           | 1011 = IC3 Capture Event is selected                                                                                                  |

|           | 1010 = IC2 Capture Event is selected                                                                                                  |

|           | 1001 = IC1 Capture Event is selected                                                                                                  |

|           | 1000 = CTED13 pin is selected                                                                                                         |

|           | 0111 = CTED12 pin is selected<br>0110 = CTED11 pin is selected                                                                        |

|           | 0101 = CTED10 pin is selected                                                                                                         |

|           | 0100 = CTED9 pin is selected                                                                                                          |

|           | 0011 = CTED1 pin is selected                                                                                                          |

|           | 0010 = CTED2 pin is selected                                                                                                          |

|           | 0001 = OC1 Compare Event is selected                                                                                                  |

|           | 0000 = Timer1 Event is selected                                                                                                       |

|           | Unimplemented: Read as '0'                                                                                                            |

| bit 15    | ON: ON Enable bit                                                                                                                     |

|           | 1 = Module is enabled                                                                                                                 |

| h:+ 4.4   | 0 = Module is disabled                                                                                                                |

| bit 14    | Unimplemented: Read as '0'                                                                                                            |

| bit 13    | CTMUSIDL: Stop in Idle Mode bit                                                                                                       |

|           | <ul> <li>1 = Discontinue module operation when device enters Idle mode</li> <li>0 = Continue module operation in Idle mode</li> </ul> |

| bit 12    | <b>TGEN:</b> Time Generation Enable bit <sup>(1)</sup>                                                                                |

| DIL 12    |                                                                                                                                       |

|           | <ul><li>1 = Enables edge delay generation</li><li>0 = Disables edge delay generation</li></ul>                                        |

| bit 11    | EDGEN: Edge Enable bit                                                                                                                |

|           | 1 = Edges are not blocked                                                                                                             |

|           | $\Omega = Edges are blocked$                                                                                                          |

- **Note 1:** When this bit is set for Pulse Delay Generation, the EDG2SEL<3:0> bits must be set to '1110' to select C2OUT.

- 2: The ADC module Sample and Hold capacitor is not automatically discharged between sample/conversion cycles. Software using the ADC as part of a capacitive measurement, must discharge the ADC capacitor before conducting the measurement. The IDISSEN bit, when set to '1', performs this function. The ADC module must be sampling while the IDISSEN bit is active to connect the discharge sink to the capacitor array.

- 3: Refer to the CTMU Current Source Specifications (Table 31-42) in Section 31.0 "Electrical Characteristics" for current values.

- 4: This bit setting is not available for the CTMU temperature diode.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4             | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------|-------------------|-------------------|-------------------|-------------------------------|-------------------|-------------------|------------------|------------------|--|

| 24.24        | r-1               | r-1               | r-1               | r-1                           | r-1               | r-1               | R/P              | R/P              |  |

| 31:24        |                   | _                 | _                 | -                             | —                 | _                 | FWDTWINSZ<1:0>   |                  |  |

| 00.40        | R/P               | R/P               | r-1               | R/P                           | R/P               | R/P               | R/P              | R/P              |  |

| 23:16        | FWDTEN            | WINDIS            |                   | WDTPS<4:0>                    |                   |                   |                  |                  |  |

| 45.0         | R/P               | R/P               | R/P               | R/P                           | r-1               | R/P               | R/P              | R/P              |  |

| 15:8         | FCKSM             | 1<1:0>            | FPBDI             | V<1:0> — OSCIOFNC POSCMOD<1:0 |                   |                   |                  |                  |  |

| 7.0          | R/P               | r-1               | R/P               | r-1                           | r-1               | R/P               | R/P              | R/P              |  |

| 7:0          | IESO              | _                 | FSOSCEN           | _                             | —                 | F                 | NOSC<2:0>        | •                |  |

### REGISTER 28-2: DEVCFG1: DEVICE CONFIGURATION WORD 1

| Legend:           | r = Reserved bit | it P = Programmable bit            |                    |  |

|-------------------|------------------|------------------------------------|--------------------|--|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, read as '0' |                    |  |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared               | x = Bit is unknown |  |

#### bit 31-26 Reserved: Write '1'

bit 25-24 FWDTWINSZ<1:0>: Watchdog Timer Window Size bits

- 11 = Window size is 25%

- 10 = Window size is 37.5%

- 01 = Window size is 50%

- 00 = Window size is 75%

#### bit 23 FWDTEN: Watchdog Timer Enable bit

- 1 = Watchdog Timer is enabled and cannot be disabled by software

- 0 = Watchdog Timer is not enabled; it can be enabled in software

#### bit 22 WINDIS: Watchdog Timer Window Enable bit

- 1 = Watchdog Timer is in non-Window mode

- 0 = Watchdog Timer is in Window mode

#### bit 21 Reserved: Write '1'

#### bit 20-16 WDTPS<4:0>: Watchdog Timer Postscale Select bits

| 10100 <b>= 1:1048576</b>                                     |

|--------------------------------------------------------------|

| 10011 <b>= 1:524288</b>                                      |

| 10010 <b>= 1:262144</b>                                      |

| 10001 = 1:131072                                             |

| 10000 <b>= 1:65536</b>                                       |

| 01111 <b>= 1:32768</b>                                       |

| 01110 <b>= 1:16384</b>                                       |

| 01101 <b>= 1:8192</b>                                        |

| 01100 <b>= 1:4096</b>                                        |

| 01011 <b>= 1:2048</b>                                        |

| 01010 <b>= 1:1024</b>                                        |

| 01001 <b>= 1:512</b>                                         |

| 01000 <b>= 1:256</b>                                         |

| 00111 <b>= 1:128</b>                                         |

| 00110 = 1:64                                                 |

| 00101 <b>= 1:32</b>                                          |

| 00100 <b>= 1:16</b>                                          |

| 00011 = 1:8                                                  |

| 00010 <b>= 1</b> :4                                          |

| 00001 <b>= 1:2</b>                                           |

| 00000 = 1:1                                                  |

| All other combinations not shown result in operation = 10100 |

| ···· · ··· · ··· · ··· · ··· · ···                           |

**Note 1:** Do not disable the Posc (POSCMOD = 11) when using this oscillator source.

## REGISTER 28-3: DEVCFG2: DEVICE CONFIGURATION WORD 2 (CONTINUED)

- bit 2-0 **FPLLIDIV<2:0>:** PLL Input Divider bits

- 111 = 12x divider

- 110 = 10x divider

- 101 = 6x divider

- 100 = 5x divider

- 011 = 4x divider

- 010 = 3x divider

- 001 = 2x divider

- 000 = 1x divider

- Note 1: This bit is available on PIC32MX4XX devices only.

# PIC32MX330/350/370/430/450/470

# PIC32MX330/350/370/430/450/470

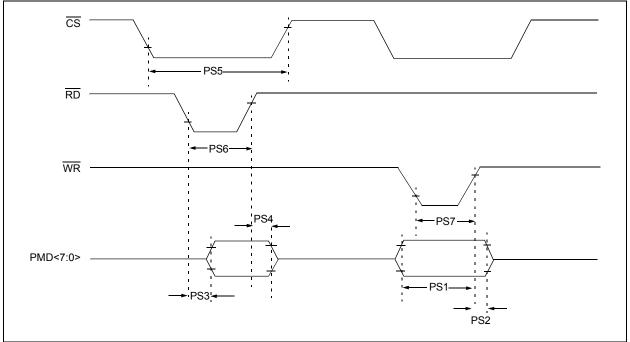

## FIGURE 31-20: PARALLEL SLAVE PORT TIMING

## TABLE 31-38: PARALLEL SLAVE PORT REQUIREMENTS

|               |                                                             |                                                                                  | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |   |    |    |            |

|---------------|-------------------------------------------------------------|----------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|----|----|------------|

| Para<br>m.No. | Symbol Characteristics <sup>1</sup> Min Typ Max Units Condi |                                                                                  |                                                                                                                                                                                                                                                                                                                                                     |   |    |    | Conditions |

| PS1           | TdtV2wr<br>H                                                | Data In Valid before $\overline{WR}$ or $\overline{CS}$<br>Inactive (setup time) | 20                                                                                                                                                                                                                                                                                                                                                  |   | _  | ns | _          |

| PS2           | TwrH2dt<br>I                                                | WR or CS Inactive to Data-In Invalid (hold time)                                 | 40                                                                                                                                                                                                                                                                                                                                                  | — | —  | ns | _          |

| PS3           | TrdL2dt<br>V                                                | RD and CS Active to Data-Out Valid                                               | _                                                                                                                                                                                                                                                                                                                                                   |   | 60 | ns | _          |

| PS4           | TrdH2dtl                                                    | RD Active or CS Inactive to Data-Out Invalid                                     | 0                                                                                                                                                                                                                                                                                                                                                   |   | 10 | ns | _          |

| PS5           | Tcs                                                         | CS Active Time                                                                   | Трв + 40                                                                                                                                                                                                                                                                                                                                            |   | —  | ns | —          |

| PS6           | Twr                                                         | WR Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                                                                                            |   | _  | ns | _          |

| PS7           | Trd                                                         | RD Active Time                                                                   | Трв + 25                                                                                                                                                                                                                                                                                                                                            | _ | _  | ns | _          |

Note 1: These parameters are characterized, but not tested in manufacturing.