Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Product Status             | Active                                                                          |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 81                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 128K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 100-TQFP                                                                        |

| Supplier Device Package    | 100-TQFP (12x12)                                                                |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx470f512lt-v-pt |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 7: PIN NAMES FOR 124-PIN DEVICES (CONTINUED)

| 124               | -PIN VTLA (BOTTOM VIEW) <sup>(1,2,3,4)</sup>                             | 17       |                   |                | A34           |                       |

|-------------------|--------------------------------------------------------------------------|----------|-------------------|----------------|---------------|-----------------------|

|                   | A                                                                        | 17       |                   | B13 B29        |               | nductive<br>ermal Pad |

|                   | PIC32MX430F064L<br>PIC32MX450F128L<br>PIC32MX450F256L<br>PIC32MX470F512L |          |                   | B1<br>B56      | B41           | A51                   |

|                   |                                                                          | y Indica | A1<br>tor         | A68            |               |                       |

| Package<br>Bump # | Full Pin Name                                                            |          | Package<br>Bump # |                | Full Pin Name |                       |

| B7                | MCLR                                                                     |          | B32               | SDA2/RA3       |               |                       |

| B8                | Vss                                                                      |          | B33               | TDO/RA5        |               |                       |

| B9                | TMS/CTED1/RA0                                                            |          | B34               | OSC1/CLKI/RC12 | 2             |                       |

| B10               | RPE9/RE9                                                                 |          | B35               | No Connect     |               |                       |

| B11               | AN4/C1INB/RB4                                                            |          | B36               | SCL1/RPA14/RA  | 14            |                       |

| B12               | Vss                                                                      |          | B37               | RPD8/RTCC/RD8  | 8             |                       |

| B13               | PGEC3/AN2/C2INB/RPB2/CTED13/RB2                                          |          | B38               | RPD10/SCK1/PM  | CS2/RD10      |                       |

| B14               | PGED1/AN0/RPB0/RB0                                                       |          | B39               | RPD0/INT0/RD0  |               |                       |

| B15               | No Connect                                                               |          | B40               | SOSCO/RPC14/T  | 1CK/RC14      |                       |

| B16               | PGED2/AN7/RPB7/CTED3/RB7                                                 |          | B41               | Vss            |               |                       |

| B17               | VREF+/CVREF+/PMA6/RA10                                                   |          | B42               | AN25/RPD2/RD2  |               |                       |

| B18               | AVss                                                                     |          | B43               | RPD12/PMD12/R  | D12           |                       |

| B19               | AN9/RPB9/CTED4/RB9                                                       |          | B44               | RPD4/PMWR/RD   | 4             |                       |

| B20               | AN11/PMA12/RB11                                                          |          | B45               | PMD14/RD6      |               |                       |

| B21               | Vdd                                                                      |          | B46               | No Connect     |               |                       |

| B22               | RPF13/RF13                                                               |          | B47               | No Connect     |               |                       |

| B23               | AN12/PMA11/RB12                                                          |          | B48               | VCAP           |               |                       |

| B24               | AN14/RPB14/CTED5/PMA1/RB14                                               |          | B49               | RPF0/PMD11/RF  | 0             |                       |

| B25               | Vss                                                                      |          | B50               | RPG1/PMD9/RG   | 1             |                       |

| B26               | RPD14/RD14                                                               |          | B51               | TRCLK/RA6      |               |                       |

| B27               | RPF4/PMA9/RF4                                                            |          | B52               | PMD0/RE0       |               |                       |

| B28               | No Connect                                                               |          | B53               | VDD            |               |                       |

| B29               | RPF8/RF8                                                                 |          | B54               | TRD2/RG14      |               |                       |

| B30               | VUSB3V3                                                                  |          | B55               | TRD0/RG13      |               |                       |

| B31               | D+                                                                       |          | B56               | RPE3/CTPLS/PM  | D3/RE3        |                       |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: Shaded package bumps are 5V tolerant.

4: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

# PIC32MX330/350/370/430/450/470

| Pin Numb                              | er                                      |                                               |                |                                                     |  |  |  |

|---------------------------------------|-----------------------------------------|-----------------------------------------------|----------------|-----------------------------------------------------|--|--|--|

| 100-pin<br>TQFP                       | 124-pin<br>VTLA                         | Pin<br>Type                                   | Buffer<br>Type | Description                                         |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             |                                                     |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             |                                                     |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             | Capture Input 1-5                                   |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             |                                                     |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             |                                                     |  |  |  |

| PPS                                   | PPS                                     | 0                                             | ST             | Output Compare Output 1                             |  |  |  |

| PPS                                   | PPS                                     | 0                                             | ST             | Output Compare Output 2                             |  |  |  |

| PPS                                   | PPS                                     | 0                                             | ST             | Output Compare Output 3                             |  |  |  |

| PPS                                   | PPS                                     | 0                                             | ST             | Output Compare Output 4                             |  |  |  |

| PPS                                   | PPS                                     | 0                                             | ST             | Output Compare Output 5                             |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             | Output Compare Fault A Input                        |  |  |  |

| 44                                    | A29                                     | Ι                                             | ST             | Output Compare Fault B Input                        |  |  |  |

| 55 <sup>(1)</sup> , 72 <sup>(2)</sup> | B30 <sup>(1)</sup> , B39 <sup>(2)</sup> | Ι                                             | ST             | External Interrupt 0                                |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             | External Interrupt 1                                |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             | External Interrupt 2                                |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             | External Interrupt 3                                |  |  |  |

| PPS                                   | PPS                                     | Ι                                             | ST             | External Interrupt 4                                |  |  |  |

| 17                                    | B9                                      | I/O                                           | ST             |                                                     |  |  |  |

| 38                                    | A26                                     | I/O                                           | ST             |                                                     |  |  |  |

| 58                                    | A39                                     | I/O                                           | ST             |                                                     |  |  |  |

| 59                                    | B32                                     | I/O                                           | ST             |                                                     |  |  |  |

| 60                                    | A40                                     | I/O                                           | ST             |                                                     |  |  |  |

| 61                                    | B33                                     | I/O                                           | ST             | PORTA is a bidirectional I/O port                   |  |  |  |

| 91                                    | B51                                     | I/O                                           | ST             |                                                     |  |  |  |

| 92                                    | A62                                     | I/O                                           | ST             | ]                                                   |  |  |  |

| 28                                    | A21                                     | I/O                                           | ST             | ]                                                   |  |  |  |

| 29                                    | B17                                     | I/O                                           | ST             | ]                                                   |  |  |  |

| 66                                    | B36                                     | I/O                                           | ST             | ]                                                   |  |  |  |

| 67                                    | A44                                     | I/O                                           | ST             | ]                                                   |  |  |  |

|                                       | 66<br>67<br>OS compat                   | 66 B36<br>67 A44<br>OS compatible input or ou | 66 B36 I/O     | 66B36I/OST67A44I/OSTOS compatible input or outputAn |  |  |  |

#### TABLE 1-1. PINOUT I/O DESCRIPTIONS (CONTINUED)

ST = Schmitt Trigger input with CMOS levels TTL = TTL input buffer

O = Output

I = Input

Note 1: This pin is only available on devices without a USB module.

2: This pin is only available on devices with a USB module.

3: This pin is not available on 64-pin devices.

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 31:24        | _                 | _                 | _                 | —                 | _                 | —                 | —                | —                |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |

| 23:16        | _                 | _                 | _                 | —                 | _                 | —                 | —                | —                |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |

| 15:8         |                   | BMXDUDBA<15:8>    |                   |                   |                   |                   |                  |                  |  |  |  |

| 7:0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |

|              |                   |                   |                   | BMXDU             | DBA<7:0>          |                   |                  |                  |  |  |  |

#### REGISTER 4-3: BMXDUDBA: DATA RAM USER DATA BASE ADDRESS REGISTER

## Legend:

| Legena:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-16 Unimplemented: Read as '0'

#### bit 15-10 BMXDUDBA<15:10>: DRM User Data Base Address bits

When non-zero, the value selects the relative base address for User mode data space in RAM, the value must be greater than BMXDKPBA.

bit 9-0 BMXDUDBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

## 5.0 FLASH PROGRAM MEMORY

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/ 470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 5. "Flash Memory" (DS60001121), Program which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

PIC32MX330/350/370/430/450/470 devices contain an internal Flash program memory for executing user code. There are three methods by which the user can program this memory:

- Run-Time Self-Programming (RTSP)

- EJTAG Programming

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

RTSP is performed by software executing from either Flash or RAM memory. Information about RTSP techniques is available in **Section 5. "Flash Program Memory"** (DS60001121) in the *"PIC32 Family Reference Manual"*.

EJTAG is performed using the EJTAG port of the device and an EJTAG capable programmer.

ICSP is performed using a serial data connection to the device and allows much faster programming times than RTSP.

The EJTAG and ICSP methods are described in the *"PIC32 Flash Programming Specification"* (DS60001145), which can be downloaded from the Microchip web site.

Note: On PIC32MX330/350/370/430/450/470 devices, the Flash page size is 4 KB and the row size is 512 bytes (1024 IW and 128 IW, respectively).

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 24.24        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |

| 31:24        |                   | _                 |                   | —                 | _                 | —                 |                  | _                |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |  |  |

| 23:16        | _                 | _                 | —                 | —                 | _                 |                   | _                | SS0              |  |  |

| 45.0         | U-0               | U-0               | U-0               | R/W-0             | U-0               | R/W-0             | R/W-0            | R/W-0            |  |  |

| 15:8         | —                 | —                 | —                 | MVEC              | —                 |                   | TPC<2:0>         |                  |  |  |

| 7:0          | U-0               | U-0               | U-0               | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |

| 7:0          |                   |                   |                   | INT4EP            | INT3EP            | INT2EP            | INT1EP           | INT0EP           |  |  |

## REGISTER 7-1: INTCON: INTERRUPT CONTROL REGISTER

#### Legend:

| Logona.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

#### bit 31-17 Unimplemented: Read as '0'

- bit 16 SS0: Single Vector Shadow Register Set bit

- 1 = Single vector is presented with a shadow register set

- 0 = Single vector is not presented with a shadow register set

#### bit 15-13 Unimplemented: Read as '0'

- bit 12 MVEC: Multi Vector Configuration bit

- 1 = Interrupt controller configured for multi vectored mode

- 0 = Interrupt controller configured for single vectored mode

#### bit 11 Unimplemented: Read as '0'

- bit 10-8 TPC<2:0>: Interrupt Proximity Timer Control bits

- 111 = Interrupts of group priority 7 or lower start the Interrupt Proximity timer

- 110 = Interrupts of group priority 6 or lower start the Interrupt Proximity timer

- 101 = Interrupts of group priority 5 or lower start the Interrupt Proximity timer

- 100 = Interrupts of group priority 4 or lower start the Interrupt Proximity timer

- 011 = Interrupts of group priority 3 or lower start the Interrupt Proximity timer

- 010 = Interrupts of group priority 2 or lower start the Interrupt Proximity timer

- 001 = Interrupts of group priority 1 start the Interrupt Proximity timer 000 = Disables Interrupt Proximity timer

- bit 7-5 **Unimplemented:** Read as '0'

- bit 4 **INT4EP:** External Interrupt 4 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 3 INT3EP: External Interrupt 3 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 2 INT2EP: External Interrupt 2 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 1 INT1EP: External Interrupt 1 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

- bit 0 INTOEP: External Interrupt 0 Edge Polarity Control bit

- 1 = Rising edge

- 0 = Falling edge

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04-04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 31:24        | IFS31             | IFS30             | IFS29             | IFS28             | IFS27             | IFS26             | IFS25            | IFS24            |  |  |  |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 23:16        | IFS23             | IFS22             | IFS21             | IFS20             | IFS19             | IFS18             | IFS17            | IFS16            |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 15:8         | IFS15             | IFS14             | IFS13             | IFS12             | IFS11             | IFS10             | IFS9             | IFS8             |  |  |  |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |  |  |  |

| 7:0          | IFS7              | IFS6              | IFS5              | IFS4              | IFS3              | IFS2              | IFS1             | IFS0             |  |  |  |

### REGISTER 7-4: IFSx: INTERRUPT FLAG STATUS REGISTER

## Legend:

| 0                 |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IFS31-IFS0: Interrupt Flag Status bits

- 1 = Interrupt request has occurred

- 0 = No interrupt request has occurred

**Note:** This register represents a generic definition of the IFSx register. Refer to Table 7-1 for the exact bit definitions.

## REGISTER 7-5: IECx: INTERRUPT ENABLE CONTROL REGISTER

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 31:24        | IEC31             | IEC30             | IEC29             | IEC28             | IEC27             | IEC26             | IEC25            | IEC24            |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        | IEC23             | IEC22             | IEC21             | IEC20             | IEC19             | IEC18             | IEC17            | IEC16            |

| 15:8         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 10.0         | IEC15             | IEC14             | IEC13             | IEC12             | IEC11             | IEC10             | IEC9             | IEC8             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 7:0          | IEC7              | IEC6              | IEC5              | IEC4              | IEC3              | IEC2              | IEC1             | IEC0             |

| Legend:           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-0 IEC31-IEC0: Interrupt Enable bits

1 = Interrupt is enabled

0 = Interrupt is disabled

**Note:** This register represents a generic definition of the IECx register. Refer to Table 7-1 for the exact bit definitions.

'1' = Bit is set

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 04-04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 31:24        |                   |                   |                   | CHEPFAB           | Г<31:24>          |                   |                  |                  |  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 23:16        | CHEPFABT<23:16>   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 15:8         | CHEPFABT<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 7.0          | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x            | R/W-x            |  |  |  |

| 7:0          |                   | •                 | •                 | CHEPFA            | 3T<7:0>           |                   |                  |                  |  |  |  |

|              |                   |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| Legend       | 1                 |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| R = Rea      | dable bit         |                   | W = Writable      | e bit             | U = Unimple       | emented bit, re   | ad as '0'        |                  |  |  |  |

## REGISTER 9-12: CHEPFABT: PREFETCH CACHE ABORT STATISTICS REGISTER

## bit 31-0 CHEPFABT<31:0>: Prefab Abort Count bits

-n = Value at POR

Incremented each time an automatic prefetch cache is aborted due to a non-sequential instruction fetch, load or store.

'0' = Bit is cleared

x = Bit is unknown

## REGISTER 11-11: U1CON: USB CONTROL REGISTER (CONTINUED)

- bit 1 **PPBRST:** Ping-Pong Buffers Reset bit

- 1 = Reset all Even/Odd buffer pointers to the EVEN BD banks

- 0 = Even/Odd buffer pointers not being Reset

- bit 0 USBEN: USB Module Enable bit<sup>(4)</sup>

- 1 = USB module and supporting circuitry is enabled

- 0 = USB module and supporting circuitry is disabled

SOFEN: SOF Enable bit<sup>(5)</sup>

- 1 = SOF token sent every 1 ms

- 0 = SOF token is disabled

- **Note 1:** Software is required to check this bit before issuing another token command to the U1TOK register (see Register 11-15).

- 2: All host control logic is reset any time that the value of this bit is toggled.

- 3: Software must set the RESUME bit for 10 ms if the part is a function, or for 25 ms if the part is a host, and then clear it to enable remote wake-up. In Host mode, the USB module will append a low-speed EOP to the RESUME signaling when this bit is cleared.

- 4: Device mode.

- 5: Host mode.

## 12.0 I/O PORTS

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 12. "I/O Ports" (DS60001120), which is available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

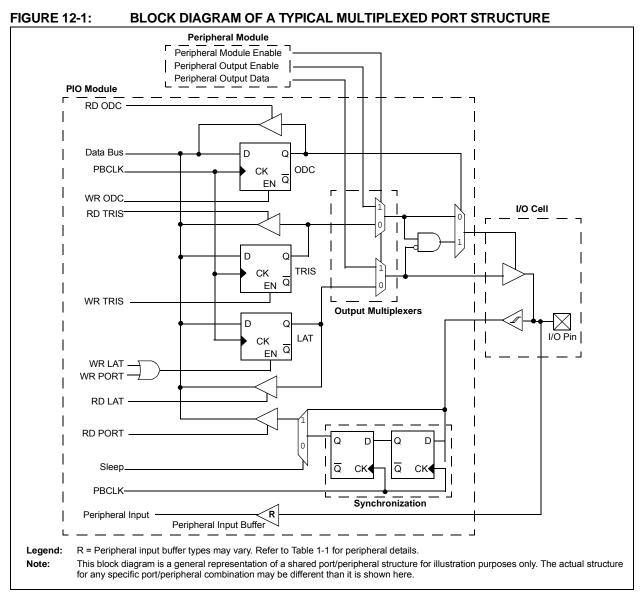

General purpose I/O pins are the simplest of peripherals. They allow the PIC<sup>®</sup> MCU to monitor and control other devices. To add flexibility and functionality, some pins are multiplexed with alternate function(s). These functions depend on which peripheral features are on the device. In general, when a peripheral is functioning, that pin may not be used as a general purpose I/O pin. Following are key features of this module:

- · Individual output pin open-drain enable/disable

- · Individual input pin weak pull-up and pull-down

- Monitor selective inputs and generate interrupt when change in pin state is detected

- Operation during CPU Sleep and Idle modes

- Fast bit manipulation using CLR, SET, and INV registers

Figure 12-1 illustrates a block diagram of a typical multiplexed I/O port.

## 12.3 Peripheral Pin Select

A major challenge in general purpose devices is providing the largest possible set of peripheral features while minimizing the conflict of features on I/O pins. The challenge is even greater on low pin count devices. In an application where more than one peripheral needs to be assigned to a single pin, inconvenient workarounds in application code or a complete redesign may be the only options.

Peripheral pin select configuration provides an alternative to these choices by enabling peripheral set selection and their placement on a wide range of I/O pins. By increasing the pinout options available on a particular device, users can better tailor the device to their entire application, rather than trimming the application to fit the device.

The peripheral pin select configuration feature operates over a fixed subset of digital I/O pins. Users may independently map the input and/or output of most digital peripherals to these I/O pins. Peripheral pin select is performed in software and generally does not require the device to be reprogrammed. Hardware safeguards are included that prevent accidental or spurious changes to the peripheral mapping once it has been established.

## 12.3.1 AVAILABLE PINS

The number of available pins is dependent on the particular device and its pin count. Pins that support the peripheral pin select feature include the designation "RPn" in their full pin designation, where "RP" designates a remappable peripheral and "n" is the remappable port number.

## 12.3.2 AVAILABLE PERIPHERALS

The peripherals managed by the peripheral pin select are all digital-only peripherals. These include general serial communications (UART and SPI), general purpose timer clock inputs, timer-related peripherals (input capture and output compare) and interrupt-on-change inputs.

In comparison, some digital-only peripheral modules are never included in the peripheral pin select feature. This is because the peripheral's function requires special I/O circuitry on a specific port and cannot be easily connected to multiple pins. These modules include I<sup>2</sup>C among others. A similar requirement excludes all modules with analog inputs, such as the Analog-to-Digital Converter (ADC).

A key difference between remappable and non-remappable peripherals is that remappable peripherals are not associated with a default I/O pin. The peripheral must always be assigned to a specific I/O pin before it can be used. In contrast, non-remappable peripherals are always available on a default pin, assuming that the peripheral is active and not conflicting with another peripheral. When a remappable peripheral is active on a given I/O pin, it takes priority over all other digital I/O and digital communication peripherals associated with the pin. Priority is given regardless of the type of peripheral that is mapped. Remappable peripherals never take priority over any analog functions associated with the pin.

### 12.3.3 CONTROLLING PERIPHERAL PIN SELECT

Peripheral pin select features are controlled through two sets of SFRs: one to map peripheral inputs, and one to map outputs. Because they are separately controlled, a particular peripheral's input and output (if the peripheral has both) can be placed on any selectable function pin without constraint.

The association of a peripheral to a peripheral-selectable pin is handled in two different ways, depending on whether an input or output is being mapped.

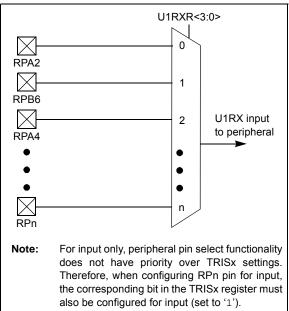

## 12.3.4 INPUT MAPPING

The inputs of the peripheral pin select options are mapped on the basis of the peripheral. That is, a control register associated with a peripheral dictates the pin it will be mapped to. The [*pin name*]R registers, where [*pin name*] refers to the peripheral pins listed in Table 12-1, are used to configure peripheral input mapping (see Register 12-1). Each register contains sets of 4 bit fields. Programming these bit fields with an appropriate value maps the RPn pin with the corresponding value to that peripheral. For any given device, the valid range of values for any bit field is shown in Table 12-1.

For example, Figure 12-2 illustrates the remappable pin selection for the U1RX input.

## FIGURE 12-2:

REMAPPABLE INPUT EXAMPLE FOR U1RX

## TABLE 12-12: PORTF REGISTER MAP FOR PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY

|                             | ONLY                            |           |       |       |               |               |       |       |      |              |      |      |              |              |              |              |              |              |               |

|-----------------------------|---------------------------------|-----------|-------|-------|---------------|---------------|-------|-------|------|--------------|------|------|--------------|--------------|--------------|--------------|--------------|--------------|---------------|

| ess                         |                                 | Ô         |       | Bits  |               |               |       |       |      |              |      |      |              |              |              |              |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup> | Bit Range | 31/15 | 30/14 | 29/13         | 28/12         | 27/11 | 26/10 | 25/9 | 24/8         | 23/7 | 22/6 | 21/5         | 20/4         | 19/3         | 18/2         | 17/1         | 16/0         | All<br>Resets |

| 6510                        | TRISF                           | 31:16     | _     |       | —             | —             | —     | —     | _    | —            | _    | -    | —            | —            | —            | -            | -            | _            | 0000          |

| 0010                        | -                               | 15:0      | —     | —     | TRISF13       | TRISF12       | —     | —     | _    | TRISF8       | —    | —    | TRISF5       | TRISF4       | TRISF3       | TRISF2       | TRISF1       | TRISF0       | xxxx          |

| 6520                        | PORTF                           | 31:16     | _     | _     | —             |               | _     | _     |      | —            | _    |      | -            | _            | _            | _            | —            | _            | 0000          |

|                             |                                 | 15:0      | —     | _     | RF13          | RF12          | —     | —     |      | RF8          | —    | _    | RF5          | RF4          | RF3          | RF2          | RF1          | RF0          | XXXX          |

| 6530                        | LATF                            | 31:16     | —     | _     | —             | _             | —     | —     |      | —            | —    | _    | —            | —            | —            | _            | —            |              | 0000          |

|                             | 2,                              | 15:0      | —     | _     | LATF13        | LATF12        | —     | —     |      | LATF8        | —    | _    | LATF5        | LATF4        | LATF3        | LATF2        | LATF1        | LATF0        | XXXX          |

| 6540                        | ODCF                            | 31:16     | —     | _     | —             | _             | —     | —     |      | —            | —    | _    | —            | —            | —            | _            | —            |              | 0000          |

|                             |                                 | 15:0      | —     | _     | ODCF13        | ODCF12        | —     | —     |      | ODCF8        | —    | _    | ODCF5        | ODCF4        | ODCF3        | ODCF2        | ODCF1        | ODCF0        | xxxx          |

| 6550                        | CNPUF                           | 31:16     | —     | _     | -             |               | —     | —     | _    | —            | _    |      | —            | —            | —            | —            | —            | —            | 0000          |

|                             |                                 | 15:0      | —     | _     | CNPUF13       | CNPUF12       | —     | —     | _    | CNPUF8       | _    |      | CNPUF5       | CNPUF4       | CNPDF3       | CNPUF2       | CNPUF1       | CNPUF0       | XXXX          |

| 6560                        | CNPDF                           | 31:16     | —     | _     | -             |               | —     | —     | _    | —            | _    |      | —            | —            | —            | —            | —            | —            | 0000          |

|                             | _                               | 15:0      | —     | _     | CNPDF13       | CNPDF12       | —     | —     | _    | CNPDF8       | _    |      | CNPDF5       | CNPFF4       | CNPDF3       | CNPDF2       | CNPDF1       | CNPDF0       | XXXX          |

| 6570                        | CNCONF                          | 31:16     | _     | _     | -             |               | —     | —     | _    | —            | _    |      |              | —            | —            | _            | _            | _            | 0000          |

|                             |                                 | 15:0      | ON    | _     | SIDL          | —             | _     | —     | _    | —            | _    | —    | _            | —            | —            | _            | _            | _            | 0000          |

| 6580                        | CNENF                           | 31:16     | —     | _     | -             |               | —     | —     | _    | —            | _    |      | —            | —            | —            | —            | —            | —            | 0000          |

|                             | _                               | 15:0      | —     | _     | CNIEF13       | CNIEF12       | —     | —     | _    | CNIEF8       | _    |      | CNIEF5       | CNIEF4       | CNIEF3       | CNIEF2       | CNIEF1       | CNIEF0       | XXXX          |

| 0500                        |                                 | 31:16     | —     |       | —             | —             | —     | —     | —    | —            | —    |      | —            |              | —            |              | _            |              | 0000          |

| 6590                        | CNSTATF                         | 15:0      | —     | —     | CN<br>STATF13 | CN<br>STATF12 | —     | —     | —    | CN<br>STATF8 | _    | —    | CN<br>STATF5 | CN<br>STATF4 | CN<br>STATF3 | CN<br>STATF2 | CN<br>STATF1 | CN<br>STATF0 | xxxx          |

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. Legend:

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

## REGISTER 18-3: SPIxSTAT: SPI STATUS REGISTER (CONTINUED)

- bit 3 SPITBE: SPI Transmit Buffer Empty Status bit

- 1 = Transmit buffer, SPIxTXB is empty

- 0 = Transmit buffer, SPIxTXB is not empty

Automatically set in hardware when SPI transfers data from SPIxTXB to SPIxSR.

Automatically cleared in hardware when SPIxBUF is written to, loading SPIxTXB.

## bit 2 Unimplemented: Read as '0'

bit 1 SPITBF: SPI Transmit Buffer Full Status bit

1 = Transmit not yet started, SPITXB is full

0 = Transmit buffer is not full

#### Standard Buffer Mode:

Automatically set in hardware when the core writes to the SPIBUF location, loading SPITXB. Automatically cleared in hardware when the SPI module transfers data from SPITXB to SPISR.

#### Enhanced Buffer Mode:

Set when CWPTR + 1 = SRPTR; cleared otherwise

#### bit 0 SPIRBF: SPI Receive Buffer Full Status bit

1 = Receive buffer, SPIxRXB is full

0 = Receive buffer, SPIxRXB is not full

#### Standard Buffer Mode:

Automatically set in hardware when the SPI module transfers data from SPIxSR to SPIxRXB. Automatically cleared in hardware when SPIxBUF is read from, reading SPIxRXB.

#### Enhanced Buffer Mode:

Set when SWPTR + 1 = CRPTR; cleared otherwise

## 19.0 INTER-INTEGRATED CIRCUIT (I<sup>2</sup>C)

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 24. "Inter-Integrated Circuit (I<sup>2</sup>C)" (DS60001116), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/ pic32). The  $I^2C$  module provides complete hardware support for both Slave and Multi-Master modes of the  $I^2C$  serial communication standard. Figure 19-1 illustrates the  $I^2C$  module block diagram.

Each  $I^2C$  module has a 2-pin interface: the SCLx pin is clock and the SDAx pin is data.

Each I<sup>2</sup>C module offers the following key features:

- I<sup>2</sup>C interface supporting both master and slave operation

- I<sup>2</sup>C Slave mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C Master mode supports 7-bit and 10-bit addressing

- I<sup>2</sup>C port allows bidirectional transfers between master and slaves

- Serial clock synchronization for the I<sup>2</sup>C port can be used as a handshake mechanism to suspend and resume serial transfer (SCLREL control)

- I<sup>2</sup>C supports multi-master operation; detects bus collision and arbitrates accordingly

- · Provides support for address bit masking

| REGISTE | R 19-1: I2CxCON: I <sup>2</sup> C CONTROL REGISTER (CONTINUED)                                                                                                                                                                                                                                                                                            |

|---------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 7   | <ul> <li>GCEN: General Call Enable bit (when operating as I<sup>2</sup>C slave)</li> <li>1 = Enable interrupt when a general call address is received in the I2CxRSR (module is enabled for reception)</li> <li>0 = General call address disabled</li> </ul>                                                                                              |

| bit 6   | <b>STREN:</b> SCLx Clock Stretch Enable bit (when operating as I <sup>2</sup> C slave)<br>Used in conjunction with SCLREL bit.<br>1 = Enable software or receive clock stretching<br>0 = Disable software or receive clock stretching                                                                                                                     |

| bit 5   | ACKDT: Acknowledge Data bit (when operating as I <sup>2</sup> C master, applicable during master receive)<br>Value that is transmitted when the software initiates an Acknowledge sequence.<br>1 = Send NACK during Acknowledge<br>0 = Send ACK during Acknowledge                                                                                        |

| bit 4   | <ul> <li>ACKEN: Acknowledge Sequence Enable bit</li> <li>(when operating as I<sup>2</sup>C master, applicable during master receive)</li> <li>1 = Initiate Acknowledge sequence on SDAx and SCLx pins and transmit ACKDT data bit.<br/>Hardware clear at end of master Acknowledge sequence.</li> <li>0 = Acknowledge sequence not in progress</li> </ul> |

| bit 3   | <ul> <li>RCEN: Receive Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Enables Receive mode for I<sup>2</sup>C. Hardware clear at end of eighth bit of master receive data byte.</li> <li>0 = Receive sequence not in progress</li> </ul>                                                                                               |

| bit 2   | <ul> <li>PEN: Stop Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Stop condition on SDAx and SCLx pins. Hardware clear at end of master Stop sequence.</li> <li>0 = Stop condition not in progress</li> </ul>                                                                                                       |

| bit 1   | <ul> <li>RSEN: Repeated Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Repeated Start condition on SDAx and SCLx pins. Hardware clear at end of master Repeated Start sequence.</li> <li>0 = Repeated Start condition not in progress</li> </ul>                                                              |

| bit 0   | <ul> <li>Start Condition Enable bit (when operating as I<sup>2</sup>C master)</li> <li>1 = Initiate Start condition on SDAx and SCLx pins. Hardware clear at end of master Start sequence.</li> <li>0 = Start condition not in progress</li> </ul>                                                                                                        |

**Note 1:** When using the 1:1 PBCLK divisor, the user software should not read/write the peripheral's SFRs in the SYSCLK cycle immediately following the instruction that clears the module's ON bit.

## 20.2 Timing Diagrams

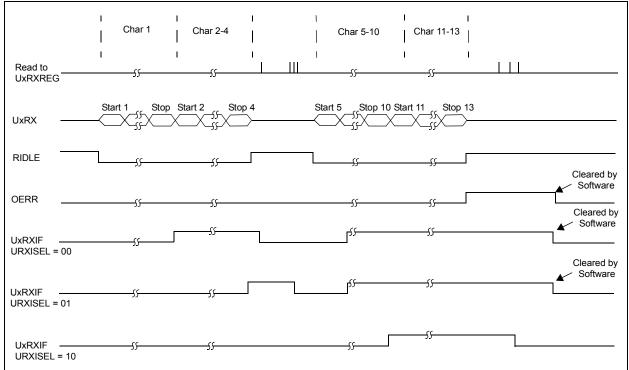

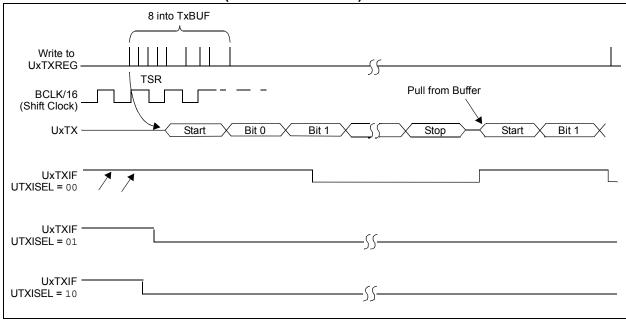

Figure 20-2 and Figure 20-3 illustrate typical receive and transmit timing for the UART module.

## FIGURE 20-2: UART RECEPTION

#### FIGURE 20-3: TRANSMISSION (8-BIT OR 9-BIT DATA)

## 24.1 Control Registers

## TABLE 24-1: COMPARATOR REGISTER MAP

| ess                         | Register<br>Name <sup>(1)</sup> | Ċ,        | Bits  |       |       |       |       |       |      |      |      |        |      |      |      | s    |       |       |            |

|-----------------------------|---------------------------------|-----------|-------|-------|-------|-------|-------|-------|------|------|------|--------|------|------|------|------|-------|-------|------------|

| Virtual Address<br>(BF80_#) |                                 | Bit Range | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6   | 21/5 | 20/4 | 19/3 | 18/2 | 17/1  | 16/0  | All Resets |

| A 000                       | CM1CON                          | 31:16     | —     | _     | _     | _     | _     | _     | _    | _    | —    |        | —    | —    | _    | —    | _     | _     | 0000       |

| A000                        |                                 | 15:0      | ON    | COE   | CPOL  | —     |       | _     |      | COUT | EVPO | L<1:0> | —    | CREF | -    |      | CCH   | <1:0> | E1C3       |

| A010                        | CM2CON                          | 31:16     | —     | —     | _     | _     | _     | —     | _    | _    | _    |        | —    | —    | _    | _    | —     |       | 0000       |

| AUTU                        | CIVIZCON                        | 15:0      | ON    | COE   | CPOL  | _     | _     | —     | _    | COUT | EVPO | L<1:0> | —    | CREF | _    | _    | CCH   | <1:0> | E1C3       |

| A060                        | CMSTAT                          | 31:16     | —     | -     | —     | —     | —     | —     | —    | —    | _    | _      | —    | _    | —    | _    | _     | —     | 0000       |

| A000                        | CIVISTAT                        | 15:0      | —     | _     | SIDL  | —     | -     | -     | -    | -    |      | _      | —    | —    | -    |      | C2OUT | C10UT | 0000       |

Legend: x = unknown value on Reset; — = unimplemented, read as '0'. Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at their virtual addresses, plus offsets of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

PIC32MX330/350/370/430/450/470

## TABLE 31-14: COMPARATOR SPECIFICATIONS

| DC CHA        |        | STICS                                 | $\begin{array}{ll} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |         |      |       |                                                                                        |  |  |  |

|---------------|--------|---------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|------|-------|----------------------------------------------------------------------------------------|--|--|--|

| Param.<br>No. | Symbol | Characteristics                       | Min.                                                                                                                                                                                                                                                                                                                                                | Typical | Max. | Units | Comments                                                                               |  |  |  |

| D300          | VIOFF  | Input Offset Voltage                  |                                                                                                                                                                                                                                                                                                                                                     | ±7.5    | ±25  | mV    | AVDD = VDD,<br>AVSS = VSS                                                              |  |  |  |

| D301          | VICM   | Input Common Mode Voltage             | 0                                                                                                                                                                                                                                                                                                                                                   | —       | Vdd  | V     | AVdd = Vdd,<br>AVss = Vss<br>(Note 2)                                                  |  |  |  |

| D302          | CMRR   | Common Mode Rejection Ratio           | 55                                                                                                                                                                                                                                                                                                                                                  | —       | _    | dB    | Max VICM = (VDD - 1)V<br>(Note 2)                                                      |  |  |  |

| D303          | Tresp  | Response Time                         | —                                                                                                                                                                                                                                                                                                                                                   | 150     | 400  | ns    | AVDD = VDD,<br>AVss = Vss<br>(Notes 1,2)                                               |  |  |  |

| D304          | ON2ov  | Comparator Enabled to Output<br>Valid |                                                                                                                                                                                                                                                                                                                                                     |         | 10   | μS    | Comparator module is<br>configured before setting<br>the comparator ON bit<br>(Note 2) |  |  |  |

| D305          | IVREF  | Internal Voltage Reference            | 1.14                                                                                                                                                                                                                                                                                                                                                | 1.2     | 1.26 | V     | —                                                                                      |  |  |  |

**Note 1:** Response time measured with one comparator input at (VDD – 1.5)/2, while the other input transitions from Vss to VDD.

**2:** These parameters are characterized but not tested.

**3:** Settling time measured while CVRR = 1 and CVR<3:0> transitions from '0000' to '1111'. This parameter is characterized, but not tested in manufacturing.

| AC CHA        | RACTER  | ISTICS                     |                               | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ & -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \end{array}$ |             |                     |                        |  |  |  |

|---------------|---------|----------------------------|-------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|---------------------|------------------------|--|--|--|

| Param.<br>No. | Symbol  | Charact                    | eristics                      | Min. <sup>(1)</sup>                                                                                                                                                                                                                                                                    | -4(<br>Max. | )°C ≤ TA ≤<br>Units | c +105°C for V-temp    |  |  |  |

| IM10          | TLO:SCL | Clock Low Time             | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        |             | μS                  |                        |  |  |  |

|               | 1201002 |                            | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        |             | μs                  | _                      |  |  |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        |             | μs                  | -                      |  |  |  |

| IM11          | THI:SCL | Clock High Time            | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        | _           | μS                  | _                      |  |  |  |

|               |         | _                          | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        | _           | μS                  | <u> </u>               |  |  |  |

|               |         |                            | 1 MHz mode<br>(Note 2)        | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        |             | μs                  | _                      |  |  |  |

| IM20          | TF:SCL  | SDAx and SCLx              | 100 kHz mode                  |                                                                                                                                                                                                                                                                                        | 300         | ns                  | CB is specified to be  |  |  |  |

|               |         | Fall Time                  | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                            | 300         | ns                  | from 10 to 400 pF      |  |  |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | _                                                                                                                                                                                                                                                                                      | 100         | ns                  |                        |  |  |  |

| IM21          | TR:SCL  | SDAx and SCLx<br>Rise Time | 100 kHz mode                  | —                                                                                                                                                                                                                                                                                      | 1000        | ns                  | CB is specified to be  |  |  |  |

|               |         |                            | 400 kHz mode                  | 20 + 0.1 Св                                                                                                                                                                                                                                                                            | 300         | ns                  | from 10 to 400 pF      |  |  |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | —                                                                                                                                                                                                                                                                                      | 300         | ns                  |                        |  |  |  |

| IM25          | TSU:DAT | Data Input                 | 100 kHz mode                  | 250                                                                                                                                                                                                                                                                                    | _           | ns                  | —                      |  |  |  |

|               |         | Setup Time                 | 400 kHz mode                  | 100                                                                                                                                                                                                                                                                                    | —           | ns                  | -                      |  |  |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | 100                                                                                                                                                                                                                                                                                    | —           | ns                  |                        |  |  |  |

| IM26          | THD:DAT | Data Input<br>Hold Time    | 100 kHz mode                  | 0                                                                                                                                                                                                                                                                                      | —           | μS                  | —                      |  |  |  |

|               |         |                            | 400 kHz mode                  | 0                                                                                                                                                                                                                                                                                      | 0.9         | μS                  |                        |  |  |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | 0                                                                                                                                                                                                                                                                                      | 0.3         | μs                  |                        |  |  |  |

| IM30          | TSU:STA | Start Condition            | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        | —           | μS                  | Only relevant for      |  |  |  |

|               |         | Setup Time                 | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        | —           | μs                  | Repeated Start         |  |  |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        |             | μs                  | condition              |  |  |  |

| IM31          | THD:STA | Start Condition            | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        | —           | μS                  | After this period, the |  |  |  |

|               |         | Hold Time                  | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        |             | μS                  | first clock pulse is   |  |  |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        | —           | μs                  | generated              |  |  |  |

| IM33          | Tsu:sto | Stop Condition             | 100 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        | —           | μS                  | —                      |  |  |  |

|               |         | Setup Time                 | 400 kHz mode                  | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        |             | μS                  | 1                      |  |  |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                                                                                                                                                                                                                                                        | _           | μs                  |                        |  |  |  |

## TABLE 31-33: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

**Note 1:** BRG is the value of the  $l^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

## 64-Lead Plastic Quad Flat, No Lead Package (MR) – 9x9x0.9 mm Body with 5.40 x 5.40 Exposed Pad [QFN]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                        | MILLIMETERS |      |          |      |  |  |  |  |

|------------------------|-------------|------|----------|------|--|--|--|--|

| Dimension              | Limits      | MIN  | NOM      | MAX  |  |  |  |  |

| Number of Pins         | N           |      | 64       |      |  |  |  |  |

| Pitch                  | е           |      | 0.50 BSC |      |  |  |  |  |

| Overall Height         | А           | 0.80 | 0.90     | 1.00 |  |  |  |  |

| Standoff               | A1          | 0.00 | 0.02     | 0.05 |  |  |  |  |

| Contact Thickness      | A3          |      | 0.20 REF |      |  |  |  |  |

| Overall Width          | Е           |      | 9.00 BSC |      |  |  |  |  |

| Exposed Pad Width      | E2          | 5.30 | 5.40     | 5.50 |  |  |  |  |

| Overall Length         | D           |      | 9.00 BSC |      |  |  |  |  |

| Exposed Pad Length     | D2          | 5.30 | 5.40     | 5.50 |  |  |  |  |

| Contact Width          | b           | 0.20 | 0.25     | 0.30 |  |  |  |  |

| Contact Length         | L           | 0.30 | 0.40     | 0.50 |  |  |  |  |

| Contact-to-Exposed Pad | К           | 0.20 | -        | -    |  |  |  |  |

Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. Package is saw singulated.

3. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

REF: Reference Dimension, usually without tolerance, for information purposes only.

Microchip Technology Drawing C04-154A Sheet 2 of 2