#### Welcome to E-XFL.COM

### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                        |

|----------------------------|---------------------------------------------------------------------------------|

| Core Processor             | MIPS32® M4K™                                                                    |

| Core Size                  | 32-Bit Single-Core                                                              |

| Speed                      | 80MHz                                                                           |

| Connectivity               | I <sup>2</sup> C, IrDA, LINbus, PMP, SPI, UART/USART, USB OTG                   |

| Peripherals                | Brown-out Detect/Reset, DMA, POR, PWM, WDT                                      |

| Number of I/O              | 85                                                                              |

| Program Memory Size        | 512KB (512K x 8)                                                                |

| Program Memory Type        | FLASH                                                                           |

| EEPROM Size                | -                                                                               |

| RAM Size                   | 128K x 8                                                                        |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 3.6V                                                                     |

| Data Converters            | A/D 28x10b                                                                      |

| Oscillator Type            | Internal                                                                        |

| Operating Temperature      | -40°C ~ 105°C (TA)                                                              |

| Mounting Type              | Surface Mount                                                                   |

| Package / Case             | 124-VFTLA Dual Rows, Exposed Pad                                                |

| Supplier Device Package    | 124-VTLA (9x9)                                                                  |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic32mx470f512lt-v-tl |

|                            |                                                                                 |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE 7: PIN NAMES FOR 124-PIN DEVICES (CONTINUED)

| 124               | -PIN VTLA (BOTTOM VIEW) <sup>(1,2,3,4)</sup>                             | 17       |                   |                | A34           |                       |

|-------------------|--------------------------------------------------------------------------|----------|-------------------|----------------|---------------|-----------------------|

|                   | A                                                                        | 17       |                   | B13 B29        |               | nductive<br>ermal Pad |

|                   | PIC32MX430F064L<br>PIC32MX450F128L<br>PIC32MX450F256L<br>PIC32MX470F512L |          |                   | B1<br>B56      | B41           | A51                   |

|                   |                                                                          | y Indica | A1<br>tor         | A68            |               |                       |

| Package<br>Bump # | Full Pin Name                                                            |          | Package<br>Bump # |                | Full Pin Name |                       |

| B7                | MCLR                                                                     |          | B32               | SDA2/RA3       |               |                       |

| B8                | Vss                                                                      |          | B33               | TDO/RA5        |               |                       |

| B9                | TMS/CTED1/RA0                                                            |          | B34               | OSC1/CLKI/RC12 | 2             |                       |

| B10               | RPE9/RE9                                                                 |          | B35               | No Connect     |               |                       |

| B11               | AN4/C1INB/RB4                                                            |          | B36               | SCL1/RPA14/RA  | 14            |                       |

| B12               | Vss                                                                      |          | B37               | RPD8/RTCC/RD8  | 8             |                       |

| B13               | PGEC3/AN2/C2INB/RPB2/CTED13/RB2                                          |          | B38               | RPD10/SCK1/PM  | CS2/RD10      |                       |

| B14               | PGED1/AN0/RPB0/RB0                                                       |          | B39               | RPD0/INT0/RD0  |               |                       |

| B15               | No Connect                                                               |          | B40               | SOSCO/RPC14/T  | 1CK/RC14      |                       |

| B16               | PGED2/AN7/RPB7/CTED3/RB7                                                 |          | B41               | Vss            |               |                       |

| B17               | VREF+/CVREF+/PMA6/RA10                                                   |          | B42               | AN25/RPD2/RD2  |               |                       |

| B18               | AVss                                                                     |          | B43               | RPD12/PMD12/R  | D12           |                       |

| B19               | AN9/RPB9/CTED4/RB9                                                       |          | B44               | RPD4/PMWR/RD   | 4             |                       |

| B20               | AN11/PMA12/RB11                                                          |          | B45               | PMD14/RD6      |               |                       |

| B21               | Vdd                                                                      |          | B46               | No Connect     |               |                       |

| B22               | RPF13/RF13                                                               |          | B47               | No Connect     |               |                       |

| B23               | AN12/PMA11/RB12                                                          |          | B48               | VCAP           |               |                       |

| B24               | AN14/RPB14/CTED5/PMA1/RB14                                               |          | B49               | RPF0/PMD11/RF  | 0             |                       |

| B25               | Vss                                                                      |          | B50               | RPG1/PMD9/RG   | 1             |                       |

| B26               | RPD14/RD14                                                               |          | B51               | TRCLK/RA6      |               |                       |

| B27               | RPF4/PMA9/RF4                                                            |          | B52               | PMD0/RE0       |               |                       |

| B28               | No Connect                                                               |          | B53               | VDD            |               |                       |

| B29               | RPF8/RF8                                                                 |          | B54               | TRD2/RG14      |               |                       |

| B30               | VUSB3V3                                                                  |          | B55               | TRD0/RG13      |               |                       |

| B31               | D+                                                                       |          | B56               | RPE3/CTPLS/PM  | D3/RE3        |                       |

Note 1: The RPn pins can be used by remappable peripherals. See Table 1 for the available peripherals and Section 12.3 "Peripheral Pin Select" for restrictions.

2: Every I/O port pin (RAx-RGx) can be used as a change notification pin (CNAx-CNGx). See Section 12.0 "I/O Ports" for more information.

3: Shaded package bumps are 5V tolerant.

4: It is recommended that the user connect the printed circuit board (PCB) ground to the conductive thermal pad on the bottom of the package. And to not run non-Vss PCB traces under the conductive thermal pad on the same side of the PCB layout.

## 2.5 ICSP Pins

The PGECx and PGEDx pins are used for In-Circuit Serial Programming<sup>TM</sup> (ICSP<sup>TM</sup>) and debugging purposes. It is recommended to keep the trace length between the ICSP connector and the ICSP pins on the device as short as possible. If the ICSP connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the PGECx and PGEDx pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

Ensure that the "Communication Channel Select" (i.e., PGECx/PGEDx pins) programmed into the device matches the physical connections for the ICSP to MPLAB<sup>®</sup> ICD 3 or MPLAB REAL ICE<sup>™</sup>.

For more information on ICD 3 and REAL ICE connection requirements, refer to the following documents that are available on the Microchip web site.

- "Using MPLAB<sup>®</sup> ICD 3" (poster) DS50001765

- "MPLAB<sup>®</sup> ICD 3 Design Advisory" DS50001764

- "MPLAB<sup>®</sup> REAL ICE™ In-Circuit Debugger User's Guide" DS50001616

- *"Using MPLAB<sup>®</sup> REAL ICE™ Emulator"* (poster) DS50001749

# 2.6 JTAG

The TMS, TDO, TDI and TCK pins are used for testing and debugging according to the Joint Test Action Group (JTAG) standard. It is recommended to keep the trace length between the JTAG connector and the JTAG pins on the device as short as possible. If the JTAG connector is expected to experience an ESD event, a series resistor is recommended, with the value in the range of a few tens of Ohms, not to exceed 100 Ohms.

Pull-up resistors, series diodes and capacitors on the TMS, TDO, TDI and TCK pins are not recommended as they will interfere with the programmer/debugger communications to the device. If such discrete components are an application requirement, they should be removed from the circuit during programming and debugging. Alternatively, refer to the AC/DC characteristics and timing requirements information in the respective device Flash programming specification for information on capacitive loading limits and pin input voltage high (VIH) and input low (VIL) requirements.

## 2.7 Trace

The trace pins can be connected to a hardware trace-enabled programmer to provide a compressed real-time instruction trace. When used for trace, the TRD3, TRD2, TRD1, TRD0 and TRCLK pins should be dedicated for this use. The trace hardware requires a 22 Ohm series resistor between the trace pins and the trace connector.

# 2.8 External Oscillator Pins

Many MCUs have options for at least two oscillators: a high-frequency primary oscillator and a low-frequency secondary oscillator (refer to **Section 8.0 "Oscillator Configuration"** for details).

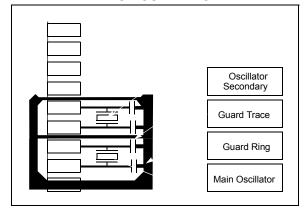

The oscillator circuit should be placed on the same side of the board as the device. Also, place the oscillator circuit close to the respective oscillator pins, not exceeding one-half inch (12 mm) distance between them. The load capacitors should be placed next to the oscillator itself, on the same side of the board. Use a grounded copper pour around the oscillator circuit to isolate them from surrounding circuits. The grounded copper pour should be routed directly to the MCU ground. Do not run any signal traces or power traces inside the ground pour. Also, if using a two-sided board, avoid any traces on the other side of the board where the crystal is placed. A suggested layout is illustrated in Figure 2-3.

### FIGURE 2-3: SUGGESTED OSCILLATOR CIRCUIT PLACEMENT

# 2.9 Unused I/Os

Unused I/O pins should not be allowed to float as inputs. They can be configured as outputs and driven to a logic-low state.

Alternatively, inputs can be reserved by connecting the pin to Vss through a 1k to 10k resistor and configuring the pin as an input.

# 2.10 EMI/EMC/EFT (IEC 61000-4-4 and IEC 61000-4-2) Suppression Considerations

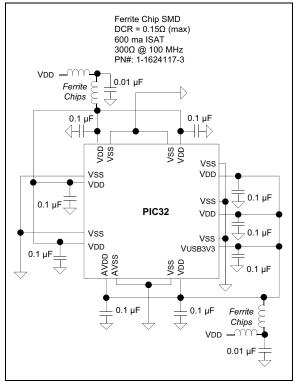

The use of LDO regulators is preferred to reduce overall system noise and provide a cleaner power source. However, when utilizing switching Buck/ Boost regulators as the local power source for PIC32 devices, as well as in electrically noisy environments or test conditions required for IEC 61000-4-4 and IEC 61000-4-2, users should evaluate the use of T-Filters (i.e., L-C-L) on the power pins, as shown in Figure 2-5. In addition to a more stable power source, use of this type of T-Filter can greatly reduce susceptibility to EMI sources and events.

FIGURE 2-5: EMI/EMC/EFT SUPPRESSION CIRCUIT

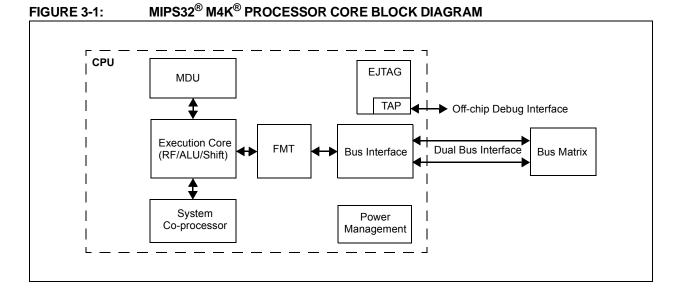

# 3.0 CPU

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 2.** "CPU" (DS60001113), which is available from the *Documentation > Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). Resources for the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core are available at http://www.imgtec.com.

The the MIPS32<sup>®</sup> M4K<sup>®</sup> Processor Core is the heart of the PIC32MX330/350/370/430/450/470 device processor. The CPU fetches instructions, decodes each instruction, fetches source operands, executes each instruction and writes the results of instruction execution to the proper destinations.

# 3.1 Features

- 5-stage pipeline

- · 32-bit address and data paths

- MIPS32<sup>®</sup> Enhanced Architecture (Release 2):

- Multiply-accumulate and multiply-subtract instructions

- Targeted multiply instruction

- Zero/One detect instructions

- WAIT instruction

- Conditional move instructions (MOVN, MOVZ)

- Vectored interrupts

- Programmable exception vector base

- Atomic interrupt enable/disable

- GPR shadow registers to minimize latency for interrupt handlers

- Bit field manipulation instructions

- MIPS16e<sup>®</sup> Code Compression:

- 16-bit encoding of 32-bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE and RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16-bit data types

- Simple Fixed Mapping Translation (FMT) Mechanism:

- Simple Dual Bus Interface:

- Independent 32-bit address and data buses

- Transactions can be aborted to improve interrupt latency

- Autonomous Multiply/Divide Unit (MDU):

- Maximum issue rate of one 32x16 multiply per clock

- Maximum issue rate of one 32x32 multiply every other clock

- Early-in iterative divide. Minimum 11 and maximum 33 clock latency (dividend (*rs*) sign extension-dependent)

- · Power Control:

- Minimum frequency: 0 MHz

- Low-Power mode (triggered by WAIT instruction)

- Extensive use of local gated clocks

- · EJTAG Debug and Instruction Trace:

- Support for single stepping

- Virtual instruction and data address/value

- Breakpoints

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 31:24        | _                 | _                 | _                 | _                 | _                 | —                 |                  | —                |  |  |  |  |  |  |

| 00.40        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | U-0              |  |  |  |  |  |  |

| 23:16        | _                 | _                 | —                 | _                 | _                 | —                 | —                | —                |  |  |  |  |  |  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-0              |  |  |  |  |  |  |

| 15:8         | BMXDKPBA<15:8>    |                   |                   |                   |                   |                   |                  |                  |  |  |  |  |  |  |

| 7.0          | R-0               | R-0               | R-0               | R-0               | R-0               | R-0               | R-0              | R-0              |  |  |  |  |  |  |

| 7:0          |                   |                   |                   | BMXDK             | PBA<7:0>          |                   |                  |                  |  |  |  |  |  |  |

## REGISTER 4-2: BMXDKPBA: DATA RAM KERNEL PROGRAM BASE ADDRESS REGISTER

### Legend:

| Legenu.           |                  |                           |                    |

|-------------------|------------------|---------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, re | ad as '0'          |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared      | x = Bit is unknown |

bit 31-16 Unimplemented: Read as '0'

bit 15-10 **BMXDKPBA<15:10>:** DRM Kernel Program Base Address bits When non-zero, this value selects the relative base address for kernel program space in RAM

bit 9-0 BMXDKPBA<9:0>: Read-Only bits Value is always '0', which forces 1 KB increments

**Note 1:** At Reset, the value in this register is forced to zero, which causes all of the RAM to be allocated to Kernel mode data usage.

2: The value in this register must be less than or equal to BMXDRMSZ.

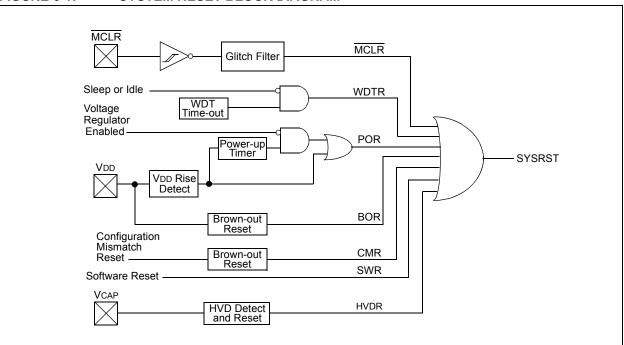

# 6.0 RESETS

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to **Section 7.** "**Resets**" (DS60001118), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32). The Reset module combines all Reset sources and controls the device Master Reset signal, SYSRST. The following is a list of device Reset sources:

- POR: Power-on Reset

- MCLR: Master Clear Reset pin

- · SWR: Software Reset

- WDTR: Watchdog Timer Reset

- · BOR: Brown-out Reset

- CMR: Configuration Mismatch Reset

- HVDR: High Voltage Detect Reset

A simplified block diagram of the Reset module is illustrated in Figure 6-1.

## FIGURE 6-1: SYSTEM RESET BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7         | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                                                               | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |  |  |

|--------------|---------------------------|-------------------|-------------------|-------------------|---------------------------------------------------------------------------------|-------------------|------------------|------------------|--|--|--|--|--|--|

|              | U-0                       | R/W-0             | R/W-0             | R/W-0             | R/W-0                                                                           | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 31:24        |                           |                   |                   | R                 | ) 2010/2017/2017/2017/2017/2017/2017/2017</td <td>1,3)</td> <td></td> <td></td> | 1,3)              |                  |                  |  |  |  |  |  |  |

| 00.40        | R/W-0                     | R/W-0 R/W-0       |                   | R/W-0             | R/W-0                                                                           | R/W-0             | R/W-0            | R/W-0            |  |  |  |  |  |  |

| 23:16        | RODIV<7:0> <sup>(3)</sup> |                   |                   |                   |                                                                                 |                   |                  |                  |  |  |  |  |  |  |

| 45.0         | R/W-0                     | U-0               | R/W-0             | R/W-0             | R/W-0                                                                           | U-0               | R/W-0, HC        | R-0, HS, HC      |  |  |  |  |  |  |

| 15:8         | ON                        | _                 | SIDL              | OE                | RSLP <sup>(2)</sup>                                                             | _                 | DIVSWEN          | ACTIVE           |  |  |  |  |  |  |

|              | U-0                       | U-0 U-0           |                   | U-0               | R/W-0                                                                           | R/W-0             | R/W-0 R/W-0      |                  |  |  |  |  |  |  |

| 7:0          |                           | _                 | _                 | _                 | ROSEL<3:0> <sup>(1)</sup>                                                       |                   |                  |                  |  |  |  |  |  |  |

## **REGISTER 8-3: REFOCON: REFERENCE OSCILLATOR CONTROL REGISTER**

| Legend:           | HC = Hardware Clearable | HS = Hardware Settable   |                    |  |  |  |  |

|-------------------|-------------------------|--------------------------|--------------------|--|--|--|--|

| R = Readable bit  | W = Writable bit        | U = Unimplemented bit, r | ead as '0'         |  |  |  |  |

| -n = Value at POR | '1' = Bit is set        | '0' = Bit is cleared     | x = Bit is unknown |  |  |  |  |

- bit 31 Unimplemented: Read as '0'

- bit 30-16 **RODIV<14:0>:** Reference Clock Divider bits<sup>(1,3)</sup> This value selects the Reference Clock Divider bits. See Figure 8-1 for more information. bit 15 **ON:** Output Enable bit 1 = Reference Oscillator Module is enabled 0 = Reference Oscillator Module is disabled

- bit 14 Unimplemented: Read as '0'

- bit 13 **SIDL:** Peripheral Stop in Idle Mode bit

- 1 = Discontinue module operation when device enters Idle mode

- 0 = Continue module operation in Idle mode

- bit 12 OE: Reference Clock Output Enable bit

- 1 = Reference clock is driven out on REFCLKO pin

- 0 = Reference clock is not driven out on REFCLKO pin

- bit 11 RSLP: Reference Oscillator Module Run in Sleep bit<sup>(2)</sup>

- 1 = Reference Oscillator Module output continues to run in Sleep

- 0 = Reference Oscillator Module output is disabled in Sleep

- bit 10 Unimplemented: Read as '0'

- bit 9 DIVSWEN: Divider Switch Enable bit

- 1 = Divider switch is in progress

- 0 = Divider switch is complete

- bit 8 ACTIVE: Reference Clock Request Status bit

- 1 = Reference clock request is active

- 0 = Reference clock request is not active

- bit 7-4 Unimplemented: Read as '0'

- **Note 1:** The ROSEL and RODIV bits should not be written while the ACTIVE bit is '1', as undefined behavior may result.

- **2:** This bit is ignored when the ROSEL<3:0> bits = 0000 or 0001.

- 3: While the ON bit is set to '1', writes to these bits do not take effect until the DIVSWEN bit is also set to '1'.

## REGISTER 10-9: DCHxINT: DMA CHANNEL 'x' INTERRUPT CONTROL REGISTER (CONTINUED)

bit 4 **CHDHIF:** Channel Destination Half Full Interrupt Flag bit

- 1 = Channel Destination Pointer has reached midpoint of destination (CHDPTR = CHDSIZ/2)

- 0 = No interrupt is pending

- bit 3 CHBCIF: Channel Block Transfer Complete Interrupt Flag bit

- 1 = A block transfer has been completed (the larger of CHSSIZ/CHDSIZ bytes has been transferred), or a pattern match event occurs

- 0 = No interrupt is pending

- bit 2 CHCCIF: Channel Cell Transfer Complete Interrupt Flag bit

- 1 = A cell transfer has been completed (CHCSIZ bytes have been transferred)

- 0 = No interrupt is pending

- bit 1 CHTAIF: Channel Transfer Abort Interrupt Flag bit

- 1 = An interrupt matching CHAIRQ has been detected and the DMA transfer has been aborted

- 0 = No interrupt is pending

- bit 0 CHERIF: Channel Address Error Interrupt Flag bit

- 1 = A channel address error has been detected

- Either the source or the destination address is invalid.

- 0 = No interrupt is pending

NOTES:

# PIC32MX330/350/370/430/450/470

### REGISTER 11-7: U1IE: USB INTERRUPT ENABLE REGISTER

|              |                   | •                 |                   |                   |                   |                   |                       |                         |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|-----------------------|-------------------------|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1      | Bit<br>24/16/8/0        |

| 31:24        | U-0                   | U-0                     |

| 31.24        | -                 | —                 | —                 | -                 | —                 | —                 | -                     | —                       |

| 23:16        | U-0                   | U-0                     |

| 23.10        | -                 | —                 | —                 | -                 | —                 | —                 | -                     | —                       |

| 15:8         | U-0                   | U-0                     |

| 15.0         | _                 | _                 | —                 | _                 | —                 | _                 | _                     | —                       |

|              | R/W-0                 | R/W-0                   |

| 7:0          | STALLIE           | ATTACHIE          | RESUMEIE          | IDLEIE            | TRNIE             | SOFIE             | UERRIE <sup>(1)</sup> | URSTIE <sup>(2)</sup>   |

|              | STALLIE           | ALIACHIE          | RESUMEIE          | IDLEIE            |                   | SOFIE             | UERRIE' /             | DETACHIE <sup>(3)</sup> |

#### Legend:

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, | read as '0'        |

|-------------------|------------------|------------------------|--------------------|

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared   | x = Bit is unknown |

### bit 31-8 Unimplemented: Read as '0'

| bit 7 | <b>STALLIE:</b> STALL Handshake Interrupt Enable bit<br>1 = STALL interrupt is enabled<br>0 = STALL interrupt is disabled         |

|-------|-----------------------------------------------------------------------------------------------------------------------------------|

| bit 6 | ATTACHIE: ATTACH Interrupt Enable bit<br>1 = ATTACH interrupt is enabled<br>0 = ATTACH interrupt is disabled                      |

| bit 5 | <b>RESUMEIE:</b> RESUME Interrupt Enable bit<br>1 = RESUME interrupt is enabled<br>0 = RESUME interrupt is disabled               |

| bit 4 | IDLEIE: Idle Detect Interrupt Enable bit<br>1 = Idle interrupt is enabled<br>0 = Idle interrupt is disabled                       |

| bit 3 | <b>TRNIE:</b> Token Processing Complete Interrupt Enable bit<br>1 = TRNIF interrupt is enabled<br>0 = TRNIF interrupt is disabled |

| bit 2 | <b>SOFIE:</b> SOF Token Interrupt Enable bit<br>1 = SOFIF interrupt is enabled<br>0 = SOFIF interrupt is disabled                 |

| bit 1 | UERRIE: USB Error Interrupt Enable bit <sup>(1)</sup><br>1 = USB Error interrupt is enabled                                       |

- 1 = USB Error interrupt is enabled 0 = USB Error interrupt is disabled

- bit 0 URSTIE: USB Reset Interrupt Enable bit<sup>(2)</sup>

- 1 = URSTIF interrupt is enabled

- 0 = URSTIF interrupt is disabled

- DETACHIE: USB Detach Interrupt Enable bit<sup>(3)</sup>

- 1 = DATTCHIF interrupt is enabled

- 0 = DATTCHIF interrupt is disabled

**Note 1:** For an interrupt to propagate USBIF, the UERRIE bit (U1IE<1>) must be set.

- 2: Device mode.

- 3: Host mode.

|                             | PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY |           |           |           |           |           |       |       |      |      |      |      |      |          |          |          |          |      |               |

|-----------------------------|-------------------------------------------------------------------------------------|-----------|-----------|-----------|-----------|-----------|-------|-------|------|------|------|------|------|----------|----------|----------|----------|------|---------------|

| ess                         |                                                                                     |           |           |           |           |           |       |       |      | Bits |      |      |      |          |          |          |          |      |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup>                                                     | Bit Range | 31/15     | 30/14     | 29/13     | 28/12     | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4     | 19/3     | 18/2     | 17/1     | 16/0 | All<br>Resets |

| 6210                        | 210 TRISC                                                                           | 31:16     | _         | —         | _         | —         | _     | —     | _    | _    | _    | —    | —    | —        | _        | _        | —        | —    | 0000          |

| 0210                        | 11100                                                                               | 15:0      | TRISC15   | TRISC14   | TRISC13   | TRISC12   | —     | —     | —    | —    | —    | —    | —    | TRISC4   | TRISC3   | TRISC2   | TRISC1   | —    | xxxx          |

| 6220                        | PORTC                                                                               | 31:16     |           | _         | _         |           | _     | —     |      |      | _    |      | —    | —        | _        | _        | —        | _    | 0000          |

| 0220                        | 1 OKTO                                                                              | 15:0      | RC15      | RC14      | RC13      | RC12      | _     | —     | _    | —    | —    | —    | —    | RC4      | RC3      | RC2      | RC1      | —    | xxxx          |

| 6230                        | LATC                                                                                | 31:16     | _         | _         | _         | _         | -     | —     | _    | _    | _    | _    | —    | —        | _        | _        | —        | —    | 0000          |

| 0230                        | LAIO                                                                                | 15:0      | LATC15    | LATC14    | LATC13    | LATC12    | _     | —     | _    | _    | _    | _    | _    | LATC4    | LATC3    | LATC2    | LATC1    | —    | xxxx          |

| 6240                        | ODCC                                                                                | 31:16     | _         | —         | _         | —         |       | _     |      |      |      | _    | _    | _        | -        | -        | _        | —    | 0000          |

| 0240                        | ODCC                                                                                | 15:0      | ODCC15    | ODCC14    | ODCC13    | ODCC12    |       | —     |      |      | _    | —    | —    | ODCC4    | ODCC3    | ODCC2    | ODCC1    | —    | xxxx          |

| 6250                        | CNPUC                                                                               | 31:16     |           | -         | -         | _         |       | —     |      |      | _    | —    | —    | -        | -        | -        | _        | —    | 0000          |

| 0250                        | CINFUC                                                                              | 15:0      | CNPUC15   | CNPUC14   | CNPUC13   | CNPUC12   | —     | —     | —    | —    | —    | -    | -    | CNPUC4   | CNPUC3   | CNPUC2   | CNPUC1   | —    | xxxx          |

| 6260                        | CNPDC                                                                               | 31:16     | -         | _         | _         | —         | —     | —     | —    | —    | —    | -    | -    | -        | —        | —        | _        | —    | 0000          |

| 0200                        | CINFDC                                                                              | 15:0      | CNPDC15   | CNPDC14   | CNPDC13   | CNPDC12   | —     | —     | —    | —    | —    | -    | -    | CNPDC4   | CNPDC3   | CNPDC2   | CNPDC1   | —    | xxxx          |

| 6270                        | CNCONC                                                                              | 31:16     | -         | _         | _         | —         | —     | —     | —    | —    | —    | -    | -    | -        | —        | —        | _        | —    | 0000          |

| 0270                        | CINCOINC                                                                            | 15:0      | ON        | _         | SIDL      | —         | —     | —     | —    | —    | —    | -    | -    | -        | —        | —        | _        | —    | 0000          |

| 6280                        | CNENC                                                                               | 31:16     | _         | _         |           | _         | _     | —     | —    | _    |      |      |      | _        | _        | _        | _        | —    | 0000          |

| 0200                        | GNEING                                                                              | 15:0      | CNIEC15   | CNIEC14   | CNIEC13   | CNIEC12   | _     | —     | —    | _    |      |      |      | CNIEC4   | CNIEC3   | CNIEC2   | CNIEC1   | —    | xxxx          |

| 6200                        | CNETATO                                                                             | 31:16     | _         |           |           | _         | _     | —     | —    | _    |      |      |      | _        | _        | _        | _        | —    | 0000          |

| 0290                        | 290 CNSTATC                                                                         | 15:0      | CNSTATC15 | CNSTATC14 | CNSTATC13 | CNSTATC12 |       | _     |      | -    | _    |      | _    | CNSTATC4 | CNSTATC3 | CNSTATC2 | CNSTATC1 | —    | xxxx          |

# TABLE 12-5: PORTC REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,

Legend:

x = Unknown value on Reset; — = Unimplemented, read as '0'; Reset values are shown in hexadecimal. All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for Note 1: more information.

|                             | PIC32MX430F064L, PIC32MX450F128L, PIC32MX450F256L, AND PIC32MX470F512L DEVICES ONLY |           |               |               |               |               |       |       |              |              |              |              |      |      |                    |                    |              |              |               |

|-----------------------------|-------------------------------------------------------------------------------------|-----------|---------------|---------------|---------------|---------------|-------|-------|--------------|--------------|--------------|--------------|------|------|--------------------|--------------------|--------------|--------------|---------------|

| ess                         |                                                                                     |           |               |               |               |               |       |       |              | Bit          | s            |              |      |      |                    |                    |              |              |               |

| Virtual Address<br>(BF88_#) | Register<br>Name <sup>(1)</sup>                                                     | Bit Range | 31/15         | 30/14         | 29/13         | 28/12         | 27/11 | 26/10 | 25/9         | 24/8         | 23/7         | 22/6         | 21/5 | 20/4 | 19/3               | 18/2               | 17/1         | 16/0         | All<br>Resets |

| 6600 ANSELG                 | 31:16                                                                               | —         | —             | —             | —             | _             | _     |       |              | _            |              |              | —    |      | _                  | —                  | —            | 0000         |               |

| 0000                        | ANOLLO                                                                              | 15:0      | —             | —             | —             | —             | —     | _     | ANSELG9      | ANSELG8      | ANSELG7      | ANSELG6      | —    | —    |                    | _                  | —            | —            | 01C0          |

| 6610                        | TRISG                                                                               | 31:16     | —             | —             | —             | —             | —     | —     | —            | —            | —            | —            | —    | —    |                    | —                  | —            | —            | 0000          |

| 00.0                        |                                                                                     | 15:0      | TRISG15       | TRISG14       | TRISG13       | TRISG12       | —     | —     | TRISG9       | TRISG8       | TRISG7       | TRISG6       | —    | —    | TRISG3             | TRISG2             | TRISG1       | TRISG0       | xxxx          |

| 6620                        | PORTG                                                                               | 31:16     | _             |               |               | —             | _     | _     | —            | _            | —            | —            | _    | —    | —                  | —                  | —            | —            | 0000          |

| 0020                        |                                                                                     | 15:0      | RG15          | RG14          | RG13          | RG12          | —     | —     | RG9          | RG8          | RG7          | RG6          | —    | —    | RG3 <sup>(2)</sup> | RG2 <sup>(2)</sup> | RG1          | RG0          | xxxx          |

| 6630                        | LATG                                                                                | 31:16     | _             |               |               | -             | _     | —     | —            | —            | —            | —            | —    | —    | -                  | —                  | —            | —            | 0000          |

|                             |                                                                                     | 15:0      | LATG15        | LATG14        | LATG13        | LATG12        | _     | —     | LATG9        | LATG8        | LATG7        | LATG6        | —    | —    | LATG3              | LATG2              | LATG1        | LATG0        | xxxx          |

| 6640                        | ODCG                                                                                | 31:16     | —             | _             | _             | —             | —     | _     | —            | —            | —            | —            | —    | —    |                    | —                  | —            | —            | 0000          |

|                             |                                                                                     | 15:0      | ODCG15        | ODCG14        | ODCG13        | ODCG12        | —     | _     | ODCG9        | ODCG8        | ODCG7        | ODCG6        | —    | —    | ODCG3              | ODCG2              | ODCG1        | ODCG0        | xxxx          |

| 6650                        | CNPUG                                                                               | 31:16     | —             | _             | _             | —             | —     | _     | —            | —            | —            | —            | —    | —    |                    | —                  | —            | —            | 0000          |

|                             |                                                                                     |           | CNPUG15       | CNPUG14       | CNPUG13       | CNPUG12       | —     | _     | CNPUG9       | CNPUG8       | CNPUG7       | CNPUG6       | _    | —    | CNPUG3             | CNPUG2             | CNPUG1       | CNPUG0       |               |

| 6660                        | CNPDG                                                                               | 31:16     | —             | —             | —             | —             | —     | _     | —            |              | —            | —            | _    | —    | —                  | —                  | —            | —            | 0000          |

|                             |                                                                                     |           | CNPDG15       | CNPDG14       | CNPDG13       | CNPDG12       | —     | _     | CNPDG9       | CNPDG8       | CNPDG7       | CNPDG6       | _    | —    | CNPDG3             | CNPDG2             | CNPDG1       | CNPDG0       |               |

| 6670                        | CNCONG                                                                              | 31:16     | -             | _             | -             | -             | _     | _     | _            | _            | _            | _            | _    | -    |                    | _                  | _            | -            | 0000          |

|                             |                                                                                     | 15:0      | ON            | _             | SIDL          | -             | _     | _     | _            | _            | _            | _            | _    | -    |                    | _                  | _            | -            | 0000          |

| 6680                        | CNENG                                                                               | 31:16     | -             | -             | -             | -             | _     | _     | -            | -            | -            | -            | _    | _    | -                  | —                  | -            | -            | 0000          |

|                             |                                                                                     | 15:0      | CNIEG15       | CNIEG14       | CNIEG13       | CNIEG12       | _     | _     | CNIEG9       | CNIEG8       | CNIEG7       | CNIEG6       | _    | _    | CNIEG3             | CNIEG2             | CNIEG1       | CNIEG0       | xxxx          |

| 0000                        |                                                                                     | 31:16     | -             | -             | -             | -             | _     | —     | —            | _            | —            | —            | _    | —    | —                  | —                  | —            | —            | 0000          |

| 6690                        | CNSTATG                                                                             | 15:0      | CN<br>STATG15 | CN<br>STATG14 | CN<br>STATG13 | CN<br>STATG12 | —     | _     | CN<br>STATG9 | CN<br>STATG8 | CN<br>STATG7 | CN<br>STATG6 | —    | —    | CN<br>STATG3       | CN<br>STATG2       | CN<br>STATG1 | CN<br>STATG0 | xxxx          |

# TABLE 12-15: PORTG REGISTER MAP FOR PIC32MX330F064L, PIC32MX350F128L, PIC32MX350F256L, PIC32MX370F512L,

Legend: x = Unknown value on Reset; - = Unimplemented, read as '0'; Reset values are shown in hexadecimal.

Note 1: All registers in this table have corresponding CLR, SET and INV registers at its virtual address, plus an offset of 0x4, 0x8 and 0xC, respectively. See Section 12.2 "CLR, SET, and INV Registers" for more information.

2: This bit only implemented on devices without a USB module.

# TABLE 12-18: PERIPHERAL PIN SELECT OUTPUT REGISTER MAP (CONTINUED)

| 2012-2016  |  |

|------------|--|

| Microchip  |  |

| Technology |  |

| Inc        |  |

0

| SS                          |                       |               |       |       |       |       |       |       |      | Bi   | its  |      |      |      |      |          |           |      |            |

|-----------------------------|-----------------------|---------------|-------|-------|-------|-------|-------|-------|------|------|------|------|------|------|------|----------|-----------|------|------------|

| Virtual Address<br>(BF80_#) | Register<br>Name      | Bit Range     | 31/15 | 30/14 | 29/13 | 28/12 | 27/11 | 26/10 | 25/9 | 24/8 | 23/7 | 22/6 | 21/5 | 20/4 | 19/3 | 18/2     | 17/1      | 16/0 | All Resets |

| FC14                        | RPE5R                 | 31:16         | _     | _     | _     | _     | _     | _     | —    |      | _    | _    | _    | —    |      | _        | _         | _    | 000        |

| 1014                        | RELIK                 | 15:0          | —     | _     | —     | —     | —     | —     | —    | —    | _    | —    | —    | —    |      | RPE5     | <3:0>     |      | 000        |

| FC20                        | RPE8R <sup>(1)</sup>  | 31:16         | _     | —     | —     | —     | —     | —     | —    | _    | _    | —    | —    | _    | —    | —        | —         | _    | 000        |

| 1 0 2 0                     |                       | 15:0          | _     | _     | _     | _     |       | _     | _    |      |      | _    | _    | _    |      | RPE8     | <3:0>     |      | 000        |

| FC24                        | RPE9R <sup>(1)</sup>  | 31:16         | _     | _     | —     | —     | —     | —     | _    | _    | _    | —    | —    | _    | _    | _        | _         | —    | 000        |

|                             |                       | 15:0          | _     | _     | —     | —     | —     | —     | —    | _    | _    | —    | —    | _    |      | RPE9     | <3:0>     |      | 000        |

| FC40                        | RPF0R                 | 31:16         | _     | _     | _     | _     | _     | _     | _    |      |      | _    | _    | _    | _    | -        | -         | -    | 000        |

|                             | -                     | 15:0          | _     |       | _     | _     |       | _     | _    |      |      | _    | _    |      |      | RPF0     | <3:0>     |      | 000        |

| FC44                        | RPF1R                 | 31:16         | _     | _     | _     | _     |       |       |      |      |      |      | _    |      | —    | -        | -         |      | 000        |

|                             |                       | 15:0          | _     | _     | _     |       | —     | _     | _    | _    | _    | _    | _    |      |      | RPF1     | <3:0>     |      | 000        |

| FC48                        | RPF2R <sup>(3)</sup>  | 31:16<br>15:0 | _     |       | —     | —     | —     | —     |      | _    |      | _    | —    |      | _    | <br>RPF2 |           | —    | 000        |

|                             |                       |               | _     |       |       |       | —     |       |      | _    |      | _    |      |      |      | RPFZ     | <3.0>     |      | 000        |

| FC4C                        | RPF3R <sup>(2)</sup>  | 31:16<br>15:0 | _     | _     | _     | _     | _     | _     |      | _    |      | _    | _    |      | —    | <br>RPF3 |           |      | 000        |

|                             |                       | 31:16         |       |       |       |       |       | _     |      |      |      |      |      |      |      | RPFJ     | <3.0>     |      | 000        |

| FC50                        | RPF4R                 | 15:0          | _     |       |       | _     | _     |       |      |      |      | _    | _    | _    | _    | <br>RPF4 |           |      | 000        |

|                             |                       | 31:16         |       |       |       |       |       |       |      |      |      |      |      |      | _    |          | < <u></u> | _    | 000        |

| FC54                        | RPF5R                 | 15:0          |       |       |       |       | _     |       |      |      |      |      | _    |      | _    | <br>RPF5 | <3:0>     |      | 000        |

|                             |                       | 31:16         | _     | _     | _     | _     | _     | _     | _    |      |      |      | _    | _    | _    |          |           | _    | 000        |

| FC58                        | RPF6R <sup>(2)</sup>  | 15:0          | _     | _     |       | _     | _     | _     |      | _    |      | _    | _    | _    |      | RPF6     |           |      | 000        |

|                             |                       | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    |      | _    | _    | _    | _    | _        |           | _    | 000        |

| FC60                        | RPF8R <sup>(1)</sup>  | 15:0          | _     | _     | _     | _     |       | _     | _    | _    | _    | _    |      | _    |      | RPF8     | <3:0>     |      | 000        |

|                             | (1)                   | 31:16         | _     | _     |       |       |       |       |      | _    | _    | _    |      |      | _    | _        | _         | _    | 000        |

| FC70                        | RPF12R <sup>(1)</sup> | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF12    | 2<3:0>    |      | 000        |

|                             | (1)                   | 31:16         | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    | _    | _        | _         | —    | 000        |

| FC74                        | RPF13R <sup>(1)</sup> | 15:0          | _     | _     | _     | _     | _     | _     | _    | _    | _    | _    | _    | _    |      | RPF13    | 3<3:0>    |      | 000        |

|                             | <b>DD000</b> (1)      | 31:16         | _     | _     | _     | _     | _     | _     | —    | _    | _    | _    | _    | _    | _    | —        | _         |      | 000        |

| FC80                        | RPG0R <sup>(1)</sup>  | 15:0          | _     | _     | _     | _     | —     | _     | —    | _    | _    | _    | _    | _    |      | RPG0     | <3:0>     |      | 000        |

| F004                        |                       | 31:16         | _     | -     | _     | _     | —     | _     | _    | _    | -    | _    | _    | _    | _    | _        | _         | _    | 000        |

| FC84                        | RPG1R <sup>(1)</sup>  | 15:0          | _     |       | _     | _     | _     |       | —    | _    |      |      |      | —    |      | RPG1     | <3:0>     |      | 000        |

| ECOS                        | DDC6D                 | 31:16         |       |       |       |       | _     |       | —    |      |      |      |      | _    |      | _        | _         |      | 000        |

| FC98                        | RPG6R                 | 15:0          | _     | _     | _     | _     | _     |       | _    |      |      |      | _    | —    |      | RPG6     | <3:0>     |      | 000        |

| FC9C                        | RPG7R                 | 31:16         |       | _     | _     | _     | _     | —     | _    |      | _    | _    | —    | _    | _    | _        | _         | _    | 000        |

| 1 090                       | NEGIK                 | 15:0          | Ι     | _     | —     | —     | _     | —     | _    | _    | _    | _    | _    |      |      | RPG7     | <3:0>     |      | 000        |

**Note 1:** This register is not available on 64-pin devices.

2: This register is only available on devices without a USB module.

3: This register is not available on 64-pin devices with a USB module.

# 17.0 OUTPUT COMPARE

Note: This data sheet summarizes the features of the PIC32MX330/350/370/430/450/470 family of devices. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to Section 16. "Output Compare" (DS60001111), which is available from the *Documentation* > *Reference Manual* section of the Microchip PIC32 web site (www.microchip.com/pic32).

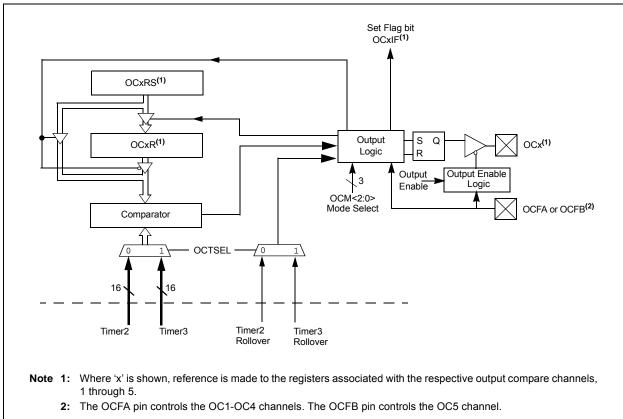

The Output Compare module is used to generate a single pulse or a train of pulses in response to selected time base events. For all modes of operation, the Output Compare module compares the values stored in the OCxR and/or the OCxRS registers to the value in the selected timer. When a match occurs, the Output Compare module generates an event based on the selected mode of operation.

The following are key features of this module:

- Multiple Output Compare modules in a device

- Programmable interrupt generation on compare event

- Single and Dual Compare modes

- Single and continuous output pulse generation

- Pulse-Width Modulation (PWM) mode

- Hardware-based PWM Fault detection and automatic output disable

- Can operate from either of two available 16-bit time bases or a single 32-bit time base

# FIGURE 17-1: OUTPUT COMPARE MODULE BLOCK DIAGRAM

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|--------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|

| 24.04        | U-0               | U-0               | U-0               | U-0               | U-0               | U-0               | U-0              | R/W-0            |

| 31:24        | _                 | —                 | _                 | _                 | _                 | _                 | _                | ADM_EN           |

| 00.40        | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0            | R/W-0            |

| 23:16        |                   |                   |                   | ADDR<             | <7:0>             |                   |                  |                  |

| 45.0         | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R/W-0             | R-0              | R-1              |

| 15:8         | UTXISE            | L<1:0>            | UTXINV            | URXEN             | UTXBRK            | UTXEN             | UTXBF            | TRMT             |

| 7.0          | R/W-0             | R/W-0             | R/W-0             | R-1               | R-0               | R-0               | R/W-0            | R-0              |

| 7:0          | URXISE            | L<1:0>            | ADDEN             | RIDLE             | PERR              | FERR              | OERR             | URXDA            |

## REGISTER 20-2: UxSTA: UARTx STATUS AND CONTROL REGISTER

## Legend:

| Logonal           |                  |                          |                    |

|-------------------|------------------|--------------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit, r | ead as '0'         |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared     | x = Bit is unknown |

### bit 31-25 Unimplemented: Read as '0'

- bit 24 ADM\_EN: Automatic Address Detect Mode Enable bit

- 1 = Automatic Address Detect mode is enabled

- 0 = Automatic Address Detect mode is disabled

- bit 23-16 ADDR<7:0>: Automatic Address Mask bits

When the ADM\_EN bit is '1', this value defines the address character to use for automatic address detection.

### bit 15-14 UTXISEL<1:0>: TX Interrupt Mode Selection bits

- 11 = Reserved, do not use

- 10 = Interrupt is generated and asserted while the transmit buffer is empty

- 01 = Interrupt is generated and asserted when all characters have been transmitted

- 00 = Interrupt is generated and asserted while the transmit buffer contains at least one empty space

### bit 13 UTXINV: Transmit Polarity Inversion bit

If IrDA mode is disabled (i.e., IREN (UxMODE<12>) is '0'):

- 1 = UxTX Idle state is '0'

- 0 = UxTX Idle state is '1'

### If IrDA mode is enabled (i.e., IREN (UxMODE<12>) is '1'):

- 1 = IrDA encoded UxTX Idle state is '1'

- 0 = IrDA encoded UxTX Idle state is '0'

### bit 12 URXEN: Receiver Enable bit

- 1 = UARTx receiver is enabled. UxRX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx receiver is disabled. UxRX pin is ignored by the UARTx module. UxRX pin is controlled by the port.

### bit 11 UTXBRK: Transmit Break bit

- 1 = Send Break on next transmission. Start bit followed by twelve '0' bits, followed by Stop bit; cleared by hardware upon completion

- 0 = Break transmission is disabled or completed

- bit 10 UTXEN: Transmit Enable bit

- 1 = UARTx transmitter is enabled. UxTX pin is controlled by UARTx (if ON = 1)

- 0 = UARTx transmitter is disabled. Any pending transmission is aborted and buffer is reset. UxTX pin is controlled by the port.

### bit 9 UTXBF: Transmit Buffer Full Status bit (read-only)

- 1 = Transmit buffer is full

- 0 = Transmit buffer is not full, at least one more character can be written

|              |                   | ICDAIL. N         |                   |                   |                                         |                   |                  |                  |  |  |

|--------------|-------------------|-------------------|-------------------|-------------------|-----------------------------------------|-------------------|------------------|------------------|--|--|

| Bit<br>Range | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3                       | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

| 04.04        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |

| 31:24        |                   | YEAR1             | 0<3:0>            |                   |                                         | YEAR0             | 1<3:0>           |                  |  |  |

| 00.40        | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |

| 23:16        |                   | MONTH             | 10<3:0>           |                   | MONTH01<3:0>                            |                   |                  |                  |  |  |

| 45.0         | R/W-x             | R/W-x             | R/W-x             | R/W-x             | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |

| 15:8         |                   | DAY10             | <3:0>             |                   | DAY01<3:0>                              |                   |                  |                  |  |  |

| 7.0          | U-0               | U-0               | U-0               | U-0               | R/W-x                                   | R/W-x             | R/W-x            | R/W-x            |  |  |

| 7:0          |                   | _                 | _                 | —                 | WDAY01<3:0>                             |                   |                  |                  |  |  |

|              |                   |                   |                   |                   | •                                       |                   |                  |                  |  |  |

| Legend:      |                   |                   |                   |                   |                                         |                   |                  |                  |  |  |

| R = Read     | able bit          |                   | W = Writable      | e bit             | U = Unimple                             | emented bit, re   | ead as '0'       |                  |  |  |

| -n = Value   | -n = Value at POR |                   |                   | et                | '0' = Bit is cleared x = Bit is unknown |                   |                  |                  |  |  |

# REGISTER 22-4: RTCDATE: RTC DATE VALUE REGISTER

bit 31-28 YEAR10<3:0>: Binary-Coded Decimal Value of Years bits, 10s place digits

bit 27-24 YEAR01<3:0>: Binary-Coded Decimal Value of Years bits, 1s place digit

bit 23-20 MONTH10<3:0>: Binary-Coded Decimal Value of Months bits, 10s place digits; contains a value of 0 or 1

bit 19-16 MONTH01<3:0>: Binary-Coded Decimal Value of Months bits, 1s place digit; contains a value from 0 to 9

bit 15-12 DAY10<3:0>: Binary-Coded Decimal Value of Days bits, 10s place digits; contains a value from 0 to 3

bit 11-8 **DAY01<3:0>:** Binary-Coded Decimal Value of Days bits, 1s place digit; contains a value from 0 to 9

bit 7-4 Unimplemented: Read as '0'

bit 3-0 WDAY01<3:0>: Binary-Coded Decimal Value of Weekdays bits,1s place digit; contains a value from 0 to 6

**Note:** This register is only writable when RTCWREN = 1 (RTCCON<3>).

# 28.0 SPECIAL FEATURES

This data sheet summarizes the features Note: of the PIC32MX330/350/370/430/450/470 family of devices. However, it is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to "Configuration" Section 32. (DS60001124) and Section 33. "Programming and **Diagnostics**" (DS60001129), which are available from the Documentation > Reference Manual section of the Microchip PIC32 web site (www.microchip.com/pic32).

The PIC32MX330/350/370/430/450/470 family of devices include several features intended to maximize application flexibility and reliability and minimize cost through elimination of external components. These are:

- · Flexible device configuration

- Joint Test Action Group (JTAG) interface

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)

## 28.1 Configuration Bits

The Configuration bits can be programmed using the following registers to select various device configurations.

- DEVCFG0: Device Configuration Word 0

- DEVCFG1: Device Configuration Word 1

- DEVCFG2: Device Configuration Word 2

- DEVCFG3: Device Configuration Word 3

- · CFGCON: Configuration Control Register

In addition, the DEVID register (Register 28-6) provides device and revision information.

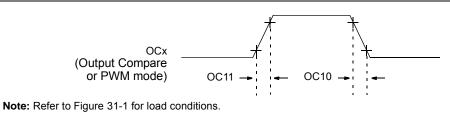

## TABLE 31-27: OUTPUT COMPARE MODULE TIMING REQUIREMENTS

|               |        | (unless                        | d Operating C<br>otherwise stat<br>g temperature | ,                      |      |       |                    |

|---------------|--------|--------------------------------|--------------------------------------------------|------------------------|------|-------|--------------------|

| Param.<br>No. | Symbol | Characteristics <sup>(1)</sup> | Min.                                             | Typical <sup>(2)</sup> | Max. | Units | Conditions         |

| OC10          | TccF   | OCx Output Fall Time           | —                                                | —                      | _    | ns    | See parameter DO32 |

| OC11          | TccR   | OCx Output Rise Time           | —                                                | —                      | _    | ns    | See parameter DO31 |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

## FIGURE 31-9: OCx/PWM MODULE TIMING CHARACTERISTICS

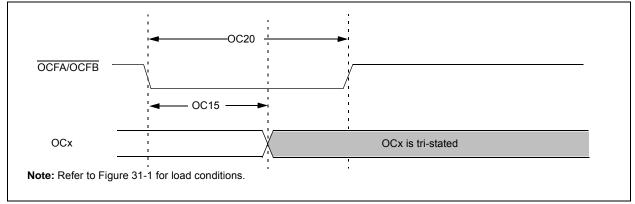

## TABLE 31-28: SIMPLE OCx/PWM MODE TIMING REQUIREMENTS

| AC CHAP      | (unless |                                | (unless o | d Operating Conditions: 2.3V to 3.6V<br>otherwise stated)<br>g temperature $0^{\circ}C \le TA \le +70^{\circ}C$ for Commercial<br>$-40^{\circ}C \le TA \le +85^{\circ}C$ for Industrial<br>$-40^{\circ}C \le TA \le +105^{\circ}C$ for V-temp |     |       |            |  |  |

|--------------|---------|--------------------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------|------------|--|--|

| Param<br>No. | Symbol  | Characteristics <sup>(1)</sup> | Min       | Typical <sup>(2)</sup>                                                                                                                                                                                                                        | Max | Units | Conditions |  |  |

| OC15         | Tfd     | Fault Input to PWM I/O Change  | —         | —                                                                                                                                                                                                                                             | 50  | ns    | _          |  |  |

| OC20         | TFLT    | Fault Input Pulse Width        | 50        | —                                                                                                                                                                                                                                             | _   | ns    | —          |  |  |

Note 1: These parameters are characterized, but not tested in manufacturing.

2: Data in "Typical" column is at 3.3V, 25°C unless otherwise stated. Parameters are for design guidance only and are not tested.

| AC CHA        | RACTER  | ISTICS                     |                               | Standard Operatin<br>(unless otherwise<br>Operating tempera | e stated)<br>iture 0°(<br>-4( | C ≤ TA ≤ +<br>)°C ≤ TA ≤ | 70°C for Commercial<br>+85°C for Industrial |  |

|---------------|---------|----------------------------|-------------------------------|-------------------------------------------------------------|-------------------------------|--------------------------|---------------------------------------------|--|

| Param.<br>No. | Symbol  | Charact                    | eristics                      | Min. <sup>(1)</sup>                                         | +105°C for V-temp Conditions  |                          |                                             |  |

| IM10          | TLO:SCL | Clock Low Time             | 100 kHz mode                  | Трв * (BRG + 2)                                             |                               | μS                       |                                             |  |

|               | 1201002 |                            | 400 kHz mode                  | Трв * (BRG + 2)                                             |                               | μs                       | _                                           |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             |                               | μs                       | -                                           |  |

| IM11          | THI:SCL | Clock High Time            | 100 kHz mode                  | Трв * (BRG + 2)                                             |                               | μS                       | _                                           |  |

|               |         | _                          | 400 kHz mode                  | Трв * (BRG + 2)                                             |                               | μS                       | _                                           |  |

|               |         |                            | 1 MHz mode<br>(Note 2)        | Трв * (BRG + 2)                                             | _                             | μs                       | _                                           |  |

| IM20          | TF:SCL  | SDAx and SCLx              | 100 kHz mode                  |                                                             | 300                           | ns                       | CB is specified to be                       |  |

|               |         | Fall Time                  | 400 kHz mode                  | 20 + 0.1 Св                                                 | 300                           | ns                       | from 10 to 400 pF                           |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | _                                                           | 100                           | ns                       |                                             |  |

| IM21          | TR:SCL  | SDAx and SCLx<br>Rise Time | 100 kHz mode                  | —                                                           | 1000                          | ns                       | CB is specified to be                       |  |

|               |         |                            | 400 kHz mode                  | 20 + 0.1 Св                                                 | 300                           | ns                       | from 10 to 400 pF                           |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | —                                                           | 300                           | ns                       |                                             |  |

| IM25          | TSU:DAT | Data Input<br>Setup Time   | 100 kHz mode                  | 250                                                         |                               | ns                       | —                                           |  |

|               |         |                            | 400 kHz mode                  | 100                                                         | _                             | ns                       |                                             |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | 100                                                         | —                             | ns                       |                                             |  |

| IM26          | THD:DAT | Data Input<br>Hold Time    | 100 kHz mode                  | 0                                                           |                               | μS                       | —                                           |  |

|               |         |                            | 400 kHz mode                  | 0                                                           | 0.9                           | μS                       | 1                                           |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | 0                                                           | 0.3                           | μs                       |                                             |  |

| IM30          | TSU:STA | Start Condition            | 100 kHz mode                  | Трв * (BRG + 2)                                             | —                             | μS                       | Only relevant for                           |  |

|               |         | Setup Time                 | 400 kHz mode                  | Трв * (BRG + 2)                                             |                               | μS                       | Repeated Start                              |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                             | μs                       | condition                                   |  |

| IM31          | THD:STA | Start Condition            | 100 kHz mode                  | Трв * (BRG + 2)                                             | —                             | μS                       | After this period, the                      |  |

|               |         | Hold Time                  | 400 kHz mode                  | Трв * (BRG + 2)                                             |                               | μS                       | first clock pulse is                        |  |

|               |         |                            | 1 MHz mode<br><b>(Note 2)</b> | Трв * (BRG + 2)                                             | —                             | μs                       | generated                                   |  |

| IM33          | Tsu:sto | Stop Condition             | 100 kHz mode                  | Трв * (BRG + 2)                                             | —                             | μS                       | —                                           |  |

|               |         | Setup Time                 | 400 kHz mode                  | Трв * (BRG + 2)                                             |                               | μS                       |                                             |  |

|               |         |                            | 1 MHz mode<br>(Note 2)        | Трв * (BRG + 2)                                             | _                             | μS                       |                                             |  |

# TABLE 31-33: I2Cx BUS DATA TIMING REQUIREMENTS (MASTER MODE)

**Note 1:** BRG is the value of the  $l^2C$  Baud Rate Generator.

2: Maximum pin capacitance = 10 pF for all I2Cx pins (for 1 MHz mode only).

**3:** The typical value for this parameter is 104 ns.

| AC CHARACTERISTICS <sup>(5)</sup> |            |                                | $\begin{array}{l} \mbox{Standard Operating Conditions: 2.3V to 3.6V} \\ \mbox{(unless otherwise stated)} \\ \mbox{Operating temperature} & 0^{\circ}C \leq TA \leq +70^{\circ}C \mbox{ for Commercial} \\ -40^{\circ}C \leq TA \leq +85^{\circ}C \mbox{ for Industrial} \\ -40^{\circ}C \leq TA \leq +105^{\circ}C \mbox{ for V-temp} \end{array}$ |              |      |       |                                                         |  |  |  |