Welcome to E-XFL.COM

## What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

## Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

## Details

E·XF

| Details                    |                                                                            |

|----------------------------|----------------------------------------------------------------------------|

| Product Status             | Active                                                                     |

| Core Processor             | PIC                                                                        |

| Core Size                  | 8-Bit                                                                      |

| Speed                      | 32MHz                                                                      |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                  |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                      |

| Number of I/O              | 6                                                                          |

| Program Memory Size        | 3.5KB (2K x 14)                                                            |

| Program Memory Type        | FLASH                                                                      |

| EEPROM Size                | 256 x 8                                                                    |

| RAM Size                   | 256 x 8                                                                    |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                |

| Data Converters            | A/D 5x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                   |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                          |

| Mounting Type              | Surface Mount                                                              |

| Package / Case             | 8-UDFN Exposed Pad                                                         |

| Supplier Device Package    | 8-UDFN (3x3)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18313-i-rf |

|                            |                                                                            |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## **Table of Contents**

| Chapte | r 1.         | General              | Descripti             | on        |     |     |   |     |   |     |   |     |     |     |    |   |     |   |     |            |   |  |

|--------|--------------|----------------------|-----------------------|-----------|-----|-----|---|-----|---|-----|---|-----|-----|-----|----|---|-----|---|-----|------------|---|--|

| 1.2 F  | eatur        | uction .<br>es<br>ew |                       | • • •     | • • | • • | • | • • |   | • • | • |     | •   |     |    |   |     | • |     | 1-1        | • |  |

| 1      | .3.1         | I/O Port             | 9                     | • • •     | ••  | • • | • | ••  | • | ••  | • | • • |     | ••  | •• | • |     | • | ••• | 1-1        |   |  |

|        |              |                      | Ports A<br>Port C .   |           |     |     |   |     |   |     |   |     |     |     |    |   |     |   |     |            |   |  |

| 1.     | .3.2<br>.3.3 | Counter/<br>Interrup | Timers .<br>t Control | <br>Logic | ••• | ••• | • | ••• | • | ••• | • | ••• | ••• | ••• | •• | • | ••• | • | ••• | 1-3<br>1-4 |   |  |

## Chapter 2. Register Descriptions

| 2.1  | Introduction                                     |

|------|--------------------------------------------------|

| 2.2  | Register Addressing for the Z8036 (Z- $CIO$ )    |

| 2.3  | Register Addressing for the Z8536 (CIO)          |

| 2.4  | Master Control Registers                         |

|      | 2.4.1 Master Interrupt Control Register          |

|      | 2.4.2 Master Configuration Control Register      |

| 2.5  | Port Specification Registers                     |

|      | 2.5.1 Port Mode Specification Registers          |

|      | 2.5.2 Port Handshake Specification Registers     |

|      | 2.5.3 Port Command and Status Registers          |

| 2.6  | Bit Path Definition Registers 2-9                |

|      | 2.6.1 Data Path Polarity Registers               |

|      | 2.6.2 Data Direction Registers                   |

|      | 2.6.3 Special I/O Control Registers              |

| 2.7  | Pattern Definition Registers                     |

| 2.8  | Port Data Registers                              |

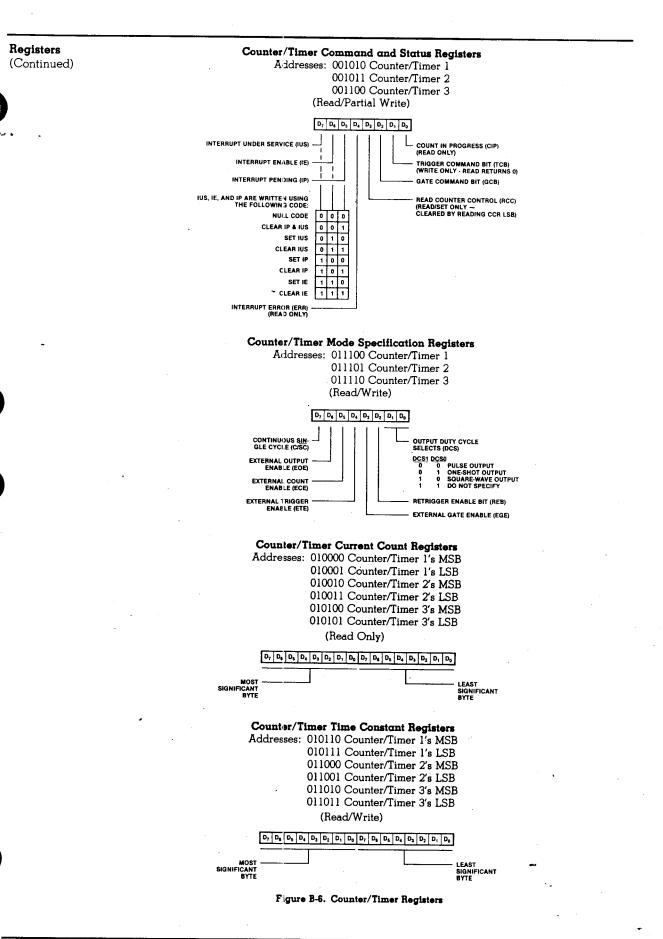

| 2.9  | Counter/Timer Control Registers                  |

|      | 2.9.1 Counter/Timer Mode Specification Registers |

|      | 2.9.2 Counter/Timer Command and Status Registers |

|      | 2.9.3 Counter/Timer Time Constant Registers      |

|      | 2.9.4 Counter/Timer Current Count Registers      |

| 2.10 | Interrupt-Related Registers                      |

|      | 2.10.1 Interrupt Vector Registers                |

|      | 2.10.2 Current Vector Register 2-16              |

|      |                                                  |

2

1

i

## Table of Contents (Continued)

| Chapi             | ter 3.  | I/O Port   | <b>Operat</b> ion                |

|-------------------|---------|------------|----------------------------------|

| 3.1<br>3.2<br>3.3 | Patterr | n Recognit | tion Logic                       |

|                   |         |            | Simple Operation                 |

|                   | 3.3.2   | Bit Port   | Pattern-Recognition Operations   |

| 3.4               | Handsha | ike Port ( | Operation                        |

|                   | 3.4.1   | Four Hand  | dshake Modes                     |

|                   |         | 3.4.1.1    | Interlocked Handshake            |

|                   |         | 3.4.1.2    | Strobed Handshake                |

|                   |         | 3.4.1.3    | Pulsed Handshake                 |

|                   |         | 3.4.1.4    | 3-Wire Handshake                 |

|                   | 3.4.2   | Input Pop  | rt with Handshake                |

|                   |         | 3.4.2.1    | Basic Modes of Operation         |

|                   |         | 3.4.2.2    | Handshake Types                  |

|                   | 3.4.3   | Output Pa  | ort with Handshake               |

|                   |         | 3.4.3.1    | Basic Modes of Operation         |

|                   |         |            | Handshake Types                  |

|                   | 3.4.4   | Bidirect   | ional Port Operation             |

|                   |         | 3.4.4.1    | Input Operation                  |

|                   |         | 3.4.4.2    | Input to Output Direction Change |

|                   |         | 3.4.4.3    | Output Operations                |

|                   |         | 3.4.4.4    | Output to Input Direction Change |

|                   |         | 3.4.4.5    | Pattern Match                    |

|                   | 3.4.5   | REQUEST/   | WAIT Line Operation              |

|                   |         | 3.4.5.1    | REQUEST Line Operation           |

|                   |         | 3.4.5.2    | WAIT Line Operation              |

|                   | 3.4.6   | Linked P   | ort Operation                    |

| Internal<br>Address<br>(Binary) | Read/Write | Register Name                         |

|---------------------------------|------------|---------------------------------------|

|                                 | Counter/   | Timer Related Registers               |

| 010000                          | R          | Counter/Timer 1 Current Count MS Byte |

| 010001                          | R          | Counter/Timer 1 Current Count LS Byte |

| 010010                          | R          | Counter/Timer 2 Current Count MS Byte |

| 010 <b>011</b>                  | R          | Counter/Timer 2 Current Count LS Byte |

| 010100                          | R R        | Counter/Timer 3 Current Count MS Byte |

| 010101                          | R          | Counter/Timer 3 Current Count LS Byte |

| 010110                          | R/W        | Counter/Timer 1 Time Constant MS Byte |

| 010111                          | R/W        | Counter/Timer 1 Time Constant LS Byte |

| 011000                          | R/W        | Counter/Timer 2 Time Constant MS Byte |

| 011001                          | R/W        | Counter/Timer 2 Time Constant LS Byte |

| 01101 <b>0</b>                  | R/W        | Counter/Timer 3 Time Constant MS Byte |

| 011011                          | R/W        | Counter/Timer 3 Time Constant LS Byte |

| 011100                          | R/W        | Counter/Timer 1 Mode Specification    |

| 011101                          | R/W        | Counter/Timer 2 Mode Specification    |

| 011110                          | R/W        | Counter/Timer 3 Mode Specification    |

| 011111                          | R          | Current Vector                        |

## Table 2-1. Z8036/Z8536 Z-CIO/CIO Register Summary--Continued

## Port A Specification Registers

| 100000 | R/W | Port A Mode Specification      |

|--------|-----|--------------------------------|

| 100001 | R/W | Port A Handshake Specification |

| 100010 | R/W | Port A Data Path Polarity      |

| 100011 | R/W | Port A Data Direction          |

| 100100 | R/W | Port A Special I/O Control     |

| 100101 | R/W | Port A Pattern Polarity        |

| 100110 | R/W | Port A Pattern Transition      |

| 100111 | R/W | Port A Pattern Mask            |

|        |     |                                |

## Port B Specification Registers

| 101000<br>101001 | R/W<br>R/W | Port B Mode Specification<br>Port B Handshake Specification |

|------------------|------------|-------------------------------------------------------------|

| 10101 <b>0</b>   | R/W        | Port B Data Path Polarity                                   |

| 101011           | R/W        | Port B Data Direction                                       |

| 101100           | R/W        | Port B Special I/O Control                                  |

| 101101           | R/W        | Port B Pattern Polarity                                     |

| 101110           | R/W        | Port B Pattern Transition                                   |

| 101111           | R/W        | Port B Pattern Mask                                         |

\* All bits can be read and some bits can be written.

\*\* Also directly addressable in Z8536 using pins A<sub>0</sub> and A<sub>1</sub>. (See Table 2-2 and Figures 8-1 and 8-2.)

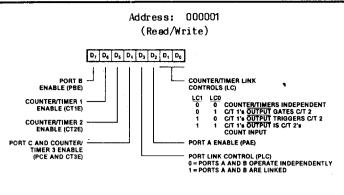

Figure 2-3. Master Configuration Control Register

Port B Enable--PBE (D7). This bit, when set to 1, allows Port B to operate normally. When cleared to 0, it inhibits the Port B logic from issuing an interrupt request (its IP cannot be set); however, if IP was already set, clearing PBE does not clear IP. While cleared to 0, PBE inhibits READY/WAIT assertion, holds all 1's catchers in a transparent condition, and forces the Port B I/O lines into a high-impedance state. The purpose of this bit is to allow Port B to be configured initially without setting its IP erroneously or having its I/O lines go low-impedance until it is safe to do so.

**Counter/Timer 1 Enable--CT1E (D<sub>6</sub>).** When cleared to 0, Counter/Timer 1 is put into an initialized state: its IP cannot be set (however, if IP was already set, clearing CT1E does not clear IP), the Count In Progress (CIP) flag is cleared, Read Counter Control (RCC) is forced to 0, and all trigger inputs are ignored. Setting CT1E to 1 allows the counter/timer to function normally.

**Counter/Timer 2 Enable--CT2E (D5).** The CT2E bit performs the same function for Counter/Timer 2 that CT1E performs for Counter/Timer 1.

**Port C and Counter/Timer 3 Enable--PCE and CT3E** ( $D_{4}$ ). This bit enables both Port C and Counter/ Timer 3. The function is the same as  $D_7$  (PBE) and  $D_6$  (CT1E) for Port B and Counter/Timer 1, respectively. In addition, while this bit is cleared to 0, the handshake logic for Ports A and B is forced into an idle state and the internal Acknowledge Input ( $\overline{\text{ACKIN}}$ ) signal is forced High. This allows the start-up of handshake operations to be precisely controlled.

**Port Link Control--PLC (D3).** When PLC is set to 1, Ports A and B are linked to form a 16-bit port. In this mode, only the Port A Handshake Specification and Command and Status registers are used. Port B must be specified as a bit port and its pattern match capability must be disabled. Also, when linked, the Port B data register must be read or written before the Port A data register. A 0 in the PLC bit allows the ports to operate independently. If the ports are to be linked, this bit must be set before the ports are enabled.

**Port A Enable--PAE (D\_2).** The Port A Enable bit performs the same function for Port A that the Port B Enable bit ( $D_7$ ) performs for Port B.

**Counter/Timer Link Controls--LC1 & LC0 (D1. &** D0). These two bits specify if and how Counter/ Timers 1 and 2 are linked. The Counter/Timers must be linked before they are enabled. The various configurations are shown in Table 2-3.

Table 2-3. Counter/Timer Link Controls

| LC <sub>1</sub> | ւշ | Configuration                                                                                                                               |

|-----------------|----|---------------------------------------------------------------------------------------------------------------------------------------------|

| 0               | 0  | Counter/Timers are independent                                                                                                              |

| 0               | 1  | Counter/Timer 1's output (inverted) gates Counter/Timer 2                                                                                   |

| 1               | 0  | Counter/Timer 1's output (inverted) triggers Counter/Timer 2                                                                                |

| 1               | 1  | Counter/Timer 1's output (inverted) is Counter/Timer 2's count input<br>(Counter/Timer 2's External Count Enable* bit must be cleared to 0) |

\* (See Section 2.9.1 for description of External Count Enable bit.)

2-5

## Table 3-1. Port C Pin Utilization

|--|

| Port A/B Configuration                                                           | Pin C3                     | Pin C <sub>2</sub> | Pin C <sub>1</sub>         | Pin C <sub>O</sub> |

|----------------------------------------------------------------------------------|----------------------------|--------------------|----------------------------|--------------------|

| Ports A & B = Bit Ports                                                          | Bit I/O                    | Bit I/O            | Bit I/O                    | Bit I/O            |

| Port A = Input or Output<br>port (Interlocked, Strobed,<br>or Pulsed Handshake)* | RFD or DAV                 | ACKIN              | REQUEST/WAIT<br>or Bit I/O | Bit I/O            |

| Port B = Input or Output<br>port (Interlocked, Strobed,<br>or Pulsed Handshake)* | REQUEST/WAIT<br>or Bit I/O | Bit I/O            | RFD or DAV                 | ACKIN              |

| Port A or B = Input port<br>(3-Wire Handshake)                                   | RFD (Output)               | DAV (Input)        | REQUEST/WAIT<br>or Bit I/O | DAC (Output)       |

| Port A or B = Output port<br>(3-Wire Handshake)                                  | DAV (Output)               | DAC (Input)        | REQUEST/WAIT<br>or Bit I/O | RFD (Input)        |

| Port A or B = Bidirectional<br>port (Interlocked or Strobed<br>Handshake)        | RFD or DAV                 | ACKIN              | REQUEST/WAIT<br>or Bit I/O | IN/OUT             |

\* Both Ports A & B can be specified input or output with Interlocked, Strobed, or Pulsed Handshake at the same time if neither uses REQUEST/WAIT. However, only one port can use the Pulsed Handshake at a time.

#### 3.4.1 Four Handshake Modes

There are four handshake modes: Interlocked, Strobed, Pulsed, and 3-Wire.

### 3.4.1.1 Interlocked Handshake

In the Interlocked Handshake mode, the action of the CIO must be acknowledged by the external device before the next action can take place. An output port does not indicate that new data is available until the external device indicates it is ready for the data. Similarly, an input port does not indicate that it is ready for new data until the data source indicates that the previous byte of data is no longer available, thereby acknowledging the input port's acceptance of the last byte. This handshake allows the CID to interface directly to the port of a Z8 microcomputer, a UPC, an FIG, an FIFO, or to another CIO port, etc., with no external logic.

#### 3.4.1.2 Strobed Handshake

In the Strobed Handshake mode, data is "strobed" into or out of the port by the external logic. The falling edge of the Acknowledge Input ( $\overline{ACKIN}$ ) strobes data into or out of the port. In contrast to the Interlocked Handshake, the signal indicating that the port is ready for another data transfer operates independently of the  $\overline{ACKIN}$  input. The external logic must ensure that data does not transfer at too fast or too slow a rate.

## 3.4.1.3 Pulsed Handshake

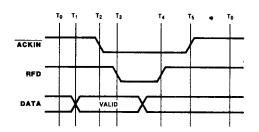

The Pulsed Handshake mode is designed to interface to mechanical-type devices which require data to be held for long periods of time and need relatively wide pulses to gate the data into or out of the device. The logic is the same as the Interlocked Handshake mode, except that an internal counter/timer (Counter/Timer 3) is linked to the ACKIN and RFD are both High. ACKIN High indicates that the data is not valid; RFD High indicates that the Buffer register is empty and ready for data.

T1. Data on port pins becomes valid.

T2. ACKIN goes Low, indicating that the data is valid, and causing it to be latched into the Buffer register.

T<sub>3</sub>. RFD goes Low, indicating that the Buffer register is full and the port is not ready for more data.

> The data is transferred into the Input Data register, the Input Data register Full (IRF) flag goes High and the Buffer register is emptied. The port is now ready for the next byte of data. RFD could go High if <u>ACKIN</u> is High; but because <u>ACKIN</u> is Low, RFD stays Low.

T<sub>0</sub>.

T1.

17.

T3.

TA.

Ts becomes Tn-

Τς.

TA.

T0.

ACKIN goes High.

T<sub>6</sub> becomes T<sub>0</sub>.

RFD goes High, concluding the handshake process; the cycle is ready to repeat.

## Strobed Input Handshake

The Strobed Handshake (Figure 3-4) operates in the same way as the Interlocked Handshake, except that the rising edge of the RFD output is independent of  $\overline{ACKIN}$  going High. As soon as the Buffer register is emptied, RFD goes High, even if  $\overline{ACKIN}$  is still Low. In all other respects, the two handshakes are the same. The falling edge of the  $\overline{ACKIN}$  input "strobes" the data into the port.

The following example provides a step-by-step analysis of an input port configured as doublebuffered and using Strobed Handshake. (This description uses Figure 3-4 as reference.)

## Figure 3-4. Strobed Input Handshake Timing Diagram

ACKIN and RFD are both High. ACKIN High indicates that the data is not valid; RFD High indicates that the Buffer register is empty and ready for data.

Data on port pins becomes valid.

> ACKIN goes Low, indicating that the data is valid, and causing it to be latched in the Buffer register.

RFD goes Low, indicating that the Buffer register is full and the port is not ready for more data.

The data is moved into the Input Data register, the Input Data register Full (IRF) flag goes High, the Buffer register is emptied, and RFD goes High.

ACKIN is High; the cycle is ready to repeat.

PS011201-0601

3-9

Command and Status register is automatically set to 1 along with Output Data Register Empty (ORE) of the Port Command and Status register when the data is moved out of the Output Data register and into the Buffer register. Writing to the port data register "fills" the Output Data register and automatically clears the IP (hence, ORE = 0 and 1P = 0. IP can be cleared (IP = 0) by software command; that is, by writing bits  $D_7-D_5$  of the Port Command and Status register. However, the Output Data register is not "filled" until the data is written. Since IP is set only when data is moved out of the Output Data register, then if the port is enabled (PAE or PBE is set to 1) without writing any data, IP will not be set even though the Output Data register is empty.

While programmed to interrupt on two bytes (ITB = 1), IP is not automatically set to 1 until both the Output Data and Buffer registers are empty; that is, the Buffer register becomes empty while the Output Data register is empty. IP is automatically cleared (IP = 0) when the second byte of data is written by the CPU to the data register. The first data write fills the Output Data register and allows the data to be moved into the Buffer register. The second data write fills the now empty Output Data register and automatically clears the IP. As when ITB = 0, when the port is initially enabled, the IP will not be set nor will an interrupt request be generated until a byte of data is written to it. Data can be written to it after it is initially configured and before it is enabled.

When ITB = 1, the Output Data register should not be written unless IP = 1, even if ORE = 1. Otherwise, the data may be written just as the Bufferregister is going empty and as IP is being set. In this case, an interrupt may be requested for a two-byte write, when only one byte is needed, because the first byte has already been written but not output.

## NOTE

The IP can be cleared on command. This suggests the following possible sequence for providing byte-by-tyte control of the DAV output: writing one byte of data and then clearing IP by command allows an interrupt when the Buffer register is "emptied" by the handshake logic.

## Single-Buffered (SB = 1)

When the output port is specified as singlebuffered (SB = 1), output data is moved from the Output Data register to the Buffer register as in the double-buffered case. However, when the data is moved into the Buffer register, the Output Data register is not emptied. A copy of the data is maintained there. In this mode, the handshake logic "empties" both registers: when  $\overline{ACKIN}$  falls, the Output Data and Buffer registers are emptied, and both ORE and IP are automatically set to 1. Writing the port data register fills the Output Data register and clears IP (ORE = IP = 0).

## NOTE

Unlike the double-buffered operation, IIB = 1 does not make sense in singlebuffered operation. Thus, when SB = 1, IIB must = 0.

## With Pattern Match Added (PMS<sub>1</sub> = PMS<sub>0</sub> $\neq$ 0)

The port's built-in pattern match logic can be used to test the data as it is coming into or through the data register. The available pattern match modes operate independently of handshake type and are specified by the Pattern Mode Specification bits ( $PMS_1$  and  $PMS_0$ ). In the output port operation, the AND and the OR modes are available for use, but the OR-PEV is not. This pattern availability for AND and OR logic is a consequence of the pattern being tested as the data is moved into the Input Data register, eliminating access to the transition information. Because of this, transition patterns cannot be used.

The Pattern Match Flag (PMF) of the Port Command and Status register is set to 1 or is cleared to 0 as the data is moved from the Output Data register to the Buffer register.

When ITB = 0, IP is set when data is moved out of the Output Data register. If PMF = 1, writing the data register does not automatically clear the IP--the IP can only be cleared by writing to the Port Command and Status Register. Also, writing the Output Data register does not "fill" it; the Output Data register can be "filled" (and ORE cleared to 0) only if it is written and the IP is cleared, (in any order). Data that is written

## Interrupt on Match Only (IMO = 1) Specified

When the Interrupt on Match. Only bit of the Port Mode Specification register is set to 1, an interrupt request will be generated only when the data moved out of the Output Data register into the Buffer register matches the pattern specification. For output ports, the IMO capability is especially useful when data transfer is under the control of an external device (for example, a DMA controller). In this way the bulk of the data transfers can be accomplished without interrupts (that is, without involvement of the CPU) by having an interrupt generated only when the match pattern is encountered. The CIO, through the IMO, allows a long string of bytes to be output without interrupts. This is accomplished by simply waiting on a pattern which is inserted at the end of a string to signal the end of the transmission by way of a single CPU interrupt request. This way, many bytes can be moved with only one interrupt request being generated.

#### NOTE

IMO must be O if either IIB or SB = 1, or if the port is a bit port.

#### 3.4.3.2 Hendshake Types

The operation of Port A and B output handshakes will be explained by describing in detail the sequence of operations performed by an output port programmed with Interlocked Handshake. Any differences encountered when using the other handshakes will then be described. See Table 3-1 for identification of the handshake lines furnished by Port C bits for Ports A and B.

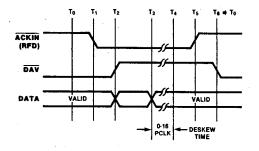

### Deskew Timer Description

Because external devices may require that the data be valid for a certain minimum amount of time prior to the DAV signal being pulled Low (to indicate data available), the CIO provides a separate deskew timer for each port. As data is transferred to the Buffer register, the deskew timer is triggered (if the timer is enabled (DTE = 1). After the number of PCLK cycles (up to 16) specified by the deskew timer Time Constant (see Figure 2-5), DAV is allowed to go Low (the interlock may keep DAV High). The deskew timer does not extend the time from ACKIN rising to DAV falling. The deskew timer therefore quarantees that the output data is valid for a specified minimum amount of time before DAV goes Low.

Deskew timers are available for output ports independent of the type of handshake employed. Each port has a separate 4-bit deskew timer. Thus, the CIO can provide the proper timing to interface to those external devices that require a large data valid to  $\overline{\text{DAV}}$  falling setup time. For example, the IEEE-488 specification requires data to be valid for 2 microseconds before  $\overline{\text{DAV}}$  can go Low.

## Interlocked Output Handshake

The Interlocked Output Handshake requires that the output port does not indicate that it has data available (DAV goes Low) until the receiving port indicates that the previous byte of data has been accepted (indicated by ACKIN being High).

Interlocked Handshake port configuration allows the CIO to communicate directly with a variety of other devices without the need for external logic. Devices such as another CIO, FIO, FIO, Z8 Port, etc., can be interfaced directly. Figure 3-2 shows two interconnected CIOs: the output port's DAV output connects to the input port's ACKIN input and the input port's RFD output connects to the output sort's ACKIN input.

In Interlocked Output Handshake mode (Figure 3-9), the CPU writes data into the Output Data register. If the Buffer register is empty, the data is moved to it and on to the port output pins ("emptying" the Output Data register). The Output Data register Empty (ORE) bit in the port Command and Status register is then set to 1 and Data Available ( $\overline{DAV}$ ) handshake line goes Low (if ACKIN is High). The CPU can now write another byte into the Output Data register, setting ORE to 0. When

Figure 3-9. Interlocked Output Handshake Timing Diagram

## 3.4.5.1 REQUEST Line Operation

Operation of the REQUEST line is dependent on the state of the port's Interrupt on Two Bytes (ITB) control bit. When ITB = 0, the REQUEST line goes active as soon as the CIO is ready for a data transfer. If the port is used for the input, the REQUEST line goes High when the Input Data register is full. If the port is used for output, the REQUEST line goes High when the Output Data register is empty. If ITB = 1, REQUEST goes active only if two bytes can be moved. For input, both Input Data and Buffer registers are full, and for output, both Buffer and Output Data registers are empty. REQUEST stays active as long as a byte is available to be read or written. However, if the port is single-buffered or if the Pattern Match Flag is set, REQUEST goes Low when the data is read or written.

In the bidirectional mode, ITB must be O. Therefore, the REQUEST line reflects the state of the Input or Output Data register, depending on the type of REQUEST line specified.

The DMA-type transfer is facilitated by the use of the Interrupt on Match Only (IMO) control bit in the Port Mode Specification register. In most DMA transfers, the peripheral does not generate an interrupt request. However, the Interrupt on Match Only (IMO) capability of the CIO allows it to interrupt the CPU when there is a specified byte match, such as an end of transfer flag, etc. Except for the specified pattern match, the CPU is not involved in the transfer; the data movement is consequently accomplished much faster. This REQUEST line/IMO pattern match operation can function in all port operating modes.

The SPECIAL REQUEST function is reserved for use with bidirectional ports only. In this case, the REQUEST line indicates the status of the register not being used in the data path at that time. If the  $IN/\overline{OUT}$  line is High (input port), the REQUEST line is High when the Output Data register is empty. If  $IN/\overline{OUT}$  is Low (output port), the REQUEST line goes High when the Input'Data register is full. In this mode, both the Input and the Output Data registers can be monitored. The RED/DAV indicates the state of the register in the data path, and the REQUEST line monitors the register not in the data path.

This line can be used to indicate when to change the CIO direction. For example, if the CIO is a "slave" bidirectional port in the input direction  $(IN/\overline{OUT} = High)$ , then when the SPECIAL REQUEST line goes Low (indicating that the Output Data register has a byte to be transferred), the master port can use this as the signal to turn the port around so that the byte can be output.

## 3.4.5.2 WAIT Line Operation

The REQUEST/WAIT line configured in the WAIT mode is useful to synchronize CPU-to-CIO transactions. For example, when the CPU wants the data transfer to be performed as rapidly as possible, it does not want to wait for an interrupt service routine to tell it that the CIO is ready to receive or supply a byte of data. Rather, the CPU attempts a read or write to the CIO. If WAIT is enabled, and the CIO is not ready for a read or write to it, WAIT is pulled Low and the CPU is forced to wait until the CIO is ready (the Input register becomes full or the Output register becomes empty), signified by the WAIT line going High. The CPU is now released from the WAIT pause and can complete the data transaction.

For an input port, WAIT is pulled Low when an attempt is made to read the Input Data register and the port is empty. For an output port, WAIT is pulled Low when an attempt is made to write to the Output Data register that is still full; the data integrity is maintained in the case of the output port--the data is not overwritten. Action is merely suspended until the write can take place.

In the Z8036,  $\overrightarrow{WAIT}$  falling is caused by  $\overrightarrow{DS}$  falling. In the Z8536,  $\overrightarrow{WAIT}$  is synchronized with either RD or  $\overrightarrow{WD}$  falling.  $\overrightarrow{WAIT}$ , however, may be required to be valid at the CPU prior to this. A practical way to use  $\overrightarrow{WAIT}$  with the CIO is to have external logic generate a  $\overrightarrow{WAIT}$  cycle automatically, which can then be extended as needed by the CIO.

The release of  $\overline{WAIT}$  in both the Z8036 and the Z8536 is synchronized with the PCLK input. Thus for the Z8036 REQUEST/ $\overline{WAIT}$  function, a PCLK input is required. Also, while the Z8036 is asserting  $\overline{WAIT}$ , internal status is updated using PCLK (not  $\overline{AS}$  as it normally does), because  $\overline{AS}$  stops as long as the CPU is  $\overline{WAIT}$ ed.

## 3.4.6 Linked Port" Operation

Ports A and B can be linked to form a 16-bit port by programming a 1 in the Port Link Control (PLC) bit of the Master Configuration Control register. In this mode, only Port A's Handshake Specification and Status registers are used. Port B must be specified as a bit port. When linked, only Port A has pattern-match capability. Port B's pattern-match capability must be disabled. Also, when the ports are linked, Port B's Data register must be read or written before Port A's. The PLC bit must be set to 1 before the ports are enabled.

t

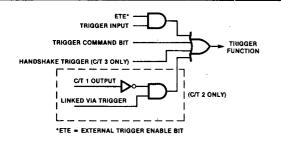

Figure 4-2. Trigger OR-Function Diagram

#### 4.2.3 Count down Sequence

The rate at which the down-counter counts is determined by the mode of the counter/timer. In the Timer mode (the External Count Enable [ECE] bit is 0), the down-counter is clocked internally by a signal that is half the frequency of the PCLK input to the chip. In the Counter mode (ECE is 1), the down-counter is decremented on the rising edge of the counter/timer's counter input.

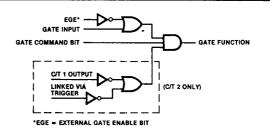

Once the down-counter is loaded, the countdown sequence continues toward terminal count as long as all of the counter/timers' hardware and software gate inputs are High. The gate inputs are: the Gate Command bit of the Counter/Timer Command and Status register, and the external gate input if enabled in the External Gate Enable bit of the counter/timer Mode Specification register. Also, for Counter/Timer 2 use only, the counter/timer output (inverted) can be used as a gate if linked via the gate in the Counter/Timer Link Controls bits of the Master Configuration Control regis-If any of the gate inputs go Low (0), the ter. countdown halts. It resumes when all gate inputs are 1 again. The gate function does not affect the trigger function.

The gate functions as the logical AND of all the potential gates (see Figure 4-3).

## NOTE

In order to ensure the enabling or disabling of the counter/timer on a particular rising edge of the clocking signal, sufficient setup time must be allowed. The gate signal must be valid prior to the immediately preceding falling edge of the clocking signal.

The reaction to triggers occurring during a countdown sequence is determined by the state of the Retrigger Enable Bit (REB) in the Mode Specification register. If REB is 0, retriggers are ignored and the countdown continues normally. If REB is 1, each trigger causes the down-counter to be reloaded and the countdown sequence starts over again. If the output is programmed in the Square-Wave mode, a retrigger causes the sequence to start over from the initial load of the time constant.

The state of the down-counter can be determined in two ways: by reading the contents of the downcounter via the Current Count register or by testing the Count In Progress (CIP) status bit in the Command and Status register. The CIP status bit is set when the down-counter is loaded; it is reset when the down-counter reaches O. The Current Count register is a 16-bit register, accessible as two 8-bit registers, which mirrors the contents of the down-counter. This register can be read anytime. However, reading the register is asynchronous to the counter's counting, and the value returned can be guaranteed as valid only if the counter is stopped. The down-counter can be read reliably while it is counting by first writing a 1 to the Read Counter Control (RCC) bit in the counter/timer's Command and Status register. This freezes the value in the Current Count register until a read of the least-significant byte is performed. A read of RCC indicates if the CCR is holding a value, or if it is following the downcounter.

## 4.2.4 Ending Condition

The Continuous/Single Cycle (C/SC) bit in the Mode Specification register controls operation of the down-counter when it reaches terminal count (the count following the count of 1). If C/SC is 0 reading the vector register returns the unmodified base vector so that it can be verified.

Another register, the Current Vector register, facilitates the use of the CIO in  $\epsilon_I$  polled environment. When read, the data returned is the same as the interrupt vector that is output in an Interrupt Acknowledge, based on the highest-priority IP set. If no unmasked IPs are set, the value  $FF_H$  is returned. The Current Vector register provides a simple way to poll all IPs in a single read.

The No Vector (NV) control bit of the Master Interrupt Control register, when set to 1, inhibits the outputting of an interrupt vector during an INTACK cycle. The NV bit does not affect the setting of the IUS operation. The only thing that the NV does is prevent the vector from being output on the bus.

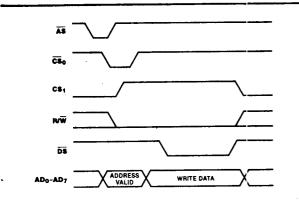

## 5.4 Z-BUS INTERRUPT OPERATION

Figure 7-5 displays Interrupt Acknowledge timing. The Z8036 generates an interrupt request by lowering the INT line only if:

- Such interrupt requests are enabled (IE is 1, MEI is 1).

- It has an interrupt pending (IP = 1).

- It does not have an interrupt under service (IUS is 0).

- No higher-priority interrupt is being serviced (IEI is 1).

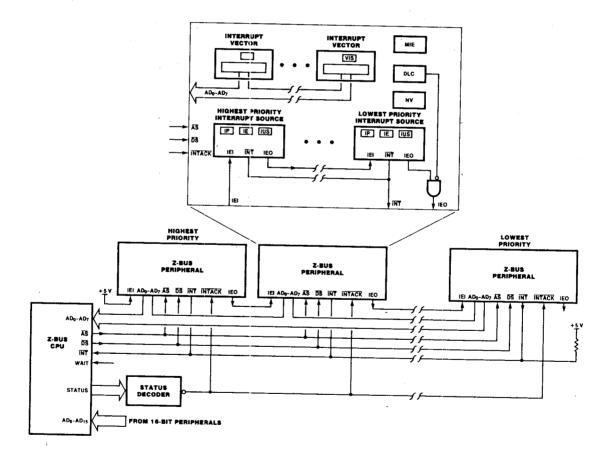

Figure 5-2 shows a typical Z-BUS interrupt arbitration setting.

IEO is not pulled down by the Z8036 at this time; IEO continues to follow IEI until an Interrupt Acknowledge transaction occurs.

Figure 5-2. Z-BUS Interrupt Arbitration

cleared to O, the corresponding logic sections are in an initialization mode. All of the registers can be read and written, but the normal operation of the sections is inhibited. The Port A and Port B Enables, when cleared to O, force their respective I/O lines into a high-impedance state, hold the 1's catchers in a reset condition, inhibit REQUEST/WAIT generation, and prevent the setting of their Interrupt Pending (IP) bits (the states of IP and Interrupt Under Service (IUS) are not affected). Additionally, output data can be written (the first data output is valid when the output drivers go active), but the data direction for these bits must be properly specified before the data is written. The Port C Enable operates in the same way, and, until set to 1, the handshake logic for Ports A and B is forced into an idle state. The Counter/Timer Enables, when set to 0, terminate any countdown sequence in progress, inhibit the counter/timer from being triggered, and force the counter output to O. While the enable is O, the Read Counter Control (RCC) bit in the Counter/Timer Command and Status register is forced to 0. Independent enable bits are provided for the different sections of the device so that the individual sections can be reconfigured without disturbing the status of the unchanged sections. By using these enable bits, the device can be initialized in any sequence as long as the desired configuration for a section is specified before its enable bit is set to 1. When ports or counter/timers are to be linked, the bits which specify linking must be programmed before the functions are enabled. In this case two writes are required to the Master Configuration Control register.

## 6.5 PROGRAMMING

Programming the CIO entails loading control registers with bits to implement the desired operation. As discussed above, individual enable bits are provided for the various major blocks so that erroneous operations do not occur while the port is being initialized. Before the ports are enabled: IPs cannot be set, REQUESI and WAIT cannot be asserted, and all outputs remain highimpedance; the handshake lines are ignored until Port C is enabled; and the counter/timers cannot be triggered until their enable bits are set.

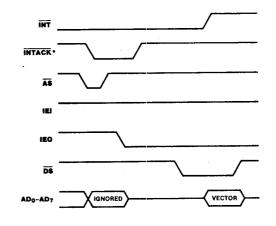

## 6.5.1 Programming the Z8036

Programming the 28036 is simple, because every register is directly addressable--a key advantage of the multiplex Address/Data bus.

The Z8036 allows two schemes for register addressing. Both schemes use only six of the eight bits of the Address/Data bus. The scheme used is determined by the Right Justify Address (RJA) bit in the Master Interrupt Control When RJA equals 0, Address bus bits 0 register. and 7 are ignored, and bits 1 through 6 are decoded for the register address (A<sub>0</sub> is derived from AD<sub>1</sub>). When RJA equals 1, bits 0 through 5 are decoded for the register address (A $_{

m O}$  is derived from ADn).

## 6.5.2 Programming the Z8536

The Data Registers of Ports A, B, and C are directly addressed by pins  $A_{\rm D}$  and  $A_{\rm 1},$  as shown in Table 6-1.

## Table 6-1. Z8536 Data Register Addressing

| A <sub>1</sub> | <b>^</b> 0 | Register             |  |  |  |  |  |  |

|----------------|------------|----------------------|--|--|--|--|--|--|

| 0              | 0          | Port C Data Register |  |  |  |  |  |  |

| 0              | 1          | Port B Data Register |  |  |  |  |  |  |

| 1              | 0          | Port A Data Register |  |  |  |  |  |  |

| 1              | 1          | Control Registers    |  |  |  |  |  |  |

All other internal registers are accessed by the following two-step sequence (with pins  $A_0 = A_1 = 1$ ). First write the address of the target register to an internal 6-bit Pointer register, then read from or write to the target register. The Data registers can also be accessed by this method.

In the Z8536, an internal state machine determines if access (with pins  $A_0 = A_1 = 1$ ) is to the Pointer register or to an internal control register (See Figure 6-1). Following any control read operation the state machine is in State 0, and the

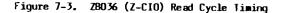

## Chapter 7 Z8036 (Z-CIO) Interfacing

## 7.1 INTRODUCTION

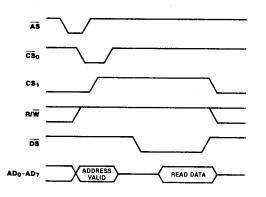

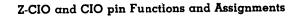

This section provides information on pin functions and assignments and functional timing diagrams for the Z8036 Z-CIO.

### 7.2 FEATURES

The following features of the Z8036 are not obvious without reference to the ac timing diagrams in the Z8036 Product Specification, document #00-2014-A0.

- The Address Strobe  $(\overline{AS})$  input functions as the clock of the Z8036. If the  $\overline{AS}$  stops, then data does not get clocked in or through the device, IPs are not set, etc. Care should be taken in the design of the system to ensure that  $\overline{AS}$  to the Z8036 is not blocked.

- The assertion of REQUEST is synchronous with PCLK.

- The release of WAIT is sychronous with PCLK.

- PCLK is only used with the counter/timers (in timer mode), the deskew timers, and the REQUEST/WAIT logic. If these functions are not used, the PCLK input can be held Low.

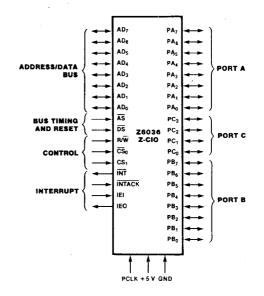

### 7.3 PIN FUNCTIONS AND ASSIGNMENTS

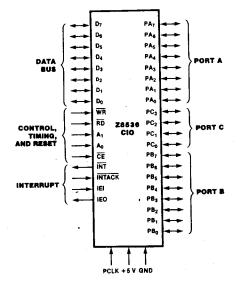

The Z8036 is configured for Z-BUS interface controls and timing. The pin functions and assignments are shown in Figures 7-1 and 7-2. Section 7.4 is a description of the pin functions for the Z8036.

### 7.4 PIN DESCRIPTIONS

| ADn-AD7.   | z-Bus  | Addre | ss/Data  | lines | (bidirec-   |

|------------|--------|-------|----------|-------|-------------|

| tional/3-s | tate). | These | multiple | xed A | ddress/Data |

Figure 7-1. Z8036 (Z-CIO) Pin Functions

| IEI         17         24         INT           IEO         18         23         + 5 V           PC0         19         22         PC3           PC1         20         21         PC2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | PCLK 16 25 INTACK                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | ` PB7 15 26 PA7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | PB6 🖸 14 27 🗋 PA6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PB5 13 28 PA5                                                                                                                                                                                                                                                                                                                                                                                | PB4 🖸 12 29 🖸 PA4                                                                         | PB3 11 2-CIO 30 PA3                                                                                                                                                                                                                                                                                                                                                                                                                                                           | PB2 10 Z8036 31 PA2                                                       | PB1 9 32 PA1                                              | PB <sub>2</sub> 10 Z803<br>PB <sub>3</sub> 11<br>PB <sub>4</sub> 12<br>PB <sub>5</sub> 13<br>PB <sub>6</sub> 14 | 16 31 PA2<br>0 30 PA3<br>29 PA4<br>28 PA5 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|-------------------------------------------|

| PB1         9         32         PA1           PB2         10         Z8036         31         PA2           PB3         11         ZCIO         30         PA3           PB4         12         29         PA4           PB5         13         28         PA5           PB6         14         27         PA6           PB7         15         26         PA7           PCLK         16         25         INTACK                                                                                                                                                                                                                                                                                                          | PB1         9         32         PA1           PB2         10         Z8036         31         PA2           PB3         11         ZC10         30         PA3           PB4         12         29         PA4           PB5         13         28         PA5           PB6         14         27         PA6                                                                                                                                                                                                                | PB1         9         32         PA1           PB2         10 <b>Z8036</b> 31         PA2           PB3         11 <b>Z-CIO</b> 30         PA3           PB4         12         29         PA4           PB5         13         28         PA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PB1         9         32         PA1           PB2         10 <b>Z8036</b> 31         PA2           PB3         11 <b>Z-CIO</b> 30         PA3           PB4         12         29         PA4                                                                                                                                                                                                                                                                                                                                                                                                                                  | PB1 9 32 PA1<br>PB2 10 <b>Z8036</b> 31 PA2<br>PB3 11 <b>30</b> PA3                                                                                                                                                                                                                                                                                                                           | PB1 9 32 PA1<br>PB2 10 <b>Z8036</b> 31 PA2<br><b>Z-CIO</b> 31 PA2                         | PB1 9 32 PA1<br>PB2 10 <b>Z8036</b> 31 PA2                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           |                                                           | PB0 8                                                                                                           | 33 🗖 PAg                                  |

| PB1         9         32         PA1           PB2         10         Z8036         31         PA2           PB3         11         ZCIO         30         PA3           PB4         12         29         PA4           PB5         13         28         PA5           PB6         14         27         PA6           PB7         15         26         PA7           PCLK         16         25         INTACK                                                                                                                                                                                                                                                                                                          | PB1         9         32         PA1           PB2         10         ZB036         31         PA2           PB3         11         ZC10         31         PA2           PB3         11         30         PA3           PB4         12         29         PA4           PB5         13         28         PA5           PB6         14         27         PA6                                                                                                                                                                | PB1         9         32         PA1           PB2         10 <b>Z8036</b> 31         PA2           PB3         11 <b>Z-CIO</b> 30         PA3           PB4         12         29         PA4           PB5         13         28         PA5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | PB1         9         32         PA1           PB2         10 <b>Z8036</b> 31         PA2           PB3         11 <b>Z-CIO</b> 30         PA3           PB4         12         29         PA4                                                                                                                                                                                                                                                                                                                                                                                                                                  | PB1 9 32 PA1<br>PB2 10 <b>Z8036</b> 31 PA2<br>PB3 11 <b>30</b> PA3                                                                                                                                                                                                                                                                                                                           | PB1 9 32 PA1<br>PB2 10 <b>Z8036</b> 31 PA2<br><b>Z-CIO</b> 31 PA2                         | PB1 9 32 PA1<br>PB2 10 <b>Z8036</b> 31 PA2                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                           | PB0 8 33 PA0                                              |                                                                                                                 | 34 <b>5</b> AS                            |

| GND         7         34         ÅŠ           PB0         8         33         PA0           PB1         9         32         PA1           PB2         10         Z8036         31         PA2           PB3         11         30         PA3           PB4         12         29         PA4           PB5         13         28         PA5           PB6         14         27         PA6           PB7         15         26         PA7           PCLK         16         25         INTACK                                                                                                                                                                                                                          | GND         7         34         ÅŠ           PB <sub>0</sub> 8         33         PA <sub>0</sub> PB <sub>1</sub> 9         32         PA <sub>1</sub> PB <sub>2</sub> 10         ZE036         31         PA <sub>2</sub> PB <sub>3</sub> 11         ZC036         31         PA <sub>2</sub> PB <sub>3</sub> 11         30         PA <sub>3</sub> PB <sub>4</sub> 12         29         PA <sub>4</sub> PB <sub>5</sub> 13         28         PA <sub>5</sub> PB <sub>6</sub> 14         27         PA <sub>6</sub>        | GND         7         34         ÅS           PB <sub>0</sub> 8         33         PA <sub>0</sub> PB <sub>1</sub> 9         32         PA <sub>1</sub> PB <sub>2</sub> 10 <b>Z8036</b> 31         PA <sub>2</sub> PB <sub>3</sub> 11         30         PA <sub>3</sub> PB <sub>4</sub> 12         29         PA <sub>4</sub> PB <sub>5</sub> 13         28         PA <sub>5</sub>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | GND         7         34         ÅŠ           PB0         8         33         PA0           PB1         9         32         PA1           PB2         10         Z8036         31         PA2           PB3         11         Z-CIO         31         PA3           PB4         12         29         PA4                                                                                                                                                                                                                                                                                                                   | GND         7         34         ÅŠ           PB0         8         33         PA0           PB1         9         32         PA1           PB2         10 <b>Z8036</b> 31         PA2           PB3         11         30         PA3                                                                                                                                                       | GND 7 34 ÅŠ<br>PBo 8 33 PAo<br>PB1 9 32 PA1<br>PB2 10 <b>Z8036</b> 31 PA2<br><b>Z-CIO</b> | GND 7 34 AS<br>PB0 8 33 PA0<br>PB1 9 32 PA1<br>PB2 10 <b>Z8036</b> 31 PA2                                                                                                                                                                                                                                                                                                                                                                                                     | GND 07 34 0 ÅŠ<br>PB0 08 33 0 PA₀                                         | GND 7 34 🛛 🗛                                              |                                                                                                                 |                                           |

| $ \begin{array}{c c c c c c c c c c c c c c c c c c c $                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | RW         6         35         CS1           GND         7         34         ÅS           PB0         8         33         PP40           PB1         9         32         PA1           PB2         10         Z8036         31         PA22           PB3         11         20         PA3         PB4           PB4         12         29         PA4                                                                                                                                                                                                                                                                     | RW         6         35         CS1           GND         7         34         ÅŠ           PB0         8         33         PA0           PB1         9         32         PA1           PB2         10         Z8036         31         PA2           PB3         11         30         PA3                                                                                                | $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                      | R/₩ 6 35 CS1<br>GND 7 34 AS<br>PB <sub>0</sub> 8 33 PA <sub>0</sub><br>PB <sub>1</sub> 9 32 PA <sub>1</sub><br>PB <sub>0</sub> 10 <b>Z8036</b> 31 PA <sub>2</sub>                                                                                                                                                                                                                                                                                                             | R/₩ [ 6 35 ] CS1<br>GND [ 7 34 ] ÅŠ<br>PB0 [ 8 33 ] PA0                   | R/₩ 6 35 CS1<br>GND 7 34 AS                               |                                                                                                                 |                                           |

| DS         5         36         CSo           RVW         6         35         CSi           GND         7         34         AS           PB0         8         33         PA0           PB1         9         32         PA1           PB2         10         ZE036         31         PA2           PB3         11         Z-CIO         30         PA3           PB4         12         29         PA4           PB5         13         28         PA6           PB5         14         27         PA6           PB7         15         26         PA7           PCLK         16         25         INTACK                                                                                                               | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | DS         5         36         CS0           RVW         6         35         CS1           GND         7         34         A5           PB0         8         33         PA0           PB1         9         32         PA1           PB2         10         Z8036         31         PA2           PB3         11         20         PA3         PB4         12         29         PA4                                                                                                                                                                                                                                      | DS         5         36         CS0           R/W         6         35         CS1           GNO         7         34         ÅÅ           PB0         8         33         PA0           PB1         9         32         PA1           PB2         10         ZB036         31         PA2           PB3         11         30         PA3                                                 | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                     | DS 5 36 CS <sub>0</sub><br>RW 6 35 CS <sub>1</sub><br>GND 7 34 AS<br>PB <sub>0</sub> 8 33 PA <sub>0</sub><br>PB <sub>1</sub> 9 32 PA <sub>1</sub><br>PB <sub>0</sub> 10 <b>Z8036</b> 31 PA <sub>2</sub>                                                                                                                                                                                                                                                                       | DS 0 5 36 0 CS₀<br>RW 0 6 35 0 CS₁<br>GND 7 34 0 AS<br>PB₀ 8 33 0 PA₀     | DS 5 36 0 CS₀<br>RW 6 35 0 CS₁<br>GND 7 34 0 AS           |                                                                                                                 |                                           |

| AD7         4         37         AD0           DS         5         36         CS0           RW         6         35         CS1           GND         7         34         AS           PB0         8         33         PA0           PB1         9         32         PA1           PB2         10         Z8036         31         PA2           PB3         11         30         PA3           PB4         12         29         PA4           PB5         13         28         PA6           PB6         14         27         PA6           PB7         15         26         PA7           PCLK         16         25         INTACK                                                                               | AD7         4         37         AD0           DS         5         36         CS0           RW         6         35         CS1           GND         7         34         AS           PB0         8         33         PA0           PB1         9         32         PA1           PB2         10         ZB036         31         PA2           PB3         11         30         PA3         PA3           PB4         12         29         PA4         PA5           PB6         13         28         PA5         PA6 | AD7         4         37         AD0           DS         5         36         CS0           R/W         6         35         CS1           GND         7         34         AS           PB0         8         33         PA0           PB1         9         32         PA1           PB2         10         Z8036         31         PA2           PB3         11         30         PA3         PB4         12         29         PA4           PB5         13         28         PA5         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S         S | AD7         4         37         AD0           DS         5         36         CS0           RW         6         35         CS1           GND         7         34         AS           PB0         8         33         PA0           PB1         9         Z8036         31         PA2           PB3         11         ZCIO         30         PA3           PB4         12         29         PA4                                                                                                                                                                                                                         | AD7         4         37         AD0           DS         5         36         CS0           R/W         6         35         CS1           GND         7         34         AB3           PB0         8         32         PA1           PB1         9         32         PA1           PB2         10         ZE036         31         PA2           PB3         11         30         PA3 | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                    | AD7 4 37 AD0<br>DS 5 36 CS0<br>R/₩ 6 35 CS1<br>GND 7 34 AS<br>PB0 8 33 PA0<br>PB1 9 32 PA1<br>PB0 10 Z8036 31 PA2                                                                                                                                                                                                                                                                                                                                                             | AD7 4 37 AD0<br>D3 5 36 CS0<br>RW 6 35 CS1<br>GND 7 34 AS<br>PB0 8 33 PA0 | AD7 4 37 AD0<br>DS 5 36 CS0<br>RW 6 35 CS1<br>GND 7 34 AS |                                                                                                                 |                                           |