Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Obsolete                                                                |

|----------------------------|-------------------------------------------------------------------------|

| Core Processor             | 8032                                                                    |

| Core Size                  | 8-Bit                                                                   |

| Speed                      | 24MHz                                                                   |

| Connectivity               | I <sup>2</sup> C, UART/USART                                            |

| Peripherals                | LVD, POR, PWM, WDT                                                      |

| Number of I/O              | 37                                                                      |

| Program Memory Size        | 80KB (80K x 8)                                                          |

| Program Memory Type        | FLASH                                                                   |

| EEPROM Size                | -                                                                       |

| RAM Size                   | 2K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                               |

| Data Converters            | A/D 4x8b                                                                |

| Oscillator Type            | Internal                                                                |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                           |

| Package / Case             | 52-TQFP                                                                 |

| Supplier Device Package    | -                                                                       |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/upsd3212cv-24t6 |

|                            |                                                                         |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

51

# **3 UPSD321xx hardware description**

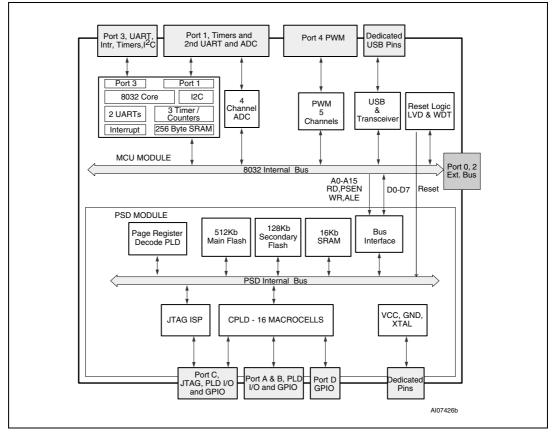

The UPSD321xx devices have a modular architecture with two main functional modules: the MCU module and the PSD module. The MCU module consists of a standard 8032 core, peripherals and other system supporting functions. The PSD module provides configurable Program and Data memories to the 8032 CPU core. In addition, it has its own set of I/O ports and a PLD with 16 macrocells for general logic implementation. Ports A,B,C, and D are general purpose programmable I/O ports that have a port architecture which is different from Ports 0-4 in the MCU module.

The PSD module communicates with the CPU Core through the internal address, data bus (A0-A15, D0-D7) and control signals (RD\_, WR\_, PSEN\_, ALE, RESET\_). The user defines the Decoding PLD in the PSDsoft Development Tool and can map the resources in the PSD module to any program or data address space.

# 9 Supervisory

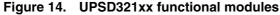

There are four ways to invoke a reset and initialize the UPSD321xx devices.

- 1. Via the external RESET pin

- 2. Via the internal LVR block

- 3. Via USB bus reset signaling

- 4. Via Watchdog Timer (WDT)

The RESET mechanism is illustrated in *Figure 19*.

Each RESET source will cause an internal reset signal active. The CPU responds by executing an internal reset and puts the internal registers in a defined state. This internal reset is also routed as an active low reset input to the PSD module.

# 9.1 External reset

The RESET pin is connected to a Schmitt trigger for noise reduction. A RESET is accomplished by holding the RESET pin LOW for at least 1ms at power up while the oscillator is running. Refer to AC spec on other RESET timing requirements.

# 9.2 Low V<sub>DD</sub> voltage reset

An internal reset is generated by the LVR circuit when the  $V_{DD}$  drops below the reset threshold. After  $V_{DD}$  reaching back up to the reset threshold, the RESET signal will remain asserted for 10ms before it is released. On initial power-up the LVR is enabled (default). After power-up the LVR can be disabled via the LVREN Bit in the PCON Register.

Note: The LVR logic is still functional in both the Idle and Power-down modes.

The reset threshold:

- 5 V operation: 4 V ± 0.25 V

- 3.3 V operation: 2.5 V ± 0.2 V

This logic supports approximately 0.1 V of hysteresis and 1 µs noise-cancelling delay.

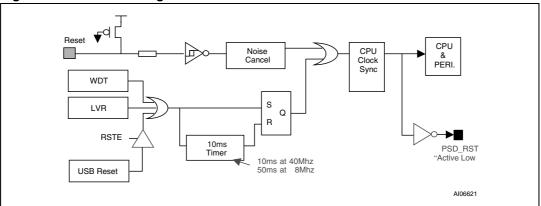

### Figure 20. RESET pulse width

### Table 34. Watchdog timer clear register (WDRST: 0A6h)

| 7        | 6      | 5      | 4      | 3      | 2      | 1      | 0      |

|----------|--------|--------|--------|--------|--------|--------|--------|

| Reserved | WDRST6 | WDRST5 | WDRST4 | WDRST3 | WDRST2 | WDRST1 | WDRST0 |

### Table 35.Description of the WDRST Bits

| Bit    | Symbol                 | Function                                                                                                                                                                                      |

|--------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7      | _                      | Reserved                                                                                                                                                                                      |

| 6 to 0 | WDRST6<br>to<br>WDRST0 | To reset watchdog timer, write any value beteen 00h and 7Eh to this<br>register.<br>This value is loaded to the 7 most significant bits of the 22-bit counter.<br>For example: MOV WDRST,#1EH |

1. The Watchdog Timer (WDT) is enabled at power-up or reset and must be served or disabled.

# 12 Standard serial interface (UART)

The UPSD321xx devices provides two standard 8032 UART serial ports. The first port is connected to pin P3.0 (RX) and P3.1 (TX). The second port is connected to pin P1.2 (RX) and P1.3(TX). The operation of the two serial ports are the same and are controlled by the SCON and SCON2 registers.

The serial port is full duplex, meaning it can transmit and receive simultaneously. It is also receive-buffered, meaning it can commence reception of a second byte before a previously received byte has been read from the register. (However, if the first byte still has not been read by the time reception of the second byte is complete, one of the bytes will be lost.) The serial port receive and transmit registers are both accessed at Special Function Register SBUF (or SBUF2 for the second serial port). Writing to SBUF loads the transmit register, and reading SBUF accesses a physically separate receive register.

The serial port can operate in 4 modes: Mode 0, 1, 2 or 3.

### Mode 0

Serial data enters and exits through RxD. TxD outputs the shift clock. 8 bits are transmitted/received (LSB first). The baud rate is fixed at 1/12 the f<sub>OSC</sub>.

#### Mode 1

10 bits are transmitted (through TxD) or received (through RxD): a Start bit (0), 8 data bits (LSB first), and a Stop bit (1). On receive, the Stop bit goes into RB8 in Special Function Register SCON. The baud rate is variable.

### Mode 2

11 bits are transmitted (through TxD) or received (through RxD): Start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a Stop bit (1). On Transmit, the 9th data bit (TB8 in SCON) can be assigned the value of '0' or '1'. Or, for example, the Parity bit (P, in the PSW) could be moved into TB8. On receive, the 9th data bit goes into RB8 in Special Function Register SCON, while the Stop bit is ignored. The baud rate is programmable to either 1/32 or 1/64 the oscillator frequency.

### Mode 3

11 bits are transmitted (through TxD) or received (through RxD): a Start bit (0), 8 data bits (LSB first), a programmable 9th data bit, and a Stop bit (1). In fact, Mode 3 is the same as Mode 2 in all respects except baud rate. The baud rate in Mode 3 is variable.

In all four modes, transmission is initiated by any instruction that uses SBUF as a destination register. Reception is initiated in Mode 0 by the condition RI = 0 and REN = 1. Reception is initiated in the other modes by the incoming start bit if REN = 1.

### 12.1 Multiprocessor communications

Modes 2 and 3 have a special provision for multiprocessor communications. In these modes, 9 data bits are received. The 9th one goes into RB8. Then comes a Stop bit. The port can be programmed such that when the Stop bit is received, the serial port interrupt will

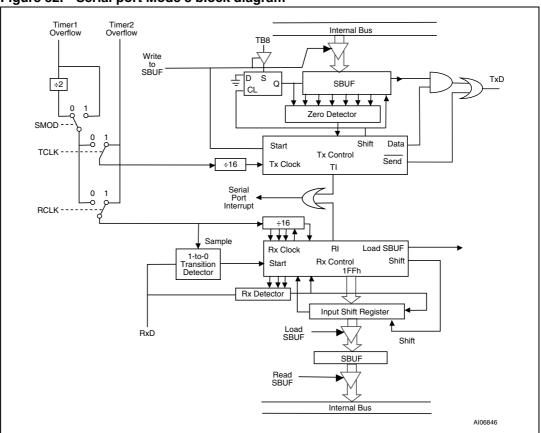

*Figure 26* shows a simplified functional diagram of the serial port in Mode 0, and associated timing.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "WRITE to SBUF" signal at S6P2 also loads a '1' into the 9th position of the transmit shift register and tells the TX Control block to commence a transmission. The internal timing is such that one full machine cycle will elapse between "WRITE to SBUF" and activation of SEND.

SEND enables the output of the shift register to the alternate out-put function line of RxD and also enable SHIFT CLOCK to the alternate output function line of TxD. SHIFT CLOCK is low during S3, S4, and S5 of every machine cycle, and high during S6, S1, and S2. At S6P2 of every machine cycle in which SEND is active, the contents of the transmit shift are shifted to the right one position.

As data bits shift out to the right, zeros come in from the left. When the MSB of the data byte is at the output position of the shift register, then the '1' that was initially loaded into the 9th position, is just to the left of the MSB, and all positions to the left of that contain zeros. This condition flags the TX Control block to do one last shift and then deactivate SEND and set T1. Both of these actions occur at S1P1. Both of these actions occur at S1P1 of the 10th machine cycle after "WRITE to SBUF."

Reception is initiated by the condition REN = 1 and R1 = 0. At S6P2 of the next machine cycle, the RX Control unit writes the bits 11111110 to the receive shift register, and in the next clock phase activates RECEIVE.

RECEIVE enables SHIFT CLOCK to the alternate output function line of TxD. SHIFT CLOCK makes transitions at S3P1 and S6P1 of every machine cycle in which RECEIVE is active, the contents of the receive shift register are shifted to the left one position. The value that comes in from the right is the value that was sampled at the RxD pin at S5P2 of the same machine cycle.

As data bits come in from the right, '1s' shift out to the left. When the '0' that was initially loaded into the right-most position arrives at the left-most position in the shift register, it flags the RX Control block to do one last shift and load SBUF. At S1P1 of the 10th machine cycle after the WRITE to SCON that cleared RI, RECEIVE is cleared as RI is set.

### 12.2.5 More about Mode 1

Ten bits are transmitted (through TxD), or received (through RxD): a start Bit (0), 8 data bits (LSB first). and a Stop bit (1). On receive, the Stop bit goes into RB8 in SCON. In the UPSD321xx devices the baud rate is determined by the Timer 1 or Timer 2 overflow rate.

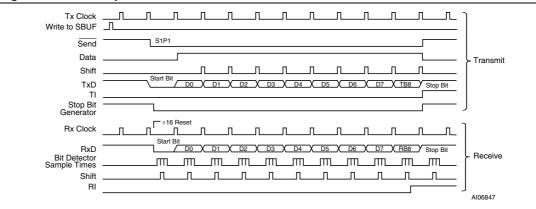

*Figure 28* shows a simplified functional diagram of the serial port in Mode 1, and associated timings for transmit receive.

Transmission is initiated by any instruction that uses SBUF as a destination register. The "WRITE to SBUF" signal also loads a '1' into the 9th bit position of the transmit shift register and flags the TX Control unit that a transmission is requested. Transmission actually commences at S1P1 of the machine cycle following the next rollover in the divide-by-16 counter. (Thus, the bit times are synchronized to the divide-by-16 counter, not to the "WRITE to SBUF" signal.)

The transmission begins with activation of SEND which puts the start bit at TxD. One bit time later, DATA is activated, which enables the output bit of the transmit shift register to TxD. The first shift pulse occurs one bit time after that.

Figure 32. Serial port Mode 3 block diagram

# 13 Analog-to-digital convertor (ADC)

The analog to digital (A/D) converter allows conversion of an analog input to a corresponding 8-bit digital value. The A/D module has four analog inputs, which are multiplexed into one sample and hold. The output of the sample and hold is the input into the converter, which generates the result via successive approximation. The analog supply voltage is connected to  $AV_{\mathsf{BFF}}$  of ladder resistance of A/D module.

The A/D module has two registers which are the control register ACON and A/D result register ADAT. The register ACON, shown in *Table 47*, controls the operation of the A/D converter module. To use analog inputs, I/O is selected by P1SFS register. Also an 8-bit prescaler ASCL divides the main system clock input down to approximately 6MHz clock that is required for the ADC logic. Appropriate values need to be loaded into the prescaler based upon the main MCU clock frequency prior to use.

The processing of conversion starts when the Start bit ADST is set to '1.' After one cycle, it is cleared by hardware. The register ADAT contains the results of the A/D conversion. When conversion is completed, the result is loaded into the ADAT the A/D Conversion Status bit ADSF is set to '1.'

The block diagram of the A/D module is shown in Figure *Figure 34*. The A/D Status bit ADSF is set automatically when A/D conversion is completed, cleared when A/D conversion is in process.

The ASCL should be loaded with a value that results in a clock rate of approximately 6MHz for the ADC using the following formula:

ADC clock input =  $(f_{OSC} / 2) / (Prescaler register value +1)$

Where  $f_{OSC}$  is the MCU clock input frequency.

The conversion time for the ADC can be calculated as follows:

ADC Conversion Time = 8 clock \* 8bits \* (ADC Clock) ~= 10.67usec (at 6MHz)

# 13.1 ADC interrupt

The ADSF Bit in the ACON register is set to '1' when the A/D conversion is complete. The status bit can be driven by the MCU, or it can be configured to generate a falling edge interrupt when the conversion is complete.

The ADSF Interrupt is enabled by setting the ADSFINT Bit in the PCON register. Once the bit is set, the external INT1 Interrupt is disabled and the ADSF Interrupt takes over as INT1. INT1 must be configured as if it is an edge interrupt input. The INP1 pin (p3.3) is available for general I/O functions, or Timer1 gate control.

### Table 61.Description of the UADR Bits

| Bit    | Symbol            | R/W | Function                                                                                                                               |

|--------|-------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------|

| 7      | USBEN             | R/W | USB Function Enable Bit.<br>When USBEN is clear, the USB module will not respond to<br>any tokens from host.<br>RESET clears this bit. |

| 6 to 0 | UADD6 to<br>UADD0 | R/W | Specify the USB address of the device.<br>RESET clears these bits.                                                                     |

### Table 62. USB interrupt enable register (UIEN: 0E9h)

| 7       | 6    | 5      | 4      | 3      | 2      | 1     | 0      |

|---------|------|--------|--------|--------|--------|-------|--------|

| SUSPNDI | RSTE | RSTFIE | TXD0IE | RXD0IE | TXD1IE | EOPIE | RESUMI |

### Table 63.Description of the UIEN bits

| Bit | Symbol  | R/W | Function                                                                      |  |  |  |

|-----|---------|-----|-------------------------------------------------------------------------------|--|--|--|

| 7   | SUSPNDI | R/W | Enable SUSPND Interrupt                                                       |  |  |  |

| 6   | RSTE    | R/W | Enable USB Reset; also resets the CPU and PSD modules when bit is set to '1.' |  |  |  |

| 5   | RSTFIE  | R/W | Enable RSTF (USB Bus Reset Flag) Interrupt                                    |  |  |  |

| 4   | TXD0IE  | R/W | Enable TXD0 Interrupt                                                         |  |  |  |

| 3   | RXD0IE  | R/W | Enable RXD0 Interrupt                                                         |  |  |  |

| 2   | TXD1IE  | R/W | Enable TXD1 Interrupt                                                         |  |  |  |

| 1   | EOPIE   | R/W | Enable EOP Interrupt                                                          |  |  |  |

| 0   | RESUMI  | R/W | Enable USB Resume Interrupt when it is the Suspend mode                       |  |  |  |

### Table 64. USB interrupt status register (UISTA: 0E8h)

| 7      | 6 | 5    | 4     | 3     | 2     | 1    | 0      |

|--------|---|------|-------|-------|-------|------|--------|

| SUSPND | _ | RSTF | TXD0F | RXD0F | TXD1F | EOPF | RESUMF |

### Table 65.Description of the UISTA bits

| Bit | Symbol | R/W | Function                                                                                                                                                                                                                                                                                                                                      |  |  |  |

|-----|--------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 7   | SUSPND | R/W | USB Suspend Mode Flag.<br>To save power, this bit should be set if a 3ms constant idle<br>state is detected on USB bus. Setting this bit stops the clock to<br>the USB and causes the USB module to enter Suspend mode.<br>Software must clear this bit after the Resume flag (RESUMF)<br>is set while this Resume Interrupt Flag is serviced |  |  |  |

| 6   | —      |     | Reserved                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 5   | RSTF   | R   | USB Reset Flag.<br>This bit is set when a valid RESET signal state is detected on<br>the D+ and D- lines. When the RSTE bit in the UIEN Register<br>is set, this reset detection will also generate an internal reset<br>signal to reset the CPU and other peripherals including the<br>USB module.                                           |  |  |  |

| Bit    | Symbol                   | R/W | Function                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |

|--------|--------------------------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 7      | TSEQ0                    | R/W | Endpoint0 Data Sequence Bit. (0=DATA0, 1=DATA1)<br>This bit determines which type of data packet (DATA0 or<br>DATA1) will be sent during the next IN transaction. Toggling of<br>this bit must be controlled by software. RESET clears this bit                                                                                                                                                                                                  |  |  |

| 6      | STALLO                   | R/W | Endpoint0 Force Stall Bit.<br>This bit causes Endpoint 0 to return a STALL handshake when<br>polled by either an IN or OUT token by the USB Host<br>Controller. The USB hardware clears this bit when a SETUP<br>token is received. RESET clears this bit.                                                                                                                                                                                       |  |  |

| 5      | TX0E                     | R/W | Endpoint0 Transmit Enable.<br>This bit enables a transmit to occur when the USB Host<br>Controller sends an IN token to Endpoint 0. Software should<br>set this bit when data is ready to be transmitted. It must be<br>cleared by software when no more Endpoint 0 data needs to<br>be transmitted. If this bit is '0' or the TXD0F is set, the USB will<br>respond with a NAK handshake to any Endpoint 0 IN tokens.<br>RESET clears this bit. |  |  |

| 4      | RX0E                     | R/W | Endpoint0 receive enable.<br>This bit enables a receive to occur when the USB Host<br>Controller sends an OUT token to Endpoint 0. Software should<br>set this bit when data is ready to be received. It must be<br>cleared by software when data cannot be received. If this bit is<br>'0' or the RXD0F is set, the USB will respond with a NAK<br>handshake to any Endpoint 0 OUT tokens. RESET clears this<br>bit.                            |  |  |

| 3 to 0 | TP0SIZ3<br>to<br>TP0SIZ0 | R/W | The number of transmit data bytes. These bits are cleared by RESET.                                                                                                                                                                                                                                                                                                                                                                              |  |  |

Table 67.

Description of the UCON0 bits

| Table 68. U | ISB Endpoint1 | (and 2 | ) transmit control | register | (UCON1: 0EBh) |

|-------------|---------------|--------|--------------------|----------|---------------|

|-------------|---------------|--------|--------------------|----------|---------------|

| 7     | 6       | 5    | 4      | 3       | 2       | 1       | 0       |

|-------|---------|------|--------|---------|---------|---------|---------|

| TSEQ1 | EP12SEL | TX1E | FRESUM | TP1SIZ3 | TP1SIZ2 | TP1SIZ1 | TP1SIZ0 |

possibility of a byte being written on the first edge of WRITE Strobe ( $\overline{WR}$ , CNTL0). Any WRITE cycle initiation is locked when V<sub>CC</sub> is below V<sub>LKO</sub>.

### 21.5 Read

Under typical conditions, the MCU may read the primary Flash memory or the secondary Flash memory using READ operations just as it would a ROM or RAM device. Alternately, the MCU may use READ operations to obtain status information about a Program or Erase cycle that is currently in progress. Lastly, the MCU may use instructions to read special data from these memory blocks. The following sections describe these READ functions.

### 21.5.1 Read memory contents

Primary Flash memory and secondary Flash memory are placed in the READ mode after Power-up, chip reset, or a Reset Flash instruction (see *Table 82*). The MCU can read the memory contents of the primary Flash memory or the secondary Flash memory by using READ operations any time the READ operation is not part of an instruction.

### 21.5.2 Read memory sector protection status

The primary Flash memory Sector Protection Status is read with an instruction composed of 4 operations: 3 specific WRITE operations and a READ operation (see *Table 82*). During the READ operation, address Bits A6, A1, and A0 must be '0,' '1,' and '0,' respectively, while Sector Select (FS0-FS3 or CSBOOT0-CSBOOT1) designates the Flash memory sector whose protection has to be verified. The READ operation produces 01h if the Flash memory sector is protected, or 00h if the sector is not protected.

The sector protection status for all NVM blocks (primary Flash memory or secondary Flash memory) can also be read by the MCU accessing the Flash Protection registers in PSD I/O space. See *Section 21.8.1: Flash memory sector protect* for register definitions.

### 21.5.3 Reading the Erase/Program status bits

The Flash memory provides several status bits to be used by the MCU to confirm the completion of an Erase or Program cycle of Flash memory. These status bits minimize the time that the MCU spends performing these tasks and are defined in *Table 83*. The status bits can be read as many times as needed.

For Flash memory, the MCU can perform a READ operation to obtain these status bits while an Erase or Program instruction is being executed by the embedded algorithm. See *Section 21.6: Programming Flash memory*, for details.

### 21.5.4 Data polling flag (DQ7)

When erasing or programming in Flash memory, the Data Polling flag bit (DQ7) outputs the complement of the bit being entered for programming/writing on the DQ7 Bit. Once the

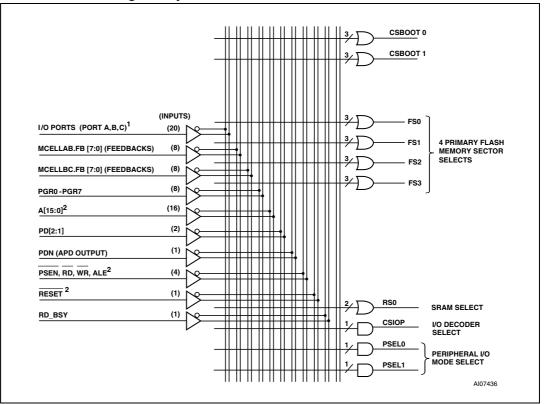

Table 88.DPLD logic array

- 1. Port A inputs are not available in the 52-pin package

- 2. Inputs from the MCU module

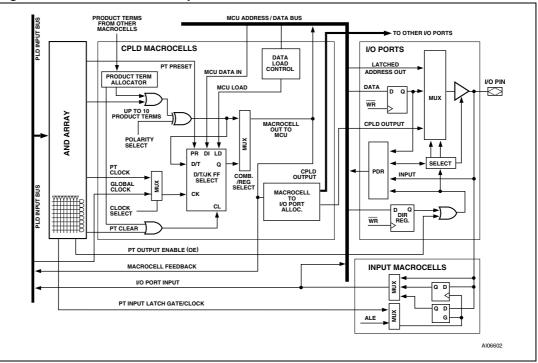

# 22.3 Complex PLD (CPLD)

The CPLD can be used to implement system logic functions, such as loadable counters and shift registers, system mailboxes, handshaking protocols, state machines, and random logic. The CPLD can also be used to generate External Chip Select (ECS1-ECS2), routed to Port D.

Although External Chip Select (ECS1-ECS2) can be produced by any Output Macrocell (OMC), these External Chip Select (ECS1-ECS2) on Port D do not consume any Output Macrocells (OMC).

As shown in *Figure 54*, the CPLD has the following blocks:

- 20 Input Macrocells (IMC)

- 16 Output Macrocells (OMC)

- Macrocell Allocator

- Product Term Allocator

- AND Array capable of generating up to 137 product terms

- Four I/O Ports.

Each of the blocks are described in the sections that follow.

The Input Macrocells (IMC) and Output Macrocells (OMC) are connected to the PSD module internal data bus and can be directly accessed by the MCU. This enables the MCU software to load data into the Output Macrocells (OMC) or read data from both the Input and Output Macrocells (IMC and OMC).

This feature allows efficient implementation of system logic and eliminates the need to connect the data bus to the AND Array as required in most standard PLD macrocell architectures.

Figure 54. Macrocell and I/O ports

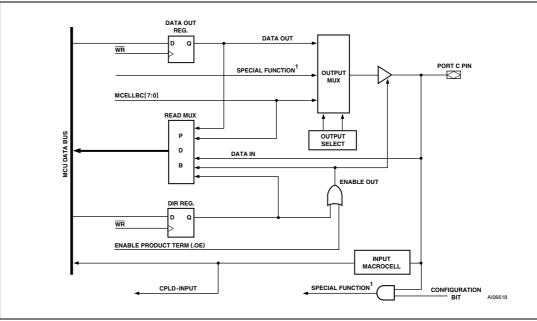

# 22.4 Output macrocell (OMC)

Eight of the Output Macrocells (OMC) are connected to Ports A and B pins and are named as McellAB0-McellAB7. The other eight macrocells are connected to Ports B and C pins and are named as McellBC0-McellBC7. If an McellAB output is not assigned to a specific pin in PSDsoft, the Macrocell Allocator block assigns it to either Port A or B. The same is true for a McellBC output on Port B or C. *Table 89* shows the macrocells and port assignment.

The Output Macrocell (OMC) architecture is shown in *Figure 55*. As shown in the figure, there are native product terms available from the AND Array, and borrowed product terms available (if unused) from other Output Macrocells (OMC). The polarity of the product term is controlled by the XOR gate. The Output Macrocell (OMC) can implement either sequential logic, using the flip-flop element, or combinatorial logic. The multiplexer selects between the sequential or combinatorial logic outputs. The multiplexer output can drive a port pin and has a feedback path to the AND Array inputs.

The flip-flop in the Output Macrocell (OMC) block can be configured as a D, T, JK, or SR type in PSDsoft. The flip-flop's clock, preset, and clear inputs may be driven from a product term of the AND Array. Alternatively, CLKIN (PD1) can be used for the clock input to the flip-

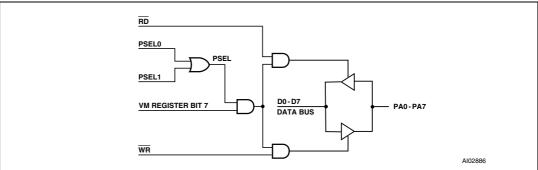

### Figure 58. Peripheral I/O mode

### Table 90. Port operating modes

| Port mode                     | Port A <sup>(1)</sup> | Port B       | Port C             | Port D |

|-------------------------------|-----------------------|--------------|--------------------|--------|

| MCU I/O                       | Yes                   | Yes          | Yes                | Yes    |

| PLD I/O                       |                       |              |                    |        |

| McellAB Outputs               | Yes                   | Yes          | No                 | No     |

| McellBC Outputs               | No                    | Yes          | Yes <sup>(2)</sup> | No     |

| Additional Ext. CS<br>Outputs | No                    | No           | No                 | Yes    |

| PLD Inputs                    | Yes                   | Yes          | Yes                | Yes    |

| Address Out                   | Yes (A7 – 0)          | Yes (A7 – 0) | No                 | No     |

| Peripheral I/O                | Yes                   | No           | No                 | No     |

| JTAG ISP                      | No                    | No           | Yes <sup>(3)</sup> | No     |

1. Port A is not available in the 52-pin package.

2. On pins PC2, PC3, PC4, and PC7 only.

3. JTAG pins (TMS, TCK, TDI, TDO) are dedicated pins.

#### Table 91. Port operating mode settings

| Mode                       | Defined in PSDsoft             | Control<br>Register<br>Setting <sup>(1)</sup> | Direction<br>Register<br>Setting <sup>(1)</sup> | VM Register<br>Setting <sup>(1)</sup> |

|----------------------------|--------------------------------|-----------------------------------------------|-------------------------------------------------|---------------------------------------|

| MCU I/O                    | Declare pins only              | 0                                             | 1 = output,<br>0 = input (Note 2)               | N/A                                   |

| PLD I/O                    | Logic equations                | N/A                                           | (Note 2)                                        | N/A                                   |

| Address Out<br>(Port A,B)  | Declare pins only              | 1                                             | 1 (Note 2)                                      | N/A                                   |

| Peripheral I/O<br>(Port A) | Logic equations<br>(PSEL0 & 1) | N/A                                           | N/A                                             | PIO Bit = 1                           |

1. N/A = Not Applicable

2. The direction of the Port A,B,C, and D pins are controlled by the Direction Register ORed with the individual output enable product term (.oe) from the CPLD AND Array.

Table 92. I/O port latched address output assignments

| Port A (PA3-PA0) | Port A (PA7-PA4) | Port B (PB3-PB0) | Port B (PB7-PB4) |

|------------------|------------------|------------------|------------------|

| Address a3-a0    | Address a7-a4    | Address a3-a0    | Address a7-a4    |

| Register Name               | Port    | MCU Access |  |

|-----------------------------|---------|------------|--|

| Control                     | A,B     | WRITE/READ |  |

| Direction                   | A,B,C,D | WRITE/READ |  |

| Drive Select <sup>(1)</sup> | A,B,C,D | WRITE/READ |  |

#### Table 93. Port configuration registers (PCR)

Note: 1. See Table 97 for Drive Register Bit definition.

#### Table 94. Port pin direction control, output enable P.T. not defined

| Direction Register Bit | Port Pin mode |

|------------------------|---------------|

| 0                      | Input         |

| 1                      | Output        |

### Table 95. Port pin direction control, output enable P.T. defined

| Direction Register Bit | Output Enable P.T. | Port Pin mode |

|------------------------|--------------------|---------------|

| 0                      | 0                  | Input         |

| 0                      | 1                  | Output        |

| 1                      | 0                  | Output        |

| 1                      | 1                  | Output        |

### Table 96. Port direction assignment example

| Bit | 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-----|---|-------|-------|-------|-------|-------|-------|-------|

| 0   |   | 0     | 0     | 0     | 0     | 1     | 1     | 1     |

### 23.9 Port data registers

The Port Data Registers, shown in *Table 98*, are used by the MCU to write data to or read data from the ports. *Table 98* shows the register name, the ports having each register type, and MCU access for each register type. The registers are described below.

### 23.9.1 Data In

Port pins are connected directly to the Data In buffer. In MCU I/O Input mode, the pin input is read through the Data In buffer.

### 23.9.2 Data Out register

Stores output data written by the MCU in the MCU I/O Output mode. The contents of the Register are driven out to the pins if the Direction Register or the output enable product term is set to '1.' The contents of the register can also be read back by the MCU.

### 23.9.3 Output macrocells (OMC)

The CPLD Output Macrocells (OMC) occupy a location in the MCU's address space. The MCU can read the output of the Output Macrocells (OMC). If the OMC Mask Register Bits

Note: 1. ISP

# **23.12 Port D – functionality and structure**

Port D has two I/O pins (only one pin, PD1, in the 52-pin package). See *Figure 61* and *Figure 62*. This port does not support Address Out mode, and therefore no Control Register is required. Of the eight bits in the Port D registers, only Bits 2 and 1 are used to configure pins PD2 and PD1.

Port D can be configured to perform one or more of the following functions:

- MCU I/O mode

- CPLD Output External Chip Select (ECS1-ECS2)

- CPLD Input direct input to the CPLD, no Input Macrocells (IMC)

- Slew rate pins can be set up for fast slew rate

Port D pins can be configured in PSDsoft Express as input pins for other dedicated functions:

- CLKIN (PD1) as input to the macrocells flip-flops and APD counter

- PSD Chip Select Input (CSI, PD2). Driving this signal High disables the Flash memory, SRAM and CSIOP.

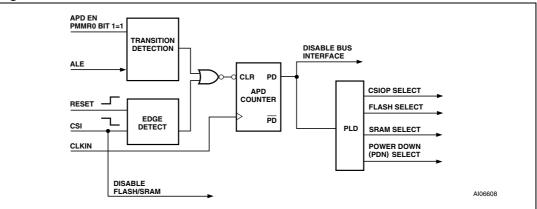

#### Figure 63. APD unit

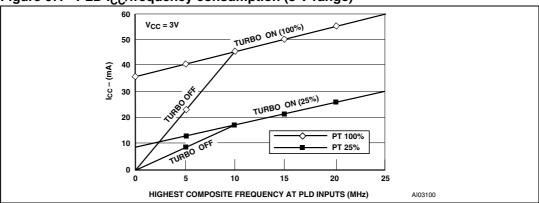

The PSD module has a Turbo Bit in PMMR0. This bit can be set to turn the Turbo mode off (the default is with Turbo mode turned on). While Turbo mode is off, the PLDs can achieve standby current when no PLD inputs are changing (zero DC current). Even when inputs do change, significant power can be saved at lower frequencies (AC current), compared to when Turbo mode is on. When the Turbo mode is on, there is a significant DC current component and the AC component is higher.

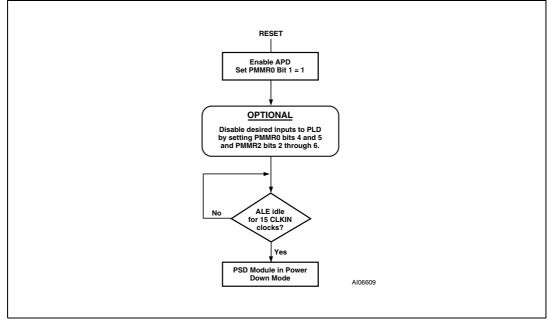

### Automatic Power-down (APD) Unit and Power-down mode

The APD Unit, shown in *Figure 63*, puts the PSD module into Power-down mode by monitoring the activity of Address Strobe (ALE). If the APD Unit is enabled, as soon as activity on Address Strobe (ALE) stops, a four-bit counter starts counting. If Address Strobe (ALE/AS, PD0) remains inactive for fifteen clock periods of CLKIN (PD1), Power-down (PDN) goes High, and the PSD module enters Power-down mode, as discussed next.

#### Power-down mode

By default, if you enable the APD Unit, Power-down mode is automatically enabled. The device enters Power-down mode if Address Strobe (ALE) remains inactive for fifteen periods of CLKIN (PD1).

The following should be kept in mind when the PSD module is in Power-down mode:

- If Address Strobe (ALE) starts pulsing again, the PSD module returns to normal Operating mode. The PSD module also returns to normal Operating mode if either PSD Chip Select Input (CSI, PD2) is Low or the RESET input is High.

- The MCU address/data bus is blocked from all memory and PLDs.

- Various signals can be blocked (prior to Power-down mode) from entering the PLDs by setting the appropriate bits in the PMMR registers. The blocked signals include MCU control signals and the common CLKIN (PD1).

Note:

- Blocking CLKIN (PD1) from the PLDs does not block CLKIN (PD1) from the APD Unit.

- All memories enter Standby mode and are drawing standby current. However, the PLD and I/O ports blocks do *not* go into Standby mode because you don't want to have to wait for the logic and I/O to "wake-up" before their outputs can change. See *Table 99* for Power-down mode effects on PSD module ports.

- Typical standby current is of the order of microamperes. These standby current values assume that there are no transitions on any PLD input.

### Other power-saving options

The PSD module offers other reduced power saving options that are independent of the Power-down mode. Except for the PSD Chip Select Input ( $\overline{CSI}$ , PD2) features, they are enabled by setting bits in PMMR0 and PMMR2.

#### Table 99. Power-down mode's effect on ports

| Port Function  | Pin Level |

|----------------|-----------|

| MCU I/O        | No Change |

| PLD Out        | No Change |

| Address Out    | Undefined |

| Peripheral I/O | Tri-State |

### 24.1 PLD power management

The power and speed of the PLDs are controlled by the Turbo Bit (Bit 3) in PMMR0. By setting the bit to '1,' the Turbo mode is off and the PLDs consume the specified Standby current when the inputs are not switching for an extended time of 70 ns. The propagation delay time is increased by 10 ns (for a 5 V device) after the Turbo Bit is set to '1' (turned off) when the inputs change at a composite frequency of less than 15MHz. When the Turbo Bit is reset to '0' (turned on), the PLDs run at full power and speed. The Turbo Bit affects the PLD's DC power, AC power, and propagation delay. When the Turbo mode is off, the UPSD321xx devices' input clock frequency is reduced by 5 MHz from the maximum rated clock frequency.

Blocking MCU control signals with the bits of PMMR2 can further reduce PLD AC power consumption.

# Table 105. PSD module example, typ. power calculation at $V_{CC}$ = 5.0 V (Turbo mode off)

|               | Conditions                |                                       |  |  |  |  |  |

|---------------|---------------------------|---------------------------------------|--|--|--|--|--|

|               | MCU clock frequency       | = 12 MHz                              |  |  |  |  |  |

| Highest Comp  | osite PLD input frequency |                                       |  |  |  |  |  |

|               | (Freq PLD)                | = 8 MHz                               |  |  |  |  |  |

| MCU ALE free  | quency (Freq ALE)         | = 2 MHz                               |  |  |  |  |  |

|               | % Flash memory access     | = 80%                                 |  |  |  |  |  |

|               | % SRAM access             | = 15%                                 |  |  |  |  |  |

|               | % I/O access              | = 5% (no additional power above base) |  |  |  |  |  |

| Operational m | lodes                     |                                       |  |  |  |  |  |

|               | % Normal                  | = 40%                                 |  |  |  |  |  |

|               | % Power-down mode         | = 60%                                 |  |  |  |  |  |

| Number of pro | oduct terms used          |                                       |  |  |  |  |  |

|               | (from fitter report)      | = 45 PT                               |  |  |  |  |  |

|               | % of total product terms  | = 45/182 = 24.7%                      |  |  |  |  |  |

|               | Turbo mode                | = Off                                 |  |  |  |  |  |

| Symbol           | Parameter                                                                                 | Test conditions (in<br>addition to those in<br><i>Table 111</i> )                                         | Min.                  | Тур. | Max.                     | Unit   |

|------------------|-------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------|------|--------------------------|--------|

| V <sub>IH</sub>  | Input high voltage (Ports 1,<br>2, 3, 4[Bits 7,6,5,4,3,1,0], A,<br>B, C, D, XTAL1, RESET) | 3.0 V < V <sub>CC</sub> < 3.6 V                                                                           | 0.7V <sub>CC</sub>    |      | V <sub>CC</sub> + 0.5    | V      |

| V <sub>IH1</sub> | Input high voltage (Port<br>4[Bit 2])                                                     | 3.0 V < V <sub>CC</sub> < 3.6 V                                                                           | 2.0                   |      | V <sub>CC</sub> +<br>0.5 | V      |

| V <sub>IL</sub>  | Input high voltage (Ports 1,<br>2, 3, 4[Bits 7,6,5,4,3,1,0],<br>XTAL1, RESET)             | 3.0 V < V <sub>CC</sub> < 3.6 V                                                                           | V <sub>SS</sub> - 0.5 |      | 0.3<br>V <sub>CC</sub>   | V      |

| V <sub>IL1</sub> | Input low voltage<br>(Ports A, B, C, D)                                                   | 3.0 V < V <sub>CC</sub> < 3.6 V                                                                           | -0.5                  |      | 0.8                      | V      |

| ♥IL1             | Input low voltage<br>(Port 4[Bit 2])                                                      | 3.0 V < V <sub>CC</sub> < 3.6 V                                                                           | V <sub>SS</sub> - 0.5 |      | 0.8                      | V      |

| V <sub>OL</sub>  | Output low voltage                                                                        | I <sub>OL</sub> = 20 μA<br>V <sub>CC</sub> = 3.0 V                                                        |                       | 0.01 | 0.1                      | V      |

| ۰OL              | (Ports A,B,C,D)                                                                           | I <sub>OL</sub> = 4 mA<br>V <sub>CC</sub> = 3.0 V                                                         |                       | 0.15 | 0.45                     | V      |

| V <sub>OL1</sub> | Output low voltage                                                                        | I <sub>OL</sub> = 1.6 mA                                                                                  |                       |      | 0.45                     | V      |

| ULI              | (Ports 1,2,3,4, WR, RD)                                                                   | I <sub>OL</sub> = 100 μA                                                                                  |                       |      | 0.3                      | V      |

| V <sub>OL2</sub> | Output low voltage<br>(Port 0, ALE, PSEN)                                                 | $I_{OL} = 3.2 \text{ mA}$                                                                                 |                       |      | 0.45                     | V      |

|                  | Output high voltage                                                                       | $I_{OL} = 200 \ \mu A$<br>$I_{OH} = -20 \ \mu A$<br>$V_{CC} = 3.0 \ V$                                    | 2.9                   | 2.99 | 0.3                      | V<br>V |

| V <sub>OH</sub>  | (Ports A,B,C,D)                                                                           | I <sub>OH</sub> = -1 mA<br>V <sub>CC</sub> = 3.0 V                                                        | 2.4                   | 2.6  |                          | V      |

|                  | Output high voltage (Port 0                                                               | I <sub>OH</sub> = -800 μA                                                                                 | 2.0                   |      |                          | V      |

| V <sub>OH2</sub> | in ext. Bus mode, ALE,<br>PSEN)                                                           | I <sub>OH</sub> = -80 μA                                                                                  | 2.7                   |      |                          | V      |

| $V_{LVR}$        | Low voltage reset                                                                         | 0.1 V hysteresis                                                                                          | 2.3                   | 2.5  | 2.7                      | V      |

| V <sub>OP</sub>  | XTAL open bias voltage<br>(XTAL1, XTAL2)                                                  | I <sub>OL</sub> = 3.2 mA                                                                                  | 1.0                   |      | 2.0                      | V      |

| V <sub>LKO</sub> | V <sub>CC</sub> (min) for Flash Erase<br>and Program                                      |                                                                                                           | 1.5                   |      | 2.2                      | V      |

| IIL              | Logic '0' input current<br>(Ports 1,2,3,4)                                                | V <sub>IN</sub> = 0.45 V<br>(0 V for Port 4[pin 2])                                                       | -1                    |      | -50                      | μA     |

| I <sub>TL</sub>  | Logic 1-to-0 transition<br>current (Ports 1,2,3,4)                                        | V <sub>IN</sub> = 3.5 V<br>(2.5 V for Port 4[pin 2])                                                      | -25                   |      | -250                     | μA     |

| I <sub>RST</sub> | Reset pin pull-up current (RESET)                                                         | $V_{IN} = V_{SS}$                                                                                         | -10                   |      | -55                      | μA     |

| I <sub>FR</sub>  | XTAL feedback resistor<br>current (XTAL1)                                                 | $\begin{array}{l} \text{XTAL1} = \text{V}_{\text{CC}} \\ \text{XTAL2} = \text{V}_{\text{SS}} \end{array}$ | -20                   |      | -50                      | μA     |

| I <sub>LI</sub>  | Input leakage current                                                                     | $V_{SS} < V_{IN} < V_{CC}$                                                                                | -1                    |      | 1                        | μA     |

| I <sub>LO</sub>  | Output leakage current                                                                    | 0.45 < V <sub>OUT</sub> < V <sub>CC</sub>                                                                 | -10                   |      | 10                       | μA     |

Table 116. DC characteristics (3 V devices)

| Symbol              | Parameter                                   | Conditions | Min. | Max. | Unit |

|---------------------|---------------------------------------------|------------|------|------|------|

| t <sub>ISCCF</sub>  | Clock (TCK, PC1) frequency (except for PLD) | (Note 1)   |      | 20   | MHz  |

| t <sub>ISCCH</sub>  | Clock (TCK, PC1) high time (except for PLD) | (Note 1)   | 23   |      | ns   |

| t <sub>ISCCL</sub>  | Clock (TCK, PC1) low time (except for PLD)  | (Note 1)   | 23   |      | ns   |

| t <sub>ISCCFP</sub> | Clock (TCK, PC1) frequency (PLD only)       | (Note 2)   |      | 2    | MHz  |

| t <sub>ISCCHP</sub> | Clock (TCK, PC1) high time (PLD only)       | (Note 2)   | 240  |      | ns   |

| t <sub>ISCCLP</sub> | Clock (TCK, PC1) low time (PLD only)        | (Note 2)   | 240  |      | ns   |

| t <sub>ISCPSU</sub> | ISC port set-up time                        |            | 7    |      | ns   |

| t <sub>ISCPH</sub>  | ISC port hold-up time                       |            | 5    |      | ns   |

| t <sub>ISCPCO</sub> | ISC port clock to output                    |            |      | 21   | ns   |

| t <sub>ISCPZV</sub> | ISC port high-impedance to valid output     |            |      | 21   | ns   |

| t <sub>ISCPVZ</sub> | ISC port valid output to high-impedance     |            |      | 21   | ns   |

Table 140. ISC timing (5 V devices)

1. For non-PLD Programming, Erase or in ISC By-pass mode.

2. For Program or Erase PLD only.

### Table 141. ISC timing (3 V devices)

| Symbol              | Parameter                                   | Conditions | Min. | Max. | Unit |

|---------------------|---------------------------------------------|------------|------|------|------|

| t <sub>ISCCF</sub>  | Clock (TCK, PC1) frequency (except for PLD) | (Note 1)   |      | 12   | MHz  |

| t <sub>ISCCH</sub>  | Clock (TCK, PC1) high time (except for PLD) | (Note 1)   | 40   |      | ns   |

| t <sub>ISCCL</sub>  | Clock (TCK, PC1) low time (except for PLD)  | (Note 1)   | 40   |      | ns   |

| t <sub>ISCCFP</sub> | Clock (TCK, PC1) frequency (PLD only)       | (Note 2)   |      | 2    | MHz  |

| t <sub>ISCCHP</sub> | Clock (TCK, PC1) high time (PLD only)       | (Note 2)   | 240  |      | ns   |

| t <sub>ISCCLP</sub> | Clock (TCK, PC1) low time (PLD only)        | (Note 2)   | 240  |      | ns   |

| t <sub>ISCPSU</sub> | ISC port set-up time                        |            | 12   |      | ns   |

| t <sub>ISCPH</sub>  | ISC port hold-up time                       |            | 5    |      | ns   |

| t <sub>ISCPCO</sub> | ISC port clock to output                    |            |      | 30   | ns   |

| t <sub>ISCPZV</sub> | ISC port high-impedance to valid output     |            |      | 30   | ns   |

| t <sub>ISCPVZ</sub> | ISC port valid output to high-impedance     |            |      | 30   | ns   |

1. For non-PLD Programming, Erase or in ISC By-pass mode.

2. For Program or Erase PLD only.

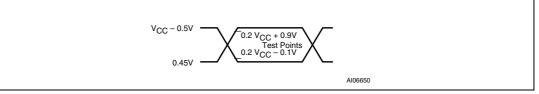

#### Figure 81. MCU module AC measurement I/O waveform

- 1. AC inputs during testing are driven at V\_{CC}\!-\!0.5 V for a logic '1,' and 0.45 V for a logic '0.'

- 2. Timing measurements are made at  $V_{IH}(\mbox{min})$  for a logic '1,' and  $V_{IL}(\mbox{max})$  for a logic '0'.