Welcome to E-XFL.COM

#### Understanding <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Embedded - DSP (Digital Signal Processors) are specialized microprocessors designed to perform complex mathematical computations on digital signals in real-time. Unlike general-purpose processors, DSPs are optimized for high-speed numeric processing tasks, making them ideal for applications that require efficient and precise manipulation of digital data. These processors are fundamental in converting and processing signals in various forms, including audio, video, and communication signals, ensuring that data is accurately interpreted and utilized in embedded systems.

#### Applications of <u>Embedded - DSP (Digital</u> <u>Signal Processors)</u>

#### Details

E·XFl

| Betans                  |                                                                        |

|-------------------------|------------------------------------------------------------------------|

| Product Status          | Active                                                                 |

| Туре                    | Floating Point                                                         |

| Interface               | DAI, SPI                                                               |

| Clock Rate              | 200MHz                                                                 |

| Non-Volatile Memory     | ROM (512kB)                                                            |

| On-Chip RAM             | 256kB                                                                  |

| Voltage - I/O           | 3.30V                                                                  |

| Voltage - Core          | 1.20V                                                                  |

| Operating Temperature   | 0°C ~ 70°C (TA)                                                        |

| Mounting Type           | Surface Mount                                                          |

| Package / Case          | 136-LFBGA, CSPBGA                                                      |

| Supplier Device Package | 136-CSPBGA (12x12)                                                     |

| Purchase URL            | https://www.e-xfl.com/product-detail/analog-devices/adsp-21262skbcz200 |

|                         |                                                                        |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

## TABLE OF CONTENTS

| Summary 1                                     |

|-----------------------------------------------|

| General Description 3                         |

| Family Core Architecture 3                    |

| Memory and I/O Interface Features 4           |

| Target Board JTAG Emulator Connector 8        |

| Development Tools 8                           |

| Additional Information 9                      |

| Related Signal Chains 9                       |

| Pin Function Descriptions 10                  |

| Address Data Pins as Flags 13                 |

| Core Instruction Rate to CLKIN Ratio Modes 13 |

| Address Data Modes 13                         |

| Product Specifications 14                     |

| Operating Conditions 14                       |

| Electrical Characteristics 14                 |

| Package Information15                         |

# ESD Caution15Maximum Power Dissipation15Absolute Maximum Ratings15Timing Specifications15Output Drive Currents37Test Conditions37Capacitive Loading37Environmental Conditions38Thermal Characteristics38144-Lead LQFP Pin Configurations39136-Ball BGA Pin Configurations40Outline Dimensions43Surface-Mount Design44Automotive Products45Ordering Guide45

#### **REVISION HISTORY**

| 12/12—Rev. F to Rev. G                                                                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------|

| Corrected Long Word Memory Space in Table 4 in<br>Memory and I/O Interface Features4                                                             |

| Updated Development Tools                                                                                                                        |

| Added section, Related Signal Chains9                                                                                                            |

| Changed the package designator in Figure 36 from BC-136 to BC-136-1. This change in no way affects form, fit, or function See Outline Dimensions |

| Updated Ordering Guide                                                                                                                           |

## **GENERAL DESCRIPTION**

The ADSP-21261/ADSP-21262/ADSP-21266 SHARC<sup>®</sup> DSPs are members of the SIMD SHARC family of DSPs featuring Analog Devices, Inc., Super Harvard Architecture. The ADSP-2126x is source code compatible with the ADSP-21160 and ADSP-21161 DSPs as well as with first generation ADSP-2106x SHARC processors in SISD (single-instruction, singledata) mode. Like other SHARC DSPs, the ADSP-2126x are 32-bit/40-bit floating-point processors optimized for high performance audio applications with dual-ported on-chip SRAM, mask-programmable ROM, multiple internal buses to eliminate I/O bottlenecks, and an innovative digital application interface.

Table 1 shows performance benchmarks for the processors running at 200 MHz. Table 2 shows the features of the individual product offerings.

#### Table 1. Processor Benchmarks (at 200 MHz)

| Benchmark Algorithm                             | Speed<br>(at 200 MHz) |

|-------------------------------------------------|-----------------------|

| 1024 Point Complex FFT (Radix 4, with reversal) | 61.3 μs               |

| FIR Filter (per tap) <sup>1</sup>               | 3.3 ns                |

| IIR Filter (per biquad) <sup>1</sup>            | 13.3 ns               |

| Matrix Multiply (pipelined)                     |                       |

| [3×3] × [3×1]                                   | 30 ns                 |

| $[4\times4]\times[4\times1]$                    | 53.3 ns               |

| Divide (y/x)                                    | 20 ns                 |

| Inverse Square Root                             | 30 ns                 |

<sup>1</sup>Assumes two files in multichannel SIMD mode.

As shown in the functional block diagram in Figure 1 on Page 1, the ADSP-2126x uses two computational units to deliver a 5 to 10 times performance increase over previous SHARC processors on a range of DSP algorithms. Fabricated in a state-of-theart, high speed, CMOS process, the ADSP-2126x DSPs achieve an instruction cycle time of 5 ns at 200 MHz or 6.6 ns at 150 MHz. With its SIMD computational hardware, the ADSP-2126x can perform 1200 MFLOPS running at 200 MHz, or 900 MFLOPS running at 150 MHz.

Table 2. ADSP-2126x SHARC Processor Features

| Feature                               | ADSP-21261                    | ADSP-21262                    | ADSP-21266                    |

|---------------------------------------|-------------------------------|-------------------------------|-------------------------------|

| RAM                                   | 1M bit                        | 2M bit                        | 2M bit                        |

| ROM                                   | 3M bit                        | 4M bit                        | 4M bit                        |

| Audio Decoders<br>in ROM <sup>1</sup> | No                            | No                            | Yes                           |

| DMA Channels                          | 18                            | 22                            | 22                            |

| SPORTs                                | 4                             | 6                             | 6                             |

| Package                               | 136-ball BGA<br>144-lead LQFP | 136-ball BGA<br>144-lead LQFP | 136-ball BGA<br>144-lead LQFP |

<sup>1</sup> For information on available audio decoding algorithms, see Table 3 on Page 4.

The ADSP-2126x continues the SHARC family's industry-leading standards of integration for DSPs, combining a high performance 32-bit DSP core with integrated, on-chip system features. These features include 2M bit dual-ported SRAM memory, 4M bit dual-ported ROM, an I/O processor that supports 22 DMA channels, six serial ports, an SPI interface, external parallel bus, and digital application interface.

The block diagram of the ADSP-2126x on Page 1 illustrates the following architectural features:

- Two processing elements, each containing an ALU, multiplier, shifter, and data register file

- Data address generators (DAG1, DAG2)

- · Program sequencer with instruction cache

- PM and DM buses capable of supporting four 32-bit data transfers between memory and the core at every core processor cycle

- Three programmable interval timers with PWM generation, PWM capture/pulse width measurement, and external event counter capabilities

- On-chip dual-ported SRAM (up to 2M bit)

- On-chip dual-ported, mask-programmable ROM (up to 4M bit)

- JTAG test access port

- 8- or 16-bit parallel port that supports interfaces to off-chip memory peripherals

- DMA controller

- Six full-duplex serial ports (four on the ADSP-21261)

- SPI-compatible interface

- Digital application interface that includes two precision clock generators (PCG), an input data port (IDP), six serial ports, eight serial interfaces, a 20-bit synchronous parallel input port, 10 interrupts, six flag outputs, six flag inputs, three programmable timers, and a flexible signal routing unit (SRU)

#### FAMILY CORE ARCHITECTURE

The ADSP-2126x is code compatible at the assembly level with the ADSP-2136x and ADSP-2116x, and with the first generation ADSP-2106x SHARC DSPs. The ADSP-2126x shares architectural features with the ADSP-2136x and ADSP-2116x SIMD SHARC family of DSPs, as detailed in the following sections.

#### SIMD Computational Engine

The ADSP-2126x contain two computational processing elements that operate as a single-instruction multiple-data (SIMD) engine. The processing elements are referred to as PEX and PEY and each contains an ALU, multiplier, shifter, and register file. PEX is always active, and PEY can be enabled by setting the PEYEN mode bit in the MODE1 register. When this mode is enabled, the same instruction is executed in both processing

#### Table 5. Internal Memory Space (ADSP-21262/ADSP-21266)

| IOP Registers 0x0000 0000-00 | IOP Registers 0x0000 0000–0003 FFFF                        |                         |                         |  |  |  |  |

|------------------------------|------------------------------------------------------------|-------------------------|-------------------------|--|--|--|--|

| Long Word (64 Bits)          | Extended Precision Normal or<br>Instruction Word (48 Bits) | Normal Word (32 Bits)   | Short Word (16 Bits)    |  |  |  |  |

| Block 0 SRAM                 | Block 0 SRAM                                               | Block 0 SRAM            | Block 0 SRAM            |  |  |  |  |

| 0x0004 0000–0x0004 3FFF      | 0x0008 0000–0x0008 5555                                    | 0x0008 0000–0x0008 7FFF | 0x0010 0000–0x0010 FFFF |  |  |  |  |

| Reserved                     | Reserved                                                   | Reserved                | Reserved                |  |  |  |  |

| 0x0004 4000–0x0005 7FFF      |                                                            | 0x0008 8000–0x000A FFFF | 0x0011 0000–0x0015 FFFF |  |  |  |  |

| Block 0 ROM                  | Block 0 ROM                                                | Block 0 ROM             | Block 0 ROM             |  |  |  |  |

| 0x0005 8000–0x0005 FFFF      | 0x000A 0000–0x000A AAAA                                    | 0x000B 0000–0x000B FFFF | 0x0016 0000–0x0017 FFFF |  |  |  |  |

| Block 1 SRAM                 | Block 1 SRAM                                               | Block 1 SRAM            | Block 1 SRAM            |  |  |  |  |

| 0x0006 0000–0x0006 3FFF      | 0x000C 0000–0x000C 5555                                    | 0x000C 0000–0x000C 7FFF | 0x0018 0000–0x0018 FFFF |  |  |  |  |

| Reserved                     | Reserved                                                   | Reserved                | Reserved                |  |  |  |  |

| 0x0006 4000–0x0007 7FFF      |                                                            | 0x000C 8000–0x000E FFFF | 0x0019 0000–0x001D FFFF |  |  |  |  |

| Block 1 ROM                  | Block 1 ROM                                                | Block 1 ROM             | Block 1 ROM             |  |  |  |  |

| 0x0007 8000–0x0007 FFFF      | 0x000E 0000–0x000E AAAA                                    | 0x000F 0000–0x000F FFFF | 0x001E 0000–0x001F FFFF |  |  |  |  |

#### Digital Application Interface (DAI)

The Digital application interface provides the ability to connect various peripherals to any of the SHARC DSP's DAI pins (DAI\_P20-1).

Connections are made using the signal routing unit (SRU, shown in the block diagram on Page 1).

The SRU is a matrix routing unit (or group of multiplexers) that enables the peripherals provided by the DAI to be interconnected under software control. This allows easy use of the DAI associated peripherals for a much wider variety of applications by using a larger set of algorithms than is possible with nonconfigurable signal paths.

The DAI also includes six serial ports, two precision clock generators (PCGs), an input data port (IDP), six flag outputs and six flag inputs, and three timers. The IDP provides an additional input path to the ADSP-2126x core, configurable as either eight channels of I<sup>2</sup>S or serial data, or as seven channels plus a single 20-bit wide synchronous parallel data acquisition port. Each data channel has its own DMA channel that is independent from the ADSP-2126x's serial ports.

For complete information on using the DAI, see the *ADSP-2126x SHARC DSP Peripherals Manual*.

#### Serial Ports

The ADSP-2126x features six full duplex synchronous serial ports that provide an inexpensive interface to a wide variety of digital and mixed-signal peripheral devices such as the Analog Devices AD183x family of audio codecs, ADCs, and DACs. The serial ports are made up of two data lines, a clock, and frame sync. The data lines can be programmed to either transmit or receive and each data line has its own dedicated DMA channel.

Serial ports are enabled via 12 programmable and simultaneous receive or transmit pins that support up to 24 transmit or 24 receive channels of audio data when all six SPORTs are enabled, or six full duplex TDM streams of 128 channels per frame.

The serial ports operate at up to one-quarter of the DSP core clock rate, providing each with a maximum data rate of 50M bits/sec for a 200 MHz core and 37.5M bits/sec for a 150 MHz core. Serial port data can be automatically transferred to and from on-chip memory via a dedicated DMA. Each of the serial ports can work in conjunction with another serial port to provide TDM support. One SPORT provides two transmit signals while the other SPORT provides two receive signals. The frame sync and clock are shared.

Serial ports operate in four modes:

- Standard DSP serial mode

- Multichannel (TDM) mode

- I<sup>2</sup>S mode

- Left-justified sample pair mode

Left-justified sample pair mode is a mode where in each frame sync cycle, two samples of data are transmitted/received—one sample on the high segment of the frame sync, the other on the low segment of the frame sync. Programs have control over various attributes of this mode.

Each of the serial ports supports the left-justified sample-pair and I<sup>2</sup>S protocols (I<sup>2</sup>S is an industry-standard interface commonly used by audio codecs, ADCs, and DACs) with two data pins, allowing four left-justified sample-pair or I<sup>2</sup>S channels (using two stereo devices) per serial port with a maximum of up to 24 audio channels. The serial ports permit little-endian or big-endian transmission formats and word lengths selectable from 3 bits to 32 bits. For the left-justified sample pair and I<sup>2</sup>S modes, data-word lengths are selectable between 8 bits and 32 bits. Serial ports offer selectable synchronization and transmit modes as well as optional  $\mu$ -law or A-law companding selection on a per channel basis. Serial port clocks and frame syncs can be internally or externally generated.

## **PIN FUNCTION DESCRIPTIONS**

The ADSP-2126x pin definitions are listed below. Inputs identified as synchronous (S) must meet timing requirements with respect to CLKIN (or with respect to TCK for TMS, TDI). Inputs identified as asynchronous (A) can be asserted asynchronously to CLKIN (or to TCK for TRST). Tie or pull unused inputs to  $V_{DDEXT}$  or GND, except for the following: DAI\_Px, SPICLK, MISO, MOSI, EMU, TMS, TRST, TDI and AD15-0 (NOTE: These pins have internal pull-up resistors.)

The following symbols appear in the Type column of Table 6: A = asynchronous, G = ground, I = input, O = output, P = power supply, S = synchronous, (A/D) = active drive, (O/D) = open-drain, and T = three-state.

#### Table 6. Pin Descriptions

| Pin       | Туре  | State During and<br>After Reset                                                                            | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|-----------|-------|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AD15-0    | I/O/T | Rev. 0.1 silicon—<br>AD15–0 pins are<br>driven low both<br>during and after<br>reset.<br>Rev. 0.2 silicon— | <b>Parallel Port Address/Data.</b> The parallel port and its corresponding DMA unit output addresses and data for peripherals on these multiplexed pins. The multiplex state is determined by the ALE pin. The parallel port can operate in either 8-bit or 16-bit mode. Each AD pin has a 22.5 k $\Omega$ internal pull-up resistor. See Address Data Modes on Page 13 for details of the AD pin operation.<br>For 8-bit mode: ALE is automatically asserted whenever a change occurs in the upper 16                                                                                                                                                                                                                             |

|           |       | AD15–0 pins are<br>three-stated and<br>pulled high both                                                    | external address bits, A23–8; ALE is used in conjunction with an external latch to retain<br>the values of the A23–8.<br>For 16-bit mode: ALE is automatically asserted whenever a change occurs in the address                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|           |       | during and after<br>reset.                                                                                 | bits, A15–0; ALE is used in conjunction with an external latch to retain the values of the A15–0. To use these pins as flags (FLAG15–0), set (= 1) Bit 20 of the SYSCTL register and disable the parallel port. See Table 7 on Page 13 for a list of how the AD15–0 pins map to the flag pins. When configured in the IDP_PDAP_CTL register, the IDP Channel 0 can use these pins for parallel input data.                                                                                                                                                                                                                                                                                                                         |

| RD        | 0     | Output only, driven high <sup>1</sup>                                                                      | <b>Parallel Port Read Enable.</b> RD is asserted low whenever the DSP reads 8-bit or 16-bit data from an external memory device. When AD15–0 are flags, this pin remains deasserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| WR        | 0     | Output only, driven high <sup>1</sup>                                                                      | <b>Parallel Port Write Enable.</b> WR is asserted low whenever the DSP writes 8-bit or 16-bit data to an external memory device. When AD15–0 are flags, this pin remains deasserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| ALE       | 0     | Output only, driven<br>Iow <sup>1</sup>                                                                    | <b>Parallel Port Address Latch Enable.</b> ALE is asserted whenever the DSP drives a new address on the parallel port address pin. On reset, ALE is active high. However, it can be reconfigured using software to be active low. When AD15–0 are flags, this pin remains deasserted.                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| FLAG3-0   | I/O/A | Three-state                                                                                                | <b>Flag Pins.</b> Each FLAG pin is configured via control bits as either an input or output. As an input, it can be tested as a condition. As an output, it can be used to signal external peripherals. These pins can be used as an SPI interface slave select output during SPI mastering. These pins are also multiplexed with the IRQx and the TIMEXP signals. In SPI master boot mode, FLAG0 is the slave select pin that must be connected to an SPI                                                                                                                                                                                                                                                                         |

|           |       |                                                                                                            | EPROM. FLAG0 is configured as a slave select during SPI master boot. When Bit 16 is set (= 1) in the SYSCTL register, FLAG0 is configured as IRQ0.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|           |       |                                                                                                            | When Bit 17 is set (= 1) in the SYSCTL register, FLAG1 is configured as $\overline{IRQ1}$ .<br>When Bit 18 is set (= 1) in the SYSCTL register, FLAG2 is configured as $\overline{IRQ2}$ .<br>When Bit 19 is set (= 1) in the SYSCTL register, FLAG3 is configured as TIMEXP, which<br>indicates that the system timer has expired.                                                                                                                                                                                                                                                                                                                                                                                                |

| DAI_P20-1 | I/O/T | Three-state with<br>programmable<br>pull-up                                                                | <b>Digital Application Interface Pins</b> . These pins provide the physical interface to the SRU. The SRU configuration registers define the combination of on-chip peripheral inputs or outputs connected to the pin and to the pin's output enable. The configuration registers of these peripherals then determine the exact behavior of the pin. Any input or output signal present in the SRU can be routed to any of these pins. The SRU provides the connection from the serial ports, input data port, precision clock generators, and timers to the DAI_P20-1 pins. These pins have internal 22.5 k $\Omega$ pull-up resistors which are enabled on reset. These pull-ups can be disabled in the DAI_PIN_PULLUP register. |

#### Table 6. Pin Descriptions (Continued)

| Pin                | Туре    | State During and<br>After Reset  | Function                                                                                                                                                                                                                                                                                   |

|--------------------|---------|----------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLK_CFG1-0         | 1       | Input only                       | <b>Core/CLKIN Ratio Control</b> . These pins set the start up clock frequency. See Table 9 for a description of the clock configuration modes.                                                                                                                                             |

|                    |         |                                  | Note that the operating frequency can be changed by programming the PLL multiplier and divider in the PMCTL register at any time after the core comes out of reset.                                                                                                                        |

| RESETOUT           | 0       | Output only                      | Reset Out. Drives out the core reset signal to an external device.                                                                                                                                                                                                                         |

| RESET              | I/A     | Input only                       | <b>Processor Reset</b> . Resets the ADSP-2126x to a known state. Upon deassertion, there is a 4096 CLKIN cycle latency for the PLL to lock. After this time, the core begins program execution from the hardware reset vector address. The RESET input must be asserted (low) at power-up. |

| ТСК                | I       | Input only <sup>3</sup>          | <b>Test Clock (JTAG)</b> . Provides a clock for JTAG boundary scan. TCK must be asserted (pulsed low) after power-up or held low for proper operation of the ADSP-2126x.                                                                                                                   |

| TMS                | I/S     | Three-state with pull-up enabled | <b>Test Mode Select (JTAG)</b> . Used to control the test state machine. TMS has a 22.5 k $\Omega$ internal pull-up resistor.                                                                                                                                                              |

| TDI                | I/S     | Three-state with pull-up enabled | <b>Test Data Input (JTAG)</b> . Provides serial data for the boundary scan logic. TDI has a 22.5 k $\Omega$ internal pull-up resistor.                                                                                                                                                     |

| TDO                | 0       | Three-state <sup>4</sup>         | Test Data Output (JTAG). Serial scan output of the boundary scan path.                                                                                                                                                                                                                     |

| TRST               | I/A     | Three-state with pull-up enabled | <b>Test Reset (JTAG)</b> . Resets the test state machine. TRST must be asserted (pulsed low) after power-up or held low for proper operation of the ADSP-2126x. TRST has a 22.5 k $\Omega$ internal pull-up resistor.                                                                      |

| EMU                | O (O/D) | Three-state with pull-up enabled | <b>Emulation Status</b> . Must be connected to the ADSP-2126x Analog Devices DSP Tools product line of JTAG emulators target board connector only. $\overline{\text{EMU}}$ has a 22.5 k $\Omega$ internal pull-up resistor.                                                                |

| V <sub>DDINT</sub> | Р       |                                  | <b>Core Power Supply</b> . Nominally +1.2 V dc and supplies the DSP's core processor (13 pins on the BGA package, 32 pins on the LQFP package).                                                                                                                                            |

| V <sub>DDEXT</sub> | Р       |                                  | <b>I/O Power Supply</b> . Nominally +3.3 V dc (6 pins on the BGA package, 10 pins on the LQFP package).                                                                                                                                                                                    |

| A <sub>VDD</sub>   | Ρ       |                                  | <b>Analog Power Supply</b> . Nominally +1.2 V dc and supplies the DSP's internal PLL (clock generator). This pin has the same specifications as $V_{DDINT}$ , except that added filtering circuitry is required. For more information, see Power Supplies on Page 7.                       |

| A <sub>vss</sub>   | G       |                                  | Analog Power Supply Return.                                                                                                                                                                                                                                                                |

| GND                | G       |                                  | Power Supply Return. (54 pins on the BGA package, 39 pins on the LQFP package).                                                                                                                                                                                                            |

$^1\,\overline{\text{RD}}, \overline{\text{WR}}, \text{and ALE}$  are continuously driven by the DSP and will not be three-stated.

<sup>2</sup>Output only is a three-state driver with its output path always enabled.

<sup>3</sup>Input only is a three-state driver, with both output path and pull-up disabled.

<sup>4</sup>Three-state is a three-state driver, with pull-up disabled.

## **PRODUCT SPECIFICATIONS**

#### **OPERATING CONDITIONS**

| Parameter <sup>1</sup>   | Description                                                      | Min  | Max               | Unit |

|--------------------------|------------------------------------------------------------------|------|-------------------|------|

| V <sub>DDINT</sub>       | Internal (Core) Supply Voltage                                   | 1.14 | 1.26              | V    |

| A <sub>VDD</sub>         | Analog (PLL) Supply Voltage                                      | 1.14 | 1.26              | V    |

| V <sub>DDEXT</sub>       | External (I/O) Supply Voltage                                    | 3.13 | 3.47              | V    |

| V <sub>IH</sub>          | High Level Input Voltage <sup>2</sup> @ V <sub>DDEXT</sub> = Max | 2.0  | $V_{DDEXT} + 0.5$ | V    |

| √ <sub>IL</sub>          | Low Level Input Voltage <sup>2</sup> @ V <sub>DDEXT</sub> = Min  | -0.5 | +0.8              | V    |

| V <sub>IH_CLKIN</sub>    | High Level Input Voltage <sup>3</sup> @ V <sub>DDEXT</sub> = Max | 1.74 | $V_{DDEXT} + 0.5$ | V    |

|                          | Low Level Input Voltage @ V <sub>DDEXT</sub> = Min               | -0.5 | +1.19             | V    |

| Г <sub>амв</sub> К Grade | Ambient Operating Temperature <sup>4, 5</sup>                    | 0    | +70               | °C   |

| T <sub>AMB</sub> B Grade | Ambient Operating Temperature <sup>4, 5</sup>                    | -40  | +85               | °C   |

<sup>1</sup>Specifications subject to change without notice.

<sup>2</sup>Applies to input and bidirectional pins: AD15–0, FLAG3–0, DAI\_Px, SPICLK, MOSI, MISO, SPIDS, BOOT\_CFGx, CLK\_CFGx, RESET, TCK, TMS, TDI, TRST. <sup>3</sup>Applies to input pin CLKIN.

<sup>4</sup>See Thermal Characteristics on Page 38 for information on thermal specifications.

<sup>5</sup> See Engineer-to-Engineer Note (No. EE-216) for further information.

#### **ELECTRICAL CHARACTERISTICS**

| Parameter <sup>1</sup>   | Description                                      | Test Conditions                                                                       | Min | Мах | Unit |

|--------------------------|--------------------------------------------------|---------------------------------------------------------------------------------------|-----|-----|------|

| V <sub>OH</sub>          | High Level Output Voltage <sup>2</sup>           | @ $V_{DDEXT} = Min$ , $I_{OH} = -1.0 \text{ mA}^3$                                    | 2.4 |     | V    |

| V <sub>OL</sub>          | Low Level Output Voltage <sup>2</sup>            | @ $V_{DDEXT} = Min$ , $I_{OL} = 1.0 \text{ mA}^3$                                     |     | 0.4 | V    |

| I <sub>IH</sub>          | High Level Input Current <sup>4, 5</sup>         | $@V_{DDEXT} = Max, V_{IN} = V_{DDEXT} Max$                                            |     | 10  | μΑ   |

| IIL                      | Low Level Input Current <sup>4</sup>             | @ $V_{DDEXT} = Max, V_{IN} = 0 V$                                                     |     | 10  | μΑ   |

| <b>I</b> <sub>ILPU</sub> | Low Level Input Current Pull-Up <sup>5</sup>     | @ $V_{DDEXT} = Max, V_{IN} = 0 V$                                                     |     | 200 | μΑ   |

| I <sub>OZH</sub>         | Three-State Leakage Current <sup>6, 7, 8</sup>   | $@V_{DDEXT} = Max, V_{IN} = V_{DDEXT} Max$                                            |     | 10  | μΑ   |

| I <sub>OZL</sub>         | Three-State Leakage Current <sup>6</sup>         | @ $V_{DDEXT} = Max, V_{IN} = 0 V$                                                     |     | 10  | μΑ   |

| I <sub>OZLPU</sub>       | Three-State Leakage Current Pull-Up <sup>7</sup> | @ $V_{DDEXT} = Max, V_{IN} = 0 V$                                                     |     | 200 | μΑ   |

| I <sub>DD-INTYP</sub>    | Supply Current (Internal) <sup>9, 10, 11</sup>   | $t_{CCLK} = 5.0 \text{ ns}, V_{DDINT} = 1.2 \text{ V}, T_{AMB} = +25^{\circ}\text{C}$ |     | 500 | mA   |

| I <sub>AVDD</sub>        | Supply Current (Analog) <sup>11</sup>            | A <sub>VDD</sub> = Max                                                                |     | 10  | mA   |

| C <sub>IN</sub>          | Input Capacitance <sup>12, 13</sup>              | $f_{IN} = 1 \text{ MHz}, T_{CASE} = 25^{\circ}\text{C}, V_{IN} = 1.2 \text{ V}$       |     | 4.7 | pF   |

<sup>1</sup>Specifications subject to change without notice.

<sup>2</sup>Applies to output and bidirectional pins: AD15-0, RD, WR, ALE, FLAG3-0, DAI\_Px, SPICLK, MOSI, MISO, EMU, TDO, CLKOUT, XTAL.

<sup>3</sup>See Output Drive Currents on Page 37 for typical drive current capabilities.

<sup>4</sup>Applies to input pins: <u>SPIDS</u>, BOOT\_CFGx, CLK\_CFGx, TCK, <u>RESET</u>, CLKIN.

<sup>5</sup> Applies to input pins with 22.5 k $\Omega$  internal pull-ups: TRST, TMS, TDI.

<sup>6</sup>Applies to three-statable pins: FLAG3–0.

$^7$  Applies to three-statable pins with 22.5 k $\Omega$  pull-ups: AD15–0, DAI\_Px, SPICLK, MISO, MOSI.

<sup>8</sup>Applies to open-drain output pins: <u>EMU</u>, MISO, MOSI.

<sup>9</sup>Typical internal current data reflects nominal operating conditions.

<sup>10</sup>See Engineer-to-Engineer Note (EE-216) for further information.

<sup>11</sup>Characterized, but not tested.

<sup>12</sup>Applies to all signal pins.

<sup>13</sup>Guaranteed, but not tested.

#### **Clock Input**

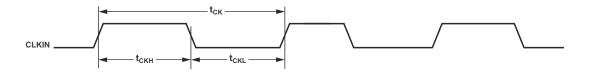

See Table 16 and Figure 6.

#### Table 16. Clock Input

|                    |                                  |                  | 150 MHz <sup>1</sup> |                 | 200 MHz <sup>2</sup> |      |

|--------------------|----------------------------------|------------------|----------------------|-----------------|----------------------|------|

| Parameter          |                                  | neter Min        |                      | Min             | Max                  | Unit |

| Timing             | Requirements                     |                  |                      |                 |                      |      |

| t <sub>cK</sub>    | CLKIN Period                     | 20 <sup>3</sup>  | 160 <sup>4</sup>     | 15 <sup>3</sup> | 160 <sup>4</sup>     | ns   |

| t <sub>ckl</sub>   | CLKIN Width Low                  | 7.5 <sup>3</sup> | 80 <sup>4</sup>      | 6 <sup>3</sup>  | 80 <sup>4</sup>      | ns   |

| t <sub>ckh</sub>   | CLKIN Width High                 | 7.5 <sup>3</sup> | 80 <sup>4</sup>      | 6 <sup>3</sup>  | 80 <sup>4</sup>      | ns   |

| t <sub>ckrf</sub>  | CLKIN Rise/Fall (0.4 V to 2.0 V) |                  | 3                    |                 | 3                    | ns   |

| f <sub>vco</sub> 5 | VCO Frequency                    | 200              | 800                  | 200             | 800                  | MHz  |

| t <sub>CCLK</sub>  | CCLK Period <sup>6</sup>         | 6.66             | 10                   | 5               | 10                   | ns   |

<sup>1</sup>Applies to all 150 MHz models. See Ordering Guide on Page 45.

<sup>2</sup> Applies to all 200 MHz models. See Ordering Guide on Page 45.

<sup>3</sup> Applies only for CLK\_CFG1-0 = 00 and default values for PLL control bits in PMCTL.

<sup>4</sup>Applies only for CLK\_CFG1-0 = 01 and default values for PLL control bits in PMCTL.

<sup>5</sup>See Figure 4 on Page 16 for VCO diagram.

<sup>6</sup>Any changes to PLL control bits in the PMCTL register must meet core clock timing specification t<sub>CCLK</sub>.

#### **Clock Signals**

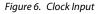

The ADSP-2126x can use an external clock or a crystal. See CLKIN pin description. The programmer can configure the ADSP-2126x to use its internal clock generator by connecting the necessary components to CLKIN and XTAL. Figure 7 shows the component connections used for a crystal operating in fundamental mode. Note that the 200 MHz clock rate is achieved using a 12.5 MHz crystal and a PLL multiplier ratio 16:1 (CCLK:CLKIN).

NOTE: C1 AND C2 ARE SPECIFIC TO CRYSTAL SPECIFIED FOR X1. CONTACT CRYSTAL MANUFACTURER FOR DETAILS. CRYSTAL SELECTION MUST COMPLY WITH CLKCFG1-0 = 10 OR = 01.

Figure 7. 150 MHz or 200 MHz Operation with a 12.5 MHz Fundamental Mode Crystal

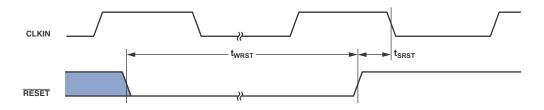

#### Reset

See Table 17 and Figure 8.

#### Table 17. Reset

| Paramete            | er                                        | Min              | Max | Unit |

|---------------------|-------------------------------------------|------------------|-----|------|

| Timing Requirements |                                           |                  |     |      |

| t <sub>WRST</sub>   | <b>RESET</b> Pulse Width Low <sup>1</sup> | $4 	imes t_{CK}$ |     | ns   |

| t <sub>srst</sub>   | <b>RESET</b> Setup Before CLKIN Low       | 8                |     | ns   |

<sup>1</sup>Applies after the power-up sequence is complete. At power-up, the processor's internal phase-locked loop requires no more than 100 μs while RESET is low, assuming stable VDD and CLKIN (not including start-up time of external clock oscillator).

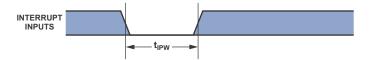

#### Interrupts

The timing specification in Table 18 and Figure 9 applies to the FLAG0, FLAG1, and FLAG2 pins when they are configured as IRQ0, IRQ1, and IRQ2 interrupts. Also applies to DAI\_P20-1 pins when configured as interrupts.

#### Table 18. Interrupts

| Parameter        |                  | Min                    | Мах | Unit |

|------------------|------------------|------------------------|-----|------|

| Timing Requiren  | nents            |                        |     |      |

| t <sub>IPW</sub> | IRQx Pulse Width | 2 t <sub>CCLK</sub> +2 |     | ns   |

Figure 9. Interrupts

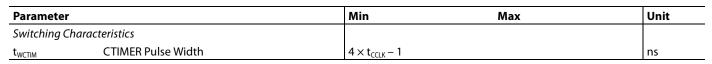

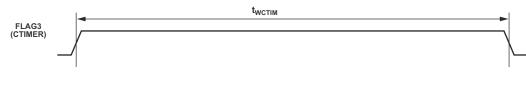

#### **Core Timer**

The timing specification in Table 19 and Figure 10 applies to FLAG3 when it is configured as the core timer (CTIMER).

#### Table 19. Core Timer

#### Timer PWM\_OUT Cycle Timing

The timing specification in Table 20 and Figure 11 applies to Timer in PWM\_OUT (pulse-width modulation) mode. Timer signals are routed to the DAI\_P20-1 pins through the SRU. Therefore, the timing specifications provided below are valid at the DAI\_P20-1 pins.

#### Table 20. Timer PWM\_OUT Timing

| Paramete          | er                       | Min                    | Мах                                 | Unit |

|-------------------|--------------------------|------------------------|-------------------------------------|------|

| Switching         | Characteristics          |                        |                                     |      |

| t <sub>PWMO</sub> | Timer Pulse Width Output | $2 	imes t_{CCLK} - 1$ | $2(2^{31}-1)\times t_{\text{CCLK}}$ | ns   |

Figure 11. Timer PWM\_OUT Timing

#### Timer WDTH\_CAP Timing

The timing specification in Table 21 and Figure 12 applies to Timer in WDTH\_CAP (pulse width count and capture) mode. Timer signals are routed to the DAI\_P20-1 pins through the SRU. Therefore, the timing specifications provided below are valid at the DAI\_P20-1 pins.

#### Table 21. Timer Width Capture Timing

| Parame           | eter              | Min                 | Мах                           | Unit |

|------------------|-------------------|---------------------|-------------------------------|------|

| Timing I         | Requirements      |                     |                               |      |

| t <sub>PWI</sub> | Timer Pulse Width | $2 \times t_{CCLK}$ | $2(2^{31}-1) \times t_{CCLK}$ | ns   |

Figure 12. Timer Width Capture Timing

#### DAI Pin-to-Pin Direct Routing

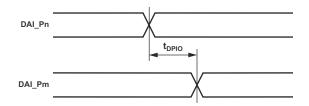

See Table 22 and Figure 13 for direct pin connections only (for example, DAI\_PB01\_I to DAI\_PB02\_O).

#### Table 22. DAI Pin-to-Pin Routing

| Parame            | ter                                           | Min | Max | Unit |

|-------------------|-----------------------------------------------|-----|-----|------|

| Timing F          | Requirements                                  |     |     |      |

| t <sub>DPIO</sub> | Delay DAI Pin Input Valid to DAI Output Valid | 1.5 | 10  | ns   |

Figure 13. DAI Pin-to-Pin Direct Routing

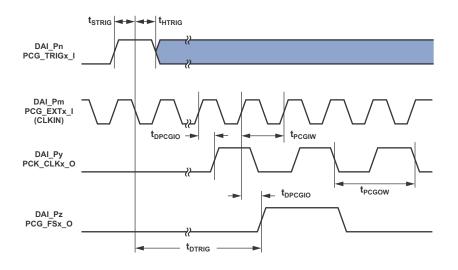

#### Precision Clock Generator (Direct Pin Routing)

The timing in Table 23 and Figure 14 is valid only when the SRU is configured such that the precision clock generator (PCG) takes its inputs directly from the DAI pins (via pin buffers) and sends its outputs directly to the DAI pins. For the

other cases where the PCG's inputs and outputs are not directly routed to/from DAI pins (via pin buffers), there is no timing data available. All timing parameters and switching characteristics apply to external DAI pins (DAI\_P07–DAI\_P20).

#### Table 23. Precision Clock Generator (Direct Pin Routing)

| Parameter           |                                                                                         | Min                          | Max                             | Unit |

|---------------------|-----------------------------------------------------------------------------------------|------------------------------|---------------------------------|------|

| Timing Requ         | uirements                                                                               |                              |                                 |      |

| t <sub>PCGIW</sub>  | Input Clock Pulse Width                                                                 | 20                           |                                 | ns   |

| t <sub>STRIG</sub>  | PCG Trigger Setup Before Falling Edge of PCG Input Clock                                | 2                            |                                 | ns   |

| t <sub>HTRIG</sub>  | PCG Trigger Hold After Falling Edge of PCG Input Clock                                  | 2                            |                                 | ns   |

| Switching C         | haracteristics                                                                          |                              |                                 |      |

| t <sub>DPCGIO</sub> | PCG Output Clock and Frame Sync Active Edge Delay After PCG Input<br>Clock Falling Edge | 2.5                          | 10                              | ns   |

| t <sub>DTRIG</sub>  | PCG Output Clock and Frame Sync Delay After PCG Trigger                                 | $2.5 + 2.5 \times t_{PCGOW}$ | $10+2.5\times t_{\text{PCGOW}}$ | ns   |

| t <sub>PCGOW</sub>  | Output Clock Pulse Width                                                                | 40                           |                                 | ns   |

Figure 14. Precision Clock Generator (Direct Pin Routing)

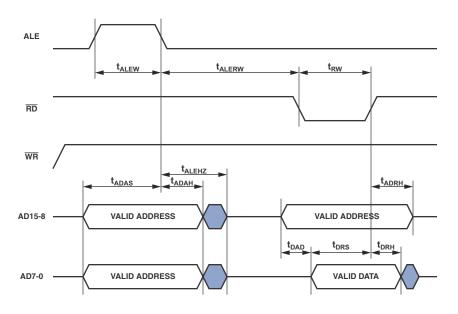

#### Memory Read—Parallel Port

The specifications in Table 25, Table 26, Figure 16, and Figure 17 are for asynchronous interfacing to memories (and memory-mapped peripherals) when the ADSP-2126x is accessing external memory space.

#### Table 25. 8-Bit Memory Read Cycle

| Parameter<br>Timing Requirements |                                               | Min                           | Мах                               | Unit |

|----------------------------------|-----------------------------------------------|-------------------------------|-----------------------------------|------|

|                                  |                                               |                               |                                   |      |

| t <sub>DRS</sub>                 | Address/Data 7–0 Setup Before RD High         | 3.3                           |                                   | ns   |

| t <sub>DRH</sub>                 | Address/Data 7–0 Hold After RD High           | 0                             |                                   | ns   |

| t <sub>DAD</sub>                 | Address 15-8 to Data Valid                    |                               | $D+0.5\times t_{\text{CCLK}}-3.5$ | ns   |

| Switching                        | Characteristics                               |                               |                                   |      |

| L                                | ALE Pulse Width                               | $2 \times t_{CCLK} - 2$       |                                   | ns   |

| ALERW                            | ALE Deasserted to Read/Write Asserted         | $1 \times t_{CCLK} - 0.5$     |                                   | ns   |

| ADAS                             | Address/Data 15-0 Setup Before ALE Deasserted | $2.5 \times t_{CCLK} - 2.0$   |                                   | ns   |

| adah 1                           | Address/Data 15-0 Hold After ALE Deasserted   | $0.5 	imes t_{CCLK} - 0.8$    |                                   | ns   |

| ALEHZ                            | ALE Deasserted to Address/Data7-0 in High-Z   | $0.5 	imes t_{CCLK} - 0.8$    | $0.5 	imes t_{CCLK} + 2.0$        | ns   |

| RW                               | RD Pulse Width                                | D – 2                         |                                   | ns   |

| t <sub>ADRH</sub>                | Address/Data 15–8 Hold After RD High          | $0.5 \times t_{CCLK} - 1 + H$ |                                   | ns   |

D = (The value set by the PPDUR Bits (5–1) in the PPCTL register)  $\times$   $t_{\mbox{\tiny CCLK}}$

$H = t_{CCLK}$  (if a hold cycle is specified, else H = 0)

<sup>1</sup>On reset, ALE is an active high cycle. However, it can be reconfigured by software to be active low.

Figure 16. 8-Bit Memory Read Cycle

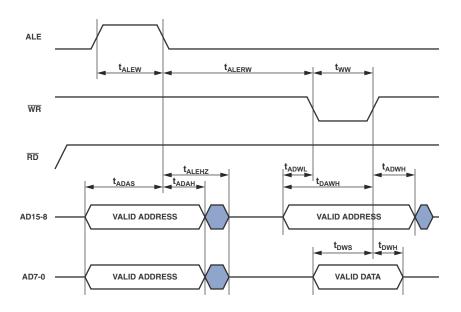

#### Memory Write—Parallel Port

Use the specifications in Table 27, Table 28, Figure 18, and Figure 19 for asynchronous interfacing to memories (and memory-mapped peripherals) when the ADSP-2126x is accessing external memory space.

#### Table 27. 8-Bit Memory Write Cycle

| Parameter                 |                                               | Min Max                         |                            | Unit |

|---------------------------|-----------------------------------------------|---------------------------------|----------------------------|------|

| Switching Characteristics |                                               |                                 |                            |      |

| t <sub>ALEW</sub>         | ALE Pulse Width                               | $2 \times t_{CCLK} - 2$         |                            | ns   |

| ALERW                     | ALE Deasserted to Read/Write Asserted         | $1 \times t_{CCLK} - 0.5$       |                            | ns   |

| ADAS                      | Address/Data 15–0 Setup Before ALE Deasserted | $2.5 	imes t_{CCLK} - 2.0$      |                            | ns   |

| ADAH                      | Address/Data 15–0 Hold After ALE Deasserted   | $0.5 	imes t_{CCLK} - 0.8$      |                            | ns   |

| ww                        | WR Pulse Width                                | D – 2                           |                            | ns   |

| ADWL                      | Address/Data 15–8 to WR Low                   | $0.5 \times t_{CCLK} - 1.5$     |                            | ns   |

| ADWH                      | Address/Data 15–8 Hold After WR High          | $0.5 \times t_{CCLK} - 1 + H$   |                            | ns   |

| ALEHZ                     | ALE Deasserted to Address/Data 15–0 in High-Z | $0.5 	imes t_{CCLK} - 0.8$      | $0.5 	imes t_{CCLK} + 2.0$ | ns   |

| DWS                       | Address/Data 7–0 Setup Before WR High         | D                               |                            | ns   |

| t <sub>DWH</sub>          | Address/Data 7–0 Hold After WR High           | $0.5 \times t_{CCLK} - 1.5 + H$ |                            | ns   |

| t <sub>DAWH</sub>         | Address/Data to WR High                       | D                               |                            | ns   |

D = (The value set by the PPDUR Bits (5–1) in the PPCTL register)  $\times$   $t_{\mbox{\tiny CCLK}}$

$H = t_{CCLK}$  (if a hold cycle is specified, else H = 0)

<sup>1</sup>On reset, ALE is an active high cycle. However, it can be reconfigured by software to be active low.

Figure 18. 8-Bit Memory Write Cycle

#### Table 31. Serial Ports—Enable and Three-State

| Parameter          |                                                       |    | Max | Unit |

|--------------------|-------------------------------------------------------|----|-----|------|

| Switching (        | Characteristics                                       |    |     |      |

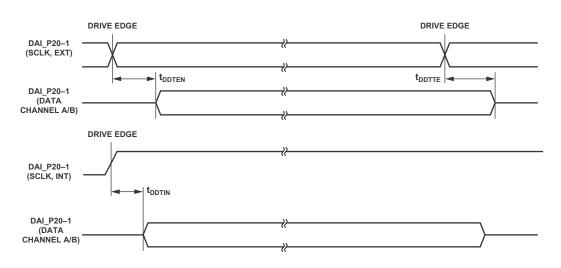

| t <sub>DDTEN</sub> | Data Enable from External Transmit SCLK <sup>1</sup>  | 2  |     | ns   |

| t <sub>DDTTE</sub> | Data Disable from External Transmit SCLK <sup>1</sup> |    | 7   | ns   |

| t <sub>DDTIN</sub> | Data Enable from Internal Transmit SCLK <sup>1</sup>  | -1 |     | ns   |

<sup>1</sup>Referenced to drive edge.

Figure 21. Enable and Three-State

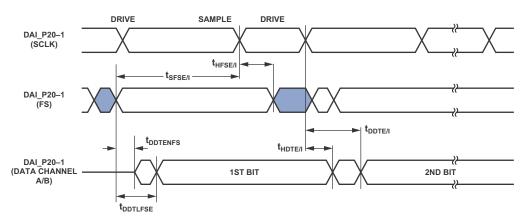

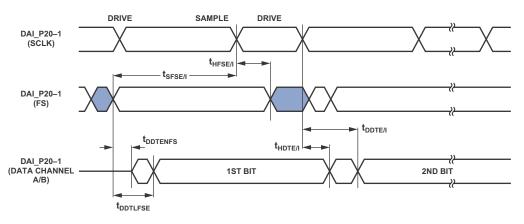

#### Table 32. Serial Ports—External Late Frame Sync

| Parameter            |                                                                                              |     | Max | Unit |

|----------------------|----------------------------------------------------------------------------------------------|-----|-----|------|

| Switching C          | haracteristics                                                                               |     |     |      |

| t <sub>DDTLFSE</sub> | Data Delay from Late External Transmit FS or External Receive FS with MCE = 1, MFD = $0^{1}$ |     | 7   | ns   |

| t <sub>DDTENFS</sub> | Data Enable for MCE = 1, MFD = $0^1$                                                         | 0.5 |     | ns   |

$^{1}$ The t<sub>DDTLESE</sub> and t<sub>DDTENES</sub> parameters apply to left-justified sample pair mode as well as DSP serial mode, and MCE = 1, MFD = 0.

#### EXTERNAL RECEIVE FS WITH MCE = 1, MFD = 0

LATE EXTERNAL TRANSMIT FS

*Figure 22. External Late Frame Sync*<sup>1</sup>

<sup>1</sup>This figure reflects changes made to support left-justified sample pair mode.

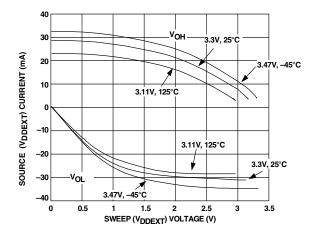

#### **OUTPUT DRIVE CURRENTS**

Figure 28 shows typical I-V characteristics for the output drivers of the ADSP-2126x. The curves represent the current drive capability of the output drivers as a function of output voltage.

Figure 28. Typical Drive

#### **TEST CONDITIONS**

The ac signal specifications (timing parameters) appear in Table 16 on Page 18 through Table 37 on Page 36. These include output disable time, output enable time, and capacitive loading.

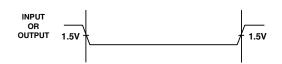

Timing is measured on signals when they cross the 1.5 V level as described in Figure 30. All delays (in nanoseconds) are measured between the point that the first signal reaches 1.5 V and the point that the second signal reaches 1.5 V.

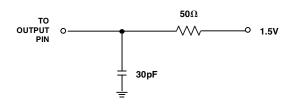

Figure 29. Equivalent Device Loading for AC Measurements (Includes All Fixtures)

Figure 30. Voltage Reference Levels for AC Measurements

#### **CAPACITIVE LOADING**

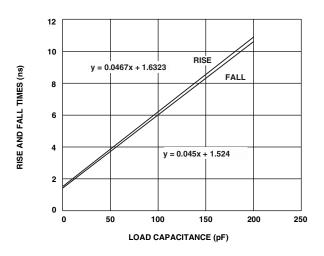

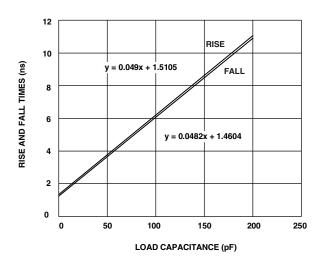

Output delays and holds are based on standard capacitive loads: 30 pF on all pins (see Figure 29). Figure 32 shows graphically how output delays and holds vary with load capacitance (note that this graph or derating does not apply to output disable delays). The graphs of Figure 31, Figure 32, and Figure 33 may not be linear outside the ranges shown for Typical Output Delay vs. Load Capacitance and Typical Output Rise Time (20% to 80%, V = Min) vs. Load Capacitance.

Figure 31. Typical Output Rise Time (20% to 80%, V<sub>DDEXT</sub> = Max)

Figure 32. Typical Output Rise/Fall Time (20% to 80%, V<sub>DDEXT</sub> = Min)

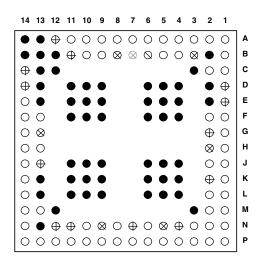

## **136-BALL BGA PIN CONFIGURATIONS**

Table 41 shows the ADSP-2126x's pin names and their default function after reset (in parentheses). Figure 34 on Page 42 shows the BGA package pin assignments.

#### Table 41. 136-Ball BGA Pin Assignments

|                    | BGA Pin |                    | BGA Pin |                    | <b>BGA Pin</b> |                    | BGA Pin |

|--------------------|---------|--------------------|---------|--------------------|----------------|--------------------|---------|

| Pin Name           | No.     | Pin Name           | No.     | Pin Name           | No.            | Pin Name           | No.     |

| CLK_CFG0           | A01     | CLK_CFG1           | B01     | BOOT_CFG1          | C01            | V <sub>DDINT</sub> | D01     |

| XTAL               | A02     | GND                | B02     | BOOT_CFG0          | C02            | GND                | D02     |

| TMS                | A03     | V <sub>DDEXT</sub> | B03     | GND                | C03            | GND                | D04     |

| ТСК                | A04     | CLKIN              | B04     | GND                | C12            | GND                | D05     |

| TDI                | A05     | TRST               | B05     | GND                | C13            | GND                | D06     |

| RESETOUT           | A06     | A <sub>VSS</sub>   | B06     | V <sub>DDINT</sub> | C14            | GND                | D09     |

| TDO                | A07     | A <sub>VDD</sub>   | B07     |                    |                | GND                | D10     |

| EMU                | A08     | V <sub>DDEXT</sub> | B08     |                    |                | GND                | D11     |

| MOSI               | A09     | SPICLK             | B09     |                    |                | GND                | D13     |

| MISO               | A10     | RESET              | B10     |                    |                | V <sub>DDINT</sub> | D14     |

| SPIDS              | A11     | V <sub>DDINT</sub> | B11     |                    |                |                    |         |

| V <sub>DDINT</sub> | A12     | GND                | B12     |                    |                |                    |         |

| GND                | A13     | GND                | B13     |                    |                |                    |         |

| GND                | A14     | GND                | B14     |                    |                |                    |         |

| V <sub>DDINT</sub> | E01     | FLAG1              | F01     | AD7                | G01            | AD6                | H01     |

| GND                | E02     | FLAG0              | F02     | V <sub>DDINT</sub> | G02            | V <sub>DDEXT</sub> | H02     |

| GND                | E04     | GND                | F04     | V <sub>DDEXT</sub> | G13            | DAI_P18 (SD5B)     | H13     |

| GND                | E05     | GND                | F05     | DAI_P19 (SCLK45)   | G14            | DAI_P17 (SD5A)     | H14     |

| GND                | E06     | GND                | F06     |                    |                |                    |         |

| GND                | E09     | GND                | F09     |                    |                |                    |         |

| GND                | E10     | GND                | F10     |                    |                |                    |         |

| GND                | E11     | GND                | F11     |                    |                |                    |         |

| GND                | E13     | FLAG2              | F13     |                    |                |                    |         |

| FLAG3              | E14     | DAI_P20 (SFS45)    | F14     |                    |                |                    |         |

### **OUTLINE DIMENSIONS**

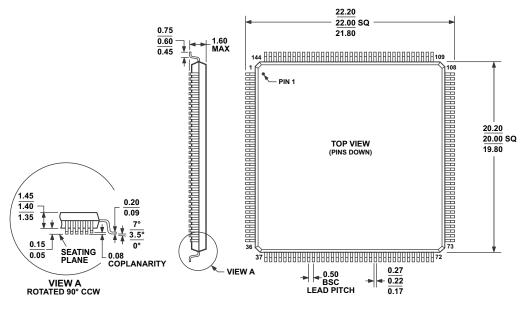

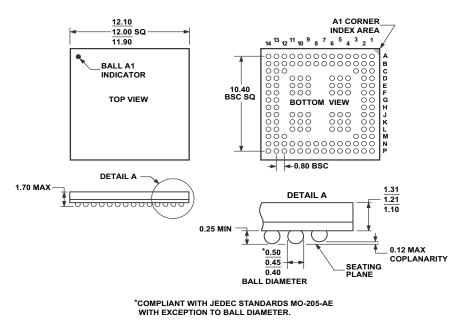

The ADSP-2126x is available in a 144-lead LQFP package and a 136-ball BGA package shown in Figure 35 and Figure 36.

COMPLIANT TO JEDEC STANDARDS MS-026-BFB

Figure 35. 144-Lead Low Profile Flat Package [LQFP] (ST-144) Dimensions shown in millimeters

Figure 36. 136-Ball Chip Scale Package Ball Grid Array [CSP\_BGA] (BC-136-1) Dimensions shown in millimeters

#### SURFACE-MOUNT DESIGN

Table 42 is provided as an aide to PCB design. For industry-<br/>standard design recommendations, refer to IPC-7351, Generic<br/>Requirements for Surface-Mount Design and Land Pattern<br/>Standard.

| Table 42. | BGA | _ED Data | a for Use | with Su | urface-N | Mount Design |

|-----------|-----|----------|-----------|---------|----------|--------------|

|-----------|-----|----------|-----------|---------|----------|--------------|

| Package                     | Ball Attach Type          | Solder Mask Opening | Ball Pad Size |  |

|-----------------------------|---------------------------|---------------------|---------------|--|

| 136-Ball CSP_BGA (BC-136-1) | Solder Mask Defined (SMD) | 0.4 mm              | 0.53 mm       |  |