#### Microchip Technology - PIC16F18324-I/P Datasheet

# E·XFL

#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

| Product Status             | Active                                                                    |

|----------------------------|---------------------------------------------------------------------------|

| Core Processor             | PIC                                                                       |

| Core Size                  | 8-Bit                                                                     |

| Speed                      | 32MHz                                                                     |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                 |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                     |

| Number of I/O              | 12                                                                        |

| Program Memory Size        | 7KB (4K x 14)                                                             |

| Program Memory Type        | FLASH                                                                     |

| EEPROM Size                | 256 x 8                                                                   |

| RAM Size                   | 512 x 8                                                                   |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                               |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                      |

| Oscillator Type            | Internal                                                                  |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                         |

| Mounting Type              | Through Hole                                                              |

| Package / Case             | 14-DIP (0.300", 7.62mm)                                                   |

| Supplier Device Package    | 14-PDIP                                                                   |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18324-i-p |

|                            |                                                                           |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

| TA  | BLE 4  | I-4: SPE | CIAL FL                          | <b>JNCTION RE</b> | EGISTER S | UMMARY B    | ANKS 0-31 (     | CONTINUE          | D)      |       |       |                       |                                 |

|-----|--------|----------|----------------------------------|-------------------|-----------|-------------|-----------------|-------------------|---------|-------|-------|-----------------------|---------------------------------|

| Ad  | ldress | Name     | PIC16(L)F18324<br>PIC16(L)F18344 | Bit 7             | Bit 6     | Bit 5       | Bit 4           | Bit 3             | Bit 2   | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>resets |

| E   | 3ank 5 |          |                                  |                   |           |             |                 |                   |         |       |       |                       |                                 |

|     |        |          |                                  |                   |           | CPU CORE RI | EGISTERS; see 1 | Table 4-2 for spe | ecifics |       |       |                       |                                 |

| 280 | Ch     | ODCONA   |                                  | _                 | _         | ODCA5       | ODCA4           | _                 | ODCA2   | ODCA1 | ODCA0 | 00 -000               | 00 -000                         |

| 201 | Dh     |          | V                                |                   |           |             | Linimala        | montod            |         |       |       |                       |                                 |

|      |         |     |        |                                | CFU CORE RE       | -0101 - 100, 300 -              |        | icines |         |           |           |           |

|------|---------|-----|--------|--------------------------------|-------------------|---------------------------------|--------|--------|---------|-----------|-----------|-----------|

| 28Ch | ODCONA  |     | —      |                                | ODCA5             | ODCA4                           | _      | ODCA2  | ODCA1   | ODCA0     | 00 -000   | 00 -000   |

| 28Dh | ODCONB  | X – |        |                                |                   | Unimple                         | mented |        |         |           | -         | —         |

|      |         | — X | ODCB7  | ODCB6                          | ODCB5             | ODCB4                           | —      | —      | —       | -         | 0000      | 0000      |

| 28Eh | ODCONC  | X — | —      | —                              | ODCC5             | ODCC4                           | ODCC3  | ODCC2  | ODCC1   | ODCC0     | 00 0000   | 00 0000   |

|      |         | — X | ODCC7  | ODCC6                          | ODCC5             | ODCC4                           | ODCC3  | ODCC2  | ODCC1   | ODCC0     | 0000 0000 | 0000 0000 |

| 28Fh | —       |     |        |                                |                   | Unimple                         | mented |        |         |           | -         | —         |

| 290h | _       |     |        |                                |                   | Unimple                         | mented |        |         |           |           | —         |

| 291h | CCPR1L  |     |        | CCPR1<7:0>                     |                   |                                 |        |        |         | xxxx xxxx | xxxx xxxx |           |

| 292h | CCPR1H  |     |        | CCPR1<15:8> xxxx xxxx xxxx xxx |                   |                                 |        |        |         |           | xxxx xxxx |           |

| 293h | CCP1CON |     | CCP1EN | _                              | CCP10UT           | CCP1OUT CCP1FMT CCP1MODE<3:0> 0 |        |        |         |           | 0-x0 0000 | 0-x0 0000 |

| 294h | CCP1CAP |     | _      |                                | CCP1CTS<3:0> 0000 |                                 |        |        |         |           | xxxx      |           |

| 295h | CCPR2L  |     |        |                                |                   | CCPR2                           | 2<7:0> |        |         |           | xxxx xxxx | xxxx xxxx |

| 296h | CCPR2H  |     |        |                                | •                 | CCPR2                           | <15:8> |        |         |           | xxxx xxxx | xxxx xxxx |

| 297h | CCP2CON |     | CCP2EN | _                              | CCP2OUT           | CCP2FMT                         |        | CCP2MC | DE<3:0> |           | 0-x0 0000 | 0-x0 0000 |

| 298h | CCP2CAP |     | _      | _                              |                   | _                               |        | CCP2C  | TS<3:0> |           | 0000      | xxxx      |

| 299h | —       | —   |        |                                |                   | Unimple                         | mented |        |         |           | -         | —         |

| 29Ah | —       | —   |        |                                |                   | Unimple                         | mented |        |         |           | -         | —         |

| 29Bh | —       |     |        |                                |                   | Unimple                         | mented |        |         |           | _         | —         |

| 29Ch | —       |     |        |                                |                   | Unimple                         | mented |        |         |           | _         | _         |

| 29Dh | —       |     |        |                                |                   | Unimple                         | mented |        |         |           | _         | —         |

| 29Eh | —       | _   |        |                                | •                 | Unimple                         | mented |        |         |           |           | —         |

| 29Fh | CCPTMRS |     | C4TSEL | .<1:0>                         | C3TSE             | EL<1:0>                         | C2TSE  | L<1:0> | C1TSE   | L<1:0>    | 0101 0101 | 0101 0101 |

x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

Only on PIC16F18324/18344. Note 1:

Register accessible from both User and ICD Debugger. 2:

| U-0                                      | U-0                                                                   | R/W-0/0                                                            | R/W-0/0                                 | R/W-0/0                        | R/W-0/0           | R/W-0/0        | R/W-0/0         |

|------------------------------------------|-----------------------------------------------------------------------|--------------------------------------------------------------------|-----------------------------------------|--------------------------------|-------------------|----------------|-----------------|

|                                          | _                                                                     |                                                                    |                                         | HFTU                           | N<5:0>            |                |                 |

| bit 7                                    |                                                                       |                                                                    |                                         |                                |                   |                | bit 0           |

|                                          |                                                                       |                                                                    |                                         |                                |                   |                |                 |

| Legend:                                  |                                                                       |                                                                    |                                         |                                |                   |                |                 |

| R = Readable bit                         |                                                                       | W = Writable                                                       | bit                                     | U = Unimplen                   | nented bit, read  | d as '0'       |                 |

| u = Bit is unchange                      | d                                                                     | x = Bit is unkn                                                    | iown                                    | -n/n = Value a                 | at POR and BC     | R/Value at all | other Resets    |

| '1' = Bit is set                         |                                                                       | '0' = Bit is clea                                                  | ared                                    | q = Reset val                  | ue is determine   | ed by hardware | e               |

| bit 5-0 HF<br>01<br>01<br>00<br>00<br>11 | <b>FUN&lt;5:0&gt;</b><br>1111 = M<br>1110<br>0001<br>0000 = C<br>1111 | ted: Read as '(<br>: HFINTOSC F<br>aximum freque<br>enter frequenc | requency Tur<br>ency<br>y. Oscillator m | ning bits<br>Nodule is running | g at the calibrat | ed frequency ( | default value). |

#### **REGISTER 7-7:** OSCTUNE: HFINTOSC TUNING REGISTER

| Name     | Bit 7   | Bit 6     | Bit 5    | Bit 4 | Bit 3  | Bit 2     | Bit 1  | Bit 0 | Register<br>on Page |  |

|----------|---------|-----------|----------|-------|--------|-----------|--------|-------|---------------------|--|

| OSCCON1  |         | NOSC<2:0> |          |       |        | 87        |        |       |                     |  |

| OSCCON2  | _       | C         | OSC<2:0> |       |        | CDIV<3:0> |        |       |                     |  |

| OSCCON3  | CWSHOLD | SOSCPWR   | SOSCBE   | ORDY  | NOSCR  | _         | _      | _     | 89                  |  |

| OSCSTAT1 | EXTOR   | HFOR      | —        | LFOR  | SOR    | ADOR      | _      | PLLR  | 90                  |  |

| OSCEN    | EXTOEN  | HFOEN     | —        | LFOEN | SOSCEN | ADOEN     | _      | _     | 91                  |  |

| OSCFRQ   | _       | _         | —        | _     |        | HFFRG     | Q<3:0> |       | 92                  |  |

| OSCTUNE  | —       |           |          |       | HFTUN  | 93        |        |       |                     |  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

#### TABLE 7-4: SUMMARY OF CONFIGURATION WORD WITH CLOCK SOURCES

| Name    | Bits | Bit -/7 | Bit -/6 | Bit 13/5 | Bit 12/4 | Bit 11/3 | Bit 10/2 | Bit 9/1  | Bit 8/0  | Register<br>on Page |

|---------|------|---------|---------|----------|----------|----------|----------|----------|----------|---------------------|

|         | 13:8 | _       | _       | FCMEN    | _        | CSWEN    | _        | _        | CLKOUTEN |                     |

| CONFIG1 | 7:0  | _       | RSTOSC2 | RSTOSC1  | RSTOSC0  | _        | FEXTOSC2 | FEXTOSC1 | FEXTOSC0 | 62                  |

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by clock sources.

© 2015-2016 Microchip Technology Inc.

| REGISTER         | 8-3: PIE1:                                                                                                        | PERIPHERA                                                                                            | L INTERRUI      | PT ENABLE I      | REGISTER 1       |                  |              |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------|-----------------|------------------|------------------|------------------|--------------|--|--|--|--|

| R/W-0/0          | R/W-0/0                                                                                                           | R/W-0/0                                                                                              | R/W-0/0         | R/W-0/0          | R/W-0/0          | R/W-0/0          | R/W-0/0      |  |  |  |  |

| TMR1GIE          | ADIE                                                                                                              | RCIE                                                                                                 | TXIE            | SSP1IE           | BCL1IE           | TMR2IE           | TMR1IE       |  |  |  |  |

| bit 7            |                                                                                                                   |                                                                                                      |                 |                  |                  |                  | bit C        |  |  |  |  |

| Levende          |                                                                                                                   |                                                                                                      |                 |                  |                  |                  |              |  |  |  |  |

| Legend:          | - h:4                                                                                                             |                                                                                                      | L:4             |                  | ented bit read   | aa (0)           |              |  |  |  |  |

| R = Readable     |                                                                                                                   | W = Writable                                                                                         |                 |                  | nented bit, read |                  | they Decete  |  |  |  |  |

| u = Bit is unc   | 9                                                                                                                 | x = Bit is unkr                                                                                      |                 |                  | at POR and BO    | R/Value at all C | liner Resels |  |  |  |  |

| '1' = Bit is set | t                                                                                                                 | '0' = Bit is cle                                                                                     | ared            |                  |                  |                  |              |  |  |  |  |

| bit 7            | TMR1GIE: T                                                                                                        | imer1 Gate Inte                                                                                      | rrupt Enable t  | oit              |                  |                  |              |  |  |  |  |

|                  |                                                                                                                   | the Timer1 gate                                                                                      | -               |                  |                  |                  |              |  |  |  |  |

|                  |                                                                                                                   | the Timer1 gate                                                                                      |                 |                  |                  |                  |              |  |  |  |  |

| bit 6            | ADIE: Analog                                                                                                      | g-to-Digital Con                                                                                     | verter (ADC)    | Interrupt Enable | e bit            |                  |              |  |  |  |  |

|                  | 1 = Enables                                                                                                       | the ADC interru                                                                                      | pt              |                  |                  |                  |              |  |  |  |  |

|                  | 0 = Disables                                                                                                      | the ADC interru                                                                                      | upt             |                  |                  |                  |              |  |  |  |  |

| bit 5            |                                                                                                                   | RT Receive Int                                                                                       | •               |                  |                  |                  |              |  |  |  |  |

|                  |                                                                                                                   | the EUSART re                                                                                        |                 |                  |                  |                  |              |  |  |  |  |

| L:1. A           |                                                                                                                   | the EUSART re                                                                                        | •               |                  |                  |                  |              |  |  |  |  |

| bit 4            |                                                                                                                   | RT Transmit Int                                                                                      | •               |                  |                  |                  |              |  |  |  |  |

|                  |                                                                                                                   | the EUSART tra<br>the EUSART tr                                                                      |                 |                  |                  |                  |              |  |  |  |  |

| bit 3            |                                                                                                                   |                                                                                                      |                 |                  | ole bit          |                  |              |  |  |  |  |

|                  | •                                                                                                                 | <b>SSP1IE:</b> Synchronous Serial Port (MSSP) Interrupt Enable bit<br>1 = Enables the MSSP interrupt |                 |                  |                  |                  |              |  |  |  |  |

|                  |                                                                                                                   | 0 = Disables the MSSP interrupt                                                                      |                 |                  |                  |                  |              |  |  |  |  |

| bit 2            | BCL1IE: MS                                                                                                        | SP1 Bus Collisi                                                                                      | on Interrupt E  | nable bit        |                  |                  |              |  |  |  |  |

|                  |                                                                                                                   | 1 = MSSP bus collision interrupt enabled                                                             |                 |                  |                  |                  |              |  |  |  |  |

|                  |                                                                                                                   | us collision inter                                                                                   | •               |                  |                  |                  |              |  |  |  |  |

| bit 1            |                                                                                                                   | R2 to PR2 Mat                                                                                        | •               |                  |                  |                  |              |  |  |  |  |

|                  | <ol> <li>Enables the Timer2 to PR2 match interrupt</li> <li>Disables the Timer2 to PR2 match interrupt</li> </ol> |                                                                                                      |                 |                  |                  |                  |              |  |  |  |  |

| bit 0            |                                                                                                                   | ner1 Overflow Ir                                                                                     |                 | •                |                  |                  |              |  |  |  |  |

|                  |                                                                                                                   | the Timer1 over                                                                                      | •               |                  |                  |                  |              |  |  |  |  |

|                  | 0 = Disables                                                                                                      | the Timer1 ove                                                                                       | rflow interrupt | :                |                  |                  |              |  |  |  |  |

| Note D           |                                                                                                                   |                                                                                                      |                 |                  |                  |                  |              |  |  |  |  |

|                  | t PEIE of the IN<br>et to enable any                                                                              |                                                                                                      |                 |                  |                  |                  |              |  |  |  |  |

| 56               | ally                                                                                                              | periprierarinter                                                                                     | ιupι.           |                  |                  |                  |              |  |  |  |  |

#### REGISTER 8-3: PIE1: PERIPHERAL INTERRUPT ENABLE REGISTER 1

#### EXAMPLE 11-4: WRITING TO PROGRAM FLASH MEMORY

|        | LE 11-4: V   | VRITING TO PROGRAM      |                                                    |

|--------|--------------|-------------------------|----------------------------------------------------|

| ; This | write rout   | ine assumes the follow  | ing:                                               |

| ; 1. 3 | 2 words of d | lata are loaded, starti | ing at the address in DATA_ADDR                    |

| ; 2. E | ach word of  | data to be written is   | made up of two adjacent bytes in DATA_ADDR,        |

| ; s    | tored in lit | tle endian format       |                                                    |

| ; 3.A  | valid start  | ing address (the least  | significant bits = 00000) is loaded in ADDRH:ADDRL |

| ; 4. A | DDRH and ADI | ORL are located in comm | non RAM (locations 0x70 - 0x7F)                    |

| ; 5.N  | VM interrupt | s are not taken into a  | account                                            |

|        |              |                         |                                                    |

|        | BANKSEL      | NVMADRH                 |                                                    |

|        | MOVF         | ADDRH,W                 |                                                    |

|        | MOVWF        | NVMADRH                 | ; Load initial address                             |

|        | MOVF         | ADDRL,W                 |                                                    |

|        | MOVWF        | NVMADRL                 |                                                    |

|        | MOVLW        | LOW DATA_ADDR           | ; Load initial data address                        |

|        | MOVWF        | FSROL                   |                                                    |

|        | MOVLW        | HIGH DATA_ADDR          |                                                    |

|        | MOVWF        | FSROH                   |                                                    |

|        | BCF          | NVMCON1, NVMREGS        | ; Set Program Flash Memory as write location       |

|        | BSF          | NVMCON1,WREN            | ; Enable writes                                    |

|        | BSF          | NVMCON1,LWLO            | ; Load only write latches                          |

| LOOP   |              |                         |                                                    |

|        | MOVIW        | FSR0++                  |                                                    |

|        | MOVWF        | NVMDATL                 | ; Load first data byte                             |

|        | MOVIW        | FSR0++                  | -                                                  |

|        | MOVWF        | NVMDATH                 | ; Load second data byte                            |

|        | MOVF         | NVMADRL,W               |                                                    |

|        | XORLW        | 0x1F                    | ; Check if lower bits of address are 00000         |

|        | ANDLW        | 0x1F                    | ; and if on last of 32 addresses                   |

|        | BTFSC        | STATUS, Z               | ; Last of 32 words?                                |

|        | GOTO         | START_WRITE             | ; If so, go write latches into memory              |

|        |              |                         |                                                    |

|        | CALL         | UNLOCK_SEQ              | ; If not, go load latch                            |

|        | INCF         | NVMADRL, F              | ; Increment address                                |

|        | GOTO         | LOOP                    |                                                    |

| START_ | WRITE        |                         |                                                    |

|        | BCF          | NVMCON1,LWLO            | ; Latch writes complete, now write memory          |

|        | CALL         | UNLOCK_SEQ              | ; Perform required unlock sequence                 |

|        | BCF          | NVMCON1,LWLO            | ; Disable writes                                   |

|        | CEO          |                         |                                                    |

| UNLOCK | MOVLW        | 55h                     |                                                    |

|        |              |                         | ; Disable interrupts                               |

|        | BCF          | INTCON, GIE             | -                                                  |

|        | MOVWF        | NVMCON2                 | ; Begin unlock sequence                            |

|        | MOVLW        | AAh                     |                                                    |

|        | MOVWF        | NVMCON2                 |                                                    |

|        | BSF          | NVMCON1,WR              |                                                    |

|        | BSF          | INTCON,GIE              | ; Unlock sequence complete, re-enable interrupts   |

|        | return       |                         |                                                    |

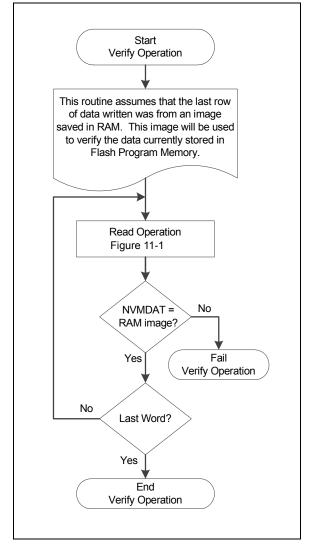

#### 11.4.8 WRITE VERIFY

It is considered good programming practice to verify that program memory writes agree with the intended value. Since program memory is stored as a full row, then the stored program memory contents are compared with the intended data stored in RAM after the last write is complete.

FIGURE 11-7: PROGRAM FLASH MEMORY VERIFY FLOWCHART

| Name                  | Bit 7                 | Bit 6                 | Bit 5    | Bit 4     | Bit 3        | Bit 2  | Bit 1     | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|----------|-----------|--------------|--------|-----------|--------|---------------------|

| TRISA                 | _                     | — TRISA5              |          | TRISA4    | (2)          | TRISA2 | TRISA1    | TRISA0 | 140                 |

| ANSELA                |                       | _                     | ANSA5    | ANSA4     | _            | ANSA2  | ANSA1     | ANSA0  | 141                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5   | TRISB4    | —            | —      | —         | —      | 146                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                 | ANSB5    | ANSB4     | —            | —      | —         | —      | 147                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5   | TRISC4    | TRISC3       | TRISC2 | TRISC1    | TRISC0 | 153                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5    | ANSC4     | ANSC3        | ANSC2  | ANSC1     | ANSC0  | 154                 |

| PIR2                  | TMR6IF                | C2IF                  | C1IF     | NVMIF     | —            | —      | TMR4IF    | NCO1IF | 106                 |

| PIE2                  | TMR6IE                | C2IE                  | C1IE     | NVMIE     | —            | —      | TMR4IE    | NCO1IE | 101                 |

| INTCON                | GIE                   | PEIE                  |          | _         | _            | _      | —         | INTEDG | 98                  |

| NCO1CON               | N1EN                  | _                     | N1OUT    | N1POL     | _            | _      | _         | N1PFM  | 253                 |

| NCO1CLK               |                       | N1PWS<2:0             | )>       | _         | _            | _      | N1CK      | S<1:0> | 254                 |

| NCO1ACCL              |                       |                       | NC       | 01ACC <7  | :0>          |        |           |        | 254                 |

| NCO1ACCH              |                       |                       | NC       | 01ACC <15 | 5:8>         |        |           |        | 255                 |

| NCO1ACCU              |                       |                       | —        |           |              | NCO1AC | C <19:16> | •      | 255                 |

| NCO1INCL              |                       |                       | N        | CO1INC<7: | 0>           |        |           |        | 255                 |

| NCO1INCH              |                       |                       | NC       | CO1INC<15 | :8>          |        |           |        | 256                 |

| NCO1INCU              |                       |                       | —        |           |              | NCO1IN | C<19:16>  |        | 256                 |

| CWG1DAT               |                       |                       | _        | _         |              | DAT    | <3:0>     |        | 212                 |

| MDSRC                 |                       |                       | _        | _         |              | MDM    | S<3:0>    |        | 269                 |

| MDCARH                |                       | MDCHPOL               | MDCHSYNC | _         | MDCH<3:0>    |        |           |        | 270                 |

| MDCARL                |                       | MDCLPOL MDCLSYNC      |          | _         | MDCL<3:0>    |        |           |        | 271                 |

| CCPxCAP               |                       | _                     | _        | _         | CCPxCTS<3:0> |        |           |        | 307                 |

| TABLE 23-1: | SUMMARY OF REGISTERS ASSOCIATED WITH NCO1 |

|-------------|-------------------------------------------|

|-------------|-------------------------------------------|

**Legend:** – = unimplemented read as '0'. Shaded cells are not used for NCO1 module.

**Note 1:** PIC16(L)F18344 only.

2: Unimplemented, read as '1'.

# PIC16(L)F18324/18344

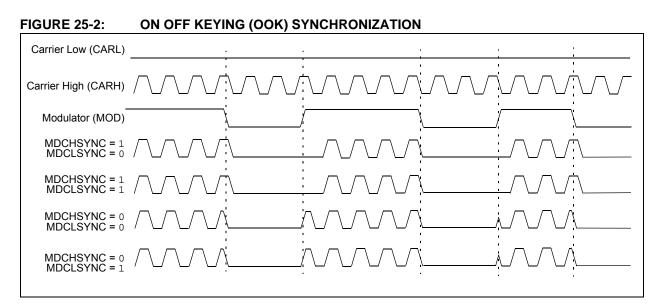

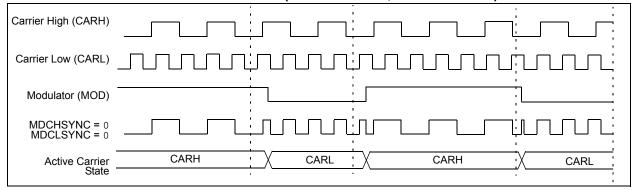

#### FIGURE 25-3: NO SYNCHRONIZATION (MDSHSYNC = 0, MDCLSYNC = 0)

#### FIGURE 25-4: CARRIER HIGH SYNCHRONIZATION (MDSHSYNC = 1, MDCLSYNC = 0)

| Carrier High (CARH)          |                                     |

|------------------------------|-------------------------------------|

| Carrier Low (CARL)           |                                     |

| Modulator (MOD)              |                                     |

| MDCHSYNC = 1<br>MDCLSYNC = 0 |                                     |

| Active Carrier<br>State      | CARH / both CARL / CARH / both CARL |

#### 25.5 Carrier Source Polarity Select

The signal provided from any selected input source for the carrier high and carrier low signals can be inverted. Inverting the signal for the carrier high source is enabled by setting the MDCHPOL bit of the MDCARH register. Inverting the signal for the carrier low source is enabled by setting the MDCLPOL bit of the MDCARL register.

#### 25.6 Programmable Modulator Data

The MDBIT of the MDCON register can be selected as the source for the modulator signal. This gives the user the ability to program the value used for modulation.

#### 25.7 Modulated Output Polarity

The modulated output signal provided on the DSM pin can also be inverted. Inverting the modulated output signal is enabled by setting the MDOPOL bit of the MDCON register.

#### 25.8 Slew Rate Control

The slew rate limitation on the output port pin can be disabled. The slew rate limitation can be removed by clearing the SLR bit of the SLRCON register associated with that pin. For example, clearing the slew rate limitation for pin RA5 would require clearing the SLRA5 bit of the SLRCONA register.

#### 25.9 Operation in Sleep Mode

The DSM module is not affected by Sleep mode. The DSM can still operate during Sleep, if the Carrier and Modulator input sources are also still operable during Sleep.

#### 25.10 Effects of a Reset

Upon any device Reset, the DSM module is disabled. The user's firmware is responsible for initializing the module before enabling the output. The registers are reset to their default values.

#### 26.8 Register Definitions: Timer0 Register

| R/W-0/0          | R/W-0/0 | R/W-0/0           | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0     |

|------------------|---------|-------------------|---------|----------------|------------------|------------------|-------------|

|                  |         |                   | TMR     | )L<7:0>        |                  |                  |             |

| bit 7            |         |                   |         |                |                  |                  | bit 0       |

|                  |         |                   |         |                |                  |                  |             |

| Legend:          |         |                   |         |                |                  |                  |             |

| R = Readable     | bit     | W = Writable      | bit     | U = Unimpler   | nented bit, read | l as '0'         |             |

| u = Bit is uncha | anged   | x = Bit is unkr   | nown    | -n/n = Value a | at POR and BO    | R/Value at all o | ther Resets |

| '1' = Bit is set |         | '0' = Bit is clea | ared    |                |                  |                  |             |

#### REGISTER 26-1: TMR0L: TIMER0 COUNT REGISTER

bit 7-0 TMR0L<7:0>:TMR0 Counter bits 7..0

#### REGISTER 26-2: TMR0H: TIMER0 PERIOD REGISTER

| R/W-1/1                  | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 | R/W-1/1 |  |

|--------------------------|---------|---------|---------|---------|---------|---------|---------|--|

| TMR0H<7:0> or TMR0<15:8> |         |         |         |         |         |         |         |  |

| bit 7                    | bit 7   |         |         |         |         |         |         |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 When T016BIT = 0 TMR0H<7:0>:TMR0 Period Register bits 7..0 When T016BIT = 1 TMR0<15:8>: TMR0 Counter bits 15..8

© 2015-2016 Microchip Technology Inc.

| R/W-0/0                                                                                        | R/W-0/0                                                                                                                                                                                                                                    | R/W-0/0                               | R/W-0/0        | R/W-0/0      | R/W-0/0          | R/W-0/0  | R/W-0/0      |

|------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------|----------------|--------------|------------------|----------|--------------|

|                                                                                                | T0CS<2:0>                                                                                                                                                                                                                                  |                                       | TOASYNC        |              | TOCKF            | °S<3:0>  |              |

| bit 7                                                                                          |                                                                                                                                                                                                                                            |                                       |                |              |                  |          | bit (        |

| Legend:                                                                                        |                                                                                                                                                                                                                                            |                                       |                |              |                  |          |              |

| R = Readable                                                                                   | e bit                                                                                                                                                                                                                                      | W = Writable                          | bit            | U = Unimpler | nented bit, read | l as '0' |              |

| u = Bit is uncl                                                                                |                                                                                                                                                                                                                                            | x = Bit is unkr                       |                | •            | at POR and BO    |          | other Resets |

| '1' = Bit is set                                                                               | -                                                                                                                                                                                                                                          | '0' = Bit is clea                     |                |              |                  |          |              |

| bit 7-5                                                                                        | 000 = TOCKI<br>001 = TOCKI                                                                                                                                                                                                                 | PPS (Inverted)                        | ource select b | its          |                  |          |              |

| 010 = Fosc/4<br>011 = HFINTOSC<br>100 = LFINTOSC<br>101 = Reserved<br>110 = SOSC<br>111 = CLC1 |                                                                                                                                                                                                                                            |                                       |                |              |                  |          |              |

| bit 4                                                                                          | <b>TOASYNC:</b> TMR0 Input Asynchronization Enable bit<br>1 = The input to the TMR0 counter is not synchronized to system clocks<br>0 = The input to the TMR0 counter is synchronized to Fosc/4                                            |                                       |                |              |                  |          |              |

| bit 3-0                                                                                        | <b>TOCKPS&lt;3:0</b><br>0000 = 1:1<br>0001 = 1:2<br>0010 = 1:4<br>0011 = 1:8<br>0100 = 1:16<br>0101 = 1:32<br>0110 = 1:64<br>0111 = 1:1256<br>1001 = 1:512<br>1010 = 1:102<br>1011 = 1:204<br>1100 = 1:405<br>1110 = 1:163<br>1111 = 1:327 | 5<br>2<br>24<br>48<br>96<br>92<br>384 | ate Select bit |              |                  |          |              |

#### REGISTER 26-4: T0CON1: TIMER0 CONTROL REGISTER 1

#### 27.1 Timer1 Operation

The Timer1 module is a 16-bit incrementing timer which is accessed through the TMR1H:TMR1L register pair. Writes to TMR1H or TMR1L directly update the timer.

The module can be used with either internal or external clock sources, and has the Timer1 Gate Enable function. When Timer1 is used with the Timer1 Gate Enable, the timer can measure time intervals or count signal pulses between two points of interest. When used without the Timer1 Gate Enable, the timer simply measures time intervals.

Timer1 is enabled by configuring the TMR1ON and TMR1GE bits in the T1CON and T1GCON registers, respectively. Table 27-1 displays the Timer1 enable selections.

### TABLE 27-1: TIMER1 ENABLE SELECTIONS

| TMR10N | TMR1GE | Timer1<br>Operation |

|--------|--------|---------------------|

| 0      | 0      | Off                 |

| 0      | 1      | Off                 |

| 1      | 0      | Always On           |

| 1      | 1      | Count Enabled       |

### 27.2 Clock Source Selection

The TMR1CS<1:0> and T1OSC bits of the T1CON register are used to select the clock source for Timer1. Table 27-2 displays the clock source selections. The TMR1H:TMR1L register pair will increment on multiples of the clock source as determined by the Timer1 prescaler.

When either the Fosc or LFINTOSC clock source is selected, the TMR1H:TMR1L register pair will increment every rising clock edge. Reading from the TMR1H:TMR1L register pair when either the Fosc or LFINTOSC is the clock source will cause a 2 LSb loss in resolution, which can be mitigated by using an asynchronous input signal to gate the Timer1 clock input (see Section 26.5 "Operation During Sleep" for more information on the Timer1 Gate Enable).

When the Fosc/4 clock source is selected, the TMR1H:TMR1L register pair increments every instruction cycle (once every four Fosc pulses).

In addition to the internal clock sources, Timer1 has a dedicated external clock input pin, T1CKI. T1CKI can be either synchronized to the system clock or can run asynchronously via the T1SYNC bit of the T1CON register. When the T1CKI pin is used as the clock source, the TMR1H:TMR1L register pair increments on the rising edge of the T1CKI clock input.

| Note: | When using Timer1 to count events, a falling edge must be registered by the counter prior to the first incrementing rising edge after any one or more of the |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------|

|       | following conditions:                                                                                                                                        |

- Timer1 enabled after POR

- Write to TMR1H or TMR1L

- Timer1 is disabled

- Timer1 is disabled (TMR1ON = 0) when T1CKI is high then Timer1 is enabled (TMR1ON=1) when T1CKI is low.

#### TABLE 27-2: CLOCK SOURCE SELECTIONS

| TMR1CS<1:0> | Clock Source                   |  |  |  |

|-------------|--------------------------------|--|--|--|

| 11          | LFINTOSC                       |  |  |  |

| 10          | External Clocking on T1CKI Pin |  |  |  |

| 01          | System Clock (Fosc)            |  |  |  |

| 00          | Instruction Clock (Fosc/4)     |  |  |  |

#### 29.2.2 TIMER1/3/5 MODE RESOURCE

Timer1/3/5 must be running in Timer mode or Synchronized Counter mode for the CCP module to use the capture feature. In Asynchronous Counter mode, the capture operation may not work.

See Section 27.0 "Timer1/3/5 Module with Gate Control" for more information on configuring Timer1/3/5.

**Note:** Clocking Timer1/3/5 from the system clock (Fosc) should not be used in Capture mode. In order for Capture mode to recognize the trigger event on the CCPx pin, Timer1/3/5 must be clocked from the instruction clock (Fosc/4) or from an external clock source.

#### 29.2.3 SOFTWARE INTERRUPT MODE

When the Capture mode is changed, a false capture interrupt may be generated. The user should keep the CCPxIE interrupt enable bit of the PIE4 register clear to avoid false interrupts. Additionally, the user should clear the CCPxIF interrupt flag bit of the PIR4 register following any change in Operating mode.

#### 29.2.4 CCP PRESCALER

There are four prescaler settings specified by the CCPxMODE<3:0> bits of the CCPxCON register. Whenever the CCP module is turned off, or the CCP module is not in Capture mode, the prescaler counter is cleared. Any Reset will clear the prescaler counter.

Switching from one capture prescaler to another does not clear the prescaler and may generate a false interrupt. To avoid this unexpected operation, turn the module off by clearing the CCPxCON register before changing the prescaler. Example 29-1 demonstrates the code to perform this function.

#### EXAMPLE 29-1: CHANGING BETWEEN CAPTURE PRESCALERS

| BANKSEL | CCPxCON     | ;Set Bank bits to point |

|---------|-------------|-------------------------|

|         |             | ;to CCPxCON             |

| CLRF    | CCPxCON     | ;Turn CCP module off    |

| MOVLW   | NEW_CAPT_PS | ;Load the W reg with    |

|         |             | ;the new prescaler      |

|         |             | ;move value and CCP ON  |

| MOVWF   | CCPxCON     | ;Load CCPxCON with this |

|         |             | ;value                  |

|         |             |                         |

#### 29.2.5 CAPTURE DURING SLEEP

Capture mode depends upon the Timer1/3/5 module for proper operation. There are two options for driving the Timer1/3/5 module in Capture mode. It can be driven by the instruction clock (Fosc/4), or by an external clock source.

When Timer1/3/5 is clocked by Fosc/4, Timer1/3/5 will not increment during Sleep. When the device wakes from Sleep, Timer1/3/5 will continue from its previous state.

Capture mode will operate during Sleep when Timer1/3/5 is clocked by an external clock source.

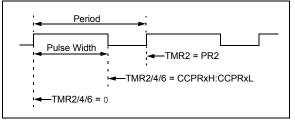

#### 29.4 PWM Overview

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the on state and the low portion of the signal is considered the off state. The high portion, also known as the pulse width, can vary in time and is defined in steps. A larger number of steps applied, which lengthens the pulse width, also supplies more power to the load. Lowering the number of steps applied, which shortens the pulse width, supplies less power. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse-width time and in turn the power that is applied to the load.

The term duty cycle describes the proportion of the on time to the off time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied.

Figure 29-3 shows a typical waveform of the PWM signal.

SIMPLIFIED PWM BLOCK DIAGRAM

**FIGURE 29-4:**

#### 29.4.1 STANDARD PWM OPERATION

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the CCPx pin with up to 10 bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- PR2/4/6 registers

- T2/4/6CON registers

- CCPRxL registers

- CCPxCON registers

Figure 29-4 shows a simplified block diagram of PWM operation.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the CCPx pin.

#### FIGURE 29-3: CCP PWM OUTPUT SIGNAL

#### Rev. 10-000157B 2/27/2014 Duty cycle registers CCPRxH CCPRxL CCPx\_out To Peripherals set CCPIF 10-bit Latch<sup>(2)</sup> (Not accessible by user) Comparator R CCPx Q s TRIS Control TMR2 Module R TMR2 (1) **ERS** logic CCPx\_pset Comparator PR2 1. 8-bit timer is concatenated with two bits generated by Fosc or two bits of the internal prescaler to Notes: create 10-bit time-base. 2. The alignment of the 10 bits from the CCPR register is determined by the CCPxFMT bit.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends a NACK in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send a Restart condition in place of the Stop bit or last ACK bit when it is in Receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

#### 30.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

#### 30.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

| R/C/HS-0/0       | R/C/HS-0/0                                                                                                                                                            | R/W-0/0                                                                                                            | R/W-0/0                                                                          | R/W-0/0                                                    | R/W-0/0                                                                                                       | R/W-0/0                                               | R/W-0/0                                           |

|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|---------------------------------------------------|

| WCOL             | SSPOV <sup>(1)</sup>                                                                                                                                                  | SSPEN                                                                                                              | CKP                                                                              |                                                            | SSPN                                                                                                          | <3:0>                                                 |                                                   |

| bit 7            |                                                                                                                                                                       |                                                                                                                    | 1                                                                                | •                                                          |                                                                                                               |                                                       | bit C                                             |

|                  |                                                                                                                                                                       |                                                                                                                    |                                                                                  |                                                            |                                                                                                               |                                                       |                                                   |

| Legend:          |                                                                                                                                                                       |                                                                                                                    |                                                                                  |                                                            |                                                                                                               |                                                       |                                                   |

| R = Readable     | bit                                                                                                                                                                   | W = Writable                                                                                                       | bit                                                                              | U = Unimplen                                               | nented bit, read                                                                                              | as '0'                                                |                                                   |

| u = Bit is unch  | anged                                                                                                                                                                 | x = Bit is unki                                                                                                    | nown                                                                             |                                                            | at POR and BO                                                                                                 |                                                       |                                                   |

| '1' = Bit is set |                                                                                                                                                                       | '0' = Bit is cle                                                                                                   | ared                                                                             | HS = Bit is se                                             | et by hardware                                                                                                | C = User clea                                         | red                                               |

| bit 7<br>bit 6   | 1 = The SSPI<br>0 = No collisi                                                                                                                                        |                                                                                                                    | vritten while it is                                                              |                                                            | the previous wo                                                                                               | rd (must be clea                                      | red in software                                   |

|                  | the data in<br>the SSPE<br>is not set<br>(must be<br>0 = No overfil<br><u>In I<sup>2</sup>C mode:</u><br>1 = A byte is                                                | n SSPSR is los<br>BUF, even if only<br>since each nev<br>cleared in softw<br>ow<br>received while<br>fransmit mode | t. Overflow car<br>/ transmitting d<br>v reception (an<br>vare).<br>• the SSPBUF | n only occur in S<br>lata, to avoid set<br>d transmission) | I holding the prev<br>lave mode. In SI-<br>tting overflow. In<br>is initiated by wr<br>holding the prev<br>). | ave mode, the u<br>Master mode, t<br>iting to the SSF | user must reac<br>he overflow bi<br>PBUF register |

| bit 5            | In both mode:<br>In SPI mode:<br>1 = Enables s<br>0 = Disables<br>In I <sup>2</sup> C mode:<br>1 = Enables s                                                          | serial port and c<br>serial port and<br>he serial port ar                                                          | ed, the followir<br>configures SCk<br>configures th<br>nd configures th          | ng pins must be<br>K, SDO, SDI and<br>ese pins as I/O      | L pins as the sou                                                                                             | ce of the serial                                      | port pins <sup>(2)</sup>                          |

| bit 4            | $\frac{\text{In SPI mode:}}{1 = \text{Idle state}}$ $0 = \text{Idle state}$ $\frac{\text{In I}^2 \text{C Slave r}}{\text{SCL release of}}$ $1 = \text{Enable closed}$ | control<br>ock<br>ck low (clock s<br><u>mode:</u>                                                                  | igh level<br>ow level                                                            | to ensure data                                             | setup time.)                                                                                                  |                                                       |                                                   |

#### 31.1 EUSART1 Asynchronous Mode

The EUSART1 transmits and receives data using the standard non-return-to-zero (NRZ) format. NRZ is implemented with two levels: a VOH Mark state which represents a '1' data bit, and a VoL Space state which represents a '0' data bit. NRZ refers to the fact that consecutively transmitted data bits of the same value stay at the output level of that bit without returning to a neutral level between each bit transmission. An NRZ transmission port idles in the Mark state. Each character transmission consists of one Start bit followed by eight or nine data bits and is always terminated by one or more Stop bits. The Start bit is always a space and the Stop bits are always marks. The most common data format is eight bits. Each transmitted bit persists for a period of 1/(Baud Rate). An on-chip dedicated 8-bit/16-bit Baud Rate Generator is used to derive standard baud rate frequencies from the system oscillator. See Table 31-3 for examples of baud rate configurations.

The EUSART1 transmits and receives the LSb first. The EUSART1's transmitter and receiver are functionally independent, but share the same data format and baud rate. Parity is not supported by the hardware, but can be implemented in software and stored as the ninth data bit.

#### 31.1.1 EUSART ASYNCHRONOUS TRANSMITTER

The EUSART1 transmitter block diagram is shown in Figure 31-1. The heart of the transmitter is the serial Transmit Shift Register (TSR), which is not directly accessible by software. The TSR obtains its data from the transmit buffer, which is the TX1REG register.

#### 31.1.1.1 Enabling the Transmitter

The EUSART1 transmitter is enabled for asynchronous operations by configuring the following three control bits:

- TXEN = 1

- SYNC = 0

- SPEN = 1

All other EUSART1 control bits are assumed to be in their default state.

Setting the TXEN bit of the TX1STA register enables the transmitter circuitry of the EUSART1. Clearing the SYNC bit of the TX1STA register configures the EUSART1 for asynchronous operation. Setting the SPEN bit of the RC1STA register enables the EUSART1 and automatically configures the TX/CK I/O pin as an output. If the TX/CK pin is shared with an analog peripheral, the analog I/O function must be disabled by clearing the corresponding ANSEL bit.

**Note:** The TXIF Transmitter Interrupt flag is set when the TXEN enable bit is set.

#### 31.1.1.2 Transmitting Data

A transmission is initiated by writing a character to the TX1REG register. If this is the first character, or the previous character has been completely flushed from the TSR, the data in the TX1REG is immediately transferred to the TSR register. If the TSR still contains all or part of a previous character, the new character data is held in the TX1REG until the Stop bit of the previous character has been transmitted. The pending character in the TX1REG is then transferred to the TSR in one TcY immediately following the Stop bit sequence commences immediately following the transfer of the data to the TSR from the TX1REG.

#### 31.1.1.3 Transmit Data Polarity

The polarity of the transmit data can be controlled with the SCKP bit of the BAUD1CON register. The default state of this bit is '0' which selects high true transmit idle and data bits. Setting the SCKP bit to '1' will invert the transmit data resulting in low true idle and data bits. The SCKP bit controls transmit data polarity in Asynchronous mode only. In Synchronous mode, the SCKP bit has a different function. See **Section 31.4.1.2 "Clock Polarity"**.

#### 31.1.1.4 Transmit Interrupt Flag

The TXIF interrupt flag bit of the PIR1 register is set whenever the EUSART1 transmitter is enabled and no character is being held for transmission in the TX1REG. In other words, the TXIF bit is only clear when the TSR is busy with a character and a new character has been queued for transmission in the TX1REG. The TXIF flag bit is not cleared immediately upon writing TX1REG. TXIF becomes valid in the second instruction cycle following the write execution. Polling TXIF immediately following the TX1REG write will return invalid results. The TXIF bit is read-only, it cannot be set or cleared by software.

The TXIF interrupt can be enabled by setting the TXIE interrupt enable bit of the PIE1 register. However, the TXIF flag bit will be set whenever the TX1REG is empty, regardless of the state of TXIE enable bit.

To use interrupts when transmitting data, set the TXIE bit only when there is more data to send. Clear the TXIE interrupt enable bit upon writing the last character of the transmission to the TX1REG.

#### 31.2 Clock Accuracy with Asynchronous Operation

The factory calibrates the internal oscillator block output (INTOSC). However, the INTOSC frequency may drift as VDD or temperature changes, and this directly affects the asynchronous baud rate. Two methods may be used to adjust the baud rate clock, but both require a reference clock source of some kind.

The first (preferred) method uses the OSCTUNE register to adjust the INTOSC output. Adjusting the value in the OSCTUNE register allows for fine resolution changes to the system clock source. See **Section 7.2.2.3 "Internal Oscillator Frequency Adjustment"** for more information.

The other method adjusts the value in the Baud Rate Generator. This can be done automatically with the Auto-Baud Detect feature (see **Section 31.3.1 "Auto-Baud Detect"**). There may not be fine enough resolution when adjusting the Baud Rate Generator to compensate for a gradual change in the peripheral clock frequency.

#### 31.3 EUSART1 Baud Rate Generator (BRG)

The Baud Rate Generator (BRG) is an 8-bit or 16-bit timer that is dedicated to the support of both the asynchronous and synchronous EUSART1 operation. By default, the BRG operates in 8-bit mode. Setting the BRG16 bit of the BAUD1CON register selects 16-bit mode.

The SP1BRGH, SP1BRGL register pair determines the period of the free running baud rate timer. In Asynchronous mode the multiplier of the baud rate period is determined by both the BRGH bit of the TX1STA register and the BRG16 bit of the BAUD1CON register. In Synchronous mode, the BRGH bit is ignored.

Table 31-1 contains the formulas for determining the baud rate. Example 31-1 provides a sample calculation for determining the baud rate and baud rate error.

Typical baud rates and error values for various asynchronous modes have been computed for your convenience and are shown in Table 31-3. It may be advantageous to use the high baud rate (BRGH = 1), or the 16-bit BRG (BRG16 = 1) to reduce the baud rate error. The 16-bit BRG mode is used to achieve slow baud rates for fast oscillator frequencies.

Writing a new value to the SP1BRGH, SP1BRGL register pair causes the BRG timer to be reset (or cleared). This ensures that the BRG does not wait for a timer overflow before outputting the new baud rate.

If the system clock is changed during an active receive operation, a receive error or data loss may result. To avoid this problem, check the status of the RCIDL bit to make sure that the receive operation is idle before changing the system clock.

#### EXAMPLE 31-1: CALCULATING BAUD RATE ERROR

For a device with Fosc of 16 MHz, desired baud rate of 9600, Asynchronous mode, 8-bit SPR1BRG:

Desired Baud Rate =  $\frac{FOSC}{64([SPBRGH:SPBRGL] + 1)}$

Solving for SP1BRGH:SP1BRGL:

$X = \frac{Fosc}{Desired Baud Rate}{64} - 1$  $= \frac{1600000}{9600}{-1}$ = [25.042] = 25Calculated Baud Rate =  $\frac{1600000}{64(25+1)}$ = 9615Error =  $\frac{Calc. Baud Rate - Desired Baud Rate}{Desired Baud Rate}$  $= \frac{(9615 - 9600)}{9600} = 0.16\%$

© 2015-2016 Microchip Technology Inc.

#### 31.4.1.6 Slave Clock

Synchronous data transfers use a separate clock line, which is synchronous with the data. A device configured as a slave receives the clock on the TX/CK line. The TX/CK pin output driver is automatically disabled when the device is configured for synchronous slave transmit or receive operation. Serial data bits change on the leading edge to ensure they are valid at the trailing edge of each clock. One data bit is transferred for each clock cycle. Only as many clock cycles should be received as there are data bits.

| Note: | If the device is configured as a slave and  |

|-------|---------------------------------------------|

|       | the TX/CK function is on an analog pin, the |

|       | corresponding ANSEL bit must be cleared.    |

#### 31.4.1.7 Receive Overrun Error

The receive FIFO buffer can hold two characters. An overrun error will be generated if a third character, in its entirety, is received before RC1REG is read to access the FIFO. When this happens the OERR bit of the RC1STA register is set. Previous data in the FIFO will not be overwritten. The two characters in the FIFO buffer can be read, however, no additional characters will be received until the error is cleared. The OERR bit can only be cleared by clearing the Overrun condition. If the overrun error occurred when the SREN bit is set and CREN is clear then the error is cleared by reading RC1REG. If the overrun occurred when the CREN bit is set then the Error condition is cleared by either clearing the CREN bit of the RC1STA register or by clearing the SPEN bit which resets the EUSART1.

#### 31.4.1.8 Receiving 9-bit Characters

The EUSART1 supports 9-bit character reception. When the RX9 bit of the RC1STA register is set the EUSART1 will shift nine bits into the RSR for each character received. The RX9D bit of the RC1STA register is the ninth, and Most Significant, data bit of the top unread character in the receive FIFO. When reading 9-bit data from the receive FIFO buffer, the RX9D data bit must be read before reading the eight Least Significant bits from the RC1REG.

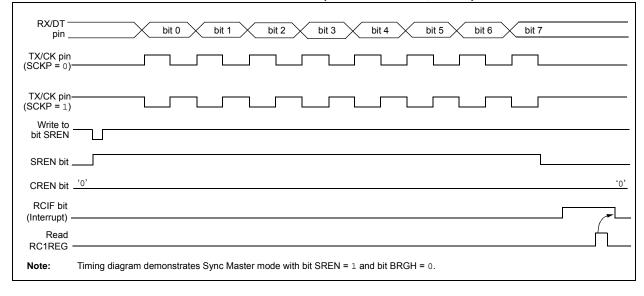

## 31.4.1.9 Synchronous Master Reception Set-up

- 1. Initialize the SP1BRGH, SP1BRGL register pair for the appropriate baud rate. Set or clear the BRGH and BRG16 bits, as required, to achieve the desired baud rate.

- 2. Clear the ANSEL bit for the RX pin (if applicable).

- 3. Enable the synchronous master serial port by setting bits SYNC, SPEN and CSRC.

- 4. Ensure bits CREN and SREN are clear.

- 5. If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 6. If 9-bit reception is desired, set bit RX9.

- 7. Start reception by setting the SREN bit or for continuous reception, set the CREN bit.

- 8. Interrupt flag bit RCIF will be set when reception of a character is complete. An interrupt will be generated if the enable bit RCIE was set.

- 9. Read the RC1STA register to get the ninth bit (if enabled) and determine if any error occurred during reception.

- 10. Read the 8-bit received data by reading the RC1REG register.

- 11. If an overrun error occurs, clear the error by either clearing the CREN bit of the RC1STA register or by clearing the SPEN bit which resets the EUSART1.

#### FIGURE 31-12: SYNCHRONOUS RECEPTION (MASTER MODE, SREN)