#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

-XF

| Product Status             | Active                                                                      |

|----------------------------|-----------------------------------------------------------------------------|

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 16-UQFN Exposed Pad                                                         |

| Supplier Device Package    | 16-UQFN (4x4)                                                               |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18324t-i-jq |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

#### **PIN ALLOCATION TABLES**

# Preliminary

| (Z) | 14-Pin PDIP/SOIC/TSSOP | 16-Pin UQFN | ADC  | Reference | Comparator       | NCO | DAC      | WSQ                   | Timers                                  | CCP                 | PWM | CWG                                            | MSSP                                           | EUSART            | CLC                   | CLKR | Interrupt                 | Pull-up | Basic              |

|-----|------------------------|-------------|------|-----------|------------------|-----|----------|-----------------------|-----------------------------------------|---------------------|-----|------------------------------------------------|------------------------------------------------|-------------------|-----------------------|------|---------------------------|---------|--------------------|

| RA0 | 13                     | 12          | ANA0 |           | C1IN0+           |     | DAC1OUT  | —                     |                                         | —                   | —   | —                                              | _                                              | —                 | —                     |      | IOC                       | Y       | ICDDAT/<br>ICSPDAT |

| RA1 | 12                     | 11          | ANA1 | VREF+     | C1IN0-<br>C2IN0- |     | DAC1REF+ | _                     |                                         | —                   | _   | _                                              | _                                              | _                 | _                     |      | IOC                       | Y       | ICDCLK/<br>ICSPCLK |

| RA2 | 11                     | 10          | ANA2 | VREF-     | -                | —   | DAC1REF- | -                     | тоскі <sup>(1)</sup>                    | CCP3 <sup>(1)</sup> | _   | CWG1IN <sup>(1)</sup><br>CWG2IN <sup>(1)</sup> | -                                              | —                 | —                     | _    | INT <sup>(1)</sup><br>IOC | Y       | —                  |

| RA3 | 4                      | 3           | -    |           | -                | _   | —        | —                     | _                                       | —                   | _   | _                                              |                                                | —                 | —                     | _    | IOC                       | Y       | MCLR<br>VPP        |

| RA4 | 3                      | 2           | ANA4 | -         | -                | —   | -        | —                     | T1G <sup>(1)</sup><br>SOSCO             | -                   | —   | -                                              |                                                | _                 | -                     | _    | IOC                       | Y       | CLKOUT<br>OSC2     |

| RA5 | 2                      | 1           | ANA5 | _         | _                | _   | _        | —                     | T1CKI <sup>(1)</sup><br>SOSCIN<br>SOSCI | —                   | —   | -                                              |                                                | —                 | CLCIN3 <sup>(1)</sup> | —    | IOC                       | Y       | CLKIN<br>OSC1      |

| RC0 | 10                     | 9           | ANC0 | _         | C2IN0+           | —   | —        | —                     | T5CKI <sup>(1)</sup>                    | -                   | _   | _                                              | SCK1 <sup>(1)</sup><br>SCL1 <sup>(1,3,4)</sup> | —                 | —                     | _    | IOC                       | Y       | —                  |

| RC1 | 9                      | 8           | ANC1 |           | C1IN1-<br>C2IN1- | —   | —        | —                     | _                                       | CCP4 <sup>(1)</sup> | —   | _                                              | SDI1 <sup>(1)</sup><br>SDA1 <sup>(1,3,4)</sup> | —                 | CLCIN2 <sup>(1)</sup> | _    | IOC                       | Y       | —                  |

| RC2 | 8                      | 7           | ANC2 | l         | C1IN2-<br>C2IN2- |     | _        | MDCIN1 <sup>(1)</sup> |                                         | —                   | —   | _                                              | _                                              | _                 | _                     |      | IOC                       | Y       |                    |

| RC3 | 7                      | 6           | ANC3 | 1         | C1IN3-<br>C2IN3- |     | _        | MDMIN <sup>(1)</sup>  | T5G <sup>(1)</sup>                      | CCP2 <sup>(1)</sup> | _   | _                                              | SS1 <sup>(1)</sup>                             | _                 | CLCIN0 <sup>(1)</sup> |      | IOC                       | Y       |                    |

| RC4 | 6                      | 5           | ANC4 |           |                  |     | _        |                       | T3G <sup>(1)</sup>                      | _                   | _   | _                                              | _                                              | _                 | CLCIN1 <sup>(1)</sup> |      | IOC                       | Y       |                    |

| RC5 | 5                      | 4           | ANC5 | _         | _                | _   | _        | MDCIN2 <sup>(1)</sup> | T3CKI <sup>(1)</sup>                    | CCP1 <sup>(1)</sup> | _   | _                                              | _                                              | RX <sup>(1)</sup> |                       | _    | IOC                       | Y       | _                  |

| Vdd | 1                      | 16          | _    | _         | _                | —   | —        | —                     | —                                       | —                   | —   | —                                              | —                                              | _                 | —                     |      | _                         | _       | Vdd                |

| Vss | 14                     | 13          | _    | _         |                  | _   | _        | —                     | —                                       | _                   | _   | _                                              | _                                              |                   | _                     | —    | —                         | -       | Vss                |

TABLE 1: 14/16-PIN ALLOCATION TABLE (PIC16(L)F18324)

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers.

3: These peripheral functions are bidirectional. The output pin selections must be the same as the input pin selections.

4: These pins are configured for I<sup>2</sup>C logic levels; clock and data signals may be assigned to any of these pins. Assignments to the other pins (e.g., RA5) will operate, but logic levels will be standard TTL/ ST as selected by the INLVL register.

| Name                                                                | Function | Input<br>Type | Output Type | Description                                           |

|---------------------------------------------------------------------|----------|---------------|-------------|-------------------------------------------------------|

| RA0/ANA0/C1IN0+/DAC1OUT/                                            | RA0      | TTL/ST        | CMOS        | General purpose I/O.                                  |

| ICDDAT/ICSPDAT                                                      | ANA0     | AN            | _           | ADC Channel A0 input.                                 |

|                                                                     | C1IN0+   | AN            | _           | Comparator C1 positive input.                         |

|                                                                     | DAC1OUT  | _             | AN          | Digital-to-Analog Converter output.                   |

|                                                                     | ICDDAT   | TTL/ST        | CMOS        | In-Circuit Debug Data I/O.                            |

|                                                                     | ICSPDAT  | TTL/ST        | CMOS        | ICSP™ Data I/O.                                       |

| RA1/ANA1/VREF+/C1IN0-/                                              | RA1      | TTL/ST        | CMOS        | General purpose I/O.                                  |

| C2IN0-/DAC1REF+/ ICDCLK/                                            | ANA1     | AN            | _           | ADC Channel A1 input.                                 |

| ICSPCLK                                                             | VREF+    | AN            | _           | ADC positive voltage reference input.                 |

|                                                                     | C1IN0-   | AN            | —           | Comparator C1 negative input.                         |

|                                                                     | C2IN0-   | AN            |             | Comparator C2 negative input.                         |

|                                                                     | DAC1REF+ | _             | AN          | Digital-to-Analog Converter positive reference input. |

|                                                                     | ICDCLK   | TTL/ST        | CMOS        | In-Circuit Debug Clock I/O.                           |

|                                                                     | ICSPCLK  | TTL/ST        | CMOS        | ICSP Clock I/O.                                       |

| RA2/ANA2/VREF-/ DAC1REF-/                                           | RA2      | TTL/ST        | CMOS        | General purpose I/O.                                  |

| T0CKI <sup>(1)</sup> / CCP3 <sup>(1)</sup> /CWG1IN <sup>(1)</sup> / | ANA2     | AN            |             | ADC Channel A2 input.                                 |

| CWG2IN <sup>(1)</sup> /INT <sup>(1)</sup>                           | VREF-    | AN            |             | ADC negative voltage reference input.                 |

|                                                                     | DAC1REF- | _             | AN          | Digital-to-Analog Converter negative reference input  |

|                                                                     | TOCKI    | TTL/ST        |             | TMR0 Clock input.                                     |

|                                                                     | CCP3     | TTL/ST        | CMOS        | Capture/Compare/PWM 3 input.                          |

|                                                                     | CWG1IN   | TTL/ST        |             | Complementary Waveform Generator 1 input.             |

|                                                                     | CWG2IN   | TTL/ST        | _           | Complementary Waveform Generator 2 input.             |

|                                                                     | INT      | TTL/ST        | —           | External interrupt input.                             |

| RA3/MCLR/VPP                                                        | RA3      | TTL/ST        | CMOS        | General purpose I/O.                                  |

|                                                                     | MCLR     | TTL/ST        | _           | Master Clear with internal pull-up.                   |

|                                                                     | Vpp      | HV            | _           | Programming voltage.                                  |

| RA4/ANA4/T1G <sup>(1)</sup> / SOSCO/                                | RA4      | TTL/ST        | CMOS        | General purpose I/O.                                  |

| CLKOUT/OSC2                                                         | ANA4     | AN            | —           | ADC Channel A4 input.                                 |

|                                                                     | T1G      | ST            | —           | TMR1 gate input.                                      |

|                                                                     | SOSCO    | _             | XTAL        | Secondary Oscillator connection.                      |

|                                                                     | CLKOUT   | _             | CMOS        | Fosc/4 output.                                        |

|                                                                     | OSC2     | _             | XTAL        | Crystal/Resonator (LP, XT, HS modes).                 |

| RA5/ANA5/T1CKI <sup>(1)</sup> / SOSCIN/                             | RA5      | TTL/ST        | CMOS        | General purpose I/O.                                  |

| SOSCI/ CLCIN3 <sup>(1)</sup> /CLKIN/                                | ANA5     | AN            | —           | ADC Channel A5 input.                                 |

| OSC1                                                                | T1CKI    | TTL/ST        | _           | TMR1 Clock input.                                     |

|                                                                     | SOSCIN   | TTL/ST        | _           | Secondary Oscillator input connection.                |

|                                                                     | SOSCI    | XTAL          | _           | Secondary Oscillator connection.                      |

|                                                                     | CLCIN3   | TTL/ST        | _           | Configurable Logic Cell 3 input.                      |

|                                                                     | CLKIN    | TTL/ST        | _           | External clock input.                                 |

|                                                                     | OSC1     | XTAL          | _           | Crystal/Resonator (LP, XT, HS modes).                 |

Legend: AN = Analog input or output CMOS=CMOS compatible input or output OD = Open-Drain TTL = TTL compatible input ST = Schmitt Trigger input with CMOS levels I<sup>2</sup>C = Schmitt Trigger input with I<sup>2</sup>C

HV = High Voltage XTAL = Crystal levels

Note 1: Default peripheral input. Input can be moved to any other pin with the PPS input selection registers. See Register 13-1.

2: All pin outputs default to PORT latch data. Any pin can be selected as a digital peripheral output with the PPS output selection registers. See Register 13-2.

3: These I<sup>2</sup>C functions are bidirectional. The output pin selections must be the same as the input pin selections.

| TABLE               | 4-4: SPEC         | IAL F                            | UNCTION RE      | GISTER SU                                                          | JMMARY B       | ANKS 0-31 (       | CONTINUE          | <b>)</b> )        |                |       |                       |                                 |

|---------------------|-------------------|----------------------------------|-----------------|--------------------------------------------------------------------|----------------|-------------------|-------------------|-------------------|----------------|-------|-----------------------|---------------------------------|

| Address             | Name              | PIC16(L)F18324<br>PIC16(L)F18344 | Bit 7           | Bit 6                                                              | Bit 5          | Bit 4             | Bit 3             | Bit 2             | Bit 1          | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>resets |

| Bank 3              | 1 — only accessib | ole from                         | Debug Executive | e, unless other                                                    | wise specified |                   |                   |                   |                |       |                       |                                 |

|                     | 1                 |                                  |                 |                                                                    | CPU CORE RE    | EGISTERS; see 1   | Table 4-2 for spe | cifics            |                |       | 1                     |                                 |

| F8Ch to<br>FE3h     | -                 | -                                |                 |                                                                    |                | Unimple           | mented            |                   |                |       | _                     | —                               |

| FE4h <sup>(2)</sup> | STATUS_SHAD       |                                  | _               | _                                                                  | _              | —                 | _                 | Z                 | DC             | С     | xxx                   | uuu                             |

| FE5h <sup>(2)</sup> | WREG_SHAD         |                                  |                 |                                                                    | Worki          | ing Register Norn | nal (Non-ICD) Sh  | adow              |                |       | xxxx xxxx             | uuuu uuuu                       |

| FE6h <sup>(2)</sup> | BSR_SHAD          |                                  | _               | _                                                                  | _              |                   | Bank Select Reg   | jister Normal (No | on-ICD) Shadow |       | x xxxx                | u uuuu                          |

| FE7h <sup>(2)</sup> | PCLATH_SHAD       |                                  | _               |                                                                    | Progra         | am Counter Latch  | High Register No  | ormal (Non-ICD)   | Shadow         |       | -xxx xxxx             | -uuu uuuu                       |

| FE8h <sup>(2)</sup> | FSR0L_SHAD        |                                  |                 | Indirect Data Memory Address 0 Low Pointer Normal (Non-ICD) Shadow |                |                   |                   |                   |                |       |                       |                                 |

| FE9h <sup>(2)</sup> | FSR0H_SHAD        |                                  |                 | Indir                                                              | ect Data Memo  | ry Address 0 Hig  | n Pointer Normal  | (Non-ICD) Shad    | low            |       | xxxx xxxx             | uuuu uuuu                       |

| FEAh <sup>(2)</sup> | FSR1L_SHAD        |                                  |                 | Indi                                                               | rect Data Memo | ory Address 1 Lov | Pointer Normal    | (Non-ICD) Shad    | ow             |       | xxxx xxxx             | uuuu uuuu                       |

Indirect Data Memory Address 1 High Pointer Normal (Non-ICD) Shadow

Unimplemented

Top of Stack Low byte

Top of Stack High byte

Current Stack pointer

\_

x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', x = reserved. Shaded locations unimplemented, read as '0'.

© 2015-2016 Microchip Technology Inc.

DS40001800B-page 54

uuuu uuuu

---1 1111

XXXX XXXX

-xxx xxxx

XXXX XXXX

\_\_\_\_

---x xxxx

XXXX XXXX

-xxx xxxx

FEBh<sup>(2)</sup>

FEDh<sup>(2)</sup>

FEEh<sup>(2)</sup>

FEFh<sup>(2)</sup>

Legend:

Note 1:

2:

FECh

FSR1H\_SHAD

STKPTR

TOSL

TOSH

\_

Only on PIC16F18324/18344.

\_

Register accessible from both User and ICD Debugger.

#### 6.1 **Power-on Reset (POR)**

The POR circuit holds the device in Reset until VDD has reached an acceptable level for minimum operation. Slow rising VDD, fast operating speeds or analog performance may require greater than minimum VDD. The PWRT, BOR or MCLR features can be used to extend the start-up period until all device operation conditions have been met.

#### 6.2 Brown-out Reset (BOR)

The BOR circuit holds the device in Reset while VDD is below a selectable minimum level. Between the POR and BOR, complete voltage range coverage for execution protection can be implemented.

The Brown-out Reset module has four operating modes controlled by the BOREN<1:0> bits in Configuration Words. The four operating modes are:

- · BOR is always on

- BOR is off when in Sleep

- BOR is controlled by software

- BOR is always off

Refer to Table 6-1 for more information.

The Brown-out Reset voltage level is selectable by configuring the BORV bit in Configuration Words.

A VDD noise rejection filter prevents the BOR from triggering on small events. If VDD falls below VBOR for a duration greater than parameter TBORDC, the device will reset, and the BOR bit of the PCON0 register will be cleared, indicating that a Brown-out Reset condition occurred. See Figure 6-2 for more information.

| BOREN<1:0> | SBOREN | Device Mode | BOR Mode | Instruction Execution upon:<br>Release of POR or Wake-up from Sleep                                                                                                                                                                                                          |

|------------|--------|-------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 11         | X      | X           | Active   | In these specific cases, "Release of POR" and<br>"Wake-up from Sleep", there is no delay in start-up.<br>The BOR ready flag, (BORRDY = 1), will be set<br>before the CPU is ready to execute instructions<br>because the BOR circuit is forced on by the<br>BOREN<1:0> bits. |

| 1.0        | х      | Awake       | Active   | Waits for release of BOR (BORRDY = 1)                                                                                                                                                                                                                                        |

| 10         | A      | Sleep       | Disabled | BOR ignored when asleep                                                                                                                                                                                                                                                      |

| 01         | 1      | x           | Active   | In these specific cases, "Release of POR" and<br>"Wake-up from Sleep", there is no delay in start-up.<br>The BOR ready flag, (BORRDY = 1), will be set<br>before the CPU is ready to execute instructions<br>because the BOR circuit is forced on by the<br>BOREN<1:0> bits. |

|            | 0      | Х           | Disabled | Pagina immediately (POPPDV =)                                                                                                                                                                                                                                                |

| 00         | Х      | X           | Disabled | Begins immediately (BORRDY = x)                                                                                                                                                                                                                                              |

TABLE 6-1: BOR OPERATING MODES

© 2015-2016 Microchip Technology Inc.

#### 6.3 Low-Power Brown-out Reset (LPBOR)

The Low-Power Brown-Out Reset (LPBOR) circuit provides alternative protection against Brown-out conditions. When VDD falls below the LPBOR threshold, the device is held in Reset. When this occurs, the BOR bit of the PCON0 register is cleared to indicate that a Brown-out Reset occurred. The BOR bit will be cleared when either the BOR or the LPBOR circuitry detects a BOR condition. The LPBOR feature can be used with or without BOR enabled.

When used while BOR is enabled, the LPBOR can be used as a secondary protection circuit in case the BOR circuit fails to detect the BOR condition. Additionally, when BOR is enabled except while in Sleep (BOREN<1:0> = 10), the LPBOR circuit will hold the device in Reset while VDD is lower than the LPBOR threshold, and will also re-arm the POR. (see Table 35-11 for LPBOR Reset voltage levels).

When used without BOR enabled, the LPBOR circuit provides a single Reset trip point with the benefit of reduced current consumption.

#### 6.3.1 ENABLING LPBOR

The LPBOR is controlled by the LPBOR bit of Configuration Words. When the device is erased, the LPBOR module defaults to disabled.

#### 6.3.1.1 LPBOR Module Output

The output of the LPBOR module is a signal indicating whether or not a Reset is to be asserted. This signal is OR'd together with the Reset signal of the BOR module to provide the generic BOR signal, which goes to the PCON0 register and to the power control block.

#### 6.4 MCLR

The  $\overline{\text{MCLR}}$  is an <u>optional</u> external input that can reset the device. The  $\overline{\text{MCLR}}$  function is controlled by the MCLRE bit of Configuration Words and the LVP bit of Configuration Words (Table 6-2).

TABLE 6-2:

MCLR

CONFIGURATION

| MCLRE | LVP | MCLR     |

|-------|-----|----------|

| 0     | 0   | Disabled |

| 1     | 0   | Enabled  |

| х     | 1   | Enabled  |

#### 6.4.1 MCLR ENABLED

When MCLR is enabled and the pin is held low, the device is held in Reset. The MCLR pin is connected to VDD through an internal weak pull-up.

The device has a noise filter in the  $\overline{\text{MCLR}}$  Reset path. The filter will detect and ignore small pulses.

| Note: | A Reset does not drive the $\overline{\text{MCLR}}$ pin low. |

|-------|--------------------------------------------------------------|

|-------|--------------------------------------------------------------|

#### 6.4.2 MCLR DISABLED

When MCLR is disabled, the pin functions as a general purpose input and the internal weak pull-up is under software control. See **Section 12.2** "**PORTA Registers**" for more information.

#### 6.5 Watchdog Timer (WDT) Reset

The Watchdog Timer generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The  $\overline{TO}$  and  $\overline{PD}$  bits in the STATUS register are changed to indicate the WDT Reset. See **Section 10.0** "**Watchdog Timer (WDT)**" for more information.

#### 6.6 **RESET Instruction**

A RESET instruction will cause a device Reset. The  $\overline{RI}$  bit in the PCON0 register will be set to '0'. See Table 6-4 for default conditions after a RESET instruction has occurred.

#### 6.7 Stack Overflow/Underflow Reset

The device can reset when the Stack overflows or underflows. The STKOVF or STKUNF bits of the PCON0 register indicate the Reset condition. These Resets are enabled by setting the STVREN bit in Configuration Words. See **Section 4.4 "Stack"** for more information.

#### 6.8 Programming Mode Exit

Upon exit of programming mode, the device will behave as if a device Reset had just occurred.

#### 6.9 Power-up Timer

The Power-up Timer provides a nominal 64 ms time-out on POR or Brown-out Reset.

The device is held in Reset as long as PWRT is active. The PWRT delay allows additional time for the VDD to rise to an acceptable level. The Power-up Timer is enabled by clearing the PWRTE bit in Configuration Words.

The Power-up Timer starts after the release of the POR and BOR.

For additional information, refer to Application Note AN607, *"Power-up Trouble Shooting"* (DS00607).

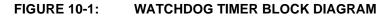

### 10.0 WATCHDOG TIMER (WDT)

The Watchdog Timer is a system timer that generates a Reset if the firmware does not issue a CLRWDT instruction within the time-out period. The Watchdog Timer is typically used to recover the system from unexpected events.

The WDT has the following features:

- Independent clock source

- Multiple operating modes

- · WDT is always on

- WDT is off when in Sleep

- · WDT is controlled by software

- · WDT is always off

- Configurable time-out period is from 1 ms to 256 seconds (nominal)

- Multiple WDT clearing conditions

- Operation during Sleep

|                      |         | -                  |         |                |                  |                  |             |

|----------------------|---------|--------------------|---------|----------------|------------------|------------------|-------------|

| R/W-0/0              | R/W-0/0 | R/W-0/0            | R/W-0/0 | U-0            | U-0              | U-0              | U-0         |

| WPUB7                | WPUB6   | WPUB5              | WPUB4   | —              | —                | —                | _           |

| bit 7                |         |                    |         |                |                  |                  | bit C       |

|                      |         |                    |         |                |                  |                  |             |

| Legend:              |         |                    |         |                |                  |                  |             |

| R = Readable         | bit     | W = Writable I     | bit     | U = Unimpler   | mented bit, read | as '0'           |             |

| u = Bit is unchanged |         | x = Bit is unknown |         | -n/n = Value   | at POR and BOI   | R/Value at all o | ther Resets |

| '1' = Bit is set     |         | '0' = Bit is clea  | ared    |                |                  |                  |             |

| ő                    |         |                    |         | -n/n = Value : | at POR and BOI   | R/Value at all o | ther Re     |

#### **REGISTER 12-13: WPUB: WEAK PULL-UP PORTB REGISTER**

| bit 7-4 | WPUB<7:4>: Weak Pull-up Register bits |

|---------|---------------------------------------|

|         | 1 = Weak Pull-up enabled              |

|         | 0 = Weak Pull-up disabled             |

| bit 3-0 | Unimplemented: Read as '0'            |

**Note:** The weak pull-up is disabled if the pin is configured as an output except when the pin is also configured as open-drain. When configured as open-drain, the pull-up is enabled when the output value is high, and disabled when the output value is low.

#### REGISTER 12-14: ODCONB: PORTB OPEN-DRAIN CONTROL REGISTER

| R/W-0/0 | R/W-0/0 | R/W-0/0 | R/W-0/0 | U-0 | U-0 | U-0 | U-0   |

|---------|---------|---------|---------|-----|-----|-----|-------|

| ODCB7   | ODCB6   | ODCB5   | ODCB4   | —   | —   | —   | —     |

| bit 7   |         |         |         |     |     |     | bit 0 |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

| bit 7-4 | ODCB<7:4>: PORTB Open-Drain Configuration bits                              |

|---------|-----------------------------------------------------------------------------|

|         | For RB<7:4> pins, respectively:                                             |

|         | 1 = Port pin operates as open-drain drive (sink current only)               |

|         | 0 = Port pin operates as standard push-pull drive (source and sink current) |

| bit 3-0 | Unimplemented: Read as '0'                                                  |

| R/W/HS-0/0            | R/W/HS-0/0                              | R/W/HS-0/0   | R/W/HS-0/0                  | R/W/HS-0/0                                            | R/W/HS-0/0       | R/W/HS-0/0 | R/W/HS-0/0 |

|-----------------------|-----------------------------------------|--------------|-----------------------------|-------------------------------------------------------|------------------|------------|------------|

| IOCCF7 <sup>(1)</sup> | IOCCF6 <sup>(1)</sup>                   | IOCCF5       | IOCCF4                      | IOCCF3                                                | IOCCF2           | IOCCF1     | IOCCF0     |

| bit 7                 |                                         |              |                             |                                                       |                  |            | bit 0      |

|                       |                                         |              |                             |                                                       |                  |            |            |

| Legend:               |                                         |              |                             |                                                       |                  |            |            |

| R = Readable          | bit                                     | W = Writable | bit                         | U = Unimpler                                          | nented bit, read | as '0'     |            |

| u = Bit is uncha      | a = Bit is unchanged x = Bit is unknown |              | nown                        | -n/n = Value at POR and BOR/Value at all other Resets |                  |            |            |

| '1' = Bit is set      | 1' = Bit is set '0' = Bit is cleared    |              | HS - Bit is set in hardware |                                                       |                  |            |            |

|                       |                                         |              |                             |                                                       |                  |            |            |

#### REGISTER 15-9: IOCCF: INTERRUPT-ON-CHANGE PORTC FLAG REGISTER

| bit 7-6 | <ul> <li>IOCCF&lt;7:6&gt;: Interrupt-on-Change PORTC Flag bits</li> <li>1 = An enabled change was detected on the associated pin.<br/>Set when IOCCPx = 1 and a rising edge was detected on RCx, or when IOCCNx = 1 and a falling edge was detected on RCx.</li> <li>0 = No change was detected, or the user cleared the detected change.</li> </ul> |

|---------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| bit 5-0 | <ul> <li>IOCCF&lt;5:0&gt;: Interrupt-on-Change PORTC Flag bits</li> <li>1 = An enabled change was detected on the associated pin.<br/>Set when IOCCPx = 1 and a rising edge was detected on RCx, or when IOCCNx = 1 and a falling edge was detected on RCx.</li> </ul>                                                                               |

0 = No change was detected, or the user cleared the detected change.

**Note 1:** PIC16(L)F18344 only.

| Name                  | Bit 7                 | Bit 6                 | Bit 5  | Bit 4  | Bit 3  | Bit 2  | Bit 1  | Bit 0  | Register<br>on Page |

|-----------------------|-----------------------|-----------------------|--------|--------|--------|--------|--------|--------|---------------------|

| ANSELA                |                       | _                     | ANSA5  | ANSA4  |        | ANSA2  | ANSA1  | ANSA0  | 141                 |

| ANSELB <sup>(1)</sup> | ANSB7                 | ANSB6                 | ANSB5  | ANSB4  | _      | —      | —      | —      | 147                 |

| ANSELC                | ANSC7 <sup>(1)</sup>  | ANSC6 <sup>(1)</sup>  | ANSC5  | ANSC4  | ANSC3  | ANSC2  | ANSC1  | ANSC0  | 154                 |

| TRISA                 | —                     | —                     | TRISA5 | TRISA4 | (2)    | TRISA2 | TRISA1 | TRISA0 | 140                 |

| TRISB <sup>(1)</sup>  | TRISB7                | TRISB6                | TRISB5 | TRISB4 | _      | —      | —      | —      | 146                 |

| TRISC                 | TRISC7 <sup>(1)</sup> | TRISC6 <sup>(1)</sup> | TRISC5 | TRISC4 | TRISC3 | TRISC2 | TRISC1 | TRISC0 | 153                 |

| INTCON                | GIE                   | PEIE                  | _      | —      | _      | —      | —      | INTEDG | 98                  |

| PIE0                  | —                     | —                     | TMR0IE | IOCIE  | _      | —      | —      | INTE   | 99                  |

| IOCAP                 | _                     | —                     | IOCAP5 | IOCAP4 | IOCAP3 | IOCAP2 | IOCAP1 | IOCAP0 | 171                 |

| IOCAN                 | _                     | —                     | IOCAN5 | IOCAN4 | IOCAN3 | IOCAN2 | IOCAN1 | IOCAN0 | 171                 |

| IOCAF                 | _                     | —                     | IOCAF5 | IOCAF4 | IOCAF3 | IOCAF2 | IOCAF1 | IOCAF0 | 172                 |

| IOCBP <sup>(1)</sup>  | IOCBP7                | IOCBP6                | IOCBP5 | IOCBP4 | _      | _      | _      | —      | 172                 |

| IOCBN <sup>(1)</sup>  | IOCBN7                | IOCBN6                | IOCBN5 | IOCBN4 | _      | _      | _      | —      | 173                 |

| IOCBF <sup>(1)</sup>  | IOCBF7                | IOCBF6                | IOCBF5 | IOCBF4 | _      | _      | _      | —      | 173                 |

| IOCCP                 | IOCCP7 <sup>(1)</sup> | IOCCP6 <sup>(1)</sup> | IOCCP5 | IOCCP4 | IOCCP3 | IOCCP2 | IOCCP1 | IOCCP0 | 174                 |

| IOCCN                 | IOCCN7 <sup>(1)</sup> | IOCCN6 <sup>(1)</sup> | IOCCN5 | IOCCN4 | IOCCN3 | IOCCN2 | IOCCN1 | IOCCN0 | 174                 |

| IOCCF                 | IOCCF7 <sup>(1)</sup> | IOCCF6 <sup>(1)</sup> | IOCCF5 | IOCCF4 | IOCCF3 | IOCCF2 | IOCCF1 | IOCCF0 | 175                 |

#### TABLE 15-1: SUMMARY OF REGISTERS ASSOCIATED WITH INTERRUPT-ON-CHANGE

Legend: — = unimplemented location, read as '0'. Shaded cells are not used by interrupt-on-change.

**Note 1:** PIC16(L)F18344 only.

2: Unimplemented, read as '1'.

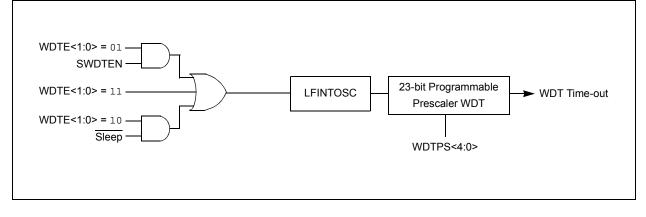

#### 18.0 COMPARATOR MODULE

Comparators are used to interface analog circuits to a digital circuit by comparing two analog voltages and providing a digital indication of their relative magnitudes. Comparators are very useful mixed signal building blocks because they provide analog functionality independent of program execution. The analog comparator module includes the following features:

- Programmable input selection

- Selectable voltage reference

- Programmable output polarity

- Rising/falling output edge interrupts

- Wake-up from Sleep

- CWG Auto-shutdown source

#### 18.1 Comparator Overview

A single comparator is shown in Figure 18-1 along with the relationship between the analog input levels and the digital output. When the analog voltage at VIN+ is less than the analog voltage at VIN-, the output of the comparator is a digital low level. When the analog voltage at VIN+ is greater than the analog voltage at VIN-, the output of the comparator is a digital high level.

The comparators available for this device are located in Table 18-1.

| TABLE 18-1: | AVAILABLE COMPARATORS |

|-------------|-----------------------|

|-------------|-----------------------|

| Device         | C1 | C2 |

|----------------|----|----|

| PIC16(L)F18324 | •  | •  |

| PIC16(L)F18344 | •  | ٠  |

#### FIGURE 18-1: SINGLE COMPARATOR

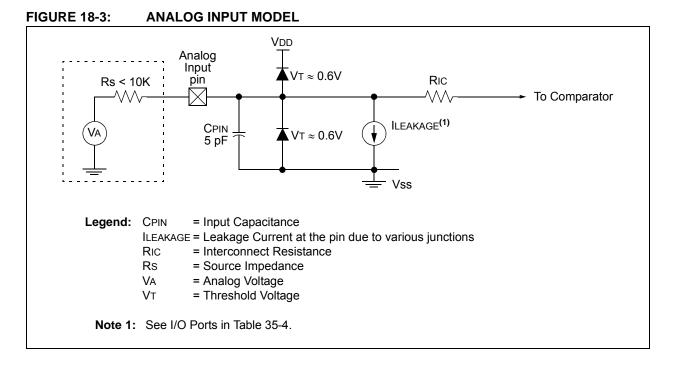

#### 18.9 Analog Input Connection Considerations

A simplified circuit for an analog input is shown in Figure 18-3. Since the analog input pins share their connection with a digital input, they have reverse biased ESD protection diodes to VDD and Vss. The analog input, therefore, must be between Vss and VDD. If the input voltage deviates from this range by more than 0.6V in either direction, one of the diodes is forward biased and a latch-up may occur.

A maximum source impedance of  $10 \text{ k}\Omega$  is recommended for the analog sources. Also, any external component connected to an analog input pin, such as a capacitor or a Zener diode, should have very little leakage current to minimize inaccuracies introduced.

- Note 1: When reading a PORT register, all pins configured as analog inputs will read as a '0'. Pins configured as digital inputs will provide an input based on their level as either a TTL or ST input buffer.

- 2: Analog levels on any pin defined as a digital input, may cause the input buffer to consume more current than is specified.

#### 19.1.3 PWM RESOLUTION

PWM resolution, expressed in number of bits, defines the maximum number of discrete steps that can be present in a single PWM period. For example, a 10-bit resolution will result in 1024 discrete steps, whereas an 8-bit resolution will result in 256 discrete steps.

The maximum PWM resolution is ten bits when PR2 is 255. The resolution is a function of the PR2 register value as shown by Equation 19-4.

#### EQUATION 19-4: PWM RESOLUTION

Resolution =  $\frac{\log[4(PR2+1)]}{\log(2)}$  bits

Note: If the pulse-width value is greater than the period the assigned PWM pin(s) will remain unchanged.

#### 19.1.4 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2 register will not increment and the state of the module will not change. If the PWMx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2 will continue from its previous state.

#### 19.1.5 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See **Section 7.0, Oscillator Module** for additional details.

#### 19.1.6 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the PWMx registers to their Reset states.

#### 19.1.7 SETUP FOR PWM OPERATION

The following steps should be taken when configuring the module for using the PWMx outputs:

- 1. Disable the PWMx pin output driver(s) by setting the associated TRIS bit(s).

- 2. Configure the PWM output polarity by configuring the PWMxPOL bit of the PWMxCON register.

- 3. Load the PR2 register with the PWM period value, as determined by Equation 19-1.

- 4. Load the PWMxDCH register and bits <7:6> of the PWMxDCL register with the PWM duty cycle value, as determined by Equation 19-2.

- 5. Configure and start Timer2:

- Clear the TMR2IF interrupt flag bit of the PIR1 register.

- Select the Timer2 prescale value by configuring the T2CKPS bit of the T2CON register.

- Enable Timer2 by setting the TMR2ON bit of the T2CON register.

- 6. Wait until the TMR2IF is set.

- 7. When the TMR2IF flag bit is set:

- Clear the associated TRIS bit(s) to enable the output driver.

- Route the signal to the desired pin by configuring the RxyPPS register.

- Enable the PWMx module by setting the PWMxEN bit of the PWMxCON register.

In order to send a complete duty cycle and period on the first PWM output, the above steps must be followed in the order given. If it is not critical to start with a complete PWM signal, then the PWM module can be enabled during Step 2 by setting the PWMxEN bit of the PWMxCON register.

| U-0                                                                                             | U-0                                                                          | R/W-x/u                                                                                                           | R/W-x/u                                                 | R/W-x/u                                            | R/W-x/u                                                | R/W-x/u                                 | R/W-x/u        |

|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|----------------------------------------------------|--------------------------------------------------------|-----------------------------------------|----------------|

| _                                                                                               | _                                                                            |                                                                                                                   |                                                         | LCxD1                                              | S<5:0>                                                 |                                         |                |

| bit 7                                                                                           |                                                                              |                                                                                                                   |                                                         |                                                    |                                                        |                                         | bit            |

| Legend:                                                                                         |                                                                              |                                                                                                                   |                                                         |                                                    |                                                        |                                         |                |

| R = Readable                                                                                    | bit                                                                          | W = Writable                                                                                                      | bit                                                     | U = Unimplem                                       | nented bit, read                                       | l as '0'                                |                |

| u = Bit is uncha                                                                                | anged                                                                        | x = Bit is unkr                                                                                                   | nown                                                    | -n/n = Value a                                     | t POR and BO                                           | R/Value at all o                        | ther Resets    |

| '1' = Bit is set                                                                                |                                                                              | '0' = Bit is cle                                                                                                  | ared                                                    |                                                    |                                                        |                                         |                |

| bit 7-6                                                                                         | Unimpleme                                                                    | nted: Read as '                                                                                                   | 0'                                                      |                                                    |                                                        |                                         |                |

| bit 5-0                                                                                         | LCxD1S<5:0<br>See Table 21                                                   | D>: CLCx Data1                                                                                                    | Input Selection                                         | on bits                                            |                                                        |                                         |                |

|                                                                                                 |                                                                              | •••                                                                                                               |                                                         |                                                    |                                                        |                                         |                |

| REGISTER 2 <sup>°</sup>                                                                         |                                                                              | SEL1: GENE                                                                                                        | RIC CLCx D                                              | ATA 1 SELEO                                        | CT REGISTEI                                            | R                                       |                |

| REGISTER 2 <sup>°</sup><br>U-0                                                                  |                                                                              |                                                                                                                   | RIC CLCx D<br>R/W-x/u                                   | ATA 1 SELEO<br>R/W-x/u                             | <b>CT REGISTEI</b><br>R/W-x/u                          | R<br>R/W-x/u                            | R/W-x/u        |

|                                                                                                 | 1-4: CLCx                                                                    | SEL1: GENE                                                                                                        |                                                         | R/W-x/u                                            |                                                        |                                         | R/W-x/u        |

| REGISTER 2'<br>U-0<br>—<br>bit 7                                                                | 1-4: CLCx                                                                    | SEL1: GENE                                                                                                        |                                                         | R/W-x/u                                            | R/W-x/u                                                |                                         | R/W-x/u<br>bit |

| U-0<br>—<br>bit 7                                                                               | 1-4: CLCx                                                                    | SEL1: GENE                                                                                                        |                                                         | R/W-x/u                                            | R/W-x/u                                                |                                         |                |

| U-0<br>—<br>bit 7<br>Legend:                                                                    | 1-4: CLCx<br>U-0                                                             | SEL1: GENE                                                                                                        | R/W-x/u                                                 | R/W-x/u<br>LCxD2                                   | R/W-x/u                                                | R/W-x/u                                 | -              |

| U-0<br>—<br>bit 7<br>Legend:<br>R = Readable                                                    | 1-4: CLCx<br>U-0<br>                                                         | SEL1: GENE                                                                                                        | R/W-x/u                                                 | R/W-x/u<br>LCxD2<br>U = Unimplem                   | R/W-x/u<br>2S<5:0>                                     | R/W-x/u                                 | bit            |

| U-0<br>—<br>bit 7<br>Legend:<br>R = Readable<br>u = Bit is uncha                                | 1-4: CLCx<br>U-0<br>                                                         | SEL1: GENE<br>R/W-x/u<br>W = Writable                                                                             | R/W-x/u<br>bit                                          | R/W-x/u<br>LCxD2<br>U = Unimplem                   | R/W-x/u<br>2S<5:0>                                     | R/W-x/u                                 | bit            |

| U-0<br>—<br>bit 7<br>Legend:<br>R = Readable<br>u = Bit is uncha<br>'1' = Bit is set            | 1-4: CLCx<br>U-0<br>—<br>bit<br>anged                                        | SEL1: GENE<br>R/W-x/u<br>W = Writable<br>x = Bit is unkr<br>'0' = Bit is cle                                      | R/W-x/u<br>bit<br>nown<br>ared                          | R/W-x/u<br>LCxD2<br>U = Unimplem                   | R/W-x/u<br>2S<5:0>                                     | R/W-x/u                                 | bit            |

| U-0<br>—<br>bit 7<br>Legend:<br>R = Readable<br>u = Bit is uncha<br>'1' = Bit is set<br>bit 7-6 | 1-4: CLCx<br>U-0<br>bit<br>anged                                             | SEL1: GENE<br>R/W-x/u<br>W = Writable<br>x = Bit is unku<br>'0' = Bit is cle<br>nted: Read as '<br>>: CLCx Data 2 | R/W-x/u<br>bit<br>nown<br>ared<br>0'                    | R/W-x/u<br>LCxD2<br>U = Unimplen<br>-n/n = Value a | R/W-x/u<br>2S<5:0>                                     | R/W-x/u                                 | bit            |

| U-0                                                                                             | 1-4: CLCx<br>U-0<br>bit<br>anged<br>Unimplemen<br>LCxD2S<5:0<br>See Table 21 | SEL1: GENE<br>R/W-x/u<br>W = Writable<br>x = Bit is unku<br>'0' = Bit is cle<br>nted: Read as '<br>>: CLCx Data 2 | R/W-x/u<br>bit<br>nown<br>ared<br>0'<br>2 Input Selecti | R/W-x/u<br>LCxD2<br>U = Unimplen<br>-n/n = Value a | R/W-x/u<br>2S<5:0><br>hented bit, read<br>t POR and BO | R/W-x/u<br>I as '0'<br>R/Value at all c | bit            |

| U-0   | U-0 | R/W-x/u | R/W-x/u     | R/W-x/u | R/W-x/u | R/W-x/u | R/W-x/u |  |  |

|-------|-----|---------|-------------|---------|---------|---------|---------|--|--|

|       | —   |         | LCxD3S<5:0> |         |         |         |         |  |  |

| bit 7 |     |         |             |         |         |         | bit 0   |  |  |

| Legend:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

#### bit 7-6 Unimplemented: Read as '0'

bit 5-0 LCxD3S<5:0>: CLCx Data 3 Input Selection bits See Table 21-1.

#### EQUATION 29-2: PULSE WIDTH

*Pulse Width* = (*CCPRxH:CCPRxL register pair*) •

TOSC • (TMR2 Prescale Value)

#### EQUATION 29-3: DUTY CYCLE RATIO

$Duty Cycle Ratio = \frac{(CCPRxH:CCPRxL register pair)}{4(PR2 + 1)}$

The CCPRxH:CCPRxL register pair and a 2-bit internal latch are used to double buffer the PWM duty cycle. This double buffering provides glitchless PWM operation.

The 8-bit timer TMR2/4/6 register is concatenated with either the 2-bit internal system clock (Fosc), or two bits of the prescaler, to create the 10-bit time base. The system clock is used if the Timer2/4/6 prescaler is set to 1:1.

When the 10-bit time base matches the CCPRxH:CCPRxL register pair, then the CCPx pin is cleared (see Figure 29-4).

#### 29.4.6 PWM RESOLUTION

PWM resolution, expressed in number of bits, defines the maximum number of discrete steps that can be present in a single PWM period. For example, a 10-bit resolution will result in 1024 discrete steps, whereas an 8-bit resolution will result in 256 discrete steps.

The maximum PWM resolution is ten bits when PRx is 255. The resolution is a function of the PRx register value as shown by Equation 29-4.

#### EQUATION 29-4: PWM RESOLUTION

Resolution =

$$\frac{\log[4(PRx+1)]}{\log(2)}$$

bits

**Note:** If the pulse-width value is greater than the period the assigned PWM pin(s) will remain unchanged.

| TADIE 20.4. | EXAMPLE DWM EDECLENCIES AND DESCLUTIONS (Ease - 20 MHz) |

|-------------|---------------------------------------------------------|

| TABLE 29-1: | EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 20 MHz) |

| PWM Frequency             | 1.22 kHz | 4.88 kHz | 19.53 kHz | 78.12 kHz | 156.3 kHz | 208.3 kHz |

|---------------------------|----------|----------|-----------|-----------|-----------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1         | 1         |

| PRx Value                 | 0xFF     | 0xFF     | 0xFF      | 0x3F      | 0x1F      | 0x17      |

| Maximum Resolution (bits) | 10       | 10       | 10        | 8         | 7         | 6.6       |

#### TABLE 29-2: EXAMPLE PWM FREQUENCIES AND RESOLUTIONS (Fosc = 8 MHz)

| PWM Frequency             | 1.22 kHz | 4.90 kHz | 19.61 kHz | 76.92 kHz | 153.85 kHz | 200.0 kHz |

|---------------------------|----------|----------|-----------|-----------|------------|-----------|

| Timer Prescale            | 16       | 4        | 1         | 1         | 1          | 1         |

| PRx Value                 | 0x65     | 0x65     | 0x65      | 0x19      | 0x0C       | 0x09      |

| Maximum Resolution (bits) | 8        | 8        | 8         | 6         | 5          | 5         |

#### 29.4.7 OPERATION IN SLEEP MODE

In Sleep mode, the TMR2/4/6 register will not increment and the state of the module will not change. If the CCPx pin is driving a value, it will continue to drive that value. When the device wakes up, TMR2/4/6 will continue from its previous state.

#### 29.4.8 CHANGES IN SYSTEM CLOCK FREQUENCY

The PWM frequency is derived from the system clock frequency. Any changes in the system clock frequency will result in changes to the PWM frequency. See **Section 7.0** "Oscillator Module" for additional details.

#### 29.4.9 EFFECTS OF RESET

Any Reset will force all ports to Input mode and the CCP registers to their Reset states.

On the last byte of data communicated, the master device may end the transmission by sending a Stop bit. If the master device is in Receive mode, it sends a NACK in place of the last ACK bit. A Stop bit is indicated by a low-to-high transition of the SDA line while the SCL line is held high.

In some cases, the master may want to maintain control of the bus and re-initiate another transmission. If so, the master device may send a Restart condition in place of the Stop bit or last ACK bit when it is in Receive mode.

The I<sup>2</sup>C bus specifies three message protocols;

- Single message where a master writes data to a slave.

- Single message where a master reads data from a slave.

- Combined message where a master initiates a minimum of two writes, or two reads, or a combination of writes and reads, to one or more slaves.

#### 30.3.1 CLOCK STRETCHING

When a slave device has not completed processing data, it can delay the transfer of more data through the process of clock stretching. An addressed slave device may hold the SCL clock line low after receiving or sending a bit, indicating that it is not yet ready to continue. The master that is communicating with the slave will attempt to raise the SCL line in order to transfer the next bit, but will detect that the clock line has not yet been released. Because the SCL connection is open-drain, the slave has the ability to hold that line low until it is ready to continue communicating.

Clock stretching allows receivers that cannot keep up with a transmitter to control the flow of incoming data.

#### 30.3.2 ARBITRATION

Each master device must monitor the bus for Start and Stop bits. If the device detects that the bus is busy, it cannot begin a new message until the bus returns to an Idle state.

However, two master devices may try to initiate a transmission on or about the same time. When this occurs, the process of arbitration begins. Each transmitter checks the level of the SDA data line and compares it to the level that it expects to find. The first transmitter to observe that the two levels do not match, loses arbitration, and must stop transmitting on the SDA line.

For example, if one transmitter holds the SDA line to a logical one (lets it float) and a second transmitter holds it to a logical zero (pulls it low), the result is that the SDA line will be low. The first transmitter then observes that the level of the line is different than expected and concludes that another transmitter is communicating.

The first transmitter to notice this difference is the one that loses arbitration and must stop driving the SDA line. If this transmitter is also a master device, it also must stop driving the SCL line. It then can monitor the lines for a Stop condition before trying to reissue its transmission. In the meantime, the other device that has not noticed any difference between the expected and actual levels on the SDA line continues with its original transmission.

Slave Transmit mode can also be arbitrated, when a master addresses multiple slaves, but this is less common.

#### 31.4.2 SYNCHRONOUS SLAVE MODE

The following bits are used to configure the EUSART1 for synchronous slave operation:

- SYNC = 1

- CSRC = 0

- SREN = 0 (for transmit); SREN = 1 (for receive)

- CREN = 0 (for transmit); CREN = 1 (for receive)

- SPEN = 1

Setting the SYNC bit of the TX1STA register configures the device for synchronous operation. Clearing the CSRC bit of the TX1STA register configures the device as a slave. Clearing the SREN and CREN bits of the RC1STA register ensures that the device is in the Transmit mode, otherwise the device will be configured to receive. Setting the SPEN bit of the RC1STA register enables the EUSART1.

#### 31.4.2.1 EUSART1 Synchronous Slave Transmit

The operation of the Synchronous Master and Slave modes are identical (see **Section 31.4.1.3 "Synchronous Master Transmission")**, except in the case of the Sleep mode.

If two words are written to the TX1REG and then the SLEEP instruction is executed, the following will occur:

- 1. The first character will immediately transfer to the TSR register and transmit.

- 2. The second word will remain in the TX1REG register.

- 3. The TXIF bit will not be set.

- After the first character has been shifted out of TSR, the TX1REG register will transfer the second character to the TSR and the TXIF bit will now be set.

- 5. If the PEIE and TXIE bits are set, the interrupt will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will call the Interrupt Service Routine.

31.4.2.2 Synchronous Slave Transmission Set-up

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for the CK pin (if applicable).

- 3. Clear the CREN and SREN bits.

- If interrupts are desired, set the TXIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 5. If 9-bit transmission is desired, set the TX9 bit.

- 6. Enable transmission by setting the TXEN bit.

- 7. If 9-bit transmission is selected, insert the Most Significant bit into the TX9D bit.

- 8. Start transmission by writing the Least Significant eight bits to the TX1REG register.

## 31.4.2.3 EUSART1 Synchronous Slave Reception

The operation of the Synchronous Master and Slave modes is identical (Section 31.4.1.5 "Synchronous Master Reception"), with the following exceptions:

- Sleep

- CREN bit is always set, therefore the receiver is never idle

- · SREN bit, which is a "don't care" in Slave mode

A character may be received while in Sleep mode by setting the CREN bit prior to entering Sleep. Once the word is received, the RSR register will transfer the data to the RC1REG register. If the RCIE enable bit is set, the interrupt generated will wake the device from Sleep and execute the next instruction. If the GIE bit is also set, the program will branch to the interrupt vector.

- 31.4.2.4 Synchronous Slave Reception Set-up

- 1. Set the SYNC and SPEN bits and clear the CSRC bit.

- 2. Clear the ANSEL bit for both the CK and DT pins (if applicable).

- If interrupts are desired, set the RCIE bit of the PIE1 register and the GIE and PEIE bits of the INTCON register.

- 4. If 9-bit reception is desired, set the RX9 bit.

- 5. Set the CREN bit to enable reception.

- The RCIF bit will be set when reception is complete. An interrupt will be generated if the RCIE bit was set.

- 7. If 9-bit mode is enabled, retrieve the Most Significant bit from the RX9D bit of the RC1STA register.

- 8. Retrieve the eight Least Significant bits from the receive FIFO by reading the RC1REG register.

- 9. If an overrun error occurs, clear the error by either clearing the CREN bit of the RC1STA register or by clearing the SPEN bit which resets the EUSART1.

| C    | onfiguration B | lits |                     | Baud Rate Formula |  |  |  |

|------|----------------|------|---------------------|-------------------|--|--|--|

| SYNC | BRG16          | BRGH | BRG/EUSART Mode     | Bauu Kale Formula |  |  |  |

| 0    | 0              | 0    | 8-bit/Asynchronous  | Fosc/[64 (n+1)]   |  |  |  |

| 0    | 0              | 1    | 8-bit/Asynchronous  |                   |  |  |  |

| 0    | 1              | 0    | 16-bit/Asynchronous | Fosc/[16 (n+1)]   |  |  |  |

| 0    | 1              | 1    | 16-bit/Asynchronous |                   |  |  |  |

| 1    | 1 0            |      | 8-bit/Synchronous   | Fosc/[4 (n+1)]    |  |  |  |

| 1    | 1              | x    | 16-bit/Synchronous  |                   |  |  |  |

#### TABLE 31-3:BAUD RATE FORMULAS

**Legend:** x = Don't care, n = value of SP1BRGH, SP1BRGL register pair.

#### TABLE 31-4: BAUD RATE FOR ASYNCHRONOUS MODES

| BAUD<br>RATE |                   | SYNC = 0, BRGH = 0, BRG16 = 0 |                             |                |            |                             |                |            |                             |                    |            |                             |

|--------------|-------------------|-------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|--------------------|------------|-----------------------------|

|              | Fosc = 32.000 MHz |                               |                             | Fosc           | = 20.00    | 0 MHz                       | Fosc           | ; = 18.43  | 2 MHz                       | Fosc = 11.0592 MHz |            |                             |

|              | Actual<br>Rate    | %<br>Error                    | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate     | %<br>Error | SPBRG<br>value<br>(decimal) |

| 300          |                   |                               | _                           | _              |            | _                           | _              |            | _                           |                    |            |                             |

| 1200         | —                 | —                             | —                           | 1221           | 1.73       | 255                         | 1200           | 0.00       | 239                         | 1200               | 0.00       | 143                         |

| 2400         | 2404              | 0.16                          | 207                         | 2404           | 0.16       | 129                         | 2400           | 0.00       | 119                         | 2400               | 0.00       | 71                          |

| 9600         | 9615              | 0.16                          | 51                          | 9470           | -1.36      | 32                          | 9600           | 0.00       | 29                          | 9600               | 0.00       | 17                          |

| 10417        | 10417             | 0.00                          | 47                          | 10417          | 0.00       | 29                          | 10286          | -1.26      | 27                          | 10165              | -2.42      | 16                          |

| 19.2k        | 19.23k            | 0.16                          | 25                          | 19.53k         | 1.73       | 15                          | 19.20k         | 0.00       | 14                          | 19.20k             | 0.00       | 8                           |

| 57.6k        | 55.55k            | -3.55                         | 3                           | —              | _          | _                           | 57.60k         | 0.00       | 7                           | 57.60k             | 0.00       | 2                           |

| 115.2k       | —                 | _                             | _                           | —              |            | —                           | —              | —          | _                           | _                  | _          | _                           |

| BAUD<br>RATE |                  | <b>SYNC =</b> 0, <b>BRGH =</b> 0, <b>BRG16 =</b> 0 |                             |                |            |                             |                |            |                             |                |                  |                             |

|--------------|------------------|----------------------------------------------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------|-----------------------------|----------------|------------------|-----------------------------|

|              | Fosc = 8.000 MHz |                                                    |                             | Fos            | c = 4.000  | ) MHz                       | Fosc           | : = 3.686  | 4 MHz                       | Fos            | Fosc = 1.000 MHz |                             |

|              | Actual<br>Rate   | %<br>Error                                         | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error | SPBRG<br>value<br>(decimal) | Actual<br>Rate | %<br>Error       | SPBRG<br>value<br>(decimal) |

| 300          | _                | _                                                  | _                           | 300            | 0.16       | 207                         | 300            | 0.00       | 191                         | 300            | 0.16             | 51                          |

| 1200         | 1202             | 0.16                                               | 103                         | 1202           | 0.16       | 51                          | 1200           | 0.00       | 47                          | 1202           | 0.16             | 12                          |

| 2400         | 2404             | 0.16                                               | 51                          | 2404           | 0.16       | 25                          | 2400           | 0.00       | 23                          | —              | _                | —                           |

| 9600         | 9615             | 0.16                                               | 12                          | _              | _          | _                           | 9600           | 0.00       | 5                           | _              | _                | —                           |

| 10417        | 10417            | 0.00                                               | 11                          | 10417          | 0.00       | 5                           | _              | _          | _                           | _              | _                | —                           |

| 19.2k        | —                | _                                                  | _                           | _              | _          | _                           | 19.20k         | 0.00       | 2                           | _              | _                | _                           |

| 57.6k        | —                | _                                                  | _                           | —              | _          | _                           | 57.60k         | 0.00       | 0                           | _              | _                | _                           |

| 115.2k       | —                | —                                                  | —                           | _              | —          | —                           | _              | —          | —                           | _              | —                |                             |

Λ