Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

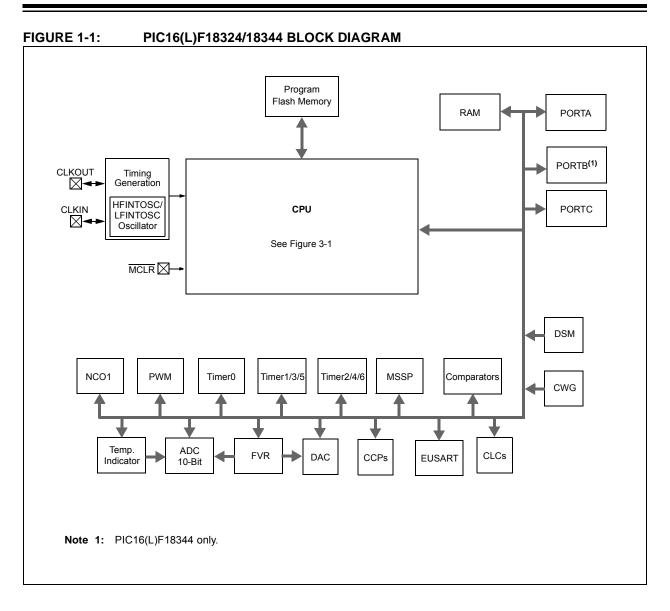

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

#### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XFI

| Details                    |                                                                             |

|----------------------------|-----------------------------------------------------------------------------|

| Product Status             | Active                                                                      |

| Core Processor             | PIC                                                                         |

| Core Size                  | 8-Bit                                                                       |

| Speed                      | 32MHz                                                                       |

| Connectivity               | I <sup>2</sup> C, LINbus, SPI, UART/USART                                   |

| Peripherals                | Brown-out Detect/Reset, POR, PWM, WDT                                       |

| Number of I/O              | 12                                                                          |

| Program Memory Size        | 7KB (4K x 14)                                                               |

| Program Memory Type        | FLASH                                                                       |

| EEPROM Size                | 256 x 8                                                                     |

| RAM Size                   | 512 x 8                                                                     |

| Voltage - Supply (Vcc/Vdd) | 2.3V ~ 5.5V                                                                 |

| Data Converters            | A/D 11x10b; D/A 1x5b                                                        |

| Oscillator Type            | Internal                                                                    |

| Operating Temperature      | -40°C ~ 85°C (TA)                                                           |

| Mounting Type              | Surface Mount                                                               |

| Package / Case             | 14-SOIC (0.154", 3.90mm Width)                                              |

| Supplier Device Package    | 14-SOIC                                                                     |

| Purchase URL               | https://www.e-xfl.com/product-detail/microchip-technology/pic16f18324t-i-sl |

|                            |                                                                             |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

# PIC16(L)F18324/18344

| TA  | BLE 4                                           | I-4: SPE | CIAL FL                          | <b>JNCTION RE</b> | EGISTER S | UMMARY B | ANKS 0-31 ( | CONTINUE | D)    |       |       |                       |                                 |

|-----|-------------------------------------------------|----------|----------------------------------|-------------------|-----------|----------|-------------|----------|-------|-------|-------|-----------------------|---------------------------------|

| Ad  | ldress                                          | Name     | PIC16(L)F18324<br>PIC16(L)F18344 | Bit 7             | Bit 6     | Bit 5    | Bit 4       | Bit 3    | Bit 2 | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>resets |

| E   | Bank 5                                          |          |                                  |                   |           |          |             |          |       |       |       |                       |                                 |

|     | CPU CORE REGISTERS; see Table 4-2 for specifics |          |                                  |                   |           |          |             |          |       |       |       |                       |                                 |

| 280 | Ch                                              | ODCONA   |                                  | _                 | _         | ODCA5    | ODCA4       | _        | ODCA2 | ODCA1 | ODCA0 | 00 -000               | 00 -000                         |

| 201 | Dh                                              |          | V                                |                   |           |          | Linimala    | montod   |       |       |       |                       |                                 |

|      |         |     |        |                                 | CFU CORE RE       | -0101 - 100, 300 - |                            | icines |         |           |           |           |

|------|---------|-----|--------|---------------------------------|-------------------|--------------------|----------------------------|--------|---------|-----------|-----------|-----------|

| 28Ch | ODCONA  |     | —      |                                 | ODCA5             | ODCA4              | _                          | ODCA2  | ODCA1   | ODCA0     | 00 -000   | 00 -000   |

| 28Dh | ODCONB  | X – |        |                                 |                   | Unimple            | mented                     |        |         |           | -         | —         |

|      |         | — X | ODCB7  | ODCB6                           | ODCB5             | ODCB4              | —                          | —      | —       | -         | 0000      | 0000      |

| 28Eh | ODCONC  | X — | —      | —                               | ODCC5             | ODCC4              | ODCC3                      | ODCC2  | ODCC1   | ODCC0     | 00 0000   | 00 0000   |

|      |         | — X | ODCC7  | ODCC6                           | ODCC5             | ODCC4              | ODCC3                      | ODCC2  | ODCC1   | ODCC0     | 0000 0000 | 0000 0000 |

| 28Fh | —       |     |        | Unimplemented                   |                   |                    |                            |        |         |           | -         | —         |

| 290h | _       |     |        | Unimplemented —                 |                   |                    |                            |        |         |           |           | —         |

| 291h | CCPR1L  |     |        | CCPR1<7:0> xxxx xxxx            |                   |                    |                            |        |         |           | xxxx xxxx | xxxx xxxx |

| 292h | CCPR1H  |     |        | CCPR1<15:8> xxxx xxxx xxxx xxxx |                   |                    |                            |        |         | xxxx xxxx |           |           |

| 293h | CCP1CON |     | CCP1EN | _                               | CCP10UT           | CCP1FMT            | AT CCP1MODE<3:0> 0-x0 0000 |        |         |           | 0-x0 0000 |           |

| 294h | CCP1CAP |     | _      |                                 | CCP1CTS<3:0> 0000 |                    |                            |        |         | xxxx      |           |           |

| 295h | CCPR2L  |     |        |                                 |                   | CCPR2              | 2<7:0>                     |        |         |           | xxxx xxxx | xxxx xxxx |

| 296h | CCPR2H  |     |        |                                 | •                 | CCPR2              | <15:8>                     |        |         |           | xxxx xxxx | xxxx xxxx |

| 297h | CCP2CON |     | CCP2EN | _                               | CCP2OUT           | CCP2FMT            |                            | CCP2MC | DE<3:0> |           | 0-x0 0000 | 0-x0 0000 |

| 298h | CCP2CAP |     | _      | _                               |                   | _                  |                            | CCP2C  | TS<3:0> |           | 0000      | xxxx      |

| 299h | —       | —   |        |                                 |                   | Unimple            | mented                     |        |         |           | -         | —         |

| 29Ah | —       | —   |        |                                 |                   | Unimple            | mented                     |        |         |           | -         | —         |

| 29Bh | —       |     |        |                                 |                   | Unimple            | mented                     |        |         |           | _         | —         |

| 29Ch | —       |     |        | Unimplemented — —               |                   |                    |                            |        |         |           |           |           |

| 29Dh | —       |     |        | Unimplemented — —               |                   |                    |                            |        |         |           |           |           |

| 29Eh | —       | _   |        | Unimplemented — —               |                   |                    |                            |        |         |           | —         |           |

| 29Fh | CCPTMRS |     | C4TSEL | .<1:0>                          | C3TSE             | EL<1:0>            | C2TSE                      | L<1:0> | C1TSE   | L<1:0>    | 0101 0101 | 0101 0101 |

x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

Only on PIC16F18324/18344. Note 1:

Register accessible from both User and ICD Debugger. 2:

| TABLE 4-4: | SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |

|------------|----------------------------------------------------------|

|------------|----------------------------------------------------------|

| IADLE                                           | ABLE 4-4: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED) |                |                                   |                                                            |         |         |         |        |          |           |                       |                                 |  |  |  |  |  |  |

|-------------------------------------------------|--------------------------------------------------------------------|----------------|-----------------------------------|------------------------------------------------------------|---------|---------|---------|--------|----------|-----------|-----------------------|---------------------------------|--|--|--|--|--|--|

| Address                                         | Name                                                               | PIC16(L)F18324 | PIC16(L)<br>8344<br>Bit 7<br>8344 | Bit 6                                                      | Bit 5   | Bit 4   | Bit 3   | Bit 2  | Bit 1    | Bit 0     | Value on:<br>POR, BOR | Value on<br>all other<br>resets |  |  |  |  |  |  |

| Bank 6                                          |                                                                    |                |                                   |                                                            |         |         |         |        |          |           |                       |                                 |  |  |  |  |  |  |

| CPU CORE REGISTERS; see Table 4-2 for specifics |                                                                    |                |                                   |                                                            |         |         |         |        |          |           |                       |                                 |  |  |  |  |  |  |

| 30Ch                                            | SLRCONA                                                            |                | —                                 | -                                                          | SLRA5   | SLRA4   | —       | SLRA2  | SLRA1    | SLRA0     | 11 -111               | 11 -111                         |  |  |  |  |  |  |

| 30Dh                                            | SLRCONB                                                            | X –            | -                                 |                                                            |         | Unimple | emented |        |          |           | —                     | —                               |  |  |  |  |  |  |

|                                                 |                                                                    | — X            | SLRB7                             | SLRB6                                                      | SLRB5   | SLRB4   | —       | —      | —        | —         | 1111                  | 1111                            |  |  |  |  |  |  |

| 30Eh                                            | SLRCONC                                                            | X –            |                                   | —                                                          | SLRC5   | SLRC4   | SLRC3   | SLRC2  | SLRC1    | SLRC0     | 11 1111               | 11 1111                         |  |  |  |  |  |  |

|                                                 |                                                                    | — ×            | SLRC7                             | SLRC6                                                      | SLRC5   | SLRC4   | SLRC3   | SLRC2  | SLRC1    | SLRC0     | 1111 1111             | 1111 1111                       |  |  |  |  |  |  |

| 30Fh                                            | —                                                                  | —              |                                   |                                                            |         | Unimple | emented |        |          |           | _                     | —                               |  |  |  |  |  |  |

| 310h                                            |                                                                    | _              |                                   |                                                            |         | Unimple | emented |        |          |           | _                     | —                               |  |  |  |  |  |  |

| 311h                                            | CCPR3L                                                             |                |                                   |                                                            |         | CCPR    | 3<7:0>  |        |          |           | xxxx xxxx             | xxxx xxxx                       |  |  |  |  |  |  |

| 312h                                            | CCPR3H                                                             |                |                                   |                                                            |         | CCPR3   | 3<15:8> |        |          |           | xxxx xxxx             | xxxx xxxx                       |  |  |  |  |  |  |

| 313h                                            | CCP3CON                                                            |                | CCP3EN                            | —                                                          | CCP3OUT | CCP3FMT |         | CCP3M0 | DDE<3:0> |           | 0-x0 0000             | 0-x0 0000                       |  |  |  |  |  |  |

| 314h                                            | CCP3CAP                                                            |                | —                                 | —                                                          | —       | —       |         | CCP3C  | TS<3:0>  |           | 0000                  | xxxx                            |  |  |  |  |  |  |

| 315h                                            | CCPR4L                                                             |                |                                   |                                                            |         | CCPR    | 4<7:0>  |        |          |           | xxxx xxxx             | xxxx xxxx                       |  |  |  |  |  |  |

| 316h                                            | CCPR4H                                                             |                |                                   | CCPR4<15:8> xxxx xxxx xxxx xxxx xxxx                       |         |         |         |        |          |           |                       |                                 |  |  |  |  |  |  |

| 317h                                            | CCP4CON                                                            |                | CCP4EN                            | CCP4EN — CCP4OUT CCP4FMT CCP4MODE<3:0> 0-x0 0000 0-x0 0000 |         |         |         |        |          | 0-x0 0000 |                       |                                 |  |  |  |  |  |  |

| 318h                                            | CCP4CAP                                                            |                | _                                 | CCP4CTS<3:0> 0000 xxxx                                     |         |         |         |        |          |           |                       |                                 |  |  |  |  |  |  |

| 319h to<br>31Fh                                 | _                                                                  | _              |                                   |                                                            |         | •       |         |        |          |           | Unimplemented –       |                                 |  |  |  |  |  |  |

Legend: x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

**Note 1:** Only on PIC16F18324/18344.

2: Register accessible from both User and ICD Debugger.

#### TABLE 4-4: SPECIAL FUNCTION REGISTER SUMMARY BANKS 0-31 (CONTINUED)

MDCLPOL

| Address | Name    | PIC16(L)F18324<br>PIC16(L)F18344 | Bit 7  | Bit 6   | Bit 5       | Bit 4           | Bit 3             | Bit 2  | Bit 1        | Bit 0 | Value on:<br>POR, BOR | Value on<br>all other<br>resets |

|---------|---------|----------------------------------|--------|---------|-------------|-----------------|-------------------|--------|--------------|-------|-----------------------|---------------------------------|

| Bank 7  | Bank 7  |                                  |        |         |             |                 |                   |        |              |       |                       |                                 |

|         |         |                                  |        |         | CPU CORE RE | EGISTERS; see ] | Table 4-2 for spe | cifics |              |       |                       |                                 |

| 39Ah    | CLKRCON |                                  | CLKREN | —       | —           | CLKRD           | C<1:0>            |        | CLKRDIV<2:0> |       | 01 0000               | 01 0001                         |

| 39Bh    | —       | —                                |        |         |             | Unimple         | emented           |        |              |       | -                     | _                               |

| 39Ch    | MDCON   |                                  | MDEN   | _       | _           | MDOPOL          | MDOUT             | _      | _            | MDBIT | 00 00                 | 00 00                           |

| 39Dh    | MDSRC   |                                  | _      | _       | _           | _               | MDMS<3:0> xxxx 0  |        |              |       | 0 uuuu                |                                 |

| 39Eh    | MDCARH  |                                  | _      | MDCHPOL | MDCHSYNC    | _               |                   |        |              |       | -uu- uuuu             |                                 |

MDCL<3:0>

-xx- xxxx

-uu- uuuu

Legend: x = unknown, u = unchanged, q = depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'.

MDCLSYNC

Note 1: Only on PIC16F18324/18344.

MDCARL

2: Register accessible from both User and ICD Debugger.

39Fh

| TABLE                                           | 4-4: SPE   | CIAL FU                          | INCTION RE | EGISTER S | UMMARY B | ANKS 0-31 (             | CONTINUE | <b>)</b>     |       |       |                       |                                 |

|-------------------------------------------------|------------|----------------------------------|------------|-----------|----------|-------------------------|----------|--------------|-------|-------|-----------------------|---------------------------------|

| Address                                         | Name       | PIC16(L)F18324<br>PIC16(L)F18344 | Bit 7      | Bit 6     | Bit 5    | Bit 4                   | Bit 3    | Bit 2        | Bit 1 | Bit 0 | Value on:<br>POR, BOR | Value or<br>all other<br>resets |

| Bank 28                                         |            |                                  |            |           |          |                         |          |              |       |       |                       |                                 |

| CPU CORE REGISTERS; see Table 4-2 for specifics |            |                                  |            |           |          |                         |          |              |       |       |                       |                                 |

| E21h                                            | SSP1DATPPS | X —                              | —          | _         | _        |                         | 1 0001   | u uuu        |       |       |                       |                                 |

|                                                 |            | — X                              | _          | _         |          | SSP1DATPPS<4:0>0 1      |          |              |       |       | 0 1100                | u uuu                           |

| E22h                                            | SSP1SSPPS  | X —                              | —          | _         | —        |                         | S        | SP1SSPPS<4:0 | >     |       | 1 0011                | u uuu                           |

|                                                 |            | — X                              | —          | —         | —        |                         | S        | SP1SSPPS<4:0 | >     |       | 1 0100                | u uuu                           |

| E23h                                            | _          | —                                |            |           |          | Unimple                 | mented   |              |       |       | -                     | _                               |

| E24h                                            | RXPPS      | X —                              | —          | —         | —        |                         |          | RXPPS<4:0>   |       |       | 1 0101                | u uuu                           |

|                                                 |            | — X                              | _          | —         | —        |                         |          | RXPPS<4:0>   |       |       | 0 1101                | u uui                           |

| E25h                                            | TXPPS      | X —                              | —          | —         | —        |                         |          | TXPPS<4:0>   |       |       | 1 0100                | u uuu                           |

|                                                 |            | — X                              | _          | _         | _        | TXPPS<4:0>0 1111u       |          |              |       |       |                       | u uuu                           |

| E26h                                            | —          | —                                |            |           |          | Unimplemented — —       |          |              |       |       |                       |                                 |

| E27h                                            | _          | —                                |            |           |          | Unimplemented — —       |          |              |       |       |                       |                                 |

| E28h                                            | CLCIN0PPS  | X —                              | _          | _         | _        | CLCIN0PPS<4:0>1 0011u u |          |              |       |       | u uuu                 |                                 |

CLCIN0PPS<4:0>

CLCIN1PPS<4:0>

CLCIN1PPS<4:0>

CLCIN2PPS<4:0>

CLCIN2PPS<4:0>

CLCIN3PPS<4:0>

CLCIN3PPS<4:0>

T3CKIPPS<4:0>

T3CKIPPS<4:0>

T3GPPS<4:0>

T3GPPS<4:0>

T5CKIPPS<4:0>

T5CKIPPS<4:0>

E29h

E2Ah

E2Bh

E2Ch

E2Dh

E2Eh

CLCIN1PPS

CLCIN2PPS

**CLCIN3PPS**

**T3CKIPPS**

T3GPPS

**T5CKIPPS**

x = unknown, u = unchanged, q =depends on condition, - = unimplemented, read as '0', r = reserved. Shaded locations unimplemented, read as '0'. Legend:

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

Note 1: Only on PIC16F18324/18344.

> Register accessible from both User and ICD Debugger. 2:

— X

Х

Х

Х

х

Х

х

\_

\_

\_

\_

\_

\_

—

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

\_

Х

X —

Х

Х

X -

Х -

PIC16(L)F18324/18344

---0 0010

---0 0100

---1 0011

---1 0001

---0 1100

---0 0101

---0 1101

---1 0001

---0 0101

---1 0001

---1 0100

---1 0001

---0 0101

---u uuuu

---u uuuu

---u uuuu

---u uuuu

--u uuuu

---u uuuu

---u uuuu

--u uuuu

---u uuuu

---u uuuu

---u uuuu

---u uuuu

---u uuuu

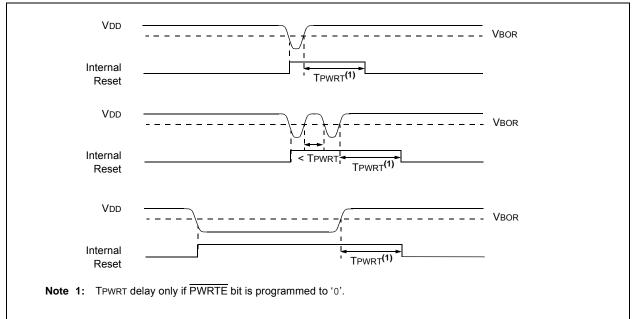

#### 6.2.1 BOR IS ALWAYS ON

When the BOREN bits of Configuration Words are programmed to '11', the BOR is always on. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is active during Sleep. The BOR does not delay wake-up from Sleep.

#### 6.2.2 BOR IS OFF IN SLEEP

When the BOREN bits of Configuration Words are programmed to '10', the BOR is on, except in Sleep. The device start-up will be delayed until the BOR is ready and VDD is higher than the BOR threshold.

BOR protection is not active during Sleep, but device wake-up will be delayed until the BOR can determine that the VDD is higher than the BOR threshold. The device wake-up will be delayed until the BOR is ready.

#### 6.2.3 BOR CONTROLLED BY SOFTWARE

When the BOREN bits of Configuration Words are programmed to '01', the BOR is controlled by the SBOREN bit of the BORCON register. The device wake from sleep is not delayed by the BOR Ready condition or the VDD level only when the SBOREN bit is cleared in software and the device is starting up from a non POR/BOR Reset event.

BOR protection begins as soon as the BOR circuit is ready. The status of the BOR circuit is reflected in the BORRDY bit of the BORCON register.

BOR protection is unchanged by Sleep.

#### 6.2.4 BOR ALWAYS OFF

When the BOREN bits of Configuration Word 2 are programmed to '00', BOR is always disabled. In this configuration, setting the SBOREN bit will have no effect on BOR operation.

#### FIGURE 6-2: BROWN-OUT SITUATIONS

| U-0                                     | R/W-0/0                                          | R/W-0/0                                                | U-0      | U-0            | R/W-0/0          | R/W-0/0          | U-0         |

|-----------------------------------------|--------------------------------------------------|--------------------------------------------------------|----------|----------------|------------------|------------------|-------------|

| —                                       | DACMD                                            | ADCMD                                                  | —        | —              | CMP2MD           | CMP1MD           | —           |

| bit 7                                   |                                                  |                                                        |          |                |                  |                  | bit 0       |

| Legend:                                 |                                                  |                                                        |          |                |                  |                  |             |

| R = Readable                            | bit                                              | W = Writable b                                         | oit      | U = Unimplerr  | nented bit, read | l as '0'         |             |

| u = Bit is unchanged x = Bit is unknown |                                                  |                                                        |          | -n/n = Value a | t POR and BO     | R/Value at all o | ther Resets |

| '1' = Bit is set                        |                                                  | '0' = Bit is clea                                      | red      | q = Value dep  | ends on condit   | ion              |             |

|                                         |                                                  |                                                        |          |                |                  |                  |             |

| bit 7                                   | Unimplemen                                       | ted: Read as '0                                        | 3        |                |                  |                  |             |

| bit 6                                   | <b>DACMD:</b> Disa<br>1 = DAC mod<br>0 = DAC mod | dule disabled                                          |          |                |                  |                  |             |

| bit 5                                   | <b>ADCMD:</b> Disa<br>1 = ADC mod<br>0 = ADC mod | dule disabled                                          |          |                |                  |                  |             |

| bit 4-3                                 | Unimplemen                                       | ted: Read as '0                                        | ,        |                |                  |                  |             |

| bit 2                                   | 1 = Compara                                      | sable Comparat<br>ator C2 module o<br>ator C2 module o | disabled |                |                  |                  |             |

| bit 1                                   | 1 = Compara                                      | sable Comparat<br>ator C1 module o<br>ator C1 module o | disabled |                |                  |                  |             |

|                                         |                                                  |                                                        |          |                |                  |                  |             |

#### REGISTER 14-3: PMD2: PMD CONTROL REGISTER 2

| U-0                               | U-0        | R/W-0/0           | U-0  | U-0                                | U-0             | R/W-0/0          | U-0          |  |  |  |

|-----------------------------------|------------|-------------------|------|------------------------------------|-----------------|------------------|--------------|--|--|--|

|                                   | —          | UART1MD           | —    | _                                  | —               | MSSP1MD          |              |  |  |  |

| bit 7                             |            |                   |      |                                    |                 |                  | bit 0        |  |  |  |

|                                   |            |                   |      |                                    |                 |                  |              |  |  |  |

| Legend:                           | Legend:    |                   |      |                                    |                 |                  |              |  |  |  |

| R = Readable bit W = Writable bit |            |                   | pit  | U = Unimplemented bit, read as '0' |                 |                  |              |  |  |  |

| u = Bit is und                    | changed    | x = Bit is unkn   | own  | -n/n = Value a                     | t POR and BOR   | R/Value at all c | other Resets |  |  |  |

| '1' = Bit is se                   | et         | '0' = Bit is clea | ared | q = Value dep                      | ends on conditi | on               |              |  |  |  |

|                                   |            |                   |      |                                    |                 |                  |              |  |  |  |

| bit 7-6                           | Unimplemen | ted: Read as '0   | ,    |                                    |                 |                  |              |  |  |  |

| bit 5                             | -          | Disable EUSAR     |      |                                    |                 |                  |              |  |  |  |

|                                   |            | 1 module disab    |      |                                    |                 |                  |              |  |  |  |

| hit 4 0                           |            | 1 module enabl    |      |                                    |                 |                  |              |  |  |  |

| bit 4-2                           | Unimplemen | ted: Read as '0   |      |                                    |                 |                  |              |  |  |  |

| bit 1                             |            | Disable MSSP1     |      |                                    |                 |                  |              |  |  |  |

|                                   |            | module disabled   |      |                                    |                 |                  |              |  |  |  |

|                                   |            | module enabled    |      |                                    |                 |                  |              |  |  |  |

| bit 0                             | Unimplemen | ted: Read as '0   | ,    |                                    |                 |                  |              |  |  |  |

### REGISTER 14-5: PMD4: PMD CONTROL REGISTER 4

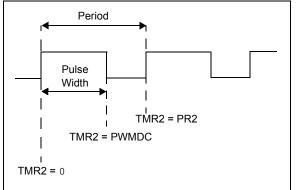

# 19.0 PULSE-WIDTH MODULATION (PWM)

The PWMx modules generate Pulse-Width Modulated (PWM) signals of varying frequency and duty cycle.

In addition to the CCP modules, the PIC16(L)F18324/18344 devices contain two PWM modules.

Pulse-Width Modulation (PWM) is a scheme that provides power to a load by switching quickly between fully on and fully off states. The PWM signal resembles a square wave where the high portion of the signal is considered the 'on' state (pulse width), and the low portion of the signal is considered the 'off' state. The term duty cycle describes the proportion of the 'on' time to the 'off' time and is expressed in percentages, where 0% is fully off and 100% is fully on. A lower duty cycle corresponds to less power applied and a higher duty cycle corresponds to more power applied. The PWM period is defined as the duration of one complete cycle or the total amount of on and off time combined.

PWM resolution defines the maximum number of steps that can be present in a single PWM period. A higher resolution allows for more precise control of the pulse-width time and in turn the power that is applied to the load.

Figure 19-1 shows a typical waveform of the PWM signal.

### 19.1 Standard PWM Mode

The standard PWM mode generates a Pulse-Width Modulation (PWM) signal on the PWMx pin with up to ten bits of resolution. The period, duty cycle, and resolution are controlled by the following registers:

- TMR2, TMR4 or TMR6 registers

- PR2, PR4 or PR6 registers

- PWMxCON registers

- PWMxDCH registers

- PWMxDCL registers

Figure 29-2, "Compare Mode Operation Block Diagram" shows a simplified block diagram of the PWM operation.

If PWMPOL = 0, the default state of the output is '0'. If PWMPOL = 1, the default state is '1'. If PWMEN = '0', the output will be the default state.

Note: The corresponding TRIS bit must be cleared to enable the PWM output on the PWMx pin

Note: The formulas and text refer to TMR2 and PR2, for simplicity. The same formulas and text apply to TMR4/6 and PR4/6. The timer sources can be selected in Register 19-4. For additional information on TMR2/4/6, refer to Section 28.0 "Timer2/4/6 Module"

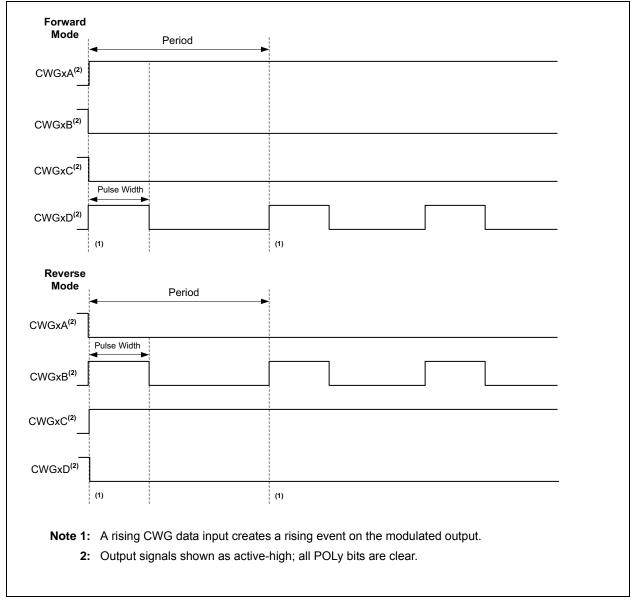

Full-Bridge Reverse Mode

In Full-Bridge Reverse mode (MODE<2:0> = 011),

CWGxC is driven to its active state and CWGxB is modulated while CWGxA and CWGxD are driven to

their inactive state, as illustrated at the bottom of

20.2.4.2

Figure 20-6.

#### 20.2.4.1 Full-Bridge Forward Mode

In Full-Bridge Forward mode (MODE<2:0> = 010), CWGxA is driven to its active state and CWGxD is modulated while CWGxB and CWGxC are driven to their inactive state, as illustrated at the top of Figure 20-6.

#### FIGURE 20-6: EXAMPLE OF FULL-BRIDGE OUTPUT

# 20.2.4.3 Direction Change in Full-Bridge Mode

In Full-Bridge mode, changing MODE<2:0> controls the forward/reverse direction. Changes to MODE<2:0> change to the new direction on the next rising edge of the modulated input.

A direction change is initiated in software by changing the MODE<2:0> bits of the WGxCON0 register. The sequence is illustrated in Figure 20-7.

- The associated active output CWGxA and the inactive output CWGxC are switched to drive in the opposite direction.

- The previously modulated output CWGxD is switched to the inactive state, and the previously inactive output CWGxB begins to modulate.

- CWG modulation resumes after the direction-switch dead band has elapsed.

### 20.9 Operation During Sleep

The CWGx module will operate during Sleep, provided that the input sources remain active.

If the HFINTOSC is selected as the module clock source, dead-band generation will remain active. This will have a direct effect on the Sleep mode current.

# 20.10 Configuring the CWG

- Ensure that the TRIS control bits corresponding to CWG outputs are set so that all are configured as inputs, ensuring that the outputs are inactive during setup. External hardware should ensure that pin levels are held to safe levels.

- 2. Clear the EN bit, if not already cleared.

- Configure the MODE<2:0> bits of the CWGxCON0 register to set the output operating mode.

- 4. Configure the POLy bits of the CWGxCON1 register to set the output polarities.

- 5. Configure the DAT<3:0> bits of the CWGxDAT register to select the data input source.

- 6. If a Steering mode is selected, configure the STRy bits to select the desired output on the CWG outputs.

- Configure the LSBD<1:0> and LSAC<1:0> bits of the CWGxAS0 register to select the autoshutdown output override states (this is necessary even if not using auto-shutdown because start-up will be from a shutdown state).

- If auto-restart is desired, set the REN bit of CWGxAS0.

- 9. If auto-shutdown is desired, configure the ASxE bits of the CWGxAS1 register to select the shutdown source.

- 10. Set the desired rising and falling dead-band times with the CWGxDBR and CWGxDBF registers.

- 11. Select the clock source in the CWGxCLKCON register.

- 12. Set the EN bit to enable the module.

- 13. Clear the TRIS bits that correspond to the CWG outputs to set them as outputs.

- 14. If auto-restart is to be used, set the REN bit and the SHUTDOWN bit will be cleared automatically. Otherwise, clear the SHUTDOWN bit in software to start the CWG.

# PIC16(L)F18324/18344

# 22.1 ADC Configuration

When configuring and using the ADC the following functions must be considered:

- Port configuration

- Channel selection

- · ADC voltage reference selection

- ADC conversion clock source

- Interrupt control

- · Result formatting

#### 22.1.1 PORT CONFIGURATION

The ADC can be used to convert both analog and digital signals. When converting analog signals, the I/O pin should be configured for analog by setting the associated TRIS and ANSEL bits. Refer to **Section 12.0 "I/O Ports"** for more information.

Note: Analog voltages on any pin that is defined as a digital input may cause the input buffer to conduct excess current.

#### 22.1.2 CHANNEL SELECTION

There are several channel selections available:

- Five PORTA pins (RA0-RA2, RA4-RA5)

- Four PORTB pins (RB4-RB7, PIC16(L)F18344 only)

- Six PORTC pins (RC0-RC5, PIC16(L)F18324)

- Eight PORTC pins (RC0-RC7, PIC16(L)F18344 only)

- Temperature Indicator

- DAC output

- Fixed Voltage Reference (FVR)

- Vss (ground)

The CHS<5:0> bits of the ADCON0 register (Register 22-1) determine which channel is connected to the sample and hold circuit.

When changing channels, a delay is required before starting the next conversion. Refer to **Section 22.2 "ADC Operation"** for more information.

Note: It is recommended that when switching from an ADC channel of a higher voltage to a channel of a lower voltage, the software selects the Vss channel before switching to the channel of the lower voltage. If the ADC does not have a dedicated Vss channel, the Vss selection (DAC1R<4:0> = b'00000') through the DAC output channel can be used. If the DAC is in use, a free input channel can be connected to Vss, and can be used in place of the DAC.

#### 22.1.3 ADC VOLTAGE REFERENCE

The ADPREF<1:0> bits of the ADCON1 register provides control of the positive voltage reference. The positive voltage reference can be:

- VREF+ pin

- Vdd

- FVR 2.048V

- FVR 4.096V (Not available on LF devices)

The ADNREF bit of the ADCON1 register provides control of the negative voltage reference. The negative voltage reference can be:

- VREF- pin

- Vss

See Section 22.0 "Analog-to-Digital Converter (ADC) Module" for more details on the Fixed Voltage Reference.

#### 22.1.4 CONVERSION CLOCK

The source of the conversion clock is software selectable via the ADCS<2:0> bits of the ADCON1 register. There are seven possible clock options:

- Fosc/2

- Fosc/4

- Fosc/8

- Fosc/16

- Fosc/32

- Fosc/64

- ADCRC (dedicated RC oscillator)

The time to complete one bit conversion is defined as TAD. One full 10-bit conversion requires 12 TAD periods as shown in Figure 22-2.

For correct conversion, the appropriate TAD specification must be met. Refer to Table 35-13 for more information. Table 22-1 gives examples of appropriate ADC clock selections.

**Note:** Unless using the ADCRC, any changes in the system clock frequency will change the ADC clock frequency, which may adversely affect the ADC result.

| R/W-0/0          | R/W-0/0 | R/W-0/0            | R/W-0/0 | R/W-0/0        | R/W-0/0          | R/W-0/0          | R/W-0/0      |

|------------------|---------|--------------------|---------|----------------|------------------|------------------|--------------|

|                  |         |                    | NCO1I   | NC<15:8>       |                  |                  |              |

| bit 7            |         |                    |         |                |                  |                  | bit 0        |

|                  |         |                    |         |                |                  |                  |              |

| Legend:          |         |                    |         |                |                  |                  |              |

| R = Readable     | bit     | W = Writable bi    | it      | U = Unimplen   | nented bit, read | l as '0'         |              |

| u = Bit is unch  | anged   | x = Bit is unkno   | wn      | -n/n = Value a | t POR and BO     | R/Value at all o | other Resets |

| '1' = Bit is set |         | '0' = Bit is clear | ed      |                |                  |                  |              |

# **REGISTER 23-7:** NCO1INCH<sup>(1)</sup>: NCO1 INCREMENT REGISTER – HIGH BYTE

bit 7-0 NCO1INC<15:8>: NCO1 Increment, high byte

Note 1: The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

# **REGISTER 23-8:** NCO1INCU<sup>(1)</sup>: NCO1 INCREMENT REGISTER – UPPER BYTE

| U-0         | U-0 | U-0 | U-0 | R/W-0/0 | R/W-0/0 | R/W-0/0  | R/W-0/0 |  |

|-------------|-----|-----|-----|---------|---------|----------|---------|--|

| —           | —   | —   | —   |         | NCO1IN  | C<19:16> |         |  |

| bit 7 bit 0 |     |     |     |         |         |          |         |  |

# Legend:

| Legena:              |                      |                                                       |

|----------------------|----------------------|-------------------------------------------------------|

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-4 Unimplemented: Read as '0'

bit 3-0 NCO1INC<19:16>: NCO1 Increment, upper byte

**Note 1:** The logical increment spans NCO1INCU:NCO1INCH:NCO1INCL.

# 25.1 DSM Operation

The DSM module can be enabled by setting the MDEN bit in the MDCON register. Clearing the MDEN bit in the MDCON register, disables the DSM module by automatically switching the carrier high and carrier low signals to the Vss signal source. The modulator signal source is also switched to the MDBIT in the MDCON register. This not only assures that the DSM module is inactive, but that it is also consuming the least amount of current.

The values used to select the carrier high, carrier low, and modulator sources held by the Modulation Source, Modulation High Carrier, and Modulation Low Carrier control registers are not affected when the MDEN bit is cleared and the DSM module is disabled. The values inside these registers remain unchanged while the DSM is inactive. The sources for the carrier high, carrier low and modulator signals will once again be selected when the MDEN bit is set and the DSM module is again enabled and active.

The modulated output signal can be disabled without shutting down the DSM module. The DSM module will remain active and continue to mix signals, but the output value will not be sent to the DSM pin. During the time that the output is disabled, the DSM pin will remain low. The modulated output can be disabled by clearing the MDEN bit in the MDCON register.

#### 25.2 Modulator Signal Sources

The modulator signal can be supplied from the following sources:

- CCP1 Output

- CCP2 Output

- PWM5 Output

- PWM6 Output

- MSSP1 SDO1 (SPI mode only)

- Comparator C1 Output

- Comparator C2 Output

- EUSART TX Output

- External Signal on MDMIN pin

- NCO1 Output

- CLC1 Output

- CLC2 Output

- CLC3 Output

- CLC4 Output

- MDBIT bit in the MDCON register

The modulator signal is selected by configuring the MDMS <3:0> bits in the MDSRC register.

# 25.3 Carrier Signal Sources

The carrier high signal and carrier low signal can be supplied from the following sources:

- CCP1 Output

- CCP2 Output

- PWM5 Output

- PWM6 Output

- NCO1 Output

- Fosc (System Clock)

- HFINTOSC

- CLC1 Output

- CLC2 Output

- CLC3 Output

- CLC4 Output

- CLKR

- External Signal on MDCIN1 pin

- External Signal on MDCIN2 pin

- Vss

The carrier high signal is selected by configuring the MDCH <3:0> bits in the MDCARH register. The carrier low signal is selected by configuring the MDCL <3:0> bits in the MDCARL register.

## 25.4 Carrier Synchronization

During the time when the DSM switches between carrier high and carrier low signal sources, the carrier data in the modulated output signal can become truncated. To prevent this, the carrier signal can be synchronized to the modulator signal. When the modulator signal transitions away from the synchronized carrier, the unsynchronized carrier source is immediately active, while the synchronized carrier remains active until its next falling edge. When the modulator signal transitions back to the synchronized carrier, the unsynchronized carrier is immediately disabled, and the modulator waits until the next falling edge of the synchronized carrier before the synchronized carrier becomes active.

Synchronization is enabled separately for the carrier high and carrier low signal sources. Synchronization for the carrier high signal is enabled by setting the MDCHSYNC bit in the MDCARH register. Synchronization for the carrier low signal is enabled by setting the MDCLSYNC bit in the MDCARL register.

Figure 25-1 through Figure 25-6 show timing diagrams of using various synchronization methods.

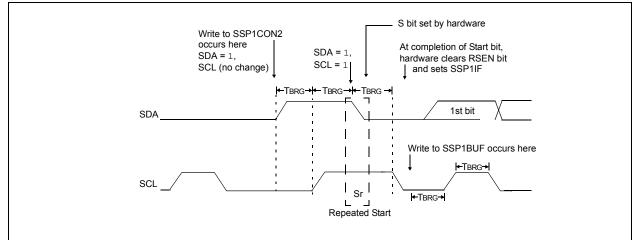

### 30.6.5 I<sup>2</sup>C MASTER MODE REPEATED START CONDITION TIMING

A Repeated Start condition (Figure 30-27) occurs when the RSEN bit of the SSP1CON2 register is programmed high and the master state machine is no longer active. When the RSEN bit is set, the SCL pin is asserted low. When the SCL pin is sampled low, the Baud Rate Generator is loaded and begins counting. The SDA pin is released (brought high) for one Baud Rate Generator count (TBRG). When the Baud Rate Generator times out, if SDA is sampled high, the SCL pin will be deasserted (brought high). When SCL is sampled high, the Baud Rate Generator is reloaded and begins counting. SDA and SCL must be sampled high for one TBRG. This action is then followed by assertion of the SDA pin (SDA = 0) for one TBRG while SCL is high. SCL is asserted low. Following this, the RSEN bit of the SSP1CON2 register will be automatically cleared and the Baud Rate Generator will not be reloaded, leaving the SDA pin held low. As soon as a Start condition is detected on the SDA and SCL pins, the S bit of the SSP1STAT register will be set. The SSP1IF bit will not be set until the Baud Rate Generator has timed out.

| Note 1: | If RSEN is programmed while any other          |  |  |  |  |

|---------|------------------------------------------------|--|--|--|--|

|         | event is in progress, it will not take effect. |  |  |  |  |

- **2:** A bus collision during the Repeated Start condition occurs if:

- SDA is sampled low when SCL goes from low-to-high.

- SCL goes low before SDA is asserted low. This may indicate that another master is attempting to transmit a data '1'.

## FIGURE 30-27: REPEATED START CONDITION WAVEFORM

# PIC16(L)F18324/18344

#### REGISTER 30-7: SSP1BUF: MSSP BUFFER REGISTER

| R/W-x/u |

|---------|---------|---------|---------|---------|---------|---------|---------|

|         |         |         | SSP1Bl  | JF<7:0> |         |         |         |

| bit 7   |         |         |         |         |         |         | bit 0   |

|         |         |         |         |         |         |         |         |

| Legend: |         |         |         |         |         |         |         |

|         |         |         |         |         |         |         |         |

| R = Readable bit     | W = Writable bit     | U = Unimplemented bit, read as '0'                    |

|----------------------|----------------------|-------------------------------------------------------|

| u = Bit is unchanged | x = Bit is unknown   | -n/n = Value at POR and BOR/Value at all other Resets |

| '1' = Bit is set     | '0' = Bit is cleared |                                                       |

bit 7-0 SSP1BUF<7:0>: MSSP Buffer bits

© 2015-2016 Microchip Technology Inc.

# PIC16(L)F18324/18344

| RETLW            | Return with literal in W                                                                                                                                          |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Syntax:          | [ <i>label</i> ] RETLW k                                                                                                                                          |  |  |  |

| Operands:        | $0 \le k \le 255$                                                                                                                                                 |  |  |  |

| Operation:       | $k \rightarrow (W);$<br>TOS $\rightarrow$ PC                                                                                                                      |  |  |  |

| Status Affected: | None                                                                                                                                                              |  |  |  |

| Description:     | The W register is loaded with the 8-bit literal 'k'. The program counter is loaded from the top of the stack (the return address). This is a 2-cycle instruction. |  |  |  |

| Words:           | 1                                                                                                                                                                 |  |  |  |

| Cycles:          | 2                                                                                                                                                                 |  |  |  |

| Example:         | CALL TABLE;W contains table<br>;offset value<br>• ;W now has table value                                                                                          |  |  |  |

| TABLE            | <pre>.<br/>ADDWF PC ;W = offset<br/>RETLW k1 ;Begin table<br/>RETLW k2 ;<br/>RETLW kn ; End of table</pre>                                                        |  |  |  |

|                  | Before Instruction<br>W = 0x07                                                                                                                                    |  |  |  |

After Instruction W =

[label] RETURN

None

None

$\text{TOS} \rightarrow \text{PC}$

**Return from Subroutine**

Return from subroutine. The stack is POPed and the top of the stack (TOS) is loaded into the program counter. This is a 2-cycle instruction.

value of k8

| RLF              | Rotate Left f through Carry                                                                                                                                                                                       |  |  |  |  |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| Syntax:          | [ <i>label</i> ] RLF f,d                                                                                                                                                                                          |  |  |  |  |

| Operands:        | $0 \le f \le 127$<br>$d \in [0,1]$                                                                                                                                                                                |  |  |  |  |

| Operation:       | See description below                                                                                                                                                                                             |  |  |  |  |

| Status Affected: | С                                                                                                                                                                                                                 |  |  |  |  |

| Description:     | The contents of register 'f' are rotated<br>one bit to the left through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>stored back in register 'f'. |  |  |  |  |

|                  | C Register f                                                                                                                                                                                                      |  |  |  |  |

| Words:           | 1                                                                                                                                                                                                                 |  |  |  |  |

| Cycles:          | 1                                                                                                                                                                                                                 |  |  |  |  |

| Example:         | RLF REG1,0                                                                                                                                                                                                        |  |  |  |  |

|                  | Before Instruction                                                                                                                                                                                                |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                                  |  |  |  |  |

|                  | C = 0                                                                                                                                                                                                             |  |  |  |  |

|                  | After Instruction                                                                                                                                                                                                 |  |  |  |  |

|                  | REG1 = 1110 0110                                                                                                                                                                                                  |  |  |  |  |

|                  | $W = 1100 \ 1100$<br>C = 1                                                                                                                                                                                        |  |  |  |  |

|                  | C = 1                                                                                                                                                                                                             |  |  |  |  |

| RRF              | Rotate Right f through Carry                                                                                                                                                                                      |  |  |  |  |

| Syntax:          | [label] RRF f,d                                                                                                                                                                                                   |  |  |  |  |

| Operande         | 0 < f < 107                                                                                                                                                                                                       |  |  |  |  |

|   | Syntax:          | [label] RRF f,d                                                                                                                                                                                                    |

|---|------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|   | Operands:        | $\begin{array}{l} 0 \leq f \leq 127 \\ d  \in  [0,1] \end{array}$                                                                                                                                                  |

|   | Operation:       | See description below                                                                                                                                                                                              |

|   | Status Affected: | С                                                                                                                                                                                                                  |

| _ | Description:     | The contents of register 'f' are rotated<br>one bit to the right through the Carry<br>flag. If 'd' is '0', the result is placed in<br>the W register. If 'd' is '1', the result is<br>placed back in register 'f'. |

| Register f |  |

|------------|--|

|            |  |

RETURN

Operands:

Operation:

Description:

Status Affected:

Syntax:

# 36.0 DC AND AC CHARACTERISTICS GRAPHS AND CHARTS

The graphs and tables provided in this section are for **design guidance** and are **not tested**.

In some graphs or tables, the data presented are **outside specified operating range** (i.e., outside specified VDD range). This is for **information only** and devices are ensured to operate properly only within the specified range.

Unless otherwise noted, all graphs apply to both the L and LF devices.

**Note:** The graphs and tables provided following this note are a statistical summary based on a limited number of samples and are provided for informational purposes only. The performance characteristics listed herein are not tested or guaranteed. In some graphs or tables, the data presented may be outside the specified operating range (e.g., outside specified power supply range) and therefore, outside the warranted range.

"Typical" represents the mean of the distribution at 25°C. "MAXIMUM", "Max.", "MINIMUM" or "Min." represents (mean +  $3\sigma$ ) or (mean -  $3\sigma$ ) respectively, where  $\sigma$  is a standard deviation, over each temperature range.

Charts and graphs are not available at this time.

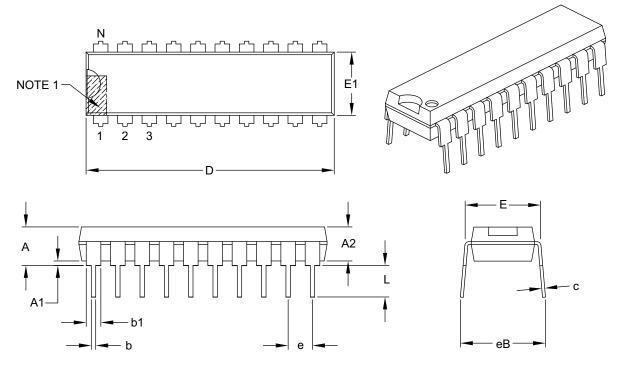

#### 20-Lead Plastic Dual In-Line (P) – 300 mil Body [PDIP]

**Note:** For the most current package drawings, please see the Microchip Packaging Specification located at http://www.microchip.com/packaging

|                            | Units    |          | INCHES |       |  |

|----------------------------|----------|----------|--------|-------|--|

| Dimensio                   | n Limits | MIN      | NOM    | MAX   |  |

| Number of Pins             | Ν        |          | 20     |       |  |

| Pitch                      | е        | .100 BSC |        |       |  |

| Top to Seating Plane       | А        | _        | -      | .210  |  |

| Molded Package Thickness   | A2       | .115     | .130   | .195  |  |

| Base to Seating Plane      | A1       | .015     | _      | -     |  |

| Shoulder to Shoulder Width | Е        | .300     | .310   | .325  |  |

| Molded Package Width       | E1       | .240     | .250   | .280  |  |

| Overall Length             | D        | .980     | 1.030  | 1.060 |  |

| Tip to Seating Plane       | L        | .115     | .130   | .150  |  |

| Lead Thickness             | С        | .008     | .010   | .015  |  |

| Upper Lead Width           | b1       | .045     | .060   | .070  |  |

| Lower Lead Width           | b        | .014     | .018   | .022  |  |

| Overall Row Spacing §      | eВ       | _        | _      | .430  |  |

#### Notes:

1. Pin 1 visual index feature may vary, but must be located within the hatched area.

2. § Significant Characteristic.

3. Dimensions D and E1 do not include mold flash or protrusions. Mold flash or protrusions shall not exceed .010" per side.

4. Dimensioning and tolerancing per ASME Y14.5M.

BSC: Basic Dimension. Theoretically exact value shown without tolerances.

Microchip Technology Drawing C04-019B