#### Welcome to E-XFL.COM

#### What is "Embedded - Microcontrollers"?

"Embedded - Microcontrollers" refer to small, integrated circuits designed to perform specific tasks within larger systems. These microcontrollers are essentially compact computers on a single chip, containing a processor core, memory, and programmable input/output peripherals. They are called "embedded" because they are embedded within electronic devices to control various functions, rather than serving as standalone computers. Microcontrollers are crucial in modern electronics, providing the intelligence and control needed for a wide range of applications.

### Applications of "<u>Embedded -</u> <u>Microcontrollers</u>"

#### Details

E·XF

| Product Status             | Not For New Designs                                                      |

|----------------------------|--------------------------------------------------------------------------|

| Core Processor             | e200z0h                                                                  |

| Core Size                  | 32-Bit Single-Core                                                       |

| Speed                      | 64MHz                                                                    |

| Connectivity               | CANbus, LINbus, SPI, UART/USART                                          |

| Peripherals                | DMA, POR, PWM, WDT                                                       |

| Number of I/O              | 67                                                                       |

| Program Memory Size        | 384KB (384K x 8)                                                         |

| Program Memory Type        | FLASH                                                                    |

| EEPROM Size                | 64K x 8                                                                  |

| RAM Size                   | 36K x 8                                                                  |

| Voltage - Supply (Vcc/Vdd) | 3V ~ 3.6V                                                                |

| Data Converters            | A/D 26x10b                                                               |

| Oscillator Type            | Internal                                                                 |

| Operating Temperature      | -40°C ~ 125°C (TA)                                                       |

| Mounting Type              | Surface Mount                                                            |

| Package / Case             | 100-LQFP                                                                 |

| Supplier Device Package    | 100-LQFP (14x14)                                                         |

| Purchase URL               | https://www.e-xfl.com/product-detail/stmicroelectronics/spc560p44l3ceabr |

|                            |                                                                          |

Email: info@E-XFL.COM

Address: Room A, 16/F, Full Win Commercial Centre, 573 Nathan Road, Mongkok, Hong Kong

|   |        | 1.5.29   | Nexus development interface (NDI)                                   |

|---|--------|----------|---------------------------------------------------------------------|

|   |        | 1.5.30   | Cyclic redundancy check (CRC)27                                     |

|   |        | 1.5.31   | IEEE 1149.1 JTAG controller                                         |

|   |        | 1.5.32   | On-chip voltage regulator (VREG) 28                                 |

| 2 | Packa  | age pinc | outs and signal descriptions                                        |

|   | 2.1    | Package  | e pinouts                                                           |

|   | 2.2    | Pin dese | cription                                                            |

|   |        | 2.2.1    | Power supply and reference voltage pins                             |

|   |        | 2.2.2    | System pins                                                         |

|   |        | 2.2.3    | Pin muxing                                                          |

| 3 | Electr | ical cha | aracteristics                                                       |

|   | 3.1    | Introduc | tion                                                                |

|   | 3.2    | Parame   | ter classification                                                  |

|   | 3.3    | Absolute | e maximum ratings                                                   |

|   | 3.4    | Recomr   | nended operating conditions 53                                      |

|   | 3.5    | Therma   | l characteristics                                                   |

|   |        | 3.5.1    | Package thermal characteristics                                     |

|   |        | 3.5.2    | General notes for specifications at maximum junction temperature 57 |

|   | 3.6    | Electron | nagnetic interference (EMI) characteristics                         |

|   | 3.7    | Electros | tatic discharge (ESD) characteristics                               |

|   | 3.8    | Power n  | nanagement electrical characteristics                               |

|   |        | 3.8.1    | Voltage regulator electrical characteristics                        |

|   |        | 3.8.2    | Voltage monitor electrical characteristics                          |

|   | 3.9    | Power u  | ıp/down sequencing 63                                               |

|   | 3.10   | DC elec  | trical characteristics                                              |

|   |        | 3.10.1   | NVUSRO register                                                     |

|   |        | 3.10.2   | DC electrical characteristics (5 V)                                 |

|   |        | 3.10.3   | DC electrical characteristics (3.3 V)                               |

|   |        | 3.10.4   | Input DC electrical characteristics definition                      |

|   |        | 3.10.5   | I/O pad current specification70                                     |

|   | 3.11   | Main os  | cillator electrical characteristics                                 |

|   | 3.12   | FMPLL    | electrical characteristics                                          |

|   | 3.13   | 16 MHz   | RC oscillator electrical characteristics                            |

| Feature                                              | Full-featured                     | Airbag         |  |  |  |  |

|------------------------------------------------------|-----------------------------------|----------------|--|--|--|--|

| FlexRay                                              | Yes                               | No             |  |  |  |  |

| FMPLL (frequency-modulated phase-locked loop) module | 2 (one FMPLL, one for<br>FlexRay) | 1 (only FMPLL) |  |  |  |  |

### Table 3. SPC560P44Lx, SPC560P50Lx device configuration differences (continued)

# 1.4 Block diagram

*Figure 1* shows a top-level block diagram of the SPC560P44Lx, SPC560P50Lx MCU.

| Block                                             | Function                                                                                                                                                                                                                                                                                                          |

|---------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Analog-to-digital converter (ADC)                 | Multi-channel, 10-bit analog-to-digital converter                                                                                                                                                                                                                                                                 |

| Boot assist module (BAM)                          | Block of read-only memory containing VLE code which is executed according to the boot mode of the device                                                                                                                                                                                                          |

| Clock generation module<br>(MC_CGM)               | Provides logic and control required for the generation of system and peripheral clocks                                                                                                                                                                                                                            |

| Controller area network<br>(FlexCAN)              | Supports the standard CAN communications protocol                                                                                                                                                                                                                                                                 |

| Cross triggering unit (CTU)                       | Enables synchronization of ADC conversions with a timer event from the eMIOS or from the PIT                                                                                                                                                                                                                      |

| Crossbar switch (XBAR)                            | Supports simultaneous connections between two master ports and three slave ports; supports a 32-bit address bus width and a 32-bit data bus width                                                                                                                                                                 |

| Cyclic redundancy check (CRC)                     | CRC checksum generator                                                                                                                                                                                                                                                                                            |

| Deserial serial peripheral<br>interface (DSPI)    | Provides a synchronous serial interface for communication with external devices                                                                                                                                                                                                                                   |

| Enhanced direct memory access (eDMA)              | Performs complex data transfers with minimal intervention from a host processor via "n" programmable channels                                                                                                                                                                                                     |

| Enhanced timer (eTimer)                           | Provides enhanced programmable up/down modulo counting                                                                                                                                                                                                                                                            |

| Error correction status module<br>(ECSM)          | Provides a myriad of miscellaneous control functions for the device including program-visible information about configuration and revision levels, a reset status register, wakeup control for exiting sleep modes, and optional features such as information on memory errors reported by error-correcting codes |

| External oscillator (XOSC)                        | Provides an output clock used as input reference for FMPLL_0 or as reference clock for specific modules depending on system needs                                                                                                                                                                                 |

| Fault collection unit (FCU)                       | Provides functional safety to the device                                                                                                                                                                                                                                                                          |

| Flash memory                                      | Provides non-volatile storage for program code, constants and variables                                                                                                                                                                                                                                           |

| Frequency-modulated phase-<br>locked loop (FMPLL) | Generates high-speed system clocks and supports programmable frequency modulation                                                                                                                                                                                                                                 |

| Interrupt controller (INTC)                       | Provides priority-based preemptive scheduling of interrupt requests                                                                                                                                                                                                                                               |

| JTAG controller                                   | Provides the means to test chip functionality and connectivity while remaining transparent to system logic when not in test mode                                                                                                                                                                                  |

| LINFlex controller                                | Manages a high number of LIN (Local Interconnect Network protocol) messages efficiently with minimum load on CPU                                                                                                                                                                                                  |

| Mode entry module (MC_ME)                         | Provides a mechanism for controlling the device operational mode and mode transition sequences in all functional states; also manages the power control unit, reset generation module and clock generation module, and holds the configuration, control and status registers accessible for applications          |

| Periodic interrupt timer (PIT)                    | Produces periodic interrupts and triggers                                                                                                                                                                                                                                                                         |

| Peripheral bridge (PBRIDGE)                       | Interface between the system bus and on-chip peripherals                                                                                                                                                                                                                                                          |

| Power control unit (MC_PCU)                       | Reduces the overall power consumption by disconnecting parts of the device<br>from the power supply via a power switching device; device components are<br>grouped into sections called "power domains" which are controlled by the PCU                                                                           |

### Table 4. SPC560P44Lx, SPC560P50Lx series block summary

## 1.5.22 FlexRay

The FlexRay module provides the following features:

- Full implementation of FlexRay Protocol Specification 2.1

- 32 configurable message buffers can be handled

- Dual channel or single channel mode of operation, each as fast as 10 Mbit/s data rate

- Message buffers configurable as Tx, Rx or RxFIFO

- Message buffer size configurable

- Message filtering for all message buffers based on FrameID, cycle count and message ID

- Programmable acceptance filters for RxFIFO message buffers

## 1.5.23 Serial communication interface module (LINFlex)

The LINFlex (local interconnect network flexible) on the SPC560P44Lx, SPC560P50Lx features the following:

- Supports LIN Master mode, LIN Slave mode and UART mode

- LIN state machine compliant to LIN1.3, 2.0, and 2.1 specifications

- Handles LIN frame transmission and reception without CPU intervention

- LIN features

- Autonomous LIN frame handling

- Message buffer to store Identifier and as much as 8 data bytes

- Supports message length as long as 64 bytes

- Detection and flagging of LIN errors (sync field, delimiter, ID parity, bit framing, checksum, and time-out)

- Classic or extended checksum calculation

- Configurable Break duration as long as 36-bit times

- Programmable baud rate prescalers (13-bit mantissa, 4-bit fractional)

- Diagnostic features: Loop back; Self Test; LIN bus stuck dominant detection

- Interrupt-driven operation with 16 interrupt sources

- LIN slave mode features

- Autonomous LIN header handling

- Autonomous LIN response handling

- UART mode

- Full-duplex operation

- Standard non return-to-zero (NRZ) mark/space format

- Data buffers with 4-byte receive, 4-byte transmit

- Configurable word length (8-bit or 9-bit words)

- Error detection and flagging

- Parity, Noise and Framing errors

- Interrupt-driven operation with four interrupt sources

- Separate transmitter and receiver CPU interrupt sources

- 16-bit programmable baud-rate modulus counter and 16-bit fractional

- 2 receiver wake-up methods

| Port  | Pad                                                                               | Alternate        |          | I/O             | Pad speed <sup>(5)</sup> |         | Pin No. |     |     |

|-------|-----------------------------------------------------------------------------------|------------------|----------|-----------------|--------------------------|---------|---------|-----|-----|

| pin   | configuration   function <sup>(1)</sup> ,   Functions   Peripheral <sup>(3)</sup> | direction<br>(4) | SRC = 0  | SRC = 1         | 100-pin                  | 144-pin |         |     |     |

|       |                                                                                   | ALT0             | GPIO[14] | SIUL            | I/O                      |         |         |     |     |

|       |                                                                                   | ALT1             | TXD      | Safety Port_0   | 0                        |         |         |     |     |

| A[14] | PCR[14]                                                                           | ALT2             | ETC[4]   | eTimer_1        | I/O                      | Slow    | Medium  | 99  | 143 |

|       |                                                                                   | ALT3             | —        | —               | —                        |         |         |     |     |

|       |                                                                                   | —                | EIRQ[13] | SIUL            | I                        |         |         |     |     |

|       |                                                                                   | ALT0             | GPIO[15] | SIUL            | I/O                      |         |         |     |     |

|       |                                                                                   | ALT1             | —        | —               | —                        |         |         |     |     |

| A[15] | PCR[15]                                                                           | ALT2             | ETC[5]   | eTimer_1        | I/O                      | Slow    | Medium  | 100 | 144 |

| A[15] | FCR[15]                                                                           | ALT3             | —        | —               | —                        | 310W    | Medium  | 100 | 144 |

|       |                                                                                   | —                | RXD      | Safety Port_0   | I                        |         |         |     |     |

|       |                                                                                   | —                | EIRQ[14] | SIUL            | I                        |         |         |     |     |

|       |                                                                                   |                  |          | Port B (16-bit) |                          |         |         |     |     |

|       |                                                                                   | ALT0             | GPIO[16] | SIUL            | I/O                      |         |         |     |     |

|       |                                                                                   | ALT1             | TXD      | FlexCAN_0       | 0                        |         |         |     |     |

| B[0]  | PCR[16]                                                                           | ALT2             | ETC[2]   | eTimer_1        | I/O                      | Slow    | Medium  | 76  | 109 |

|       |                                                                                   | ALT3             | DEBUG[0] | SSCM            | —                        |         |         |     |     |

|       |                                                                                   | —                | EIRQ[15] | SIUL            | I                        |         |         |     |     |

|       |                                                                                   | ALT0             | GPIO[17] | SIUL            | I/O                      |         |         |     |     |

|       |                                                                                   | ALT1             | —        | —               | —                        |         |         |     |     |

| B[1]  | PCR[17]                                                                           | ALT2             | ETC[3]   | eTimer_1        | I/O                      | Slow    | Medium  | 77  | 110 |

| D[1]  | FOR[17]                                                                           | ALT3             | DEBUG[1] | SSCM            | —                        | 310W    | Medium  | 11  | 110 |

|       |                                                                                   | —                | RXD      | FlexCAN_0       | I                        |         |         |     |     |

|       |                                                                                   | —                | EIRQ[16] | SIUL            | I                        |         |         |     |     |

|       |                                                                                   | ALT0             | GPIO[18] | SIUL            | I/O                      |         |         |     |     |

|       |                                                                                   | ALT1             | TXD      | LIN_0           | 0                        |         |         |     |     |

| B[2]  | PCR[18]                                                                           | ALT2             | —        | —               | —                        | Slow    | Medium  | 79  | 114 |

|       |                                                                                   | ALT3             | DEBUG[2] | SSCM            | —                        |         |         |     |     |

|       |                                                                                   | —                | EIRQ[17] | SIUL            | I                        |         |         |     |     |

|       |                                                                                   | ALT0             | GPIO[19] | SIUL            | I/O                      |         |         |     |     |

|       |                                                                                   | ALT1             | —        | —               | —                        |         |         |     |     |

| B[3]  | PCR[19]                                                                           | ALT2             | —        | —               | —                        | Slow    | Medium  | 80  | 116 |

|       |                                                                                   | ALT3             | DEBUG[3] | SSCM            | —                        |         |         |     |     |

|       |                                                                                   | —                | RXD      | LIN_0           | I                        |         |         |     |     |

|       |                                                                                   | ALT0             | GPIO[22] | SIUL            | I/O                      |         |         |     |     |

|       |                                                                                   | ALT1             | CLKOUT   | MC_CGL          | 0                        |         |         |     |     |

| B[6]  | PCR[22]                                                                           | ALT2             | CS2      | DSPI_2          | 0                        | Slow    | Medium  | 96  | 138 |

|       |                                                                                   | ALT3             | —        | —               | —                        |         |         |     |     |

|       |                                                                                   | —                | EIRQ[18] | SIUL            | I                        |         |         |     |     |

# Table 7. Pin muxing (continued)

| Port    | Pad                             | Alternate                       | Alternate    | I/O                       | Pad speed <sup>(5)</sup> |         | Pin No. |         |         |

|---------|---------------------------------|---------------------------------|--------------|---------------------------|--------------------------|---------|---------|---------|---------|

| nin     | configuration<br>register (PCR) | function <sup>(1),</sup><br>(2) | Functions    | Peripheral <sup>(3)</sup> | direction<br>(4)         | SRC = 0 | SRC = 1 | 100-pin | 144-pin |

|         |                                 | ALT0                            | GPIO[23]     | SIUL                      |                          |         |         |         |         |

|         |                                 | ALT1                            |              | —                         |                          |         |         |         |         |

| B[7]    | PCR[23]                         | ALT2                            |              | —                         | Input only               | _       | _       | 29      | 43      |

|         |                                 | ALT3                            |              | ADC_0                     |                          |         |         |         |         |

|         |                                 | _                               | AN[0]<br>RXD | LIN_0                     |                          |         |         |         |         |

|         |                                 | ALT0                            |              |                           |                          |         |         |         |         |

|         |                                 | ALT0<br>ALT1                    | GPIO[24]     | SIUL                      |                          |         |         |         |         |

|         |                                 | ALT2                            | _            | _                         |                          |         |         |         |         |

| B[8]    | PCR[24]                         | ALT3                            |              | _                         | Input only               | —       | —       | 31      | 47      |

|         |                                 | _                               | AN[1]        | ADC_0                     |                          |         |         |         |         |

|         |                                 | —                               | ETC[5]       | eTimer_0                  |                          |         |         |         |         |

|         |                                 | ALT0                            | GPIO[25]     | SIUL                      |                          |         |         |         |         |

|         |                                 | ALT1                            | _            | —                         |                          |         |         |         |         |

| B[9]    | PCR[25]                         | ALT2                            |              | —                         | Input only               | —       | —       | 35      | 52      |

|         |                                 | ALT3                            | —            | —                         |                          |         |         |         |         |

|         |                                 | —                               | AN[11]       | ADC_0 / ADC_1             |                          |         |         |         |         |

|         |                                 | ALT0                            | GPIO[26]     | SIUL                      |                          |         |         |         |         |

| DI ( O) | DODION                          | ALT1                            |              | —                         |                          |         |         |         |         |

| B[10]   | PCR[26]                         | ALT2<br>ALT3                    |              | —                         | Input only               | _       | _       | 36      | 53      |

|         |                                 | ALI3<br>—                       | <br>AN[12]   | ADC_0 / ADC_1             |                          |         |         |         |         |

|         |                                 | ALT0                            | GPIO[27]     | SIUL                      |                          |         |         |         |         |

|         |                                 | ALT1                            | —            |                           |                          |         |         |         |         |

| B[11]   | PCR[27]                         | ALT2                            | _            | _                         | Input only               | _       | _       | 37      | 54      |

|         |                                 | ALT3                            |              | _                         |                          |         |         |         |         |

|         |                                 | —                               | AN[13]       | ADC_0 / ADC_1             |                          |         |         |         |         |

|         |                                 | ALT0                            | GPIO[28]     | SIUL                      |                          |         |         |         |         |

|         |                                 | ALT1                            | _            | —                         |                          |         |         |         |         |

| B[12]   | PCR[28]                         | ALT2                            |              | —                         | Input only               | —       | —       | 38      | 55      |

|         |                                 | ALT3                            | —            | —                         |                          |         |         |         |         |

|         |                                 | _                               | AN[14]       | ADC_0 / ADC_1             |                          |         |         |         |         |

|         |                                 | ALT0                            | GPIO[29]     | SIUL                      |                          |         |         |         |         |

|         |                                 | ALT1                            | _            | —                         |                          |         |         |         |         |

| B[13]   | PCR[29]                         | ALT2<br>ALT3                    | _            |                           | Input only               | —       | —       | 42      | 60      |

|         |                                 | ALIS                            | <br>AN[0]    | ADC_1                     |                          |         |         |         |         |

|         |                                 | _                               | RXD          | LIN_1                     |                          |         |         |         |         |

# Table 7. Pin muxing (continued)

| Port  | Pad                          | Alternate                       |                    |                           | I/O              | Pad s   | peed <sup>(5)</sup> | Pin No. |         |

|-------|------------------------------|---------------------------------|--------------------|---------------------------|------------------|---------|---------------------|---------|---------|

| pin   | configuration register (PCR) | function <sup>(1),</sup><br>(2) | Functions          | Peripheral <sup>(3)</sup> | direction<br>(4) | SRC = 0 | SRC = 1             | 100-pin | 144-pin |

|       |                              | ALT0                            | GPIO[62]           | SIUL                      | I/O              |         |                     |         |         |

|       |                              | ALT1                            | B[1]               | FlexPWM_0                 | 0                |         |                     |         |         |

| D[14] | PCR[62]                      | ALT2                            | CS3                | DSPI_3                    | 0                | Slow    | Medium              | 73      | 105     |

|       |                              | ALT3                            | —                  | —                         | —                |         |                     |         |         |

|       |                              | —                               | SIN                | DSPI_3                    | I                |         |                     |         |         |

|       |                              | ALT0                            | GPIO[63]           | SIUL                      |                  |         |                     |         |         |

|       |                              | ALT1                            | —                  | —                         |                  |         |                     |         |         |

| D[15] | PCR[63]                      | ALT2                            | _                  | —                         | Input only       | —       | —                   | 41      | 58      |

|       |                              | ALT3                            | —                  | —                         |                  |         |                     |         |         |

|       |                              | —                               | AN[4]              | ADC_1                     |                  |         |                     |         |         |

|       |                              |                                 |                    | Port E(16-bit)            |                  |         |                     |         |         |

|       |                              | ALT0                            | GPIO[64]           | SIUL                      |                  |         |                     |         |         |

|       |                              | ALT1                            | —                  | —                         |                  |         |                     |         |         |

| E[0]  | PCR[64]                      | ALT2                            | _                  | —                         | Input only       | —       | —                   | 46      | 68      |

|       |                              | ALT3                            | —                  | —                         |                  |         |                     |         |         |

|       |                              | —                               | AN[5]              | ADC_1                     |                  |         |                     |         |         |

|       |                              | ALT0                            | GPIO[65]           | SIUL                      |                  |         |                     |         |         |

|       |                              | ALT1                            | —                  | —                         |                  |         |                     |         |         |

| E[1]  | PCR[65]                      | ALT2                            | —                  | —                         | Input only       | —       | —                   | 27      | 39      |

|       |                              | ALT3                            | —                  | —                         |                  |         |                     |         |         |

|       |                              | —                               | AN[4]              | ADC_0                     |                  |         |                     |         |         |

|       |                              | ALT0                            | GPIO[66]           | SIUL                      |                  |         |                     |         |         |

|       |                              | ALT1                            | —                  | —                         |                  |         |                     |         |         |

| E[2]  | PCR[66]                      | ALT2                            | —                  | —                         | Input only       | —       | —                   | 32      | 49      |

|       |                              | ALT3                            | —                  | —                         |                  |         |                     |         |         |

|       |                              | —                               | AN[5]              | ADC_0                     |                  |         |                     |         |         |

|       |                              | ALT0                            | GPIO[67]           | SIUL                      |                  |         |                     |         |         |

|       |                              | ALT1                            | —                  | —                         |                  |         |                     |         |         |

| E[3]  | PCR[67]                      | ALT2                            | —                  | —                         | Input only       | —       | —                   |         | 40      |

|       |                              | ALT3                            | —<br>• • • • • • • | —                         |                  |         |                     |         |         |

|       |                              | _                               | AN[6]              | ADC_0                     |                  |         |                     |         |         |

|       |                              | ALT0                            | GPIO[68]           | SIUL                      |                  |         |                     |         |         |

|       |                              | ALT1                            | —                  | —                         |                  |         |                     |         |         |

| E[4]  | PCR[68]                      | ALT2                            | —                  | —                         | Input only       | —       | _                   |         | 42      |

|       |                              | ALT3                            |                    | —                         |                  |         |                     |         |         |

|       |                              | —                               | AN[7]              | ADC_0                     |                  |         |                     |         |         |

# Table 7. Pin muxing (continued)

# **3 Electrical characteristics**

## 3.1 Introduction

This section contains device electrical characteristics as well as temperature and power considerations.

This microcontroller contains input protection against damage due to high static voltages. However, it is advisable to take precautions to avoid application of any voltage higher than the specified maximum rated voltages.

To enhance reliability, unused inputs can be driven to an appropriate logic voltage level ( $V_{DD}$  or  $V_{SS}$ ). This can be done by the internal pull-up or pull-down resistors, which are provided by the device for most general purpose pins.

The following tables provide the device characteristics and its demands on the system.

In the tables where the device logic provides signals with their respective timing characteristics, the symbol "CC" for Controller Characteristics is included in the Symbol column.

In the tables where the external system must provide signals with their respective timing characteristics to the device, the symbol "SR" for System Requirement is included in the Symbol column.

**Caution:** All of the following parameter values can vary depending on the application and must be confirmed during silicon characterization or silicon reliability trial.

# 3.2 Parameter classification

The electrical parameters are guaranteed by various methods. To give the customer a better understanding, the classifications listed in *Table 8* are used and the parameters are tagged accordingly in the tables where appropriate.

| Classification tag                                                                                                                                                                                                  | Tag description                                                                                                                           |  |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Р                                                                                                                                                                                                                   | Those parameters are guaranteed during production testing on each individual device.                                                      |  |  |  |

| С                                                                                                                                                                                                                   | Those parameters are achieved by the design characterization by measuring a statistically relevant sample size across process variations. |  |  |  |

| T Those parameters are achieved by design characterization on a small sample size from typical devices under typical conditions unless otherwise noted. All values shown in the ty column are within this category. |                                                                                                                                           |  |  |  |

| D                                                                                                                                                                                                                   | Those parameters are derived mainly from simulations.                                                                                     |  |  |  |

Table 8.Parameter classifications

Note: The classification is shown in the column labeled "C" in the parameter tables where appropriate.

# 3.3 Absolute maximum ratings

| 0 mm h a l                            | Deromotor |                                                                                                                | O an alliticana                       |      | Unit                                  |     |  |

|---------------------------------------|-----------|----------------------------------------------------------------------------------------------------------------|---------------------------------------|------|---------------------------------------|-----|--|

| Symbol                                |           | Parameter                                                                                                      | Conditions                            | Min  | Max <sup>(2)</sup>                    |     |  |

| V <sub>SS</sub>                       | SR        | Device ground                                                                                                  | —                                     | 0    | 0                                     | V   |  |

| V <sub>DD_HV_IOx</sub> <sup>(3)</sup> | SR        | 3.3 V / 5.0 V input/output supply voltage with respect to ground (V <sub>SS</sub> )                            | —                                     | -0.3 | 6.0                                   | V   |  |

| V <sub>SS_HV_IOx</sub>                | SR        | Input/output ground voltage with respect to ground (V <sub>SS</sub> )                                          | —                                     | -0.1 | 0.1                                   | V   |  |

|                                       |           | 3.3 V / 5.0 V code and data flash                                                                              | —                                     |      | 6.0                                   |     |  |

| V <sub>DD_HV_FL</sub>                 | SR        | supply voltage with respect to ground $(V_{SS})$                                                               | Relative to<br>V <sub>DD_HV_IOx</sub> | -0.3 | V <sub>DD_HV_IOx</sub> + 0.3          | V   |  |

| $V_{SS_HV_FL}$                        | SR        | Code and data flash ground with respect to ground (V <sub>SS</sub> )                                           | —                                     | -0.1 | 0.1                                   | V   |  |

|                                       |           | 3.3 V / 5.0 V crystal oscillator                                                                               | —                                     |      | 6.0                                   |     |  |

| V <sub>DD_HV_OSC</sub>                | SR        | amplifier supply voltage with respect to ground ( $V_{SS}$ )                                                   | Relative to<br>V <sub>DD_HV_IOx</sub> | -0.3 | V <sub>DD_HV_IOx</sub> + 0.3          | V   |  |

| V <sub>SS_HV_OSC</sub>                | SR        | 3.3 V / 5.0 V crystal oscillator<br>amplifier reference voltage with<br>respect to ground (V <sub>SS</sub> )   | —                                     | -0.1 | 0.1                                   | V   |  |

|                                       |           | 3.3 V / 5.0 V voltage regulator suppl                                                                          | —                                     |      | 6.0                                   |     |  |

| $V_{DD_HV_REG}$                       | SR        | voltage with respect to ground (V <sub>SS</sub> )                                                              | Relative to<br>V <sub>DD_HV_IOx</sub> | -0.3 | V <sub>DD_HV_IOx</sub> + 0.3          | V   |  |

| V <sub>DD_HV_</sub> ADC0              | QD        | 3.3 V / 5.0 V ADC_0 supply and high reference voltage with respect to                                          | V <sub>DD_HV_REG</sub> < 2.7 V        | -0.3 | $V_{DD_{HV_{REG}}} + 0.3$             | V   |  |

| - (4)-                                | SIX       | ground (V <sub>SS</sub> )                                                                                      | V <sub>DD_HV_REG</sub> ><br>2.7 V     | -0.3 | 6.0                                   | v   |  |

| V <sub>SS_HV_ADC0</sub>               | SR        | ADC_0 ground and low reference voltage with respect to ground (V <sub>SS</sub> )                               | —                                     | -0.1 | 0.1                                   | V   |  |

| V <sub>DD_HV_ADC1</sub> (             | сD        | 3.3 V / 5.0 V ADC_0 supply and high reference voltage with respect to                                          | V <sub>DD_HV_REG</sub> < 2.7 V        | -0.3 | V <sub>DD_HV_REG</sub> + 0.3          | V   |  |

| - 4)-                                 | SN        | ground (V <sub>SS</sub> )                                                                                      | V <sub>DD_HV_REG</sub> ><br>2.7 V     | -0.3 | 6.0                                   | v   |  |

| V <sub>SS_HV_ADC1</sub>               | SR        | ADC_1 ground and low reference voltage with respect to ground (V <sub>SS</sub> )                               | —                                     | -0.1 | 0.1                                   | V   |  |

| TV <sub>DD</sub>                      | SR        | Slope characteristics on all $V_{DD}$ during power up <sup>(5)</sup> with respect to ground (V <sub>SS</sub> ) | _                                     | 3.0  | 500 x 10 <sup>3</sup><br>(0.5 [V/µs]) | V/s |  |

|                                       |           | Voltage on any pin with respect to                                                                             | —                                     |      | 6.0                                   |     |  |

| V <sub>IN</sub>                       | SR        | ground (V_{SS_HV_IOx}) with respect to ground (V_{SS})                                                         | Relative to<br>V <sub>DD_HV_IOx</sub> | -0.3 | V <sub>DD_HV_IOx</sub> + 0.3          | V   |  |

## Table 9. Absolute maximum ratings<sup>(1)</sup>

- C.E. Triplett and B. Joiner, An Experimental Characterization of a 272 PBGA Within an Automotive Engine Controller Module, Proceedings of SemiTherm, San Diego, 1998, pp. 47–54.

- 2. G. Kromann, S. Shidore, and S. Addison, *Thermal Modeling of a PBGA for Air-Cooled Applications*, Electronic Packaging and Production, pp. 53–58, March 1998.

- 3. B. Joiner and V. Adams, *Measurement and Simulation of Junction to Board Thermal Resistance and Its Application in Thermal Modeling*, Proceedings of SemiTherm, San Diego, 1999, pp. 212–220.

# 3.6 Electromagnetic interference (EMI) characteristics

| Symbol           | Parameter          | Conditions                                                                                            | Clocks                                                    | Frequency       | Level<br>(Max) | Unit |

|------------------|--------------------|-------------------------------------------------------------------------------------------------------|-----------------------------------------------------------|-----------------|----------------|------|

|                  |                    | 1) ovice contiguration test                                                                           | f <sub>OSC</sub> 8 MHz                                    | 150 kHz–150 MHz | 16             | dBµV |

|                  |                    | adiated emissions<br>Supply voltage = 5 V DC<br>Ambient temperature = 25 °C<br>Worst-case orientation | f <sub>CPU</sub> 64 MHz<br>No PLL frequency<br>modulation | 150–1000 MHz    | 15             | uυμν |

| V                | Radiated emissions |                                                                                                       |                                                           | IEC Level       | М              | —    |

| V <sub>EME</sub> |                    |                                                                                                       | f <sub>OSC</sub> 8 MHz<br>f <sub>CPU</sub> 64 MHz         | 150 kHz–150 MHz | 15             | dBµV |

|                  |                    |                                                                                                       |                                                           | 150–1000 MHz    | 14             | ubµv |

|                  |                    |                                                                                                       | 1% PLL frequency modulation                               | IEC Level       | М              | —    |

### Table 14. EMI testing specifications

# 3.7 Electrostatic discharge (ESD) characteristics

### Table 15.ESD ratings(1),(2)

| Symbol                |        | Parameter                                      | Conditions | Value         | Unit |

|-----------------------|--------|------------------------------------------------|------------|---------------|------|

| V <sub>ESD(HBM)</sub> | S<br>R | Electrostatic discharge (Human Body Model)     | _          | 2000          | V    |

|                       | s      | Electrostatic discharge (Charged Device Model) |            | 750 (corners) | v    |

| VESD(CDM) F           | R      | Electrostatic discharge (Charged Device Model) | _          | 500 (other)   | v    |

1. All ESD testing is in conformity with CDF-AEC-Q100 Stress Test Qualification for Automotive Grade Integrated Circuits.

2. A device will be defined as a failure if after exposure to ESD pulses the device no longer meets the device specification requirements. Complete DC parametric and functional testing shall be performed per applicable device specification at room temperature followed by hot temperature, unless specified otherwise in the device specification.

# **3.8 Power management electrical characteristics**

### 3.8.1 Voltage regulator electrical characteristics

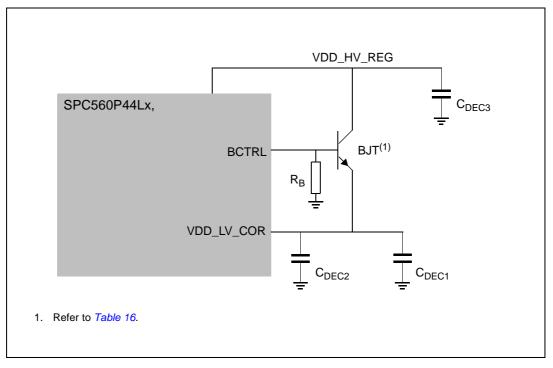

The internal voltage regulator requires an external NPN ballast to be connected as shown in *Figure 9. Table 16* contains all approved NPN ballast components. Capacitances should be placed on the board as near as possible to the associated pins. Care should also be taken to limit the serial inductance of the V<sub>DD HV REG</sub>, BCTRL and V<sub>DD LV CORx</sub> pins to less than

L<sub>Rea</sub>, see Table 17.

Note:

The voltage regulator output cannot be used to drive external circuits. Output pins are used only for decoupling capacitances.

$V_{DD\_LV\_COR}$  must be generated using internal regulator and external NPN transistor. It is not possible to provide  $V_{DD\_LV\_COR}$  through external regulator.

For the SPC560P44Lx, SPC560P50Lx microcontroller, capacitors, with total values not below  $C_{DEC1}$ , should be placed between  $V_{DD\_LV\_CORx}/V_{SS\_LV\_CORx}$  close to external ballast transistor emitter. 4 capacitors, with total values not below  $C_{DEC2}$ , should be placed close to microcontroller pins between each  $V_{DD\_LV\_CORx}/V_{SS\_LV\_CORx}$  supply pairs and the  $V_{DD\_LV\_REGCOR}/V_{SS\_LV\_REGCOR}$  pair . Additionally, capacitors with total values not below  $C_{DEC3}$ , should be placed between the  $V_{DD\_HV\_REG}/V_{SS\_HV\_REG}$  pins close to ballast collector. Capacitors values have to take into account capacitor accuracy, aging and variation versus temperature.

All reported information are valid for voltage and temperature ranges described in recommended operating condition, *Table 10* and *Table 11*.

### Table 16. Approved NPN ballast components (configuration with resistor on base)

| Part  | Manufacturer | Approved derivatives <sup>(1)</sup> |

|-------|--------------|-------------------------------------|

|       | ON Semi      | BCP68                               |

| BCP68 | NXP          | BCP68-25                            |

|       | Infineon     | BCP68-25                            |

| BCX68 | Infineon     | BCX68-10;BCX68-16;BCX68-25          |

| BC868 | NXP          | BC868                               |

| Part  | Manufacturer | Approved derivatives <sup>(1)</sup> |

|-------|--------------|-------------------------------------|

| BC817 | Infineon     | BC817-16;BC817-25;BC817SU;          |

| BCOTT | NXP          | BC817-16;BC817-25                   |

|       | ST           | BCP56-16                            |

| BCP56 | Infineon     | BCP56-10;BCP56-16                   |

| BCP56 | ON Semi      | BCP56-10                            |

|       | NXP          | BCP56-10;BCP56-16                   |

### Table 16. Approved NPN ballast components (configuration with resistor on base)

1. For automotive applications please check with the appropriate transistor vendor for automotive grade certification

| Symbol                    |    | с | Parameter                                                                       | Conditions                                                                                                                                        |                                                                                                | Value                                                                                                                                                                                                                   |      | Unit |    |

|---------------------------|----|---|---------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|------|----|

| Symbol                    |    | C | Parameter                                                                       | Conditions                                                                                                                                        | Min                                                                                            | Тур                                                                                                                                                                                                                     | Max  | Unit |    |

| V <sub>DD_LV_REGCOR</sub> | сс | Ρ | Output voltage under<br>maximum load run supply<br>current configuration        | Post-trimming                                                                                                                                     | 1.15                                                                                           | _                                                                                                                                                                                                                       | 1.32 | V    |    |

| R <sub>B</sub>            | SR | — | External resistance on bipolar junction transistor (BJT) base                   | _                                                                                                                                                 | 18                                                                                             |                                                                                                                                                                                                                         | 22   | kΩ   |    |

| C <sub>DEC1</sub>         | SR | _ | External decoupling/stability ceramic capacitor                                 | BJT from <i>Table 16</i> . 3<br>capacitances (i.e. X7R or<br>X8R capacitors) with nominal<br>value of 10 µF                                       | 19.5                                                                                           | Min         Typ         Max           1.15          1.32           18          22           19.5         30            14.3         22            14.3         22            10          40           1200         1760 | μF   |      |    |

|                           |    |   |                                                                                 | BJT BC817, one capacitance of 22 μF                                                                                                               | 7, one capacitance 14.3 22                                                                     |                                                                                                                                                                                                                         | μF   |      |    |

|                           |    |   |                                                                                 | Resulting ESR of all three capacitors of C <sub>DEC1</sub>                                                                                        | BJT from <i>Table 16</i> . 3x10 μF.<br>Absolute maximum value<br>between 100 kHz and<br>10 MHz | _                                                                                                                                                                                                                       | _    | 50   | mΩ |

| R <sub>REG</sub>          | SR |   | Resulting ESR of the unique capacitor C <sub>DEC1</sub>                         | BJT BC817, 1x 22 µF.<br>Absolute maximum value<br>between 100 kHz and<br>10 MHz                                                                   | 10                                                                                             |                                                                                                                                                                                                                         | 40   | mΩ   |    |

| C <sub>DEC2</sub>         | SR | _ | External decoupling/stability ceramic capacitor                                 | 4 capacitances (i.e. X7R or<br>X8R capacitors) with nominal<br>value of 440 nF                                                                    | 1200                                                                                           | 1760                                                                                                                                                                                                                    | _    | nF   |    |

| C <sub>DEC3</sub>         | SR |   | External decoupling/stability<br>ceramic capacitor on<br>V <sub>DD_HV_REG</sub> | 3 capacitances (i.e. X7R or X8R capacitors) with nominal value of 10 $\mu$ F; C <sub>DEC3</sub> has to be equal or greater than C <sub>DEC1</sub> | 19.5                                                                                           | 30                                                                                                                                                                                                                      |      | μF   |    |

| L <sub>Reg</sub>          | SR | — | Resulting ESL of V_DD_HV_REG BCTRL and V_DD_LV_CORx pins                        | _                                                                                                                                                 | _                                                                                              | —                                                                                                                                                                                                                       | 15   | nH   |    |

### Table 17. Voltage regulator electrical characteristics (configuration with resistor on base)

| 0                   | ~  | Descustor                                            | O an dition o                     | Va                    | alue                                                                                                                     | 11   |  |

|---------------------|----|------------------------------------------------------|-----------------------------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------|------|--|

| Symbol              | C  | Parameter                                            | Conditions                        | Min                   | Max          V <sub>DD_HV_IOx</sub> + 0.1 <sup>(2)</sup> 0.5          0.5          0.5          0.5          10       10 | Unit |  |

| V                   | Ρ  | High level input voltage                             | —                                 | $0.65 V_{DD_HV_IOx}$  | —                                                                                                                        | V    |  |

| V <sub>IH</sub>     | D  | i lightlevel linput voltage                          | —                                 | —                     | $V_{DD\_HV\_IOx} + 0.1^{(2)}$                                                                                            | V    |  |

| V <sub>HYS</sub>    | Т  | Schmitt trigger hysteresis                           | —                                 | $0.1 V_{DD_HV_IOx}$   | —                                                                                                                        | V    |  |

| $V_{OL_S}$          | Ρ  | Slow, low level output voltage                       | I <sub>OL</sub> = 1.5 mA          | —                     | 0.5                                                                                                                      | V    |  |

| V <sub>OH_S</sub>   | Ρ  | Slow, high level output voltage                      | I <sub>OH</sub> = -1.5 mA         | $V_{DD_HV_IOx} - 0.8$ | —                                                                                                                        | V    |  |

| V <sub>OL_M</sub>   | Ρ  | Medium, low level output voltage                     | I <sub>OL</sub> = 2 mA            | —                     | 0.5                                                                                                                      | V    |  |

| V <sub>OH_M</sub>   | Ρ  | Medium, high level output voltage                    | I <sub>OH</sub> = -2 mA           | $V_{DD_HV_IOx} - 0.8$ | —                                                                                                                        | V    |  |

| $V_{OL_F}$          | Ρ  | Fast, low level output voltage                       | I <sub>OL</sub> = 1.5 mA          | —                     | 0.5                                                                                                                      | V    |  |

| V <sub>OH_F</sub>   | Ρ  | Fast, high level output voltage                      | I <sub>OH</sub> = -1.5 mA         | $V_{DD_HV_IOx} - 0.8$ | —                                                                                                                        | V    |  |

| V <sub>OL_SYM</sub> | Ρ  | Symmetric, low level output voltage                  | I <sub>OL</sub> = 1.5 mA          | —                     | 0.5                                                                                                                      | V    |  |

| V <sub>OH_SYM</sub> | Ρ  | Symmetric, high level output voltage                 | I <sub>OH</sub> = -1.5 mA         | $V_{DD_HV_IOx} - 0.8$ | —                                                                                                                        | V    |  |

|                     | р  | Equivalent pull-up current                           | $V_{IN} = V_{IL}$                 | -130                  | —                                                                                                                        |      |  |

| I <sub>PU</sub>     | Г  | Equivalent pull-up current                           | $V_{IN} = V_{IH}$                 | —                     | -10                                                                                                                      | μA   |  |

|                     | р  | Equivalent pull-down current                         | $V_{IN} = V_{IL}$                 | 10                    | —                                                                                                                        |      |  |

| I <sub>PD</sub>     | Г  | Equivalent pull-down current                         | $V_{IN} = V_{IH}$                 | —                     | 130                                                                                                                      | μA   |  |

| IIL                 | Ρ  | Input leakage current (all<br>bidirectional ports)   | $T_{A} = -40$ to 125 °C           | _                     | 1                                                                                                                        | μA   |  |

| Ι <sub>ΙL</sub>     | Ρ  | Input leakage current (all ADC input-<br>only ports) | $T_{A} = -40$ to 125 °C           | _                     | 0.5                                                                                                                      | μA   |  |

| C <sub>IN</sub>     | D  | Input capacitance                                    | —                                 | —                     | 10                                                                                                                       | pF   |  |

|                     |    | RESET, equivalent pull-up current                    | $V_{IN} = V_{IL}$                 | -130                  | —                                                                                                                        |      |  |

| I <sub>PU</sub>     | טן | RESET, equivalent pull-up current                    | V <sub>IN</sub> = V <sub>IH</sub> | —                     | -10                                                                                                                      | μA   |  |

# Table 23.DC electrical characteristics (3.3 V, NVUSRO[PAD3V5V] = 1)<sup>(1)</sup> (continued)

1. These specifications are design targets and subject to change per device characterization.

2. "SR" parameter values must not exceed the absolute maximum ratings shown in Table 9.

Calling  $f_0$  the bandwidth of the source signal (and as a consequence the cut-off frequency of the anti-aliasing filter,  $f_F$ ), according to the Nyquist theorem the conversion rate  $f_C$  must be at least  $2f_0$ ; it means that the constant time of the filter is greater than or at least equal to twice the conversion period ( $T_C$ ). Again the conversion period  $T_C$  is longer than the sampling time  $T_S$ , which is just a portion of it, even when fixed channel continuous conversion mode is selected (fastest conversion rate at a specific channel): in conclusion it is evident that the time constant of the filter  $R_FC_F$  is definitively much higher than the sampling time  $T_S$ , so the charge level on  $C_S$  cannot be modified by the analog signal source during the time in which the sampling switch is closed.

The considerations above lead to impose new constraints on the external circuit, to reduce the accuracy error due to the voltage drop on  $C_S$ ; from the two charge balance equations above, it is simple to derive *Equation 11* between the ideal and real sampled voltage on  $C_S$ :

#### **Equation 11**

$$\frac{V_A}{V_{A2}} = \frac{C_{P1} + C_{P2} + C_F}{C_{P1} + C_{P2} + C_F + C_S}$$

From this formula, in the worst case (when  $V_A$  is maximum, that is for instance 5 V), assuming to accept a maximum error of half a count, a constraint is evident on  $C_F$  value:

**Equation 12**

$$C_F > 2048 \bullet C_S$$

### 3.14.2 ADC conversion characteristics

| Table 33. ADC conversion characteristics | Table 33. | ADC conversion characteristics |

|------------------------------------------|-----------|--------------------------------|

|------------------------------------------|-----------|--------------------------------|

| Symbo                | ol                | с | Parameter                                                                                                                  | Conditions <sup>(1)</sup>                                | N                                | Unit |                                  |      |  |

|----------------------|-------------------|---|----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------|----------------------------------|------|----------------------------------|------|--|

| Symb                 |                   | C | raiametei                                                                                                                  | Conditions                                               | Min                              | Тур  | Max                              | Unit |  |

| V <sub>INAN0</sub>   | SR                |   | ADC0 and shared ADC0/1<br>analog input voltage <sup>(2), (3)</sup>                                                         | _                                                        | V <sub>SS_HV_ADV0</sub><br>- 0.3 | _    | V <sub>DD_HV_ADV0</sub><br>+ 0.3 | V    |  |

| V <sub>INAN1</sub>   | SR                |   | ADC1 analog input voltage <sup>(2),</sup> <sup>(4)</sup>                                                                   | _                                                        | V <sub>SS_HV_ADV1</sub><br>- 0.3 | _    | V <sub>DD_HV_ADV1</sub><br>+ 0.3 | V    |  |

| f <sub>CK</sub>      | SR                |   | ADC clock frequency<br>(depends on ADC<br>configuration)<br>(The duty cycle depends on<br>AD_clk <sup>(5)</sup> frequency) | _                                                        | 3(6)                             | _    | 60                               | MHz  |  |

| f <sub>s</sub>       | SR                | — | Sampling frequency                                                                                                         | —                                                        | _                                |      | 1.53                             | MHz  |  |

| tuna                 | tapc s — D Sample |   | (7)                                                                                                                        | f <sub>ADC</sub> = 20 MHz,<br>INPSAMP = 3                | 125                              | _    | —                                | ns   |  |

| t <sub>ADC_S</sub> — |                   |   | f <sub>ADC</sub> = 9 MHz,<br>INPSAMP = 255                                                                                 |                                                          | _                                | 28.2 | μs                               |      |  |

| t <sub>ADC_C</sub>   | _                 | Ρ | Conversion time <sup>(8)</sup>                                                                                             | f <sub>ADC</sub> = 20 MHz <sup>(9)</sup> ,<br>INPCMP = 1 | 0.650                            | _    | _                                | μs   |  |

| Na  | No. Symbol                            |    | с | Parameter                                                 | Conditions | Value |     | Unit |

|-----|---------------------------------------|----|---|-----------------------------------------------------------|------------|-------|-----|------|

| NO. |                                       |    | C | Falameter                                                 | Conditions | Min   | Max | Unit |

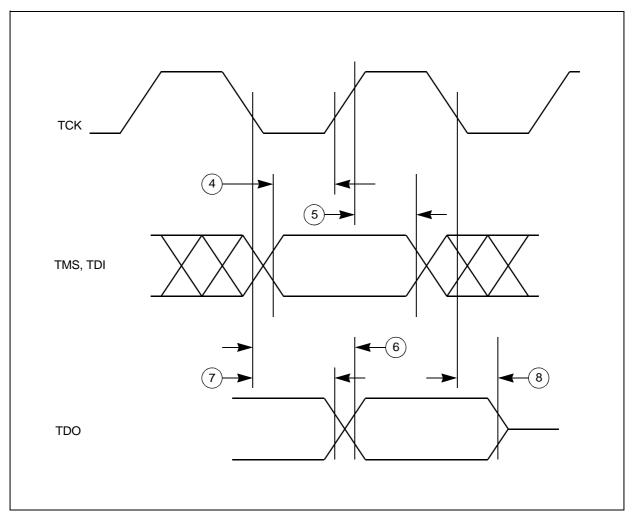

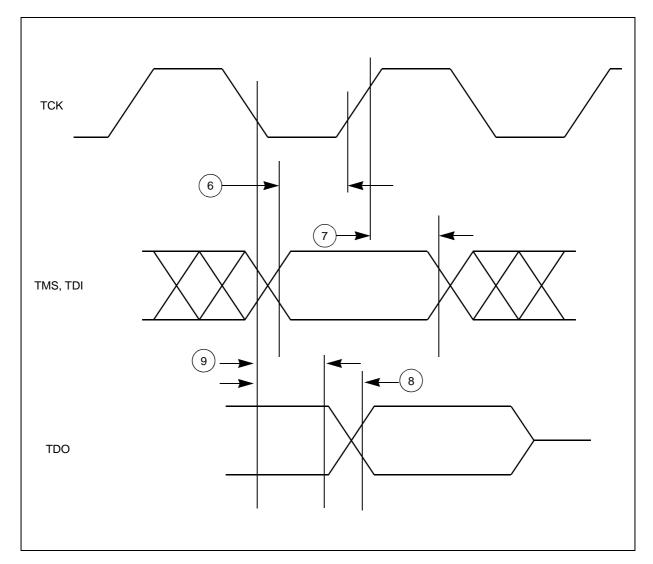

| 5   | t <sub>TMSH</sub> , t <sub>TDIH</sub> | CC | D | TMS, TDI data hold time                                   | —          | 25    | —   | ns   |

| 6   | t <sub>TDOV</sub>                     | СС | D | TCK low to TDO data valid                                 | —          |       | 40  | ns   |

| 7   | t <sub>TDOI</sub>                     | CC | D | TCK low to TDO data invalid                               | —          | 0     | —   | ns   |

| 8   | t <sub>TDOHZ</sub>                    | CC | D | TCK low to TDO high impedance                             | _          | 40    | —   | ns   |